Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Informe #1

Informe #1

Cargado por

Omar GarcíaTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Informe #1

Informe #1

Cargado por

Omar GarcíaCopyright:

Formatos disponibles

Informe N 1 Contadores 1. Objetivos Disear un contador que cumpla con las condiciones impuestas por el diseador.

r. Aprender el proceso de diseo de un contador.

2. Fundamento terico Un contador es un sistema secuencial con una sola entrada de informacin y varias salidas, la nica informacin de estrada son los pulsos de reloj, tambin se puede decir que los contadores son asociaciones de biestables (Flip Flops) que en respuesta a una seal de reloj cambia el valor binario de las salidas cuyas combinaciones pueden estar estructuradas en un cdigo binario cualquiera. En electrnica digital, Un contador (counter en ingls) es un circuito secuencial construido a partir de biestables y puertas lgicas capaz de realizar el cmputo de los impulsos que recibe en la entrada destinada a tal efecto, almacenar datos o actuar como divisor de frecuencia. Habitualmente, el cmputo se realiza en un cdigo binario, que con frecuencia ser el binario natural o el BCD natural (contador de dcadas). Segn la forma en que conmutan los biestables, podemos hablar de contadores sncronos (todos los biestables conmutan a la vez, con una seal de reloj comn) o asncronos (el reloj no es comn y los biestables conmutan uno tras otro). Segn el sentido de la cuenta, se distinguen en ascendentes, descendentes y UPDOWN(ascendentes o descendentes segn la seal de control). Segn la cantidad de nmeros que pueden contar, se puede hablar de contadores binarios de n bits (cuentan todos los nmeros posibles de n bits, desde 0 hasta ), contadores BCD (cuentan del 0 al 9) y contadores Mdulo N (cuentan desde el 0 hasta el N-cuarto. El nmero mximo de estados por los que pasa un contador se denomina mdulo del contador. Este nmero viene determinado por la expresin donde n indica el nmero de bits del contador. Ejemplo, un contador de mdulo 4 pasa por 4 estados, y contara del 0 al 3. Si necesitamos un contador con un mdulo distinto de , lo que se hace es aadir un circuito combinacional. 2.1.Contadores sncronos El termino sncrono se refiere a los eventos que tienen una relacin temporal fija entre si, de manera que todos los biestables cambian de estado simultneamente; para que el contador en estas condiciones realice una secuencia prestablecida, es necesario que las entradas sncronas de los biestables incluyan una lgica combinacional en funcin de las salidas de los biestables para generar las entradas de excitacin adecuadas. Se detalla este tipo de contadores ya que son de inters para el presenta laboratorio, porque en esta oportunidad se desea disear contadores sncronos ascendentes y descendentes. 2.2.Pasos a seguir para el diseo de contadores Los contadores son un caso particular de los circuitos secuenciales sncronos. Se aplicar el procedimiento de diseo de los circuitos secuenciales a los contadores sncronos identificando con el mtodo los pasos a seguir.

a) Especificaciones del contador. Generalmente se trata de una descripcin (en lenguaje natural no ambiguo o al menos eso se espera) de la secuencia que debe seguir el contador, en este caso la interpretacin del enunciado se realiza a travs de un diagrama de flujo entre los estados internos que representan la secuencia de evolucin del contador y este diagrama llega a ser nico y reducido, la evolucin de un estado (nodo del diagrama) a otro se realiza mediante la seal de reloj indicado con una lnea que parte de un estado y termina en otro, sealando el sentido en esta lnea con una flecha. b) Tabla de fases tabla de estados. En el diseo del contador no es necesario realizar esta tabla de fases puesto que se tiene de la interpretacin el diagrama de flujo. c) Reducir el nmero de estados internos. Como no se realiza la tabla de fases tabla de estados tampoco es necesario realizar este pas puesto que el diagrama de flujo de la interpretacin es nico y reducido. d) Tabla de fases reducida. De la interpretacin del enunciado se obtiene el diagrama de flujo del contador y que es nico y reducido, en esta tabla de fases se muestra el estado de partida ajustado con las entradas asncronas sncronas de los FF, se debe detallar la seal de control que determina si el contador es ascendente o descendente la secuencia de evolucin con la seal de reloj. Los estados del contador se indican con un crculo y en su interior se anota el nombre del estado, para la evolucin entre cada estado se indica con una lnea que parte de un estado y termina en otro sealando con una flecha el sentido de conmutacin, sobre esta lnea se anota el estado del reloj. Cabe aclarar que si el contador es de un solo sentido es decir ascendente o descendente no es necesario disponer de una seal de control ya que la seal de reloj realiza la secuencia requerida. e) Codificacin de los estados internos. En un contador est determinado el nmero mximo de la cuenta a realizar y este coincide con el nmero de estados del diagrama de flujo, este nmero debe ser menor o igual que , donde n es el nmero de bits que se usar en la codificacin de cada uno de los estados; slo resta adoptar el cdigo binario en que se realiza la cuenta y este puede ser cualquiera, en este punto tambin se puede adoptar el tipo de FF a ser utilizado es un dato del problema, asimismo de la relacin de 2", n representa el nmero de biestables que permite realizar la cuenta. Con el cdigo adoptado realizamos la tabla de fases reducida y codificada. f) Diagramas de Karnaugh. Para realizar los diagramas de Karnaugh previamente debemos decidir si la sntesis se efecta utilizando las tablas de excitacin previa las ecuaciones fundamentales de los FF, de tal manera que: Si adoptamos el mtodo de las tablas de excitacin previa se debe realizar esta tabla para cada secuencia del contador, tomando en cuenta que el cdigo adoptado en cada estado representa la salida de cada FF que participa en el circuito, realizada la tabla de excitacin para cada estado de la tabla de fases reducida y codificada, se procede a vaciar las tablas de excitacin as determinadas en un diagrama de. Karnaugh para cada una de las entradas sncronas del FF adoptado, en l diagrama de Karnaugh para cada cubculo se toma como variables lgicas las salidas de los FF. De estos diagramas se determinan las funciones lgicas que controlan cada entrada de informacin sncrona de los FF. Si adoptamos el mtodo de la ecuacin fundamental de los FF, a partir de la tabla de fases reducida y codificada vaciamos los estados de la tabla en diagramas de Karnaugh para cada una de las columnas de la tabla, tomando como variables en ste diagrama las salidas de los FF. De estos diagramas determinamos las ecuaciones lgicas mediante un proceso de comparacin de estas ecuaciones con las ecuaciones fundamentales de los FF, se determina las funciones lgicas de cada una de las entradas sncronas de los FF que forman el contador. g) Circuito Lgico.

De las ecuaciones lgicas de control de las entradas sncronas determinada; en el paso anterior, adoptados los operadores combinacionales y secuenciales se procede a dibujar el circuito resultante, luego verificamos el trabajo lgico del contador. 3. Descripcin de los componentes 3.1.Flip flop 74LS76 (flip flop JK) El 74LS76A ofrece pulsos de reloj individuales J, K, la configuracin directa y dirigir contribuyan de forma clara. Estos dos flip-flops estn diseados de manera que cuando el pulso de reloj es alto, las entradas estn habilitadas y los datos sern aceptados. El nivel lgico de las entradas J y K llevar a cabo de acuerdo con el Tabla de verdad, siempre y cuando mnimo los tiempos de preparacin se observan. Los datos de entrada se transfieren a las salidas en las transiciones de reloj de alta-baja. Deshacer cambios

En teora se usa un flip fliop T que tiene una tabla de excitacin propia, sin embargo, se utilizara el flip flop JK para implementar el circuito contador con la modificacin de cortocircuitar los pines correspondientes a las entradas J y K para ambos biestables y asi obtener un flip flop T. 3.2.Compuertas en general Se utilizan compuertas AND, OR, NOT, XOR y otras dependiendo a las necesidades del caso. Tratndose de las compuertas AND pueden ser de dos entradas, de tres entradas y de cuatro entradas dependiendo del nmero de factores que intervengan en la operacin, de acuerdo con ello los cdigos de fabricacin son 74LS08, 74LS11 y 74LS21 respectivamente. 4. Especificaciones y diseo del contador 4.1. Especificaciones Debe ser un contador sncrono de modulo 8 (contador de 0 a 7) utilizando biestables del tipo T; para codificar los estados se usa el cdigo binario ordinario. Adems se requiere que el contador tenga dos seales de control externas que cumplan las siguientes cuatro secuencias dependiendo del valor de la seal externa. Si

7

1 5

Contador descendente que cuente de 2 en 2 (nmeros impares) Como la cuenta se ejecuta desde 0 hasta 7 entonces si se cuentan solo nmeros pares la secuencia es la mostrada en el diagrama de estado mostrado a la izquierda.

Para los estados no deseados de dispone arbitrariamente que inicien la cuenta en 7; los posibles estados no deseados son 0, 2, 4 y 6, tomando en cuenta que es un contador que solo va a manejar 3 bits para realizar el trabajo. Si 7 0 1 2 3 Si 0 6 2 Contador ascendente que cuente de 2 en 2 (nmeros pares) Como la cuenta se ejecuta desde 0 hasta 7 entonces si se cuentan solo nmeros pares la secuencia es la mostrada en el diagrama de estado mostrado a la izquierda. Para los estados no deseados de dispone arbitrariamente que inicien la cuenta en 0; los posibles estados no deseados son 1, 3, 5 y 7, tomando en cuenta que es un contador que solo va a manejar 3 bits para realizar el trabajo. 4 6 5 Contador descendente que cuente de 1 en 1 (cuenta descendente normal) Como la cuenta se ejecuta desde 0 hasta 7 entonces si se cuenta de manera descendente la secuencia es igual a la mostrada en el diagrama de la izquierda. No hay estados no deseados que se puedan dar.

4 Si 0 7 6 5 4 3 1 2

Contador ascendente que cuente de 1 en 1 (cuenta ascendente normal) Como la cuenta se ejecuta desde 0 hasta 7 entonces si se cuenta de manera ascendente la secuencia es igual a la mostrada en el diagrama de la izquierda No hay estados no deseados que se puedan dar.

4.2.Diseo del contador El diagrama de estados esta en la parte superior donde se especifican los requerimientos del contador para cada caso. Se procede a hacer una tabla de verdad que verifique los estados anteriores y posteriores por los que el contador debe pasar y se elabora las entradas para el flip flop T.

4.2.1. Diseo contador descendente de uno en uno ( Estado previo Estado actual Decimal 0 1 2 3 4 5 6 7 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 1 1 1 0 1 0 1 1 1 1 1 0 1 1 1 0 1 1 1 1 1 1 1 1

) Entrada Flip Flop T 1 1 1 0 0 1 0 0 1 1 0 1 1 1 0 1 1 0 1 0 1 0 1 0

4.1.2. Diseo contador descendente de nmeros impares ( Estado previo Estado actual Decimal 0 1 2 3 4 5 6 7 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0

) Entrada Flip Flop T 1 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 1 1 1 1 1 1

) 4.2.3. Diseo contador ascendente de dos en dos de nmeros pares ( Estado previo Estado actual Entrada Flip Flop T Decimal 0 1 2 3 4 5 6 7 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 1 0 1 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 ) Entrada Flip Flop T 1 0 1 0 1 0 1 0 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 1 1 1 1 1 1 1 0 0 1 0 0 1 1 1 1 0 1 1 1 0 1 1 0 1 0 1 0 1 0 1

4.2.4. Diseo contador ascendente de uno en uno ( Estado previo Estado actual Decimal 0 1 2 3 4 5 6 7 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0

4.3. Simplificacin por mapas de Karnaugh La simplificacin por mapas de Karnaugh se hace para llegar a la expresin mas reducida con el fin de emplear un nmero menor de componentes, ganar ms espacio y hacer ms fcil la implementacin del circuito diseado Se simplifica la funcin correspondiente a la entrada del Flip Flop T, para el presente circuito se simplifican las tres entradas, correspondientes al nmero de bits que maneja el circuito. 4.3.1. Entrada para 00 0 1 4.3.2. Entrada para 00 0 1 4.3.2. Entrada para 00 0 1 4.4. Funciones de entrada Con ayuda de los mapas de Karnaugh se obtienen las funciones simplificadas de las tres diferentes entradas. ( ) ) ( ( ) ( ) 1 0 0 0 1 0 1 0 1 0 1 1 01 0 0 0 0 0 0 0 1 11 0 1 0 1 1 1 0 1 10 0 0 0 0 1 1 1 1 1 0 1 0 1 0 1 0 01 0 1 0 1 1 1 1 1 11 0 1 0 1 0 1 0 1 10 1 0 1 0 1 0 1 0 1 1 1 1 0 1 0 1 01 1 1 1 1 0 1 0 1 11 1 1 1 1 1 0 1 0 10 1 1 1 1

Las funciones obtenidas todava pueden simplificarse ms mediante el Algebra de Boole, entonces se tiene: ( ( ( ) ( ) ) ( ) ) ( ( ) ( ) ) ( )

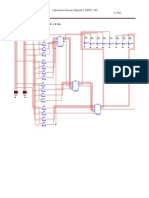

Con las funciones simplificadas se implementa el circuito en el programa simulador PROTEUS versin 7, en el cual se prueba si el circuito funciona como se desea antes de armarlo fsicamente.

La simulacin del circuito funciona de la manera pedida. Se remplazaron las funciones por compuertas lgicas TTL y CMOS que cumplen las tablas de verdad requeridas. El circuito se simplifico a su mnima expresin, de las funciones simplificadas se observa que algunas e estas se repiten varias veces por lo tanto solo basta con tomar la seal y colocarla donde corresponda, para lograr la secuencia buscada. Se emplearon las siguientes compuertas lgicas digitales:

Donde la compuerta XNOR o NOR exclusiva es una puerta lgica digital. Cuando todas sus entradas son iguales entre s para dos entradas A y B, o cuando el nmero de 1 (unos) da una cantidad par para el caso de tres o ms entradas, su salida est en 1 o en ALTA. Se puede ver claramente que la salida X solamente es "1" (1 lgico, nivel alto) cuando la entrada A es igual a la B. Esta situacin se representa en lgebra booleana como: La representacin circuital es con pulsadores normales cerrados y abiertos, conectados en un circuito combinado. En lgica, corresponde a la bicondicional "si y slo si". Por ejemplo: "Matas va a aprobar Tecnologa de las Computadoras si y slo si estudia mucho". Las puertas Lgicas XNOR se fabrican de dos entradas. Cdigos de los fabricantes de Circuitos Integrados para la compuerta EXNOR: Tecnologa TTL 74HC7266 Tecnologa CMOS 4077 5. Observaciones

El circuito mostrado en simulacin funciona adecuadamente de acuerdo a los requerimientos iniciales, se debe tener cuidado a la hora de hacer las conexiones ya que es un circuito donde intervienen muchas compuertas. 6. Conclusiones

El circuito simulado en computadora y el circuito implementado de forma fsica funcionan de acuerdo a los requerimientos iniciales, por lo tanto, se demuestra la validez del procedimiento de diseo de contadores y se muestra una clara aplicacin del mismo, ya que puede obedecer a la secuencia requerida para cada combinacin de seales externas.

También podría gustarte

- Calibracion Motor CumminsDocumento6 páginasCalibracion Motor CumminsAlfredo Diaz80% (20)

- Dominantes SecundariasDocumento2 páginasDominantes SecundariasOmar GarcíaAún no hay calificaciones

- Estandar PrefecturaDocumento18 páginasEstandar PrefecturaOmar GarcíaAún no hay calificaciones

- La Noche TerribleDocumento2 páginasLa Noche TerribleOmar GarcíaAún no hay calificaciones

- Estandar NrecaDocumento139 páginasEstandar NrecaOmar García100% (3)

- Receta de Jovialidad (Pablo Picasso y Mercedes Sosa)Documento14 páginasReceta de Jovialidad (Pablo Picasso y Mercedes Sosa)R 8aAún no hay calificaciones

- Circuito Multiplicador Binario 4Documento1 páginaCircuito Multiplicador Binario 4Omar GarcíaAún no hay calificaciones

- Control de Riego Inteligente Con El Pic 12f675Documento4 páginasControl de Riego Inteligente Con El Pic 12f675Omar GarcíaAún no hay calificaciones

- Uniones AtornilladasDocumento92 páginasUniones Atornilladasnedduc20Aún no hay calificaciones

- Historia de Un NumeroDocumento3 páginasHistoria de Un NumeroOmar GarcíaAún no hay calificaciones

- El Hombrecito Vestido de GrisDocumento3 páginasEl Hombrecito Vestido de GrisOmar GarcíaAún no hay calificaciones

- Ejercicios Basico Windows 7Documento2 páginasEjercicios Basico Windows 7Tabata VasquezAún no hay calificaciones

- Tareas de La Breve Historia de La GraficaciónDocumento3 páginasTareas de La Breve Historia de La GraficaciónDENIS OMAR CUYO TTITOAún no hay calificaciones

- Programación 11º 2014Documento40 páginasProgramación 11º 2014marlenAún no hay calificaciones

- Examen Final - Semana 8 Distribución PlantasDocumento6 páginasExamen Final - Semana 8 Distribución Plantaslinda12345678912345650% (4)

- Manual de SEGURIDAD en ISSABEL de Telefonía IPDocumento19 páginasManual de SEGURIDAD en ISSABEL de Telefonía IPJuan Michael Davila GalindoAún no hay calificaciones

- Diseño Del Sistema Motriz para Un Vehículo EléctricoDocumento15 páginasDiseño Del Sistema Motriz para Un Vehículo Eléctricoandre leonardo aguilar hilarioAún no hay calificaciones

- Ponderaciones Uclm Lomce v03Documento1 páginaPonderaciones Uclm Lomce v03api-286070736Aún no hay calificaciones

- Foto ControlDocumento6 páginasFoto ControlFredy Mantilla RoldanAún no hay calificaciones

- 10 Convertidores CD CD 1Documento22 páginas10 Convertidores CD CD 1Fernanda Araya SotoAún no hay calificaciones

- LOF-1806 Gestion Del Transporte MultimodalDocumento10 páginasLOF-1806 Gestion Del Transporte MultimodalAzucena Perez RamosAún no hay calificaciones

- Formación Profesional Dual: Servicio Nacional de Adiestramiento en Trabajo IndustrialDocumento14 páginasFormación Profesional Dual: Servicio Nacional de Adiestramiento en Trabajo Industrialwhitman Gonzales ValdezAún no hay calificaciones

- AP09 AA10 EV02 Diseno Ejecucion Ppruebas SIDocumento3 páginasAP09 AA10 EV02 Diseno Ejecucion Ppruebas SIAlfred Salsa BorinquenAún no hay calificaciones

- Mediciones e Instrumentacion IndustrialDocumento64 páginasMediciones e Instrumentacion IndustrialJose CastañedaAún no hay calificaciones

- Presentación Empresa-2Documento12 páginasPresentación Empresa-2Gabriela LucenaAún no hay calificaciones

- Balance en HornosDocumento131 páginasBalance en HornosstefhanyAún no hay calificaciones

- Seguridad Por NivelesDocumento709 páginasSeguridad Por NivelespuchuxAún no hay calificaciones

- Actividad 1 - Uso de La Tecnología para El Apoyo de La Enseñanza en Audición y LenguajeDocumento3 páginasActividad 1 - Uso de La Tecnología para El Apoyo de La Enseñanza en Audición y LenguajecesevernoteAún no hay calificaciones

- QuimicaDocumento8 páginasQuimicaCaleb MárquezAún no hay calificaciones

- 04 Apu-Instalaciones ElectricasDocumento23 páginas04 Apu-Instalaciones ElectricaswaldyAún no hay calificaciones

- Confiabilidad Operacional-Gassan PDFDocumento21 páginasConfiabilidad Operacional-Gassan PDFybrahimjAún no hay calificaciones

- Caso 10 AppleDocumento24 páginasCaso 10 Applelawroti31Aún no hay calificaciones

- Huella EcológicaDocumento4 páginasHuella EcológicaDaniel HernándezAún no hay calificaciones

- APOLO Weight Digital Indicator Inst. and Use Manual - 4 - 0Documento53 páginasAPOLO Weight Digital Indicator Inst. and Use Manual - 4 - 0scribd_guirreAún no hay calificaciones

- Nanotecnología Aplicada en La Minería IbaDocumento11 páginasNanotecnología Aplicada en La Minería IbaLuis Alberto ParaguezAún no hay calificaciones

- Robotica EducativaDocumento4 páginasRobotica EducativaJessica Leandra Velasco PérezAún no hay calificaciones

- Larry Yate - Paso 6 IndividualDocumento11 páginasLarry Yate - Paso 6 IndividualLarry Bryan Wilson100% (1)

- Diseño de EnsacadorasDocumento10 páginasDiseño de EnsacadorasYuri OrellanoAún no hay calificaciones

- Pestaña Diseño de Pagina Informatica 2021Documento5 páginasPestaña Diseño de Pagina Informatica 2021Nicoll SarabiaAún no hay calificaciones

- Practica 1 Control Scr-UjtDocumento3 páginasPractica 1 Control Scr-UjtJonatan Eduardo Rodriguez ZavalaAún no hay calificaciones