Documentos de Académico

Documentos de Profesional

Documentos de Cultura

23 1 Multiplicadoresdivisores

23 1 Multiplicadoresdivisores

Cargado por

poolxmTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

23 1 Multiplicadoresdivisores

23 1 Multiplicadoresdivisores

Cargado por

poolxmCopyright:

Formatos disponibles

Universidad Rey Juan Carlos

ESTRUCTURA Y TECNOLOGA DE COMPUTADORES

Circuitos para multiplicacin y divisin de nmeros en coma fija

Luis Rincn Crcoles Licesio J. Rodrguez-Aragn

Circuitos para multiplicacin y divisin de nmeros en coma fija

Programa

1. 2. 3. 4. 5. 6. 7. 8. 9. Bibliografa. Multiplicacin binaria en coma fija. Multiplicacin por una constante. Multiplicacin por suma - desplazamiento. Multiplicacin por grupos solapados. Circuitos para multiplicacin rpida. Divisin binaria en coma fija. Divisin por una constante. Divisin con restauracin. Instrucciones para multiplicacin y divisin en ensamblador.

Circuitos para multiplicacin y divisin de nmeros en coma fija

Bibliografa

D.A. PATTERSON, J.L. HENNESSY. Estructura y Diseo de Computadores. Revert, 2000. DORMIDO, S. CANTO M.A., MIRA J., DELGADO A.E. Estructura y Tecnologa de Computadores. 2 edicin. Sanz y Torres, 2000. PARHAMI, B. Computer Arithmetic. Oxford University Press, 2000. P. DE MIGUEL. Fundamentos de los Computadores. 7 edicin. Paraninfo, 1999. W. STALLINGS. Organizacin y Arquitectura de Computadores. 5 edicin, Prentice Hall, 2000.

Circuitos para multiplicacin y divisin de nmeros en coma fija

1. Multiplicacin binaria en coma fija

La operacin de multiplicacin de nmeros en coma fija no suele estar contemplada directamente por las UAL, sino que se suele realizar mediante circuitos especficos: Construir un circuito multiplicador rpido exige una circuitera compleja, y las UAL slo realizan directamente las operaciones aritmticas y lgicas ms bsicas. La multiplicacin se puede realizar en la UAL mediante una secuencia de sumas y desplazamientos controlados por la unidad de control (UC), si bien no resulta demasiado eficiente. La multiplicacin puede realizarse tambin mediante un programa en ensamblador que conste de un bucle con una secuencia de sumas y desplazamientos, aunque esto es mucho menos eficiente an. Terminologa de la multiplicacin: Mxm=P M: multiplicando. m: multiplicador. P: producto o resultado.

4

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin binaria en coma fija

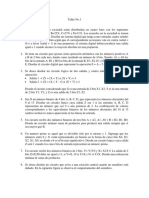

PRODUCTO BINARIO ()

A

0 0 0 1 0 1

12 6 72

1 1 0 0 1 1 0 0 0 0 0

multiplicando multiplicador

B

1

1 1 0 0 1 1 0 0 1 0 0 1 0 0 0 64 + 8 M3

Productos parciales resultado

M m R

= 72 M1 m1 M1 m0 M0 m1 R1 R0 M0 m0 M0 m0

multiplicando multiplicador Productos parciales

M3m0 M3m1 M3m2 M2 m2 R4 M2 m1 M1 m2 R3

M2 m2 M2 m0 M1 m1 M0 m2 R2

R6

R5

resultado

5

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin binaria en coma fija

La multiplicacin en coma fija es una secuencia de desplazamientos y sumas con extensin de signo.

Si los operandos estn en binario puro, se rellenan con ceros a la izquierda. Los operandos en complemento a 2 se rellenan a su izquierda con el bit de signo. En cualquier caso, a la derecha se rellena con ceros.

Ejemplo: multiplicar M=101001102=16610 por m=000110012=2510 0000000010100110 + 0000000000000000 + 0000000000000000 + 0000010100110000 + 0000101001100000 + 0000000000000000 + 0000000000000000 + 0000000000000000 0001000000110110 M*m0*20 = M*1: M sin desplazar M*m1*21 = 0 M*m2*22 = 0 M*m3*23 = M*8: M desplazado 3 lugares M*m4*24 = M*16: M desplazado 4 lugares M*m5*25 = 0 M*m6*26 = 0 M*m7*27 = 0 M*m

El producto de dos nmeros binarios de n bits produce un resultado que puede tener hasta 2n bits de ancho. 6

Circuitos para multiplicacin y divisin de nmeros en coma fija

2. Multiplicacin por un valor constante

La multiplicacin es una operacin costosa en tiempo de ejecucin. Por tanto, es aconsejable evitar las multiplicaciones en los programas siempre que sea posible. Si uno de los operandos (por ejemplo el multiplicador) es una constante conocida en tiempo de compilacin (o ensamblaje), es frecuente que el compilador (o ensamblador) sustituya la multiplicacin por otras operaciones. Cuando el multiplicador es una constante potencia de 2, la multiplicacin se puede sustituir por un desplazamiento del multiplicando hacia la izquierda. Si el multiplicador es 2k, se desplazar el multiplicando k lugares a la izquierda.

N = a n-1 2 n-1 + ........ + a 0 2 0

N 2 m = a n-1 2 n-1+m + ........ + a 0 2 0 +m

Ejemplo: 11010012 23 = 11010010002

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin por un valor constante

Cuando el multiplicador es una constante que no es una potencia de 2, la multiplicacin puede descomponerse en una secuencia de instrucciones de desplazamiento y de suma. Ejemplo: multiplicar M=101001102=16610 por m=000110012=2510 Descomponemos el multiplicador m=25=16+8+1. As, la operacin ser M*25 = M*(16+8+1) = M*16+M*8+M que se traduce en dos desplazamientos (de 3 y 4 lugares respectivamente) y dos sumas (consumiramos una variable intermedia). 101001100000 +010100110000 +000010100110 1000000110110 Desplazamiento de M cuatro posiciones Desplazamiento de M tres posiciones M sin desplazar Resultado de la suma (del producto)

8

Circuitos para multiplicacin y divisin de nmeros en coma fija

3. Multiplicacin por suma desplazamiento

Vamos a ver: 1) El algoritmo de lpiz y papel (o de suma-desplazamiento) para multiplicar nmeros en binario puro (sin signo) de n bits. 2) Un circuito que permite realizar la operacin utilizando dicho algoritmo. 3) Una versin optimizada del algoritmo, con el correspondiente circuito. 4) La versin final del algoritmo, an ms optimizada, acompaada del correspondiente circuito. Los circuitos se basan en: Un sumador, que puede ser el de la UAL. Varios registros de desplazamiento. Un circuito secuencial de control, que puede ser parte de la UC.

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin por S D: 1 versin

La multiplicacin ser un proceso iterativo, y en cada ciclo se realizarn las siguientes operaciones:

1. Se realiza el producto del multiplicando por el bit 0 del multiplicador, con lo cual obtendremos productos parciales que pueden valer lo mismo que el multiplicando desplazado (cuando el bit del multiplicador sea 1) o bien 0 (cuando dicho bit sea nulo). 2. Se desplazar el multiplicando un lugar hacia la izquierda para alinear correctamente los productos parciales, que estarn convenientemente rellenados con ceros a la izquierda y/o a la derecha (para ello, doblaremos el tamao del multiplicando, e inicialmente lo rellenaremos con ceros a la izquierda). 3. Se desplaza o se rota el multiplicador un lugar hacia la derecha (por esto siempre se multiplica por el bit 0 del multiplicador). 4. Se sumar el producto parcial con la suma acumulada de los productos parciales obtenidos en los pasos anteriores (al principio el producto acumulado ser 0).

10

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin por S D: 1 versin

Circuitera necesaria:

Un registro de 2n bits capaz de realizar desplazamientos unitarios hacia la izquierda para el multiplicando. Un registro de n bits capaz de realizar desplazamientos unitarios hacia la derecha para el multiplicador. Un registro de 2n bits para el producto. Un contador de 0 a n para contar el nmero de iteraciones. Un sumador de 2n bits. Un controlador para generar la secuencia de seales necesaria.

Multiplicand Shift left 64 bits

Circuito para n = 32 bits con las conexiones y seales de control necesarias.

64-bit ALU

Multiplier Shift right 32 bits

Product Write 64 bits

Control test

11

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin por S D: 1 versin

Inicio

Operaciones de la fase de inicio: 1. Iniciar el registro Multiplicando (mitad superior con todos los bits a 0, mitad inferior con el multiplicando) 2. Iniciar el registro Multiplicador 3. Producto 0 4. Contador 0

Multiplicand Shift left 64 bits

Producto Producto + Multiplicando

Bit 0 del Multiplicador = 0?

0

Desplazamiento del registro Multiplicando a la izquierda

No

Desplazamiento del registro Multiplicador a la derecha

Contador Contador+1

64-bit ALU Multiplier Shift right 32 bits

Contador = n ?

Product Write Control test

64 bits

Fin

Ejercicio: dibujar el diagrama de estados del controlador del circuito.

12

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin por S D: 1 versin

Ejemplo: n=4, multiplicar M=10102=1010 por m=00112=310

Iteracin 0 1 Paso Valores iniciales Producto Producto + Multiplicando Desplazar Multiplicando a la izqda. Desplazar Multiplicador a la derecha 2 Producto Producto + Multiplicando Desplazar Multiplicando a la izqda. Desplazar Multiplicador a la derecha 3 Ninguna operacin Desplazar Multiplicando a la izqda. Desplazar Multiplicador a la derecha 4 Ninguna operacin Desplazar Multiplicando a la izqda. Desplazar Multiplicador a la derecha Multiplicador 0011 0001 0000 0000 0000 Multiplicando 0000 1010 0001 0100 0010 1000 0101 0000 1010 0000 Producto 0000 0000 0000 1010 0001 1110 0001 1110

13

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin por S D: 2 versin

En el circuito anterior sucede que: La mitad de los bits del registro Multiplicando siempre son 0, con lo cual slo la mitad contiene datos tiles. Tambin sobra la mitad de la UAL, pues est sumando en cada paso el doble de datos de lo estrictamente necesario. Por tanto, se ide un algoritmo similar al anterior, pero sin duplicar el tamao del multiplicador, y utilizando un sumador de n bits. Puesto que las sumas son de n bits, el registro Producto estar dividido en dos mitades (Productoizq: mitad izquierda; Productoder: mitad derecha; P: registro completo). En cada iteracin se suma slo sobre la mitad izquierda. Los desplazamientos se realizan sobre el registro completo. Deja de ser necesario desplazar el registro Multiplicando. Sigue siendo preciso desplazar el registro Multiplicador para consultar siempre su bit 0.

14

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin por S D: 2 versin

Circuitera necesaria:

Un registro de n bits para el multiplicando. Un registro de n bits capaz de realizar desplazamientos lgicos unitarios hacia la derecha para el multiplicador. Un sumador de n bits. Un biestable para guardar el acarreo de las sumas (no aparece en el dibujo). Un registro de 2n bits para el producto, que pueda cargarse en paralelo en su mitad izquierda dejando intacta la mitad derecha; este registro admitir desplazamientos lgicos unitarios hacia la derecha del registro completo concatenando el biestable de acarreo por la izquierda. Un contador de 0 a n para contar el nmero de iteraciones. Un controlador para generar la secuencia de seales necesaria.

Multiplicand

Circuito para n = 32 bits con las conexiones y seales de control necesarias.

32 bits

32-bit ALU

Multiplier Shift right 32 bits Product 64 bits Shift right Write Control test

15

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin por S D: 2 versin

Inicio

Operaciones de la fase de inicio: 1. Iniciar el registro Multiplicando

Productoizq Productoizq + Multiplicando

Bit 0 del Multiplicador = 0?

0

2. Iniciar el registro Multiplicador 3. Producto 0 4. Contador 0

Multiplicand 32 bits

Desplazamiento del registro Producto a la derecha

No

Desplazamiento del registro Multiplicador a la derecha

Contador Contador+1

Multiplier Shift right 32 bits Product Shift right Write Control test

32-bit ALU

Contador = n ?

S

Fin

64 bits

Ejercicio: dibujar el diagrama de estados del controlador del circuito.

16

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin por S D: 2 versin

Ejemplo: n=4, multiplicar M=10102=1010 por m=00112=310

Iteracin 0 1 Valores iniciales Productoizq Productoizq + Multiplicando Desplazar Producto a la derecha Desplazar Multiplicador a la derecha 2 Productoizq Productoizq + Multiplicando Desplazar Producto a la derecha Desplazar Multiplicador a la derecha 3 Ninguna operacin Desplazar Producto a la derecha Desplazar Multiplicador a la derecha 4 Ninguna operacin Desplazar Producto a la derecha Desplazar Multiplicador a la derecha Paso Multiplicador 0011 0001 0000 0000 0000 Multiplicando 1010 Producto 0 0000 0000 0 1010 0000 0 0101 0000 0 1111 0000 0 0111 1000 0 0011 1100 0 0001 1110 0001 1110

17

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin por S D: 3 versin

En el circuito anterior sucede que: Al principio, el registro Producto tiene la mitad de sus bits desperdiciados. A medida que van realizndose pasos del algoritmo, el espacio desaprovechado del registro Producto se va reduciendo. Los bits del multiplicador van dejando de ser tiles a medida que se van realizando los productos parciales (en realidad se van perdiendo si hacemos desplazamientos sobre el registro Multiplicador y no rotaciones). El espacio desaprovechado del registro Producto es exactamente igual que el nmero de bits del multiplicador que necesitamos mantener en cada instante. Por tanto, se incorpor una mejora al circuito, de forma que el registro Multiplicador desaparece, y el multiplicador se carga inicialmente en la mitad derecha del registro Producto. En cada iteracin, cuando vayamos a consultar un bit del multiplicador, consultaremos el bit menos significativo del registro Producto.

18

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin por S D: 3 versin

Circuitera necesaria:

Un registro de n bits para el multiplicando. Un sumador de n bits. Un biestable para guardar el acarreo de las sumas (no aparece en el dibujo). Un registro de 2n bits para el producto, que pueda cargarse en paralelo en su mitad izquierda dejando intacta la mitad derecha, o cargarse en paralelo en su mitad derecha dejando intacta su mitad izquierda; este registro admitir desplazamientos lgicos unitarios hacia la derecha del registro completo concatenando el biestable de acarreo por la izquierda. Un contador de 0 a n para contar el nmero de iteraciones. Un controlador para generar la secuencia de seales necesaria.

Multiplicand 32 bits

Circuito para n = 32 bits con las conexiones y seales de control necesarias.

32-bit ALU

Product 64 bits

Shift right Write

Control test

19

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin por S D: 3 versin

Operaciones de la fase de inicio:

Inicio

Productoizq Productoizq + Multiplicando

No

Bit 0 del Producto = 0?

0

1. Iniciar el registro Multiplicando 2. Iniciar el registro Producto (mitad izquierda a 0, mitad derecha con el multiplicador) 3. Contador 0

Multiplicand 32 bits

Desplazamiento del registro Producto a la derecha

Contador Contador+1

32-bit ALU

Contador = n ?

S

Product 64 bits

Shift right Write

Control test

Fin

Ejercicio: dibujar el diagrama de estados del controlador del circuito.

20

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin por S D: 3 versin

Ejemplo: n=4, multiplicar M=10102=1010 por m=00112=310

Iteracin 0 1 Valores iniciales Productoizq Productoizq + Multiplicando Desplazar Producto a la derecha 2 Productoizq Productoizq + Multiplicando Desplazar Producto a la derecha 3 Ninguna operacin Desplazar Producto a la derecha 4 Ninguna operacin Desplazar Producto a la derecha Paso Multiplicando 1010 Producto 0 0000 0011 0 1010 0011 0 0101 0001 0 1111 0001 0 0111 1000 0 0011 1100 0001 1110

Los nmeros utilizados estn en binario puro. El algoritmo se puede adaptar a nmeros en complemento a 2.

Con multiplicador negativo en la ltima iteracin hay que restar en vez de sumar.

21

Circuitos para multiplicacin y divisin de nmeros en coma fija

Multiplicacin por S D: ruta de datos 3 versin

Ini

Clr TC CE

CONTROLADOR

INICIO

Fin Cuenta

Contador 0-3

Desplaza Carga BitZ0

A3 A2 A1 A0

Multiplicando

Sumador de 4 bits

B3 B2 B1 B0

Clr

Reloj

D CE

Clr

Producto

L S

Multiplicador

L S

Z7 Z6 Z5 Z4

Z3 Z2 Z1 Z0

22

Circuitos para multiplicacin y divisin de nmeros en coma fija

4. Multiplicacin por grupos solapados

El algoritmo de lpiz y papel (o suma desplazamiento) considera los bits del multiplicador uno a uno, y va generando productos parciales que va sumando y acumulando. Los algoritmos de multiplicacin por grupos solapados (G-S) generan productos parciales considerando los bits del multiplicador por grupos. Los algoritmos de multiplicacin por G-S analizan una ventana o grupo de n bits del multiplicador en cada iteracin. En funcin de los bits de la ventana, se generan uno o varios productos parciales. De cara a la siguiente iteracin, la ventana de bits analizados se desplaza un lugar hacia la derecha (las ventanas o grupos de bits del multiplicador se solapan en las sucesivas interaciones). El caso de G-S ms sencillo es el algoritmo de Booth, que considera grupos solapados de 2 bits en el multiplicador para generar los productos parciales.

23

Circuitos para multiplicacin y divisin de nmeros en coma fija

Algoritmo de Booth

El algoritmo de Booth presentado funciona para operandos en complemento a 2 (para binario puro habra que realizar una pequea adaptacin). En un nmero binario, una cadena de bits a 1 equivale a una diferencia de dos potencias de 2 (es una suma de elementos de una progresin geomtrica de razn 2). k k-1 j+1 j ... 0 1 1 ... 1 1 0 ... = 2k+1-2j El algoritmo analiza los bits del multiplicador 2 a 2 de derecha a izquierda:

Si detecta que est al final de una cadena de bits a 1 resta la mitad izquierda del registro producto menos el multiplicando Si detecta que est al principio de una cadena de bits a 1 suma la mitad izquierda del registro producto ms el multiplicando. Multiplicadori Multiplicadori-1 Operacin 0 0 1 1 0 1 0 1 Nada (en medio de cadena de ceros) Sumar (inicio de cadena de unos) Restar (final de cadena de unos) Nada (en medio de cadena de unos)

24

Circuitos para multiplicacin y divisin de nmeros en coma fija

Algoritmo de Booth

En definitiva, el algoritmo de Booth se basa en recodificar el multiplicador y convertirlo en una secuencia de dgitos con valores 1, 0 y 1 (codificacin de dgitos con signo).

1 cuando comienza cadena de bits a 1 (implica hacer una suma). -1 cuando termina cadena de bits a 1 (implica hacer una resta). 0 en otro caso.

Ejemplo: recodificacin del nmero 01001110C2

Nmero original Nmero recodificado 0 1 1 -1 0 0 0 1 1 0 1 0 1 -1 0 0

Ejemplo: recodificacin del nmero 11100011C2

Nmero original Nmero recodificado 1 0 1 1 0 0 0 0 0 1 1 0 1 -1 0 -1

Los nmeros en binario puro se recodifican aadiendo un bit a 0 a la izquierda del todo (ejercicio: probarlo). 25

Circuitos para multiplicacin y divisin de nmeros en coma fija

Algoritmo de Booth

Ejemplo: multiplicar M=10100110C2=-9010 por m=00011001C2=2510 Recodificamos el multiplicador y realizamos la operacin:

Multiplicador original Multiplicador recodificado 0 0 0 0 0 1 1 0 1 0 0 1 1 -1

-1 0

0000000001011010 + 1111111101001100 + 0000000000000000 + 0000001011010000 + 0000000000000000 + 1111010011000000 + 0000000000000000 + 0000000000000000 1111011100110110

M*m0*(-20) = -1*M M*m1*21 = 2*M M*m2*22 = 0 M*m3*(-23) = -8*M M*m4*24 = 0 M*m5*25 = 32*M M*m6*26 = 0 M*m7*27 = 0 M*m

26

Circuitos para multiplicacin y divisin de nmeros en coma fija

Algoritmo de Booth

Podra emplearse la circuitera del algoritmo de suma-desplazamiento con algunas pequeas modificaciones (se parte de la versin 3):

Utilizar un sumador-restador. Despreciar el bit de acarreo superior, ya que se manejan datos en complemento a 2. Realizar desplazamientos aritmticos (extendiendo el signo). Aadir un bit que se concatenar a la derecha del registro Producto, iniciado con un 0 y que se modificar cada vez que se haga un desplazamiento sobre Producto (la ventana de bits analizada en cada iteracin est formada por el bit menos significativo del registro Producto y el bit aadido a su derecha).

Multiplicand 32 bits

32-bit ALU

Product 64 bits

Shift right Write

Control test

27

Circuitos para multiplicacin y divisin de nmeros en coma fija

Algoritmo de Booth

Inicio

Multiplicand 32 bits

32-bit ALU

10

p0p-1 ?

00 11

01

Product 64 bits

Shift right Write

Control test

Productoizq Productoizq Multiplicando

No

Productoizq Productoizq + Multiplicando

Desplazar Producto # p-1 a la derecha

Operaciones de la fase de inicio: 1. Iniciar el registro Multiplicando 2. Iniciar el registro Producto (mitad izquierda a 0, mitad derecha con el multiplicador, bit p-1 a 0) 3. Contador 0 Ejercicio: dibujar el diagrama de estados del controlador del circuito. 28

Contador Contador+1

Contador = 0 ?

S

Fin

Aclaraciones: p0: bit menos significativo del registro Producto. p-1: bit aadido a la derecha del registro Producto. Producto # p-1: registro Producto concatenado con el bit p-1.

Circuitos para multiplicacin y divisin de nmeros en coma fija

Algoritmo de Booth

Ejemplo: n=4, multiplicar M=1010C2= -610 por m=0011C2=310 El multiplicando cambiado de signo es M=0110C2

Iteracin 0 1 Valores iniciales Productoizq Productoizq - Multiplicando Desplazar Producto a la derecha 2 Ninguna operacin Desplazar Producto a la derecha 3 Productoizq Productoizq + Multiplicando Desplazar Producto a la derecha 4 Ninguna operacin Desplazar Producto a la derecha Paso Multiplicando 1010 Producto 0000 0011 0 0110 0011 0 0011 0001 1 0001 1000 1 1011 1000 1 1101 1100 0 1110 1110

Los nmeros utilizados estn en complemento a 2. El algoritmo se puede adaptar a nmeros en binario puro.

Si el multiplicador comienza por 1, realizar un ajuste final sumando el multiplicador a la mitad izquierda del registro Producto. 29

Circuitos para multiplicacin y divisin de nmeros en coma fija

5. Circuitos para multiplicacin rpida

En vez de ejecutar la multiplicacin a travs de un proceso iterativo de sumas y desplazamientos regulado por un controlador secuencial, el producto se puede realizar a partir de un sumador de mltiples sumandos (los productos parciales) convenientemente organizados. Para construir multiplicadores de altas velocidades caben dos posibilidades: Sumar los productos parciales rpidamente. Reducir el nmero de productos parciales que hay que sumar. Para sumar los productos parciales ms rpido se puede recurrir por ejemplo a: Las matrices de sumadores. Los sumadores en rbol. Para reducir el nmero de productos parciales se puede recurrir por ejemplo a: Multiplicadores en base mayor que 2 (normalmente en base 4). Recodificacin de Booth utilizando grupos solapados de 3 ms bits. Otra tcnica: guardar todos los posibles resultados en una ROM. La ROM tendra 22n posiciones de 2n bits cada una!

30

Circuitos para multiplicacin y divisin de nmeros en coma fija

Matriz de sumadores con acarreo propagado

Multiplicar consiste en sumar varios productos parciales desplazados. Primer enfoque para multiplicar rpidamente: 1) Calcular los productos parciales mediante puertas AND 2) Sumar dichos productos parciales mediante sumadores tradicionales. Pega: retardo total grande. Para mejorar las prestaciones del circuito, pueden utilizarse otros enfoques: Matriz de CSA. rbol de Wallace. rbol de Dadda. Tambin es posible multiplicar nmeros con signo: Multiplicador de Pezaris. Multiplicador de Baugh-Wooley.

31

Circuitos para multiplicacin y divisin de nmeros en coma fija

6. Divisin binaria en coma fija

La operacin de divisin de nmeros en coma fija no suele estar contemplada directamente por las UAL, sino que se suele realizar mediante circuitos especficos: Construir un circuito divisor rpido es an ms complicado que en el caso del multiplicador. La divisin se puede realizar en la UAL mediante una secuencia de sumas, restas, comparaciones y desplazamientos controlados por la unidad de control (UC), si bien no resulta demasiado eficiente. La divisin puede realizarse tambin mediante un programa en ensamblador que conste de un bucle con una secuencia de sumas, restas, comparaciones y desplazamientos, aunque esto es mucho menos eficiente an. Antes de dividir, los circuitos deben comprobar obligatoriamente si el divisor es igual o distinto de 0 para evitar desbordamientos. Terminologa de la divisin: D: dividendo. d: divisor. C: cociente. R: resto. D/d=C dxC+R=D

32

Circuitos para multiplicacin y divisin de nmeros en coma fija

Divisin binaria en coma fija

Es fcil elegir cada dgito del cociente, ya que slo puede valer 0 1. Si el dividendo parcial es mayor o igual que el divisor, el siguiente dgito del cociente es 1, si no es 0.

112 0

8 14

dividendo

1 1 1 0 1 0 0 0 0 1 1 0 -100 0 1 0 - 10 0 0 - 0 0

0 0 0 0 0 0 0 0 0 0

1 0 0 0 1 1 1 0

divisor cociente

0 0 0 0 0 0 0 0

resto

33

Circuitos para multiplicacin y divisin de nmeros en coma fija

7. Divisin por un valor constante

La divisin es una operacin costosa en tiempo de ejecucin. Por tanto, es aconsejable evitar las multiplicaciones en los programas siempre que sea posible. Si el divisor es una constante conocida en tiempo de compilacin (o ensamblaje), el compilador (o ensamblador) puede sustituir la divisin por otras operaciones. Cuando el divisor es una constante potencia de 2, el cociente de la divisin se puede obtener mediante por un desplazamiento del dividendo hacia la derecha (esto es cierto slo para nmeros en binario puro!). Si el divisor es 2k, el cociente se obtiene desplazando el dividendo k lugares a la derecha. Los bits sobrantes (parte fraccionaria del resultado) constituiran el resto de la divisin entera, convenientemente escalado por 2k.

N = a n-1 2 n-1 + ........ + a 0 2 0

Ejemplo: 11010012 / 23 cociente = 11012, resto = 0012

N = a n-1 2 n-1m + ........ + a 0 2 0 m 2m

Si el divisor es una constante que no es potencia de 2, el clculo es complicado.

34

Circuitos para multiplicacin y divisin de nmeros en coma fija

8. Divisin con restauracin

En primer lugar se presentar un algoritmo bsico para dividir nmeros en binario puro (sin signo) de n bits. A continuacin se presentar un circuito que permite realizar la operacin utilizando dicho algoritmo. Seguidamente se presentar una versin optimizada del algoritmo, con el correspondiente circuito. Se incluir una tercera versin del algoritmo an ms optimizada acompaada del correspondiente circuito. Finalmente se indicarn las modificaciones que ser preciso introducir en los circuitos para poder dividir nmeros con signo. Los circuitos que vamos a ver a continuacin se basan en: Un sumador/restador, que puede ser el de la UAL. Varios registros de desplazamiento. Un circuito secuencial de control, que puede ser parte de la UC.

35

Circuitos para multiplicacin y divisin de nmeros en coma fija

Divisin con restauracin: 1 versin

La divisin se realizar ms o menos igual que como se hace con lpiz y papel. Ser un proceso iterativo de n+1 ciclos, en cada uno de los cuales se realizarn las siguientes operaciones: 1. Se resta el dividendo parcial menos el divisor. Si la resta es positiva seguimos por el paso 2, y si es negativa vamos al paso 3. 2. Resta positiva: el dividendo parcial cabe en el divisor. Por tanto, se aade un 1 al cociente, y se desplaza el mismo un lugar a la derecha. Ir a 4. 3. Resta negativa: el dividendo parcial no cabe en el divisor. Por tanto, se aade un 0 al cociente y se desplaza el mismo un lugar a la derecha. Se restaura el dividendo parcial sumndole el divisor. Ir a 4. 4. Se desplaza el divisor un lugar a la derecha.

36

Circuitos para multiplicacin y divisin de nmeros en coma fija

Divisin con restauracin: 1 versin

Circuitera necesaria:

Un registro de 2n bits que inicialmente contendr el dividendo. Un registro de 2n bits capaz de realizar desplazamientos unitarios hacia la derecha para el divisor. Un registro de n bits capaz de realizar desplazamientos unitarios hacia la izquierda para el cociente. Un contador de 0 a n+1 para contar el nmero de iteraciones. Un sumador / restador de 2n bits. Un controlador para generar la secuencia de seales necesaria.

Divisor Sh ift right 64 bits

Circuito para n = 32 bits con las conexiones y seales de control necesarias.

64-bit ALU

Q uotie nt Sh ift left 32 bits

R em ainder W rite 64 bits

Control test

37

Circuitos para multiplicacin y divisin de nmeros en coma fija

Divisin con restauracin: 1 versin

Inicio

Operaciones de la fase de inicio: 1. Iniciar el registro Resto (mitad superior con todos los bits a 0, mitad inferior con el dividendo). 2. Iniciar el registro Divisor (mitad superior con el divisor, mitad inferior con todos los bits a 0). 3. Cociente 0 4. Contador 0

Divisor Sh ift right 64 bits

Resto Resto-Divisor

No

Resto < 0?

No

Desplazar Cociente 1 bit hacia la izquierda Cociente0 1

Resto Resto+Divisor Desplazar Cociente 1 bit hacia la izquierda Cociente0 0

Desplazar Divisor 1 bit hacia la derecha Contador Contador+1

Contador=n+1?

S

64-bit ALU

Q uotie nt Sh ift left 32 bits

Fin

R em ainder W rite 64 bits

Control test

Ejercicio propuesto: dibujar el diagrama de estados del controlador del circuito.

38

Circuitos para multiplicacin y divisin de nmeros en coma fija

Divisin con restauracin: 1 versin

Ejemplo: n=4, dividir D=10102=1010 por d=00112=310

Iteracin

0 1 Valores iniciales Resto Resto - Divisor Resto<0+Divisor, sll Cociente, Cociente0=0 Desplazar Divisor a la derecha 2 Resto Resto - Divisor Resto<0+Divisor, sll Cociente, Cociente0=0 Desplazar Divisor a la derecha 3 Resto Resto - Divisor Resto<0+Divisor, sll Cociente, Cociente0=0 Desplazar Divisor a la derecha 4 Resto Resto - Divisor Resto0 sll Cociente, Cociente0=1 Desplazar Divisor a la derecha 5 Resto Resto - Divisor Resto0 sll Cociente, Cociente0=1 Desplazar Divisor a la derecha

Paso

Cociente

0000 0000 0001 0000 0000 0001 0011 0011

Divisor

0011 0000 0001 1000 0000 1100 0000 0110 0000 0011 0000 0001

Resto

0000 1010 1101 0000 0000 1010 1111 0010 0000 1010 1111 1110 0000 1010 0000 0100 0000 0001 0000 0001 39

Circuitos para multiplicacin y divisin de nmeros en coma fija

Divisin con restauracin: 2 versin

En el circuito anterior sucede que: La mitad de los bits del divisor no contienen informacin til. Como consecuencia de lo anterior, tambin sobra la mitad de la UAL, pues est sumando y/o restando en cada paso el doble de datos de lo estrictamente necesario. Por tanto, se ide un algoritmo similar al anterior, pero sin duplicar el tamao del divisor, y utilizando un sumador / restador de n bits. Puesto que las sumas y restas son de n bits, el registro Resto estar dividido en dos mitades (Restoizq: mitad izquierda; Restoder: mitad derecha; Resto: registro completo). En cada iteracin se suma y/o resta slo sobre la mitad izquierda. Los desplazamientos se realizan sobre el registro completo. Deja de ser necesario desplazar el registro Divisor. Sigue siendo preciso desplazar el registro Cociente para escribir en su bit 0 el nuevo dgito calculado en cada paso. El resto queda en la mitad izquierda del registro Resto. Nunca puede haber un 1 en el primer dgito del cociente: por consiguiente, pueden reordenarse el desplazamiento y la resta de forma que se elimine una iteracin del algoritmo. 40

Circuitos para multiplicacin y divisin de nmeros en coma fija

Divisin con restauracin: 2 versin

Circuitera necesaria:

Un registro de n bits para el divisor. Un registro de n bits capaz de realizar desplazamientos lgicos unitarios hacia la izquierda para el cociente. Un sumador / restador de n bits. Un registro de 2n bits para el resto, que pueda cargarse en paralelo en una mitad dejando intacta la otra mitad; este registro admitir desplazamientos lgicos unitarios del registro completo hacia la izquierda. Un contador de 0 a n para contar el nmero de iteraciones. Un controlador para generar la secuencia de seales necesaria.

Divisor 32 bits

Circuito para n = 32 bits con las conexiones y seales de control necesarias.

32-bit ALU

Quotient Shift left 32 bits

Remainder 64 bits

Shift left Write

Control test

41

Circuitos para multiplicacin y divisin de nmeros en coma fija

Divisin con restauracin: 2 versin

Inicio Desplazar Resto 1 bit hacia la izquierda

Operaciones de la fase de inicio: 1. Iniciar el registro Divisor 2. Iniciar el registro Resto (mitad inferior con el dividendo, mitad superior con todos sus bits a 0) 3. Cociente 0 4. Contador 0

Divisor 32 bits

Restoizq Restoizq-Divisor

No

Resto < 0?

No

Desplazar Resto 1 bit hacia la izquierda Desplazar Cociente 1 bit hacia la izquierda Cociente0 1

Restoizq Restoizq+Divisor Desplazar Resto 1 bit hacia la izquierda Desplazar Cociente 1 bit hacia la izquierda Cociente0 0

Contador Contador+1

32-bit ALU Quotient Shift left 32 bits Remainder 64 bits Shift left Write Control test

Contador=n?

S

Desplazar Restoizq 1 bit hacia la derecha Fin

Ejercicio propuesto: dibujar el diagrama de estados del controlador del circuito.

42

Circuitos para multiplicacin y divisin de nmeros en coma fija

Divisin con restauracin: 2 versin

Ejemplo: n=4, dividir D=10102=1010 por d=00112=310

Iteracin

0 1 2 3 4 Ajuste final Valores iniciales Desplazar Resto a la izquierda Restoizq Restoizq Divisor Resto<0 +Divisor, sll Resto, sll Cociente, Cociente0=0 Restoizq Restoizq Divisor Resto<0 +Divisor, sll Resto, sll Cociente, Cociente0=0 Restoizq Restoizq Divisor Resto0 sll Resto, sll Cociente, Cociente0=1 Restoizq Restoizq Divisor Resto0 sll Resto, sll Cociente, Cociente0=1 Desplazar Restoizq a la derecha 0011 0011

Paso

Cociente

0000 0000 0000 0001

Divisor

0011

Resto

0000 1010 0001 0100 1110 0100 0010 1000 1111 1000 0101 0000 0010 0000 0100 0000 0001 0000 0010 0000 0001 0000

43

Circuitos para multiplicacin y divisin de nmeros en coma fija

Divisin con restauracin: 3 versin

En el circuito anterior sucede que: Al principio, el registro Resto est completamente ocupado. A medida que van realizndose pasos del algoritmo, parte del contenido del registro Resto comienza a estar desaprovechado. Segn realizamos pasos, obtenemos los bits del cociente uno a uno. El espacio desaprovechado del registro Resto es exactamente igual que el nmero de bits del cociente que tenemos calculados en cada instante. Por tanto, se incorpor una mejora al circuito, de forma que el registro Cociente desaparece. El dividendo se carga inicialmente en la mitad derecha del registro Resto. En cada iteracin, cuando obtengamos un bit del cociente, lo almacenaremos en el bit menos significativo del registro Resto. Al final el cociente queda en la mitad menos significativa del registro Resto, mientras que el resto queda en la mitad ms significativa de dicho registro.

44

Circuitos para multiplicacin y divisin de nmeros en coma fija

Divisin con restauracin: 3 versin

Circuitera necesaria:

Un registro de n bits para el divisor. Un sumador / restador de n bits. Un registro de 2n bits para el resto y el cociente, que pueda cargarse en paralelo en su mitad izquierda dejando intacta la mitad derecha, o cargarse en paralelo en su mitad derecha dejando intacta su mitad izquierda; este registro admitir desplazamientos lgicos unitarios hacia la izquierda del registro completo. Un contador de 0 a n para contar el nmero de iteraciones. Un controlador para generar la secuencia de seales necesaria.

Divisor 32 bits

Circuito para n = 32 bits con las conexiones y seales de control necesarias.

32-bit ALU

Remainder 64 bits

Shift right Shift left Write

Control test

45

Circuitos para multiplicacin y divisin de nmeros en coma fija

Divisin con restauracin: 3 versin

Inicio Desplazar Resto 1 bit hacia la izquierda

Restoizq Restoizq-Divisor

No

Resto < 0?

Operaciones de la fase de inicio: 1. Iniciar el registro Divisor 2. Iniciar el registro Resto (mitad izquierda a 0, mitad derecha con el dividendo) 3. Contador 0

Divisor 32 bits

No

Desplazar Resto 1 bit hacia la izquierda Resto0 1

Restoizq Restoizq+Divisor Desplazar Resto 1 bit hacia la izquierda Resto0 0

Contador Contador+1

32-bit ALU

Contador=n?

S

Desplazar Restoizq 1 bit hacia la derecha Fin

Remainder 64 bits

Shift right Shift left Write

Control test

Ejercicio propuesto: dibujar el diagrama de estados del controlador del circuito.

46

Circuitos para multiplicacin y divisin de nmeros en coma fija

Divisin con restauracin: 3 versin

Ejemplo: n=4, dividir D=10102=1010 por d=00112=310

Iteracin

0 1 Valores iniciales Desplazar Resto a la izquierda Restoizq Restoizq Divisor Resto<0 Restoizq Restoizq + Divisor Desplazar Resto a la izquierda Resto0=0 2 Restoizq Restoizq Divisor Resto<0 Restoizq Restoizq + Divisor Desplazar Resto a la izquierda Resto0=0 3 Restoizq Restoizq Divisor Resto0 Desplazar Resto a la izquierda Resto0=1 4 Restoizq Restoizq Divisor Resto0 Desplazar Resto a la izquierda Resto0=1 Ajuste final Desplazar Restoizq a la derecha

Paso

Divisor

0011

Resto

0000 1010 0001 0100 1110 0100 0001 0100 0010 1000 0010 1000 1111 1000 0010 1000 0101 0000 0101 0000 0010 0000 0100 0000 0100 0001 0001 0001 0010 0010 0010 0011 0001 0011 47

Circuitos para multiplicacin y divisin de nmeros en coma fija

Divisin con restauracin

Los algoritmos y circuitos mostrados dividen nmeros dados en binario puro. Puede hacerse divisin con restauracin para nmeros en complemento a 2, aunque el algoritmo es complicado. Divisin de nmeros en complemento a 2: se puede hacer pasando los operandos a positivos antes de hacer la divisin, y ajustando los signos del cociente y/o el resto si es preciso: Si el signo del dividendo y el del divisor coinciden, el cociente es positivo, y en caso contrario es negativo. El signo del resto es el mismo que el del dividendo.

48

Circuitos para multiplicacin y divisin de nmeros en coma fija

9. Multiplicacin y divisin en ensamblador

MIPS La multiplicacin y la divisin emplean dos registros especiales para guardar los resultados: Hi y Lo. En la multiplicacin, la parte ms significativa del resultado queda en Hi y la menos significativa en Lo. En la divisin, el cociente queda en Lo y el resto en Hi. Instrucciones de multiplicacin: Con signo: mult. Sin signo: multu. Instrucciones de divisin: Con signo: div. Sin signo: divu. MC68000: Multiplicacin (muls, mulu): operandos de 16 bits, resultado de 32 bits. Divisin (divs, divu): dividendo de 32 bits, divisor de 16 bits, cociente de 16 bits, resto de 16 bits.

49

También podría gustarte

- Ejercicio1 UD6.2 (SI) Andoni FelipeDocumento7 páginasEjercicio1 UD6.2 (SI) Andoni FelipeAndoni Felipe MelgarAún no hay calificaciones

- Codigo de Exceso 3Documento3 páginasCodigo de Exceso 3reo32Aún no hay calificaciones

- Suma y Resta en BinarioDocumento2 páginasSuma y Resta en BinarioRonald MartinezAún no hay calificaciones

- Wuolah Free Soluciones Ejs MemoriaDocumento16 páginasWuolah Free Soluciones Ejs MemoriaValen EirnymAún no hay calificaciones

- Tema 5 - Sistemas de NumeraciónDocumento18 páginasTema 5 - Sistemas de NumeraciónJOHNNY PABLO LIZA VELÁSQUEZAún no hay calificaciones

- Fase 1 - Reconocimiento de Sistemas de Numeración y Simplificación de Funciones LógicasDocumento18 páginasFase 1 - Reconocimiento de Sistemas de Numeración y Simplificación de Funciones LógicasHeison Bonilla VargasAún no hay calificaciones

- CircuitosDocumento167 páginasCircuitoslaratikAún no hay calificaciones

- Sistema Binario - Wikipedia, La Enciclopedia LibreDocumento12 páginasSistema Binario - Wikipedia, La Enciclopedia LibreMonique GardnerAún no hay calificaciones

- Guia 3 - Decodificadores y CodificadoresDocumento9 páginasGuia 3 - Decodificadores y CodificadoresYani VillegazAún no hay calificaciones

- Cap 1 New Margin 1Documento25 páginasCap 1 New Margin 1Juan PeñaAún no hay calificaciones

- Introducción y Sistemas NuméricosDocumento68 páginasIntroducción y Sistemas NuméricosAngela Maria Benavides JojoaAún no hay calificaciones

- Informe PrevioDocumento16 páginasInforme PrevioAdriel Mamani QuispeAún no hay calificaciones

- Informe LAB Nº4 Circuitos Dig. L13 ROJAS CAJALEON, ESTEBAN ALEXDocumento6 páginasInforme LAB Nº4 Circuitos Dig. L13 ROJAS CAJALEON, ESTEBAN ALEXEsteban RojasAún no hay calificaciones

- ElectronicaDocumento78 páginasElectronicaAbraham Mora ReyesAún no hay calificaciones

- Preparatorio 1 Salazar FranciscoDocumento8 páginasPreparatorio 1 Salazar FranciscoFrank SDAún no hay calificaciones

- Omron CX OneDocumento16 páginasOmron CX OneJavier MuñozAún no hay calificaciones

- Ejercicios y Problemas CombinacionalesDocumento46 páginasEjercicios y Problemas CombinacionalesGemerson Ahumada Sernaqué0% (1)

- Conversión Del Sistema Decimal Al BinarioDocumento21 páginasConversión Del Sistema Decimal Al BinarioAnet VZAún no hay calificaciones

- Sumador de 4 BitsDocumento4 páginasSumador de 4 BitsJose Luis Kenta MuxoAún no hay calificaciones

- Procedimientos VAGCOM (VCDS)Documento1 páginaProcedimientos VAGCOM (VCDS)Paul CastroAún no hay calificaciones

- Conversion de Decimal A Binario Incluyendo DecimalesDocumento6 páginasConversion de Decimal A Binario Incluyendo DecimalesMadrid JosueAún no hay calificaciones

- APRENDA ENSAMBLADOR 80x86 EN DOS PATADAS PDFDocumento45 páginasAPRENDA ENSAMBLADOR 80x86 EN DOS PATADAS PDFAlberto Castillo MejiaAún no hay calificaciones

- Circuitos Combinacionales (MSI)Documento34 páginasCircuitos Combinacionales (MSI)Nestor QuijadaAún no hay calificaciones

- Taller No.1Documento2 páginasTaller No.1MargellyAún no hay calificaciones

- Conversion Entre Diferentes BasesDocumento3 páginasConversion Entre Diferentes BasesVictor Gonzàlez PalafoxAún no hay calificaciones

- Proyecto SUmadorDocumento12 páginasProyecto SUmadoralbrtmsAún no hay calificaciones

- 2023 TP2 - CodigosDocumento5 páginas2023 TP2 - CodigosLeo PereiraAún no hay calificaciones

- Juego de Instrucciones 8086 PDFDocumento47 páginasJuego de Instrucciones 8086 PDFLuis GuardiaAún no hay calificaciones

- Lab 07 Sist Digit. Jhon LaureanoDocumento24 páginasLab 07 Sist Digit. Jhon LaureanoJhon LaureanoAún no hay calificaciones

- Clase 6 Sumadores Multiplexores PDFDocumento20 páginasClase 6 Sumadores Multiplexores PDFMaite ZuritaAún no hay calificaciones