Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Laboratorio 1

Cargado por

Carol CardenasTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Laboratorio 1

Cargado por

Carol CardenasCopyright:

Formatos disponibles

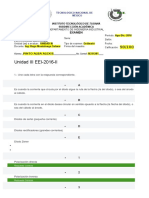

FUNCIONAMIENTO DE COMPUERTAS DIGITALES

SAMUEL GONZALEZ COELLO

CAROL VIVIANA CARDENAS

LUIS ANTONIO HERRERA

UNIVERSIDAD DE CUNDINAMARCA

FACULTAD DE INGENIERA

PROGRAMA INGENIERA ELECTRNICA

FUSAGASUG

2011

FUNCIONAMIENTO DE COMPUERTAS DIGITALES

SAMUEL GONZALEZ COELLO

CAROL VIVIANA CARDENAS

LUIS ANTONIO HERRERA

Informe de Laboratorio N 1 correspondiente al Ncleo Temtico de Circuitos

Digitales I

ILBER ADONAYT RUGE RUGE

Ingeniero Electrnico

UNIVERSIDAD DE CUNDINAMARCA

FACULTAD DE INGENIERA

PROGRAMA INGENIERA ELECTRNICA

FUSAGASUG

2011

CONTENIDO

0. INTRODUCCION

1. OBJETIVOS

2. MATERIALES SUGERIDOS

3. PLANTEAMIENTO Y PROCEDIMIENTO

3.1. Funcionamiento de la Compuerta OR

3.2. Funcionamiento de la compuerta OR de cuatro entradas

3.3. Funcionamiento compuerta AND de cuatro entradas

3.4. Funcionamiento de la compuerta NOT

3.5. Funcionamiento de la compuerta XOR

4. TEOREMA DE MORGAN

5. CONCLUCIONES

6. REFERENCIAS

0. INTRODUCCION

En la electrnica digital un circuito lgico es aquel que maneja la informacin en

forma de 1 y 0, dos niveles lgicos de voltaje fijos. En el siguiente informe de

laboratorio estudiaremos el funcionamiento de los circuitos lgicos los cuales

estn compuestos por elementos digitales como la compuerta AND, compuerta

OR, Compuerta NOT y compuerta XOR.

Durante la prctica es necesario realizar una comprobacin terica para la cual

utilizaremos los Teoremas de Morgan los cuales sirven para transformar sumas

lgicas en productos lgicos y viceversa.

1. OBJETIVOS

1.1. OBJETIVO GENERAL

Realizar una comprobacin experimental de los conceptos vistos en

clase acerca de Compuertas Lgicas, Tablas de Verdad y Teorema de

Morgan.

1.2. OBJETIVOS ESPECIFICOS

Llevar a la prctica los conceptos tericos acerca del funcionamiento de las

compuertas digitales And, Or, Not y Xor de acuerdo a la tabla de

funcionamiento de las mismas.

Implementar conceptos bsicos de electrnica para el montaje y desarrollo

de la prctica dentro del laboratorio.

2. MATERIALES SUGERIDOS:

IC 74LS04, IC74LS08, IC74LS32 E IC74LS86

1 PROTOBOARD

1 PINZAS

1 PELACABLES

RESISTENCIAS DE 330

RESISTENCIAS DE 4.7K

TRANSISTORES 2N2222A

DIPSWITCH

LEDS

3. PLANTEAMIENTO Y PROCEDIMIENTO:

Para el desarrollo de la prctica es necesario conocer el comportamiento de cada

una de las compuertas lgicas a comprobar, as como el funcionamiento y la

distribucin de cada uno de los circuitos integrados utilizados durante la

comprobacin experimental. A continuacin se realizara una explicacin de cada

una de las compuertas con los resultados obtenidos respectivamente.

3.1. Funcionamiento De La Compuerta Or:

Figura 1. Distribucin de pines del ic 74ls32.

Los niveles lgicos de entrada se obtienen mediante los interruptores a y b y el

estado de Salida se visualiza mediante el led, con su correspondiente amplificador

para no sobrecargar La salida.

Figura 2. Circuito Practico para experimentar la compuerta CI 74ls32.

A continuacin se mostrar en la Tabla 1, los estados 1 y 0 y los valores de

tensin de las salidas de la compuerta OR tomados experimentalmente.

A B LED (Salida) TENSION EN LA

SALIDA (V)

0 0 0 0.04

0 1 1 4.73

1 0 1 4.73

1 1 1 4.73

Tabla 1. Tabla de verdad compuerta lgica OR

Figura 3. Simulacin del Circuito compuerta Or

Como podemos Ver en la simulacin La Entrada Uno Esta Abierta y El 1 lgico

tiene una Tensin de 3.77 V, mientras que La entrada Dos Esta Cerrada y el 0

Lgico tiene una Tensin de 1.19 mV.

Los datos Obtenidos Experimentalmente son aproximados a lo obtenidos en la

simulacin.

1

2

3

U1:A

74LS32

R2

4.7k

R1

4.7k

R3

10k

Q1

NPN

R4

270

D1

LED-RED

OFF ON

1

2

4

3

DSW1

DIPSW_2

V1

5V

Volts

+3.77

mV

+1.19

3.2. Funcionamiento compuerta Or de cuatro entradas:

Para realizar tal procedimiento se utilizaran tres compuertas 74LS32. El circuito se

puede realizar como se muestra en la Figura 3.

Las entradas A, B, C y D del circuito tendrn como funcin la suma entre estas

dos compuertas sus salidas sern las entradas de una tercer compuerta

sumndose entre s y la salida ser A+B+C+D y el LED indicar que cualquier

entrada ya sea A, B, C o D si esta en nivel o estado 1 este se encender y tendr

como salida un 1, pero si todas las entradas se encuentran en nivel bajo o 0 su

salida ser 0. Este funcionamiento se mostrar en la Tabla 2, en donde

observaremos los estados de la compuerta OR con cuatro entradas.

Figura 4. Montaje de compuerta Or de 4 entradas

A continuacin se mostrar en la Tabla 1, los estados 1 y 0 y los valores de

tensin de las salidas de la compuerta OR tomados experimentalmente.

A B C D ESTADO TENSION

(V)

0 0 0 0 0 0.111

0 0 0 1 1 4.36

0 0 1 0 1 4.38

0 0 1 1 1 4.39

0 1 0 0 1 4.33

0 1 0 1 1 4.23

0 1 1 0 1 4.41

0 1 1 1 1 4.40

1 0 0 0 1 4.40

1 0 0 1 1 4.40

1 0 1 0 1 4.40

1 0 1 1 1 4.40

1 1 0 0 1 4.40

1 1 0 1 1 4.40

1 1 1 0 1 4.37

1 1 1 1 1 4.40

Tabla 2. Tabla de verdad compuerta lgica OR de Cuatro Entradas

Figura 5. Simulacin del Circuito compuerta Or de Cuatro entradas

Como podemos Ver en la simulacin las Entradas Uno Dos y Cuatro estn

Abiertas y El 1 lgico tiene una Tensin de 4.18 V, mientras que La entrada Dos

1

2

3

U1:A

74LS32

4

5

6

U1:B

74LS32

9

10

8

U1:C

74LS32

OFF ON

1

2

3

4

8

7

6

5

DSW1

DIPSW_4

R1

4.7k

R2

4.7k

R3

4.7k

R4

4.7k

R5

10k

Q1

NPN

D1

LED-RED

R6

270

V1

5V

Volts

+4.18

mV

+1.32

Esta Cerrada y el 0 Lgico tiene una Tensin de 1.32 mV. Si cualquiera de las

entradas es 1 la salida ser 1 y encender el Led. Para que la salida sea 0

todas las entradas tienen que ser 0.

Los datos de Tensin obtenidos Experimentalmente son aproximados a lo

obtenidos en la simulacin.

3.3. Funcionamiento compuerta And de cuatro entradas:

Figura 6. Distribucin de pines del ic 74ls32.

Para la compuerta AND se utiliza el CI 74LS08 y se monta el circuito de la Figura

3, Remplazando la compuerta OR (CI 74LS32) por la compuerta lgica AND (CI

74LS08)

Las entradas A, B, C y D del circuito tendrn como funcin la multiplicacin entre

estas dos compuertas sus salidas sern las entradas de una tercer compuerta

multiplicndose entre s y la salida ser A*B*C*D y el LED indicar que cualquier

entrada ya sea A, B, C o D si est en estado 0 este estar apagado y tendr

como salida un 0 , pero si todas las entradas se encuentran en nivel 1 su salida

ser 1 . Este funcionamiento se mostrar en la Tabla 3, en donde observaremos

los niveles de la compuerta AND con cuatro entradas.

A continuacin se mostrar en la Tabla 1, los estados 1 y 0 y los valores de

tensin de las salidas de la compuerta OR tomados experimentalmente.

A B C D ESTADO TENSION

(V)

0 0 0 0 0 0.13

0 0 0 1 0 0.13

0 0 1 0 0 0.13

0 0 1 1 0 0.13

0 1 0 0 0 0.13

0 1 0 1 0 0.13

0 1 1 0 0 0.13

0 1 1 1 0 0.13

1 0 0 0 0 0.13

1 0 0 1 0 0.13

1 0 1 0 0 0.13

1 0 1 1 0 0.13

1 1 0 0 0 0.13

1 1 0 1 0 0.13

1 1 1 0 0 0.13

1 1 1 1 1 4.10

Tabla 3. Tabla de verdad compuerta lgica AND de Cuatro Entradas

Figura 7. Simulacin del Circuito compuerta AND de Cuatro entradas

1

2

3

U1:A

74LS32

4

5

6

U1:B

74LS32

9

10

8

U1:C

74LS32

OFF ON

1

2

3

4

8

7

6

5

DSW1

DIPSW_4

R1

4.7k

R2

4.7k

R3

4.7k

R4

4.7k

R5

10k

Q1

NPN

D1

LED-RED

R6

270

V1

5V

Volts

+4.18

mV

+1.32

3.4. Funcin lgica NOT de cuatro entradas

Para esta compuerta se utiliza el CI 74LS04 y se monta el mismo circuito de la

Figura 2, cambiando el CI 74LS32 compuerta lgica NOT por el CI 74LS04

compuerta lgica NOT.

Figura 8. Distribucin de pines del CL 74LS04.

El funcionamiento de este circuito es negar la entrada es decir si tenemos un (1) o

nivel alto su salida ser (0) o nivel bajo y viceversa. Este funcionamiento se

mostrar en la Tabla 8.

A ESTADO TENSION

(V)

0 0 0.001

1 1 4.979

Tabla 4. Tabla de verdad compuerta lgica NOT de cuatro entradas.

3.5. Funcin lgica XOR de cuatro entradas:

Figura 9. Compuerta XOR 74SL86

Para la compuerta XOR se utiliza el CI 74LS86 y se monta el mismo circuito de la

Figura 3, cambiando el CI 74LS32 compuerta lgica OR por el CI 74LS86

compuerta lgica XOR.

Este circuito est formado por 3 compuertas XOR la salida de la primera

compuerta A y B y la de la segunda compuerta que es C y D, conforman las dos

entrada de la tercer compuerta del circuito, el LED indicara el estado de la salida

de la tercer compuerta. Si la salida de la compuerta 1 es diferente a la salida de

la compuerta 2 la salida de la tercer compuerta ser 1 de lo contrario el estado

de la salida ser 0, la tercer compuerta tiene mismo funcionamiento para las

compuerta 1 y 2. Este funcionamiento se mostrar en la Tabla 4, en donde

observaremos los estados de la compuerta XOR de cuatro entradas.

A B C D ESTADO TENSION

(V)

0 0 0 0 0 0.16

0 0 0 1 1 4.35

0 0 1 0 1 4.32

0 0 1 1 0 0.16

0 1 0 0 1 4.30

0 1 0 1 0 0.17

0 1 1 0 0 0.17

0 1 1 1 1 4.41

1 0 0 0 1 4.23

1 0 0 1 0 0.17

1 0 1 0 0 0.17

1 0 1 1 1 4.36

1 1 0 0 0 0.18

1 1 0 1 1 4.39

1 1 1 0 1 4.37

1 1 1 1 0 0.16

Tabla 5. Tabla de verdad compuerta lgica XOR de cuatro entradas.

Figura 9. Simulacin circuito compuerta XOR de cuatro entradas

1

2

3

U1:A

74LS86

4

5

6

U1:B

74LS86

R1

4.7k

R2

4.7k

R3

4.7k

R4

4.7k

OFF ON

1

2

3

4

8

7

6

5

DSW1

DIPSW_4

9

10

8

U1:C

74LS86

R5

10k

Q1

NPN

D1

LED-RED

R6

270

4. TEOREMA DE MORGAN

Para la comprobacin terica de cada una de las compuertas lgicas utilizaremos

el Teorema de Morgan, el cual permiten transformar funciones suma en funciones

producto y viceversa, lo que permite hacer circuitos usando un mismo tipo de

compuerta. El teorema se basa en dos expresiones bsicas:

A BA B (Ecuacin 1)

A BA B (Ecuacin 2)

La comprobacin del teorema se realizara con la implementacin de dos circuitos,

el resultado de la experimentacin debe arrojar que los estados de las dos salidas

de cada circuito coincidan para todas las combinaciones y aplicar dicho teorema

para encontrar la equivalencia de la Ecuacin 3.

Figura 10. Circuito prctico para comprobacin del teorema de Morgan

A B (A+B)

SALIDA1: A+B

0 0 0 1

0 1 1 0

1 0 1 0

1 1 1 0

A B

A

SALIDA 2: A

0 0 1 1 1

0 1 1 0 0

1 0 0 1 0

1 1 0 0 0

Tabla 6. Tabla de verdad de la equivalencia de los circuitos de la Figura 10

Figura 11. Circuito prctico para comprobacin del teorema de Morgan

Tabla de verdad respecto al circuito de la figura 11, llegando a la comprobacin

del teorema de Morgan.

A B (A B)

SALIDA1: A B

0 0 0 1

0 1 0 1

1 0 0 1

1 1 1 0

A B

A

SALIDA2:A

+B

0 0 1 1 1

0 1 1 0 1

1 0 0 1 1

1 1 0 0 0

Tabla 7. Tabla de verdad de la equivalencia de los dos circuitos de la Figura 11

La Ecuacin 4 es la equivalente de la ecuacin 3, segn el Teorema de Morgan

FA BCDE (Ecuacin 3)

FAB C D E

FAB CD E (Ecuacin 4)

Tambin se puede verificar mediante tablas de verdad y aplicaciones de Morgan la

equivalencia de las siguientes expresiones (Ecuacin 5)

A B C D E A B C D E (Ecuacin 5)

Mediante el siguiente ejercicio verificamos la equivalencia de las dos expresiones

y con las tablas de verdad 11 y 12 observamos la igualdad.

NAB

MCDE

AB

CDE

X=AB

CDE

A B C B E

B

AB

CDE

CDE

AB

+CDE

0 0 0 0 0 1 0 0 1 1

0 0 0 0 1 1 0 0 1 1

0 0 0 1 0 1 0 0 1 1

0 0 0 1 1 1 0 0 1 1

0 0 1 0 0 1 0 0 1 1

0 0 1 0 1 1 0 0 1 1

0 0 1 1 0 1 0 0 1 1

0 0 1 1 1 1 0 1 0 0

0 1 0 0 0 0 0 0 1 1

0 1 0 0 1 0 0 0 1 1

0 1 0 1 0 0 0 0 1 1

0 1 0 1 1 0 0 0 1 1

0 1 1 0 0 0 0 0 1 1

0 1 1 0 1 0 0 0 1 1

0 1 1 1 0 0 0 0 1 1

0 1 1 1 1 0 0 1 0 0

1 0 0 0 0 1 1 0 1 1

1 0 0 0 1 1 1 0 1 1

1 0 0 1 0 1 1 0 1 1

1 0 0 1 1 1 1 0 1 1

1 0 1 0 0 1 1 0 1 1

1 0 1 0 1 1 1 0 1 1

1 0 1 1 0 1 1 0 1 1

1 0 1 1 1 1 1 1 0 1

1 1 0 0 0 0 0 0 1 1

1 1 0 0 1 0 0 0 1 1

1 1 0 1 0 0 0 0 1 1

1 1 0 1 1 0 0 0 1 1

1 1 1 0 0 0 0 0 1 1

1 1 1 0 1 0 0 0 1 1

1 1 1 1 0 0 0 0 1 1

1 1 1 1 1 0 0 1 0 0

Tabla 8. Tabla de verdad de la equivalencia de la primera expresin

A B C B E

B

AB

AB

CDE

AB

CDE

AB

CDE

0 0 0 0 0 1 0 1 0 0 1

0 0 0 0 1 1 0 1 0 0 1

0 0 0 1 0 1 0 1 0 0 1

0 0 0 1 1 1 0 1 0 0 1

0 0 1 0 0 1 0 1 0 0 1

0 0 1 0 1 1 0 1 0 0 1

0 0 1 1 0 1 0 1 0 0 1

0 0 1 1 1 1 0 1 1 1 0

0 1 0 0 0 0 0 1 0 0 1

0 1 0 0 1 0 0 1 0 0 1

0 1 0 1 0 0 0 1 0 0 1

0 1 0 1 1 0 0 1 0 0 1

0 1 1 0 0 0 0 1 0 0 1

0 1 1 0 1 0 0 1 0 0 1

0 1 1 1 0 0 0 1 0 0 1

0 1 1 1 1 0 0 1 1 1 0

1 0 0 0 0 1 1 0 0 0 1

1 0 0 0 1 1 1 0 0 0 1

1 0 0 1 0 1 1 0 0 0 1

1 0 0 1 1 1 1 0 0 0 1

1 0 1 0 0 1 1 0 0 0 1

1 0 1 0 1 1 1 0 0 0 1

1 0 1 1 0 1 1 0 0 0 1

1 0 1 1 1 1 1 0 1 0 1

1 1 0 0 0 0 0 1 0 0 1

1 1 0 0 1 0 0 1 0 0 1

1 1 0 1 0 0 0 1 0 0 1

1 1 0 1 1 0 0 1 0 0 1

1 1 1 0 0 0 0 1 0 0 1

1 1 1 0 1 0 0 1 0 0 1

1 1 1 1 0 0 0 1 0 0 1

1 1 1 1 1 0 0 1 1 1 0

Tabla 9. Tabla de verdad de la equivalencia de la expresin de la derecha de la Ecuacin 5.

5. CONCLUCIONES

De acuerdo a la prctica realizada se lleg a la comprobacin experimental

del funcionamiento de cada una de las compuertas lgicas, obteniendo

como resultado la demostracin de cada una de las tablas de verdad

respectivamente.

A partir de los datos obtenidos de voltaje en cada circuito, comprobamos el

comportamiento terico de las tensiones el cual indica que para una seal

digital 1 el nivel de tensin es de 2 a 5 voltios, y para una seal 0 el nivel

de tensin es de 0 a 0,8 voltios tal como lo indican las tablas de resultados.

Durante la realizacin terica del laboratorio concluimos que la

implementacin del teorema de Morgan es fundamental para la

simplificacin en la resolucin de ecuaciones lgicas.

REFERENCIAS

http://www.mitecnologico.com/Main/AlgebraBooleanaYTeoremasDeMorgan

(tomado el 5 de Marzo de 2011).

http://www.unicrom.com/dig_CircNorequicalente.asp (tomado el 5 de marzo

de 2011).

http://www.ramonmedina.name/files/universidad/lsd/lsd0002.pdf (tomado el

7 de Marzo de 2011).

THOMAS FLOYD, FUNDAMENTOS DE ELECTRNICA DIGITAL, ED.

PRENTICE HALL.

También podría gustarte

- Foro 2 de Diseno Logico 6 CuatriDocumento7 páginasForo 2 de Diseno Logico 6 Cuatrienrique daniel bravo zarate100% (1)

- Diseño de Sistemas Digitales y Arquitectura de ComputadorasDocumento332 páginasDiseño de Sistemas Digitales y Arquitectura de Computadorascuauh pimente100% (1)

- Reporte 3 Compuertas LogicasDocumento30 páginasReporte 3 Compuertas LogicasArturo Pineda100% (2)

- Electronica 2 Semana 4Documento9 páginasElectronica 2 Semana 4Carlos PobleteAún no hay calificaciones

- Practice 1Documento8 páginasPractice 1Bere OlmosAún no hay calificaciones

- Informe de Laboratorio de Compuertas LogicasDocumento13 páginasInforme de Laboratorio de Compuertas LogicasLuis RondoAún no hay calificaciones

- Laboratorio N 4 OR AND NOTDocumento7 páginasLaboratorio N 4 OR AND NOTKATHERINE ANDREA HERRERA VARGASAún no hay calificaciones

- Ci PDFDocumento12 páginasCi PDFRAMOS GARCIA JENIFER YESENIAAún no hay calificaciones

- Informe de Laboratorio DecodificadoresDocumento7 páginasInforme de Laboratorio DecodificadoresAndres DGAún no hay calificaciones

- P4 Alvarado Aviles Escobar Moran MendezDocumento20 páginasP4 Alvarado Aviles Escobar Moran MendezSamuel MoralesAún no hay calificaciones

- Laboratorio 1 Lógicos AND OR NOTDocumento12 páginasLaboratorio 1 Lógicos AND OR NOTdeoli1990Aún no hay calificaciones

- Practica 2 CorregidoDocumento22 páginasPractica 2 CorregidoJohn PorterAún no hay calificaciones

- Practica 2 Electrónica Equipo 14Documento23 páginasPractica 2 Electrónica Equipo 14Ximena J LanderosAún no hay calificaciones

- Informe Compuertas Logicas LaboratorioDocumento19 páginasInforme Compuertas Logicas LaboratorioFernando Marín Quevedo0% (1)

- Compuertas Logicas BasicasDocumento16 páginasCompuertas Logicas BasicasRonny Javier Gonzalez GutierrezAún no hay calificaciones

- Práctica N 6Documento13 páginasPráctica N 6Rosita Lima BenitesAún no hay calificaciones

- Lab #1 Compuertas LogicasDocumento6 páginasLab #1 Compuertas LogicasManolo Camilo Ortega CondegaAún no hay calificaciones

- Practica 2 Sistemas Digitales EspeDocumento22 páginasPractica 2 Sistemas Digitales EspeJulio RamírezAún no hay calificaciones

- Informe Compuertas LogicasDocumento8 páginasInforme Compuertas LogicasRuben Darío AyalaAún no hay calificaciones

- Diseño Sumador RestdorDocumento10 páginasDiseño Sumador RestdorRamiro David MAún no hay calificaciones

- LABORATORIO 01 - Puertas LogicasDocumento4 páginasLABORATORIO 01 - Puertas LogicasJesus Martin Alvarez VasquezAún no hay calificaciones

- Informe de Laboratorio de Compuertas LógicasDocumento11 páginasInforme de Laboratorio de Compuertas LógicasM Fernandhoo DMAún no hay calificaciones

- Lab #1 Compuertas LogicasDocumento5 páginasLab #1 Compuertas Logicassanes durangoAún no hay calificaciones

- Practica 3 ElectronicaDocumento24 páginasPractica 3 ElectronicaXimena J LanderosAún no hay calificaciones

- PRACTICA 1 LaboratorioDigitalDocumento23 páginasPRACTICA 1 LaboratorioDigitalRonald Molina FariasAún no hay calificaciones

- Compuertas Lógicas y Tabla de VerdadDocumento17 páginasCompuertas Lógicas y Tabla de VerdadAc Bob BeatAún no hay calificaciones

- Informe Sobre Circuitos Lógicos (Compuertas Lógicas)Documento13 páginasInforme Sobre Circuitos Lógicos (Compuertas Lógicas)Cheyn88% (8)

- PRÁCTICA 1. AND, OR, y Lógica InversoraDocumento17 páginasPRÁCTICA 1. AND, OR, y Lógica InversoraMaria BeltranAún no hay calificaciones

- Práctica 3 - Compuertas LogicasDocumento17 páginasPráctica 3 - Compuertas LogicasDanielAún no hay calificaciones

- Compuertas Logicas Con RelevadoresDocumento14 páginasCompuertas Logicas Con RelevadoresGabino Barrera MillanAún no hay calificaciones

- Informe de Laboratorio No 1,2,3,4Documento21 páginasInforme de Laboratorio No 1,2,3,4Elizabeth estefany Choque lozaAún no hay calificaciones

- Práctica 2 - SE - Unidad 3Documento9 páginasPráctica 2 - SE - Unidad 3Sergio Armando EsparzaAún no hay calificaciones

- Informe Digital 1Documento6 páginasInforme Digital 1Nidi Veizaga ArispeAún no hay calificaciones

- Universidad Nacional Autónoma de México: Práctica 1: Herramientas de Prueba para El Sistema MínimoDocumento7 páginasUniversidad Nacional Autónoma de México: Práctica 1: Herramientas de Prueba para El Sistema MínimoUziiel OlguiinAún no hay calificaciones

- Laboratorio 2 Circuitos CombinatoriosDocumento10 páginasLaboratorio 2 Circuitos CombinatoriosJair CoronelAún no hay calificaciones

- Práctica 1Documento7 páginasPráctica 1Maria BeltranAún no hay calificaciones

- Estados LogicosDocumento12 páginasEstados LogicosIsmaPillajo100% (1)

- Introducción Al Manejo de Circuitos Integrados y Comprobación de La Operación de Las Compuertas Lógicas Básicas.Documento11 páginasIntroducción Al Manejo de Circuitos Integrados y Comprobación de La Operación de Las Compuertas Lógicas Básicas.Gustavo Adolfo Mestra Garay100% (3)

- Practica 1 Circuitos LogicosDocumento7 páginasPractica 1 Circuitos LogicosEnrique Romero BlancoAún no hay calificaciones

- Practica 2 Esime Zacatenco Electronica 1Documento2 páginasPractica 2 Esime Zacatenco Electronica 1Alal Morales MontenegroAún no hay calificaciones

- Informe #2 - Sistemas DigitalesDocumento6 páginasInforme #2 - Sistemas DigitalesJackeline Palencia VasquezAún no hay calificaciones

- Experimento 2 - Compuertas Logicas - Circuitos DigitalesDocumento8 páginasExperimento 2 - Compuertas Logicas - Circuitos DigitalesBrenda CastilloAún no hay calificaciones

- Boletín de Práctica 1 FCO UPVDocumento9 páginasBoletín de Práctica 1 FCO UPVRiwa DainAún no hay calificaciones

- Reportes de PracticaDocumento44 páginasReportes de PracticaGalvan Salgado Maria FernandaAún no hay calificaciones

- Reporte de Practica 1 Funciones EquivalentesDocumento8 páginasReporte de Practica 1 Funciones EquivalentesAbraham HernandezAún no hay calificaciones

- Laboratorio Circuitos CombinatoriosDocumento11 páginasLaboratorio Circuitos CombinatoriosHeyner Marmol VerbelAún no hay calificaciones

- P3 EiiiDocumento13 páginasP3 Eiiielectronico49Aún no hay calificaciones

- Manual de Prácticas de Electrónica Básica - Christian EspinosaDocumento13 páginasManual de Prácticas de Electrónica Básica - Christian EspinosaelkmaleonAún no hay calificaciones

- Caracteristicas de Conexion de CompuertasDocumento6 páginasCaracteristicas de Conexion de CompuertasArthur Thony LtgAún no hay calificaciones

- Practica 2 Codigo BCDDocumento8 páginasPractica 2 Codigo BCDLuis GómezAún no hay calificaciones

- PRACTICA de Compuestas LogicasDocumento13 páginasPRACTICA de Compuestas Logicasmane777Aún no hay calificaciones

- Practica 1 - Comprobacion de Compuertas or and Not Nor NandDocumento11 páginasPractica 1 - Comprobacion de Compuertas or and Not Nor NandDanAún no hay calificaciones

- Reporte Practica Compuertas LogicasDocumento12 páginasReporte Practica Compuertas Logicasilustresimio100% (1)

- Practica 1Documento11 páginasPractica 1sergio cerinoAún no hay calificaciones

- Informe - Compuertas LógicasDocumento6 páginasInforme - Compuertas LógicasLuis Alejandro Alvarez RengifoAún no hay calificaciones

- Practica 1 Electronica DigitalDocumento4 páginasPractica 1 Electronica DigitalVictor RinconAún no hay calificaciones

- Principios BásicosDocumento6 páginasPrincipios BásicosKatherine RíosAún no hay calificaciones

- Ites CarlosDocumento22 páginasItes CarlosDavid RobalinoAún no hay calificaciones

- Informe#1 de CircuitosDocumento14 páginasInforme#1 de CircuitosALVARO GONZALO SOLIZ AGREDAAún no hay calificaciones

- Guia4. LabDocumento13 páginasGuia4. LabLaura Daniela Moreno SotoAún no hay calificaciones

- Parctica 1 - Circuitos LogicosDocumento10 páginasParctica 1 - Circuitos LogicosMIGUEL MORALESAún no hay calificaciones

- Clase 2 - 1 Lógica DigitalDocumento52 páginasClase 2 - 1 Lógica DigitalYessy TrottaAún no hay calificaciones

- Operadores AnalogicosDocumento25 páginasOperadores AnalogicosyamitinfanteAún no hay calificaciones

- Semana7. Compuertas LógicasDocumento6 páginasSemana7. Compuertas LógicasDomínguez Monroy Martin YussetAún no hay calificaciones

- Tema3 Algebra de Boole - Electronica DigitalDocumento25 páginasTema3 Algebra de Boole - Electronica DigitalLEONARDO BALTAZAR ACARAPIAún no hay calificaciones

- Compuerta XORDocumento3 páginasCompuerta XORAngel de JesusAún no hay calificaciones

- Diseño de Circuitos CombinacionalesDocumento7 páginasDiseño de Circuitos CombinacionalesSamuel Diaz Parra0% (1)

- Evaluacion IsoformismoDocumento7 páginasEvaluacion IsoformismoAndreita QuesadaAún no hay calificaciones

- Gpo X Unidad III EeiDocumento8 páginasGpo X Unidad III EeiIng Hugo Montelongo SolanoAún no hay calificaciones

- Algebra de Boole y Compuertas LógicasDocumento13 páginasAlgebra de Boole y Compuertas LógicaseliasAún no hay calificaciones

- Márgenes de RuidoDocumento3 páginasMárgenes de Ruidoruben rivera50% (2)

- PRACTICA 1 LaboratorioDigitalDocumento23 páginasPRACTICA 1 LaboratorioDigitalRonald Molina FariasAún no hay calificaciones

- Diseño de Circuitos LogicosDocumento36 páginasDiseño de Circuitos LogicosFabian CasteloAún no hay calificaciones

- Diseño Logico T2 PDFDocumento178 páginasDiseño Logico T2 PDFISTHAR CAHUM MARRUFFOAún no hay calificaciones

- Compuertas LógicasDocumento5 páginasCompuertas LógicasKATHERINE SANTAMARIAAún no hay calificaciones

- Algebra BoleanaDocumento10 páginasAlgebra BoleanaTavoVillanuevaAún no hay calificaciones

- Taller Simulador ZelioSoftDocumento9 páginasTaller Simulador ZelioSoftDaniel DelgadoAún no hay calificaciones

- Circuito Integrado 7408Documento3 páginasCircuito Integrado 7408Raul Rivera67% (3)

- Sumador 4 BitsDocumento8 páginasSumador 4 Bitsalejandro gonzalez unzueta100% (1)

- Angel Manuel - Rubio - Ortega02Documento8 páginasAngel Manuel - Rubio - Ortega02pepeAún no hay calificaciones

- Ejemplo Contador Del 0 Al 99Documento16 páginasEjemplo Contador Del 0 Al 99George MoreloAún no hay calificaciones

- Aplicación Lógica CombinacionalDocumento1 páginaAplicación Lógica CombinacionalJesus Rene Arocutipa CentellasAún no hay calificaciones

- Cuestionario Previo 6 Diseño Digital FI UNAMDocumento3 páginasCuestionario Previo 6 Diseño Digital FI UNAMPandaAún no hay calificaciones

- Compuertas Funciones LogoDocumento4 páginasCompuertas Funciones Logogfc12345678100% (2)

- Clase 7Documento28 páginasClase 7angel ruizAún no hay calificaciones

- Transparencias VHDLDocumento21 páginasTransparencias VHDLNeyder OrdoñezAún no hay calificaciones

- Taller SumadorDocumento3 páginasTaller Sumadorjose5torres-7Aún no hay calificaciones

- Símbolos EléctricosDocumento54 páginasSímbolos Eléctricosmoyter1981Aún no hay calificaciones

- Ii2012Apunte Teorico-Practico - Parte IDocumento84 páginasIi2012Apunte Teorico-Practico - Parte ILlanes GabrielAún no hay calificaciones