Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Manual Practicas Sistemas Logicos PDF

Manual Practicas Sistemas Logicos PDF

Cargado por

erteduTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Manual Practicas Sistemas Logicos PDF

Manual Practicas Sistemas Logicos PDF

Cargado por

erteduCopyright:

Formatos disponibles

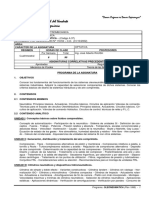

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

PRCTICA 1. PRINCIPIOS DE LAS COMPUERTAS LGICAS DIGITALES

OBJETIVOS

Conocer y clasificar las principales compuertas lgicas comerciales.

Diferenciar las tecnologas TTL y CMOS

MARCO TERICO

1. TECNOLOGAS BIPOLARES (TTL) Y MOS (CMOS)

1.1. TTL Transistor - Transistor Logic. (emplea transistores BJT)

Caractersticas:

- Velocidad de transferencia elevada

- Tensiones de alimentacin limitadas (tpicamente 5V +/- 5%)

1.2. CMOS o MOS complementaria Utiliza transistores NMOS y PMOS

Caractersticas:

- Menor consumo de energa que TTL.

- Gran flexibilidad en las tensiones de alimentacin.

2. INTEGRACIN DE CIRCUITOS

SSI: Small Scale of Integration, (unas pocas compuertas)

MSI: Medium Scale of Integration, (hasta 100 compuertas)

LSI: Large Scale of Integration, (de 100 a 1000 compuertas)

VLSI: Very Large Scale of Integration, (Ms de 1000 compuertas)

3. NIVELES DE TENSIN

Seales digitales 0 - V

L

(Tierra, Ground, GND, 0V)

1 - V

H

(VCC, VDD, 5V)

Debido al ruido (interferencias electromagnticas) es necesario asignar a los valores V

L

y

V

H

un pequeo margen de tensin alrededor de su valor nominal.

3.1. Tensiones TTL

Tensin de alimentacin suele ser 5V VCC = 5V.

_____________________________________________________________________________

ITESM Campus Toluca CVH

1

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Parmetros bsicos del estndar de tensiones TTL:

Para las salidas:

0V 0,4 valor de nivel de tensin bajo V

L

garantizado por el fabricante para una salida

(V

OL

).

2,4V 5V valor de nivel de tensin alto V

H

garantizado para una salida (V

OH

).

Para las entradas:

0V 0,8 rango de valores aceptado para una entrada de nivel bajo V

L

(0 lgico V

IL

).

2V 5V rango de valores aceptado para una entrada de nivel alto V

H

(1 lgico V

IH

).

4. MARGEN DE RUIDO N.M. (Noise Margen)

Es el margen de tensin que se tiene entre los niveles de tensin de entrada y salida de una

puerta lgica, considerando un funcionamiento correcto.

Definido matemticamente:

NM

H

= V

IH

- V

OH

= V

OH min

- V

IH min

NM

L

= V

IL

V

OL

= V

IL max

V

OL max

El margen de ruido es el mnimo de NM

H

y NM

L

, y para que una tecnologa digital

funcione, siempre ha de ser positivo.

Para la tecnologa TTL NM = 0,4 V

_____________________________________________________________________________

ITESM Campus Toluca CVH

2

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Si se excede margen de ruido, la salida de un circuito es impredecible. El margen de ruido

que se le permite a una determinada tecnologa digital reduce la susceptibilidad a errores

inducidos por ruido y mejora la fiabilidad de los equipos electrnicos digitales.

5. NIVELES DE CORRIENTE

Son los valores de corriente de entrada y de salida que garantiza el fabricante de una

determinada tecnologa digital. Se definen 4 niveles de corriente (para las entradas y para

las salidas) ya sea teniendo un 0 un 1.

I

IH

High-Level Input Current

La corriente de entrada por una puerta cuando se aplica una tensin de nivel alto a esa

entrada. Es una corriente positiva dado que entra hacia la puerta.

I

IL

Low-Level Input Current

La corriente de entrada por una puerta cuando se aplica una tensin de nivel bajo a esa

entrada. Es una corriente negativa dado que sale de la puerta.

I

OH

High-Level Output Current

La corriente de salida por una puerta cuando establece un nivel de tensin alto en la misma.

Es una corriente que sale y por tanto negativa.

I

OL

Low-Level Output Current

La corriente de salida por una puerta cuando establece un nivel de tensin bajo en la

misma. Es una corriente que entra y por tanto positiva.

El fabricante, para cada tecnologa digital, indica los valores mnimos, tpicos y mximos.

Para que una tecnologa funcione:

I

OH min

> I

IH max

y I

OL min

> I

IL max

6. FAN-OUT

Debido a la energa mxima que una compuerta puede absorber o consumir se impone un

lmite en el nmero mximo de salidas que puede tener una puerta lgica. Es lo que se

conoce como FAN-OUT (Ver figura 1). Para TTL el valor tpico es 10 y para CMOS.

I = I

1

+ I

2

+ . + I

N

Para calcular el fan-out, se debe aplicar la siguiente expresin matemtica:

=

max IH

min OH

max IL

min OL

I

I

,

I

I

min Fan - Out

_____________________________________________________________________________

ITESM Campus Toluca CVH

3

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Figura 1. Fan-Out.

7. RETARDO DE LAS COMPUERTAS LGICAS

Siempre existe un retardo entre la entrada y la salida de cualquier circuito electrnico

(retardo de propagacin)

Ej. Inversor Ideal:

En realidad existe un retardo, t

pd

(propagation delay) retardo de propagacin.

Se puede modelar un inversor real como un inversor ideal en serie con un bloque de retardo

de propagacin.

_____________________________________________________________________________

ITESM Campus Toluca CVH

4

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

A menudo, los fabricantes, distinguen entre el retardo de pasar de V

L

a V

H

y el de pasar de

V

H

a V

L

La nomenclatura utilizada es: t

pdLH

y t

pdHL

8. CONSUMO DE LAS COMPUERTAS LGICAS

Es la potencia (Watts) disipada por el circuito

Normalmente la potencia esta limitada a un valor mximo para evitar la destruccin del

dispositivo.

hPotencia o Consumo esttico

P = V

CC

I

CC

hPotencia o Consumo dinmico

Mayor frecuencia = Mayor consumo

9. SALIDAS EN DRENADOR Y COLECTOR ABIERTO

Salida en drenador abierto MOS

Salida en colector abierto TTL

El usuario de debe encargar de aadir una resistencia externa para obtener un

funcionamiento correcto del dispositivo.

Ejemplo: Diagrama electrnico de una compuerta NAND de 2 entradas en tecnologa TTL

(bipolar).

_____________________________________________________________________________

ITESM Campus Toluca CVH

5

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Aplicaciones tpicas:

Flexibilidad en el diseo con distintas tecnologas y distintas tensiones de alimentacin.

Ejemplo:

Otra aplicacin tpica de este tipo de tecnologa de fabricacin es la implementacin de

buses de datos.

MATERIAL Y EQUIPO

- 1 Compuerta 74LS04

- 1 Compuerta 74LS08

- 1 Compuerta 74LS32

- 1 Compuerta 74LS00

- 1 Compuerta 74LS02

- 1 Fuente de alimentacin

- 1 Multmetro

- 1 Punta lgica

DESARROLLO

1. Buscar informacin sobre las compuertas lgicas comerciales que se indican en la tabla

1 y llenar los campos faltantes.

_____________________________________________________________________________

ITESM Campus Toluca CVH

6

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

TTL CMOS

Voltaje de alimentacin

VOH

VOL

VIH

VIL

IOH

IOL

IIH

IIL

Margen de ruido

Fan-Out

Retardo

Tabla 1. Valores tpicos para las tecnologas TTL y CMOS.

2. Probar prcticamente la tabla de verdad para cada compuerta de la tabla 2.

Esquema Tipo Matrcula

Not 74LS04

And 74LS08

Or 74LS32

Nand 74LS00

Nor 74LS02

Tabla 2. Compuertas lgicas ms comunes.

3. Calcule el valor de resistencia y disipacin de potencia cuando se conecta un LED a la

salida de un inversor de colector abierto 74LS06, si la corriente demandada es 15mA.

Notas:

1. La manera correcta de conectar una carga a una compuerta TTL es como es muestra en

la figura 1.

Figura 1. Conexin de una carga para compuertas TTL.

_____________________________________________________________________________

ITESM Campus Toluca CVH

7

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

_____________________________________________________________________________

ITESM Campus Toluca CVH

8

2. Las entradas de las compuertas TTL que no se conectaron son consideradas por lo

general como unos lgicos, aunque pueden variar en cualquier momento y producir errores.

Es altamente recomendable conectarlas a V

CC

o Tierra segn sea necesario.

3. Las entradas de las compuertas CMOS deben conectarse obligatoriamente ya sea a V

CC

o

a Tierra, de lo contrario el dispositivo se puede daar. Esta tecnologa es altamente sensible

a cargas estticas.

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

PRCTICA 2. DETECTOR DE NIVEL

OBJETIVOS

Aprender a realizar interfases TTL - Componentes analgicos.

Implementar funciones booleanas utilizando las compuertas comerciales

MARCO TERICO

1. SENSORES

1.1. Sensores pticos

Este tipo de dispositivos a menudo son llamados fotodetectores. En este caso, la energa

luminosa que entra al cristal de semiconductor excita a los electrones a niveles ms altos de

energa, dejando huecos atrs. Posteriormente estos electrones y huecos se alejan unos de

otros, conformando una corriente elctrica.

Entre los principales fotodetectores se pueden encontrar y clasificar los siguientes:

Fotoemisores, que emiten electrones cuando existe energa radiante que incide sobre

material sensible a dicha radiacin. Dentro de esta categora encontramos:

Fototransitores

LASCR (Light Sensitive Sillicon Controlled Rectifier)

Fotoconductores, que cambian su resistencia elctrica debido a la exposicin a energa

radiante. Ejemplos:

Fotoresistores

Fotodiodo

Fotovoltaicos los cuales generan un voltaje al exponerse a energa radiante. Ejemplo:

Fotoceldas

1.1.1. El Fototransistor

_____________________________________________________________________________

ITESM Campus Toluca CVH

1

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

El fototransistor es un dispositivo electrnico que genera energa elctrica a partir de

energa luminosa. Funciona de manera muy semejante a un transistor comn, con la

diferencia de que la corriente de base se obtiene por la incidencia de luz sobre una regin

de base amplia y expuesta.

El funcionamiento de un fototransistor es el siguiente:

Al exponer el fototransistor a la luz, los fotones entran en contacto con la base del mismo,

generando huecos y con ello una corriente de base que hace que el transistor entre en la

regin activa, y se presente una corriente de colector a emisor. Es decir, los fotones en este

caso, reemplazan la corriente de base que normalmente se aplica elctricamente. Es por

este motivo que a menudo la terminal correspondiente a la base est ausente del transistor.

La caracterstica ms sobresaliente de un fototransistor es que permite detectar luz y

amplificar mediante el uso de un slo dispositivo.

Figura 1. El fototransistor.

La figura 1 muestra un fototransistor, La parte exterior del fototransistor est hecha de un

material llamado epoxy, que es una resina que permite el ingreso de radiacin hacia la base

del transistor

El fototransistor se conecta en la configuracin de corte y saturacin para obtener niveles

lgicos dependiendo de la presencia o ausencia de luz.

1.2. Sensores de temperatura.

Son aquellos dispositivos electrnicos que convierten una seal calorfica en una seal

elctrica. Existen diferentes tipos de sensores trmicos como:

Termopar. Est constituido por dos alambres metlicos diferentes que, unidos,

desarrollan una diferencia de voltaje entre sus extremos libres que es aproximadamente

proporcional a la diferencia de temperaturas entre estas puntas y la unin.

Termistor y RTD. Son elementos cuya resistencia varia conforme se modifica la

temperatura.

Sensores semiconductores. Los hay del tipo de diodo o CI. Este tipo de dispositivos

varan su voltaje con respecto a la temperatura, la ventaja de los CIs es que su salida es

lineal en un intervalo muy amplio.

_____________________________________________________________________________

ITESM Campus Toluca CVH

2

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

1.2.1. Sensor LM35

Los sensores LM35 son sensores de temperatura de precisin en circuito integrado (CI)

cuya salida es linealmente proporcional a la temperatura en grados Celsius. Este tipo de

sensores entregan 10 mV/C y su conexin solo consiste en polarizar el dispositivo tal y

como se ve en la figura 2.

Figura 2. Conexin de un sensor de temperatura LM35.

2. COMPARADORES

Los comparadores se construyen con amplificadores operacionales y generalmente su salida

varia entre +Vsat. La figura 3 ilustra las terminales de un amplificador operacional.

Figura 3. Las terminales del amplificador operacional.

Un comparador en lazo abierto es bsicamente un amplificador operacional polarizado con

dos seales en las terminales de entrada para ser comparadas. Existen dos tipos de

comparadores dependiendo de la terminal que se utilice para introducir la seal a comparar.

Si la seal se introduce por la entrada inversora el comparador es inversor y su

comportamiento es el de la figura 4.

Figura 4. Comparador inversor.

_____________________________________________________________________________

ITESM Campus Toluca CVH

3

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Si la seal se introduce por la entrada no inversora el comparador es no inversor y su

comportamiento es el de la figura 5.

Figura 5. Comparador no inversor.

MATERIAL Y EQUIPO

- Compuertas TTL

- 1 Amplificador operacional LM324

- 2 Fototransistores

- 2 LM35

- 1 Fuente de alimentacin

- 1 Multmetro

- 1 Punta lgica

DESARROLLO

1. Resolver el problema dado y obtener la funcin de salida.

2. Implementarlo fsicamente usando el nmero mnimo de compuertas.

Problema

En una planta qumica existen cuatro tanques que contienen lquidos que estn siendo

calentados. Se usan sensores de nivel de lquido para detectar cundo en los tanques A y B

el nivel sube por encima de un nivel mximo prefijado, sensores de temperatura en los

tanques C y D que detectan cundo la temperatura en esos tanques esta por arriba de un

lmite. Supngase que las salidas de los sensores de nivel lquido A y B estn bajas cuando

el nivel es satisfactorio y altas cuando llegan al nivel mximo. Las salidas de los sensores C

y D son bajas cuando la temperatura es satisfactoria y altas en caso contrario.

Disear un circuito lgico que detecte cundo el nivel en el tanque A o en el B es alto y al

mismo tiempo la temperatura en cualquiera de los tanques C o D es alta (este no es un caso

real, solo sirve como ejemplo).

_____________________________________________________________________________

ITESM Campus Toluca CVH

4

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

_____________________________________________________________________________

ITESM Campus Toluca CVH

5

Sugerencia: Utilice como base el diagrama de bloques que se ilustra en la figura 6. Tome

en cuenta que en el diagrama se consideran salidas altas de los sensores para las seales

pticas y de temperatura evitando el uso de inversores en la lgica de compuertas.

Figura 6. Diagrama de bloques para el problema propuesto.

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

PRCTICA 3. Reduccin e implementacin de funciones utilizando mapas de karnaugh

OBJETIVOS

Reducir la funcin lgica para cada segmento en un decodificador BCD a 7 segmentos.

Implementar las funciones booleanas utilizando el menor nmero de compuertas.

MARCO TERICO

1. Reduccin mediante mapas de Karnaugh

El mtodo que a continuacin se describe sirve para reducir funciones lgicas de monomios

de cuatro variables. Para facilitar su comprensin se utilizar un ejemplo resuelto paso a

paso.

Ejemplo: La prctica dos de este manual consista de un problema de cuatro tanques

controlados por nivel y temperatura. La condicin del problema es: encender una alarma si

se sobrepasa el lmite del tanque A o del B y si se excede la temperatura del tanque C o del

D.

La solucin al problema que se obtuvo de manera intuitiva fue S = (A+B)(C+D). Qu

sucede si queremos obtener la funcin en monomios de manera analtica? Una opcin es

utilizar mapas de Karnaugh como se ilustra a continuacin.

1. Primero se realiza la tabla de verdad para las diecisis posibles combinaciones

producidas por las cuatro entradas.

ABCD S

0000 0

0001 0

0010 0

0011 0

0100 0

0101 1

0110 1

0111 1

1000 0

1001 1

1010 1

1011 1

1100 0

1101 1

1110 1

1111 1

_____________________________________________________________________________

ITESM Campus Toluca CVH

1

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

2. Despus se vacan los datos en una tabla de cuatro por cuatro ubicando cada uno o

cero en la coordenada que le corresponde por nombre y valor de la entrada (i.e.

entrada A con valor 00, etc.)

AB

CD 00 01 11 10

00 0 0 0 0

01 0 1 1 1

11 0 1 1 1

10 0 1 1 1

3. Agrupe los unos de la tabla en paquetes que sean potencias de dos. Para saber si se

agrupo correctamente realice el siguiente clculo 2

n

; n = Entradas en el mapa nmero

de entradas que forman la funcin, el resultado debe ser igual al nmero de unos que

agrupo.

AB

CD 00 01 11 10

00 0 0 0 0

01 0 1 1 1

11 0 1 1 1

10 0 1 1 1

4. Obtenga la funcin parcial de cada grupo considerando solamente las entradas que no

cambian de cada agrupacin. Las entradas que corresponden tanto a filas como a

columnas se consideran como tal si tienen el valor de uno, y como negadas si tienen el

valor de cero.

Por ejemplo, para la agrupacin superior izquierda de la tabla se tiene el siguiente

componente del monomio: BD

Y el monomio total es: S = AC + AD + BC + BD

2. Desplegadores de 7 segmentos

Los desplegadores estan compuestos de 7 leds rectangulares llamados segmentos. Cada

segmento tiene una letra asignada, comienza con la a y termina con la f. Se enumeran

en el sentido de las manecillas del reloj comenzando con el segmento superior. Existen dos

tipos de desplegadores, los de nodo comn y los de ctodo comn, la diferencia es que los

primeros se activan con niveles lgicos cero y los segundos con niveles lgicos uno.

Para ilustrar su funcionamiento se utilizar un desplegador de ctodo comn, que

internamente se vera as:

_____________________________________________________________________________

ITESM Campus Toluca CVH

2

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Usualmente funcionan con 5V y una corriente de 12mA, las caractersticas exactas as

como la asignacin de terminales se puede revisar en los manuales.

Con un solo desplegador se pueden formar los nmeros decimales del 0 al 9 (se

utilizan decodificadores BCD-7 segmentos) o los nmeros hexadecimales del 0 al F

(utilizando decodificadores hexadecimal-7 segmentos).

Si se desea obtener por ejemplo la tabla de un decodificador hexadecimal a 7 segmentos

basta con escribir en cuatro columnas de entrada las16 posibles combinaciones binarias y

en siete columnas de salida las 16 combinaciones correspondientes, tal y como se muestra

a continuacin:

Entradas Salidas

Hex D C B A g f E d c b a

0 0 0 0 0 0 1 1 1 1 1 1

1 0 0 0 1 0 0 0 0 1 1 0

2 0 0 1 0 1 0 1 1 0 1 1

3 0 0 1 1 1 0 0 1 1 1 1

4 0 1 0 0 1 1 0 0 1 1 0

5 0 1 0 1 1 1 0 1 1 0 1

6 0 1 1 0 1 1 1 1 1 0 1

7 0 1 1 1 1 0 0 0 1 1 1

8 1 0 0 0 1 1 1 1 1 1 1

9 1 0 0 1 1 1 0 0 1 1 1

A 1 0 1 0 1 1 1 0 1 1 1

B 1 0 1 1 1 1 1 1 1 0 0

C 1 1 0 0 0 1 1 1 0 0 1

D 1 1 0 1 0 1 1 1 1 1 0

E 1 1 1 0 1 1 1 1 0 0 1

F 1 1 1 1 1 1 1 0 0 0 1

Tabla 1. Decodificacin BCD/Hexadeciaml a 7 segmentos.

_____________________________________________________________________________

ITESM Campus Toluca CVH

3

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Como se puede observar en la tabla 1 solo se enva a uno el segmento que se desea

iluminar, de esta forma para desplegar un 8 se iluminan todos los segmentos, la palabra

hexadecimal que se genera para la salida es FF o 7F. Ambas palabras tienen el mismo

efecto cuando a es el bit menos significativo.

3. Implementacin con compuertas NAND

La implementacin con compuertas NAND es muy utilizada para implementar monomios.

Generalmente se utilizan compuertas CMOS por que tienen un mayor numero de entradas

por dispositivo. Para ilustrar su uso se implementar el siguiente monomio.

S = /BC + ABC + /A/C (La diagonal indica negacin)

El circuito con compuertas NAND queda de la siguiente manera:

La razn es la siguiente:

La salida de la compuerta 1 es: /(/BC)

La salida de la compuerta 2 es: /(ABC)

La salida de la compuerta 3 es: /(/A/C)

La salida de la compuerta 4 es: / (/(/BC)* /(ABC)* /(/A/C))

Aplicando DMorgan a la salida tenemos: //(/BC) + //(ABC) + //(/A/C)

Que simplificando es igual al monomio: /BC + ABC + /A/C

MATERIAL Y EQUIPO

- Compuertas TTL

- 1 Dip Switch

- 1 Desplegador de 7 segmentos

- Resisitencias

- 1 Fuente de alimentacin

- 1 Multmetro

- 1 Punta lgica

_____________________________________________________________________________

ITESM Campus Toluca CVH

4

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

_____________________________________________________________________________

ITESM Campus Toluca CVH

5

DESARROLLO

1. Obtenga los siete mapas de karnaugh correspondientes a cada segmento para realizar un

decodificador BCD a 7 Segmentos a partir de la tabla 1.

2. Implemente los segmentos a, b y c utilizando compuertas NAND CMOS, utilize

aquellas cuyo nmero de entradas sea el ms adecuado.

3. Conecte los tres circuitos de segmentos como se ilustra a continuacin.

Circuito simplificado para tres segmentos del decodificador BCD- 7 Segmentos.

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

PRCTICA 4. Grabacin y lectura de una memoria RAM 6116

OBJETIVOS

Aprender a leer y escribir un dato en una memoria RAM

Utilizar correctamente los buffers para evitar corto circuito y aumentar la corriente.

MARCO TERICO

La memoria 6116 es una memoria de acceso aleatorio de 2k bytes. El bus de direcciones

consta de once terminales (2

11

=2048), el bit menos significativo es A0 y el ms

significativo es A10. El bus de datos es de 8 bits y va desde D0 hasta D7. Tiene adems una

terminal de habilitacin (Chip Select), una que indica modo lectura (WR) y otra para modo

escritura ( RD), todas ellas son activas en bajo.

El bus de direcciones sirve como apuntador de la tabla y el de datos es para leer o escribir

el contenido de los campos, por ejemplo:

21

12

12

13

4

3

2

1

0

Direccin

En est tabla el bus de direcciones contiene el nmero 1, y el dato de esa direccin es 12,

que pude ser ledo por el bus de datos. Si por ejemplo desea escribir un 8 en la direccin 4,

se pone este nmero en el bus de direcciones y un 8 en el bus de datos.

_____________________________________________________________________________

ITESM Campus Toluca CVH

1

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

El bus de datos es bidireccional (I/0), es decir, por el salen y entran los datos, pero no

simultneamente. En el momento en que entran los datos a la memoria se le llamar

operacin de escritura y al momento en que salen operacin de lectura.

El diagrama de tiempos de la operacin de lectura se muestra a continuacin.

Operacin de escritura tiene el siguiente diagrama de tiempos.

Los diagramas de tiempos muestran el orden en que se deben introducir las seales

(address, CS, WE o OE) para escribir o leer adecuadamente una localidad de memoria. La

siguiente tabla muestra la combinacin de estas seales para ambas operaciones.

_____________________________________________________________________________

ITESM Campus Toluca CVH

2

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

MATERIAL Y EQUIPO

- Una memoria RAM 6116

- 2 Dip Switch

- 1 Desplegador de 7 segmentos

- 2 Buffers 74245

- Resisitencias

- 1 Fuente de alimentacin

- 1 Multmetro

- 1 Punta lgica

DESARROLLO

Construya un circuito para escribir y leer datos en una memoria RAM 6116. Para facilitar

la construccin de dicho circuito primero lea la siguiente explicacin.

Cuando se ejecuta una operacin de grabacin se tienen niveles externos de voltaje a la

entrada de las terminales (son los datos de entrada). Cuando se realiza la operacin de

lectura tambin hay niveles de voltaje en las terminales, solo que ente caso son internos. Si

se lee alguna localidad de memoria cuando hay un dato de entrada presente se tendr sin

lugar a dudas un corto en el bus de datos. Para evitarlo es necesario que el bus de datos este

en tercer estado al momento de leer la memoria, para ello se utiliza entonces un buffer

bidireccional, en este caso se utilizar el 74LS245. Con el propsito de evitar que ambas

operaciones se presenten al mismo tiempo se utiliza un inversor entre las terminales WR y

RD.

El buffer 74LS245 tambin sirve para incrementar la corriente, si desea conectar una carga

a la memoria se debe pasar primero por un buffer.

Construya el circuito de la figura 2 y almacene en las primeras 16 localidades de memoria

los datos necesarios para que el desplegador de 7 segmentos muestre los nmeros del 0 al F

hex, segn sea la localidad de memoria escogida. Para conectar la memoria guese en el la

figura 1.

Figura 1. Asignacin de terminales.

_____________________________________________________________________________

ITESM Campus Toluca CVH

3

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

_____________________________________________________________________________

ITESM Campus Toluca CVH

4

Grabacin de la memoria RAM

1. Deshabilitar la memora (poner CS a uno)

2. Poner en el bus la direccin en la cual se desea escribir

3. Poner a WRcero y RD a uno.

4. Poner el dato a grabar en el bus de datos.

5. Activar CS (mandarlo a cero con un pulso).

Lectura de la memoria RAM

1. Deshabilitar la memora (poner CS a uno)

2. Poner en el bus la direccin que se desea leer.

3. Poner a WRuno y RD a cero.

4. Asegurarse de que no existan datos en el bus de datos.

5. Activar CS (mandarlo a cero con un pulso).

Nota:

En el circuito no se han polarizado los integrados, las terminales no usadas de la memoria

deben conectarse a tierra mediante una resistencia de 10k. Se muestra como introducir los

datos para evitar cortos pues el bus es bidireccional, sin embargo las direcciones son solo

puertos de entrada y basta con introducirlas con un micro interruptor (dip switch).

Figura 1. Circuito propuesto.

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

PRCTICA 5. Calculadora con GAL

OBJETIVOS

Reducir la funcin lgica para cada operacin aritmtica que se indique.

Implementar las funciones booleanas utilizando GALs.

MARCO TERICO

Los GALs (Generic Array Logic) son arreglos de compuertas basados en celdas

reconfigurables con tecnologa E

2

CMOS (Elctricamente borrable). Este arreglo permite

implementar funciones booleanas mediante programacin. Por ejemplo, en la siguiente

figura se ilustra la implementacin de la funcin X=/AB+AB+/A/B.

Para generar el cdigo del GAL se utilizan programas como ABEL, Foundation, Palasm,

entre otros. En este caso se utilizar Palasm, para lo cual siga los siguientes pasos:

Primero realice su programa en cualquier editor de textos observando el siguiente patrn:

;---------------------------------- Declaration Segment ------------

TITLE EJEMPLO.PDS

PATTERN A

REVISION 1.0

AUTHOR YO

COMPANY ITESM

DATE 31/04/2002

CHIP DECODER PAL16V8

;---------------------------------- PIN Declarations ---------------

_____________________________________________________________________________

ITESM Campus Toluca CVH

1

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

PIN 2 A COMBINATORIAL ; INPUT

PIN 3 B COMBINATORIAL ; INPUT

PIN 10 GND ; INPUT

PIN 12 SA1 COMBINATORIAL ; OUTPUT

PIN 13 SA3 COMBINATORIAL ; OUTPUT

PIN 20 VCC ; INPUT

;----------------------------------- Boolean Equation Segment ------

EQUATIONS

SA1 = /A

SA3 = /B

;---- Este programa funciona como inversor de las entradas A y B -----

El programa comienza con la declaracin de segmento en donde escribimos el ttulo

(Nombre de nuestro archivo con extensin pds), patrn, revisin, autor compaa y fecha.

El ltimo segmento es el GAL que se va a utilizar y es muy importante que coincida con el

que se tiene fsicamente.

En la declaracin de terminales se pone el nmero de terminal, el nombre que desea darle,

el tipo de terminal (combinatoria o secuencial) y su funcin (entrada o salida).

En la seccin de ecuaciones se edita la ecuacin comenzando con el nombre de la terminal

de salida, el signo de igual y la ecuacin en funcin de las variables de salida. La operacin

AND, OR y NOT se realizan con los smbolos *, + y / respectivamente.

Una vez terminado el programa guardarlo como archivo de texto utilizando la extensin

pds.

Para compilar el programa se utiliza el paquete Palasm, al abrirlo primero hay que cargar

el archivo como se muestra

_____________________________________________________________________________

ITESM Campus Toluca CVH

2

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Entonces aparece una ventana en donde escribimos el nombre del archivo con extensin

pds, si no lo encuentra cambie primero el directorio hacia la ubicacin del archivo, para

aceptar teclee F10 en todos los casos. Una vez cargado se podr leer en el recuadro inferior

derecho el nombre del archivo y el GAL que utilizar.

Para compilar haga lo siguiente

Este proceso generar un archivo con el mismo nombre que el de su diseo pero con

extensin jed. Este archivo es el que se tiene que cargar en el GAL, para ello se utiliza el

programa SP3. Al abrirlo primero se tiene que cargar el archivo jed que ha sido creado

como se ilustra:

_____________________________________________________________________________

ITESM Campus Toluca CVH

3

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Ya que ha sido cargado hay que seleccionar el tipo de GAL, para ello escogemos la opcin

Select by Device

y aparece la siguiente ventana, en la cual seleccionamos la matricula base del GAL, el

fabricante y como tipo se escoge PLD, en este caso se ha seleccionado un GAL16V8 (que

es lo que se escribi en la declaracin de segmento del programa).

Hecho lo anterior es momento de programar el GAL, para ello se selecciona Funtion Select

_____________________________________________________________________________

ITESM Campus Toluca CVH

4

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

entonces aparece una ventana sobre la cual se presiona Run para as concluir con la

programacin del GAL.

MATERIAL Y EQUIPO

- 2 Gal 16V8

- 2 Dip Switch

- 2 Desplegadores de 7 segmentos

- 2 Decodificadores BCD - 7 segmentos 74LS48

- 4 Buffers 74LS245

- Resisitencias

- 1 Fuente de alimentacin

- 1 Multmetro

- 1 Punta lgica

DESARROLLO

La prctica consiste en construir una calculadora que realice las siguientes operaciones con

enteros: suma, resta, multiplicacin y divisin.

1. Obtenga los siete mapas de karnaugh correspondientes a cada operacin.

2. Implemente todas las operaciones utilizando dos GALs (uno para multiplicacin y

suma, el otro para resta y divisin).

3. Conecte los dos GALs a los decodificadores utilizando buffers para evitar corto circuito

como se ilustra en la figura 2.

Como ejemplo se muestra cmo obtener la tabla de verdad para la multiplicacin de dos

nmeros de 2 bits.

_____________________________________________________________________________

ITESM Campus Toluca CVH

5

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

_____________________________________________________________________________

ITESM Campus Toluca CVH

6

A1 A0 B1 B0 M3 M2 M1 M0

0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 0

0 0 1 0 0 0 0 0

0 0 1 1 0 0 0 0

0 1 0 0 0 0 0 0

0 1 0 1 0 0 0 1

0 1 1 0 0 0 1 0

0 1 1 1 0 0 1 1

1 0 0 0 0 0 0 0

1 0 0 1 0 0 1 0

1 0 1 0 0 1 0 0

1 0 1 1 0 1 1 0

1 1 0 0 0 0 0 0

1 1 0 1 0 0 1 1

1 1 1 0 0 1 1 0

1 1 1 1 1 0 0 1

Tabla 1. Tabla de verdad de la multiplicacin.

La operacin de suma ser para dos nmeros de tres bits. La operacin de resta es para dos

nmeros de tres bits y un signo (solo signo en el resultado), y la operacin de divisin para

dos nmeros de tres bits indicando solamente como resultado un nmero entero (ej. 5/2=2).

Figura 2. Diagrama a bloques de la calculadora

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

PRCTICA 6. Banda transportadora

OBJETIVOS

Simular un proceso de manufactura utilizando GALs

Utilizar correctamente los contadores y los temporizadores.

MARCO TERICO

Contadores

Los contadores son dispositivos electrnicos que tienen su base en los divisores de

frecuencia. Para ilustrar su funcionamiento se dibujar el diagrama de tiempos de un divisor

de frecuencia, ver figura 1 .

Figura 1. Diagrama de tiempos de un divisor de frecuencia

Se puede observar que la seal de entrada (CLK) se divide por dos en QA y por cuatro en

QB. Sin embrago, el efecto que nos interesa es que cuando QB vale cero, QA vale cero y

CLK vale cero eso es el numero binario QB, QA, CLK = 000, cuando CLK cambia de cero

a uno entonces se tiene 001, y as sucesivamente hasta tener 111. Este es un contador de

tres bits y puede contar del cero al siete cclicamente.

El contador que se utilizar en est prctica es el 74LS190. Este contador permite contar

desde 0 hasta 9 (la salida esta en las terminales QA-QD), tiene una seal de reloj en donde

se introduce la seal del evento que se esta contando (CLK), dos seales de salida que

indican cuando se a concluido el conteo (RCO, MAX/MIN), cinco entradas para asignar un

nmero al inicio del conteo (LOAD, A-D), un habilitador (CTEN) y una terminal para

escoger entre conteo hacia arriba y conteo hacia abajo (D/U). Para conocer la asignacin de

las terminales y caractersticas elctricas del 74LS190 revise el manual TTL Data Book. En

la figura 2 se muestra la asignacin de terminales.

_____________________________________________________________________________

ITESM Campus Toluca CVH

1

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Figura 2. Asignacin de terminales del 74LS190.

Para entender el funcionamiento de este dispositivo es conveniente recurrir al diagrama de

tiempos del mismo. En la figura 3 se observa el diagrama de tiempos.

Figura 3. Diagrama de tiempos del contador 75LS190.

_____________________________________________________________________________

ITESM Campus Toluca CVH

2

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Temporizadores

Los temporizadores son dispositivos que permiten controlar el tiempo que dura un evento.

En esta prctica se utilizar un circuito integrado electrnico con matricula LM555. Este

dispositivo analgico funciona bsicamente con un par de comparadores (amplificadores

operacionales), transistores y Flip-Flops.

El temporizador LM355 tiene diferentes aplicaciones segn sea el modo de operacin con

el que se trabaje, a nosotros nos interesa el modo de oscilador monoestable. En este modo

el circuito se dispara por cierto tiempo despus de que ha recibido un pulso de inicio. La

duracin del pulso de salida esta determinada por un capacitor y una resistencia mediante la

siguiente frmula (Se obtiene el perodo):

T = 1.1 R

A

C

o directamente a partir de la siguiente tabla:

Finalmente, el circuito del 555 como oscilador monoestable es el siguiente:

Donde la entrada es por la terminal 2 (Trigger), y la salida por la 3. El voltaje de

alimentacin entre 5 y 15 Volts.

_____________________________________________________________________________

ITESM Campus Toluca CVH

3

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

MATERIAL Y EQUIPO

- Un temporizador LM555

- Un contador 74LS190

- 2 Motores de CD

- 2 Bandas transportadoras

- Un GAL

- Un decodificador de BCD a 7 segmentos

- Un desplegador de 7 segmentos

DESARROLLO

Disear e implementar el proceso que se explica a continuacin. Un sistema consta de dos

bandas transportadoras (B1 y B2). La banda 1 transporta pequeas piezas que han de ser

trabajadas y posteriormente acumuladas en una caja. La banda 2 contiene cajas, cada caja

contendr nueve piezas que han sido anteriormente procesadas. El siguiente diagrama

facilita la comprensin del proceso:

Figura 4. Diagrama del proceso.

La banda 1 y la banda 2 son perpendiculares, tanto las piezas como las cajas se colocan con

la mano al inicio de la banda. El sensor queda libre a eleccin del estudiante, el proceso

debe ser creativo, no es necesario que trabaje realmente sobre la pieza pero tampoco puede

ser que se encienda un led.

Los pasos para el funcionamiento del proceso son:

1. El sistema inicia apagado, sin piezas en la banda 1 ni caja en la banda 2, las dos bandas,

el proceso y el temporizador estn apagados.

2. Se enciende el interruptor (On/Off), automticamente se enciende la banda 2 y se

detiene hasta que el sensor 2 indique que la caja esta en posicin para recibir las piezas.

3. Comienza a moverse la banda 1.

_____________________________________________________________________________

ITESM Campus Toluca CVH

4

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

_____________________________________________________________________________

ITESM Campus Toluca CVH

5

4. Cuado el sensor 1 detecta la pieza se manda el pulso de inicio para el temporizador y

comienza el proceso (la banda uno sigue caminado), Un segundo temporizador con

tiempo mayor que T1 da tiempo para que la pieza acabe de recorrer la banda y caiga en

la caja.

5. La novena pieza debe ser procesada y caer en la caja, despus se detendr la banda 1 y

comienza a moverse la bada 2, se resetea el contador y se espera una nueva caja en la

banda 2 para iniciar el ciclo nuevamente.

Este problema se debe resolver en pasos:

Primero arme los temporizadores, el contador y el sensor.

Comience la construccin de las bandas.

Construya el circuito de potencia para encender los motores.

Realice la tabla de verdad de el ciclo, considere todos los sensores y actuadotes del

sistema.

Implemente las funciones lgicas en un GAL.

Integre todos los circuitos y los componentes mecnicos.

Es muy importante ir probando el funcionamiento de cada etapa, no avance a la siguiente

etapa hasta que el circuito o dispositivo mecnico que este probando funcione

correctamente.

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

PRCTICA 8. Bandas transportadoras con PLC

OBJETIVOS

Simular un proceso de manufactura utilizando PLCs

Utilizar las funciones bsicas del PLC.

MARCO TERICO

Controladores Lgicos Programables (PLCs)

Los PLCs son dispositivos electrnicos que permiten almacenar una secuencia de ordenes y

ejecutarlas de forma cclica para realizar una tarea.

Aunque se podra pensar que es el equivalente a una computadora, existen diferencias entre

ambos. El PLC est diseado para trabajar en ambientes industriales, ejecutar su programa

de forma indefinida y es menos propenso a fallos que una computadora convencional.

Adems, su programacin est mas orientada al mbito industrial, incluso existen lenguajes

que "simulan" el comportamiento del equipo con el de un sistema de relevadores.

Tipos de PLCs

Existen dos tipos de PLCs, los modulares y los compactos. Los modulares como su nombre

lo indica estn compuestos por mdulos: modulo de entrada, salida, CPU, comunicaciones,

fuente de alimentacin, etc. Los compactos son PLC que no pueden crecer mas en

hardware, aunque son bastante tiles en aplicaciones sencillas. La figura 1 muestran

algunos componentes de un PLC modular S7-224.

Figura 1. Componentes de un PLC S7-224

Operaciones del PLC

Los PLCs soportan las siguientes operaciones:

Aritmticas. Como la suma, resta, divisin y multiplicacin.

Lgicas. Operaciones AND, OR, NOT, XOR

_____________________________________________________________________________

ITESM Campus Toluca CVH

1

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Comparacin. Pueden comparar bits, bytes, palabras y palabras dobles.

Temporizacin. Se realiza con un factor de escalamiento y una base de tiempo . (1, 10 o

100 ms)

Conteo. Se permiten operaciones de conteo tradicional y conteo rpido.

El ciclo de la CPU

La CPU S7-200 se ha previsto para que ejecute cclicamente una serie de tareas, incluyendo

el programa de usuario. Dicha ejecucin se denomina ciclo del PLC. Durante el ciclo que

se muestra en la figura 2, la CPU ejecuta la mayora de las tareas siguientes (o todas ellas):

Figura 2. Ciclo del PLC.

Lee las entradas.

Ejecuta el programa de usuario.

Procesa las peticiones de comunicacin.

Efecta un autodiagnstico.

Escribe en las salidas.

Leer las entradas digitales

Al principio de cada ciclo se leen los valores actuales de las entradas digitales y se escriben

en la imagen del proceso de las entradas. La CPU reserva un espacio de la imagen del

proceso de las entradas en incrementos de ocho bits (un byte). Si la CPU o el mdulo de

ampliacin no proveen una entrada fsica para cada bit del byte reservado, no ser posible

asignar dichos bits a los mdulos siguientes en la cadena de E/S o utilizarlos en el programa

de usuario. Al comienzo de cada ciclo, la CPU pone a 0 estos bits no utilizados en la

imagen del proceso. No obstante, si la CPU asiste varios mdulos de ampliacin y no se

est utilizando su capacidad de E/S (porque no se han instalado los mdulos de

ampliacin), los bits de entradas de ampliacin no utilizados se pueden usar como marcas

internas adicionales.

Ejecutar el programa

Durante esta fase del ciclo, la CPU ejecuta el programa desde la primera operacin hasta la

ltima. El control directo de las entradas y salidas permite acceder directamente a las

mismas mientras se ejecuta el programa o una rutina de interrupcin.

_____________________________________________________________________________

ITESM Campus Toluca CVH

2

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Adems, la CPU procesa los mensajes que haya recibido por el puerto de comunicacin.

Efectuar el autodiagnstico de la CPU

Durante el autodiagnstico se comprueba el firmware de la CPU y la memoria del

programa (slo en modo RUN), as como el estado de los mdulos de ampliacin.

Escribir en las salidas digitales

Al final de cada ciclo, la CPU escribe los valores de la imagen del proceso de las salidas en

las salidas digitales. La CPU reserva una espacio de la imagen del proceso de las salidas en

incrementos de ocho bits (un byte). Si la CPU o el mdulo de ampliacin no proveen una

salida fsica para cada bit del byte reservado, no ser posible asignar dichos bits a los

mdulos siguientes en la cadena de E/S.

MATERIAL Y EQUIPO

- Un PLC S7-224 o 216

- 2 Motores de CD

- 2 Bandas transportadoras

- Una PC con windows 95, 98 o NT y STEP 7 Micro WIn.

- Un decodificador de BCD a 7 segmentos

- Un desplegador de 7 segmentos

- Inversores 74LS06

DESARROLLO

Utilice el programa Step 7 para programar el PLC como se vio en clase. La conexin del

PLC se realiza como se lustra en la figura 3.

Figura 3. Conexin del PLC con la PC.

La forma de programar el PLC ha sido vista en clase, sin embargo para obtener informacin

detallada recurra al manual del PLC disponible en Course Documents de BlackBoard.

_____________________________________________________________________________

ITESM Campus Toluca CVH

3

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

_____________________________________________________________________________

ITESM Campus Toluca CVH

4

Esta prctica es equivalente a la practica nmero seis, solo que el problema se resuelve

utilizando las operaciones lgicas del PLC para implementar las funciones boolenanas

obtenidas para el GAL.

A diferencia de la prctica seis, no es necesario conectar los temporizadores o contadores

como dispositivos externos ya que estos se programan internamente en el PLC. Las

entradas al PLC se conectan en su mayora utilizando inversores de colector abierto para

conseguir los 24 volts requeridos. Las salidas son a relevador.

En la figura 4 se muestra el diagrama del proceso. Note que el funcionamiento del mismo

es exactamente igual al de la prctica 6. lo que cambia es el dispositivo electrnico con el

cual se resuelve el problema.

Figura 4. Diagrama del proceso.

Los pasos para el funcionamiento del proceso son:

1. El sistema inicia apagado, sin piezas en la banda 1 ni caja en la banda 2, las dos bandas,

el proceso y el temporizador estn apagados.

2. Se enciende el interruptor (On/Off), automticamente se enciende la banda 2 y se

detiene hasta que el sensor 2 indique que la caja esta en posicin para recibir las piezas.

3. Comienza a moverse la banda 1.

4. Cuado el sensor 1 detecta la pieza se manda el pulso de inicio para el temporizador y

comienza el proceso (la banda uno sigue caminado), Un segundo temporizador con

tiempo mayor que T1 da tiempo para que la pieza acabe de recorrer la banda y caiga en

la caja.

5. La novena pieza debe ser procesada y caer en la caja, despus se detendr la banda 1 y

comienza a moverse la bada 2, se resetea el contador y se espera una nueva caja en la

banda 2 para iniciar el ciclo nuevamente.

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

PRCTICA 9. Proceso secuencial con PLC

OBJETIVOS

Simular un proceso secuencial de manufactura utilizando PLCs

Utilizar las funciones de control secuencial del PLC.

MARCO TERICO

Un proceso secuencial es aquel que evoluciona en forma de pasos, es decir, cumple con las

etapas del proceso dependiendo de la variacin de las variables externas. Por ejemplo, el

proceso de una banda transportadora que se detiene al pasar una pieza seria como sigue:

El proceso comienza cuando la banda esta apagada, se cierra un interruptor y la banda

comienza a girar, cuando una pieza atraviesa un sensor se detiene durante 5 segundos y

despus se vuelve a encender hasta que cruce otra pieza.

Para poder implementar el control de este proceso en un PLC es necesario modelar dicho

proceso primero. Una herramienta muy til es llamada diagramas de estados y se resume en

lo siguiente:

Un estado es equivalente a un paso, en donde se ejecuta una accin. Grficamente se

representa con un crculo. Las acciones se escriben sobre una diagonal que sale de cada

crculo.

Una transicin es un evento que indica cuando se puede pasar de un estado a otro.

Grficamente se representa con un arco que une dos estados, o un solo estado. Las

transiciones se escriben la flecha del arco.

El diagrama de estados para el ejemplo de la banda queda como se muestra en la figura 1:

Figura 1. Diagrama de estados.

En el ejemplo no se ha considerado el caso cuando se abre el interruptor, pero basta con

dibujar un arco desde los estados uno y dos al estado cero indicando como transicin

interruptor abierto

_____________________________________________________________________________

ITESM Campus Toluca CVH

1

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Relevadores de control secuencial

Para realizar la implementacin del diagrama de estados en el PLC se utilizan los

relevadores de control secuencial, bsicamente son variables energizadas durante un

instante de tiempo determinado por las condiciones de la transicin. Es decir, un evento

pone a uno un estado y as se mantiene hasta que un segundo evento resetea dicho estado.

El proceso descrito se puede realizar utilizando variables de memoria (V) aunque existe una

herramienta que lo facilita, los relevadores conocidos como SCR (secuential control relay).

Para utilizar un SCR se deben aplicar los siguientes tres comandos:

La operacin Cargar rel de control secuencial indica el comienzo de un segmento SCR.

Si el bit S est activado se habilita la circulacin de la corriente hasta el segmento SCR. La

operacin LSCR se debe finalizar con una operacin SCRE.

La operacin Transicin del rel de control secuencial identifica el bit SCR que se debe

habilitar (el siguiente bit S a activar). Cuando la corriente fluye hasta la bobina o hasta el

cuadro FUP, el bit S direccionado se activa y el bit S de la operacin LSCR (que habilit

este segmento SCR) se desactiva.

La operacin Fin del rel de control secuencial indica el fin de un segmento SCR.

Para mayor informacin recurra al manual del PLC ubicado en Course Documents de

BlackBoard.

MATERIAL Y EQUIPO

- Un PLC S7-224 o 216

- 2 Motores de CD

- 2 Bandas transportadoras

- Una PC con windows 95, 98 o NT y STEP 7 Micro WIn.

- Un decodificador de BCD a 7 segmentos

- Un desplegador de 7 segmentos

- Inversores 74LS06

DESARROLLO

Esta prctica tiene bsicamente el mismo funcionamiento que el de la prctica anterior,

pero la forma de resolver el programa es completamente diferente. El la prctica ocho se

implementaron funciones lgicas, en este caso se implementarn los estados del diagrama

de estados que se haya obtenido.

Igual que en la prctica ocho los temporizadores y los contadores se programan en el PLC,

pero difieren en lo que se espera del sistema. Anteriormente era muy difcil detener la

banda transportadora cuando entraba una pieza a un proceso, ahora es muy sencillo porque

la transicin puede o no depender de la posicin de cada pieza.

_____________________________________________________________________________

ITESM Campus Toluca CVH

2

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

_____________________________________________________________________________

ITESM Campus Toluca CVH

3

En la figura 2 se muestra el diagrama del proceso. Note que el funcionamiento del mismo

es casi igual al de la prctica 8 excepcin hecha de algunos cambios que a continuacin se

explican. Observe que tambin se ha agregado un sensor ms en la banda uno.

Figura 2. Diagrama del proceso.

Los pasos para el funcionamiento del proceso son:

1. El sistema inicia apagado, sin piezas en la banda 1 ni caja en la banda 2, las dos bandas,

el proceso y el temporizador estn apagados.

2. Se enciende el interruptor (On/Off), automticamente se enciende la banda 2 y se

detiene hasta que el sensor 2 indique que la caja esta en posicin para recibir las piezas.

3. Comienza a moverse la banda 1.

4. Cuado el sensor 1 detecta la pieza se manda el pulso de inicio para el temporizador y

comienza el proceso, se detiene la banda 1.

5. Cuando el sensor al final de la banda cuenta cada pieza indiza el nmero en un

desplegador de 7 segmentos, se deben tener 7 piezas en cada caja.

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

PRCTICA 11. Circuitos Neumticos Simples

Objetivo

Estudiar los conceptos de preparacin de aire, actuadores lineales y vlvulas e implementar

los circuitos bsicos de neumtica.

Marco Terico

La neumtica se refiere a la utilizacin de gases como sistemas impulsores. Est

transmisin de potencia mediante gases puede convertirse en potencia mecnica. Se tiene

que todos los gases pueden comprimirse y adems, el aire comprimido es elstico (ejerce

presin sobre todas las superficies del continente que ocupa). Considerando a la fuerza

como el efecto de empujar o tirar de una superficie, entonces el aire genera una fuerza (F)

sobre un rea de superficie (A) y a presin (P) conocidas a razn de F = P*A (Ley de

Pascal).

Preparacin del aire

El primer paso para trabajar con un sistema neumtico consiste en preparar el aire

comprimido, por lo general este sale del compresor con impurezas (grasa, agua, polvo...)

que deben ser removidas al entrar al sistema. Para realizar esta tarea se utiliza una unidad

de mantenimiento (conocida como FRL Filtro, Regulador, Lubricador ). El filtro se

encarga de remover las impurezas del aire. El regulador, como su nombre lo indica, regula

la presin del aire (La presin de trabajo es normalmente de 60 a 100 PSI). Y el lubricador

se encarga de dosificar aceite en el aire para los cilindros y evitar desgaste. Cada uno de los

tres componentes del FRL tiene un smbolo particular, pero por lo general se unifican en el

smbolo de la unidad de mantenimiento que se muestra a continuacin.

Actuadores lineales.

Ahora es necesario comprender el funcionamiento de los actuadores neumticos lineales. A

menudo conocidos como pistones o cilindros neumticos, estos actuadores se encargan de

generar un movimiento lineal, el smbolo y partes de un cilindro se muestran a

continuacin:

_____________________________________________________________________________

ITESM Campus Toluca CVH

1

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Los cilindros lineales ms comunes son:

Los cilindros de simple efecto son los ms sencillos y funcionan bsicamente de la

siguiente manera: En el caso del a- el aire entra por el puerto de la tapa ocasionando que

este se extienda, cuando se retira el aire, el resorte interior de la cabeza hace que se retraiga.

El cilindro de doble efecto se extiende cuando entra aire por la tapa y sale por la cabeza y,

se retrae cuando entra por la cabeza y sale por la tapa.

Aparte de los actuadores lineales tambin los hay rotatorios, como los que utilizan para

apretar y aflojar las tuercas los mecnicos, pero estos no sern estudiados en este curso.

Vlvulas

Las vlvulas son las encargadas de mover los cilindros, las vlvulas se pueden ver como

llaves que se abren o cierran para permitir el flujo de aire hacia los cilindros. La

representacin de una vlvula es mediante recuadros alineados horizontalmente y se

nombran de acuerdo a sus posiciones y sus vas. A continuacin se ilustra la simbologa de

una vlvula y la forma de llamarla.

Esta vlvula tiene dos posiciones, la de la derecha siempre se llama la posicin normal y

dependiendo de la direccin del flujo de aire en sus vas es que se obtiene el nombre

completo de la misma. Tambin tiene tres vas (solo se cuentan las de la posicin normal) y

_____________________________________________________________________________

ITESM Campus Toluca CVH

2

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

dos accionamientos, que son los que permiten alternar entre posiciones. Finalmente, esta

vlvula se llama 3/2 (tres vas, dos posiciones) y se lee tres dos.

Las vas de la posicin normal son las nicas que se enumeran y, se hace indicando con el

nmero uno a la entrada de presin, los nmeros dos y cuatro son salidas hacia los

actuadores y las tres y cinco son escapes.

Vlvula 2/2

La vlvula ms simple es la 2/2 NC, su smbolo se muestra abajo a la izquierda. Observe

que hay dos tapones en la posicin normal y un conducto de la va uno a la dos en la

posicin complementaria. Por los tanto, como no hay flujo de aire en la posicin normal, el

nombre completo de esta vlvula es 2/2 NC. (normalmente cerrada). Todas las vlvulas

tienen una complementaria y la de la 2/2 NC es la 2/2 NO (normalmente abierta), su

smbolo es el mismo con las posiciones mutuamente intercambiadas.

Cuando la vlvula esta en su posicin normal no hay flujo de aire, cuando se esta en la

complementaria (equivale a que la vlvula se mueva a la derecha) hay flujo y el circuito

que se tenga alimentado a la va dos funcionar. Simbologicamente es as, pero realmente

ocurre moviendo un vstago de izquierda a derecha y de derecha a izquierda tapando y

destapando las vas con unas gomas. La siguiente figura ilustra el proceso.

Esta vlvula se aplica bsicamente en sensores neumticos, botones y llaves.

Vlvula 3/2

La vlvula que se muestra a la izquierda en la siguiente figura es una 3/2 NC (tres vas, dos

posiciones y como tiene un tapn en la entrada de presin esta cerrada). A su derecha esta

la 3/2 NO.

_____________________________________________________________________________

ITESM Campus Toluca CVH

3

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Funciona de manera similar a la 2/2 como se ilustra enseguida

Esta vlvula se utiliza principalmente con cilindros de simple efecto

Vlvula 4/2

Se muestra la 4/2 12 y su complementaria la 4/2 14, ahora se nombran de acuerdo a las va

conectada con la uno (por donde entra y sale el aire en su posicin normal).

Fsicamente se constituye de la siguiente manera

Esta vlvula se utiliza en cilindros de doble efecto, pero no es la ms comn pues resulta

ms complicada su manufactura.

Vlvula 5/2

Los smbolos de las vlvulas 5/2 12 y 5/2 14 se tienen abajo

Fsicamente se tiene un funcionamiento ilustrado por la siguiente figura:

_____________________________________________________________________________

ITESM Campus Toluca CVH

4

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Esta vlvula se utiliza con los cilindros de doble efecto.

Vlvula 5/3

El smbolo de esta vlvula es el siguiente, note que la posicin normal es en medio.

Funciona como se muestra en la figura

Este cilindro se utiliza con cilindros de doble efecto sin vstago.

Accionamientos

Son los encargados de realizar ese movimiento de izquierda a derecha y viceversa en las

vlvulas, pueden ser desde un simple botn hasta un solenoide. Se dibujan a los costados

de la vlvula y si estn activos la vlvula estar en la posicin de dicho accionamiento. Por

ejemplo, en la siguiente figura se tiene una vlvula 2/2 con un muelle para la posicin

normal y un botn para la posicin complementaria. El efecto del muelle es que la vlvula

siempre esta cerrada a menos que se presione el botn que es cuando se abre.

Algunos de los accionamientos ms comunes son:

_____________________________________________________________________________

ITESM Campus Toluca CVH

5

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Material

Maletn de prcticas de neumtica.

Desarrollo

1. Construir y simular en Automation Studio un circuito que extiende y retrae el vstago

de un cilindro con un par de botones.

Durante la prctica utilice los pulsadores verde y negro y el botn de emergencia para

alimentar / inhibir todo el circuito.

Regule el caudal para que se extienda a la misma velocidad a la que se retrae y compruebe

la ley de Pascal disminuyendo la presin en el sitema.

2. Construir y simular en Automation Studio un circuito que extienda y retraiga un par

de cilindros con un par de botones y un par de sensores. Los botones servirn para

controlar el primer cilindro y los sensores acoplados en el vstago movern el segundo

cilindro en sentido inverso; es decir, cuando el cilindro uno se extienda el dos se retrae

y viceversa.

_____________________________________________________________________________

ITESM Campus Toluca CVH

6

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

_____________________________________________________________________________

ITESM Campus Toluca CVH

7

3. Construir y simular un circuito que extienda y retraiga alternadamente los tres cilindros

utilizando un par de botones y sensores (diseo abierto al estudiante).

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

PRCTICA 10. Circuitos Neumticos Secuenciales

Objetivo

Estudiar los conceptos de lgica combinatoria y secuencial para circuitos neumticos y

realizar su implementacin.

Marco Terico

Compuertas lgicas

Se utilizan principalmente las compuertas AND, OR y NOT, a continuacin se muestra el

smbolo, tabla de verdad y estructura interna de ellas:

And Or

Memorias

En neumtica la memoria de uso corriente es equivalente a un Latch Set - Reset (SR), la

siguiente figura muestra el smbolo y estructura interna de la memoria.

Grafcet

Mtodo Francs cuyas siglas significan (Graphe de Comands Etape / Transition, grfico de

mando etapa / transicin), sirve para modelar procesos secuenciales. Esta compuesto de

etapas, transiciones y acciones, las primeras se dibujan como recuadros que contienen el

nmero de etapa, por lo general la primera etapa se dibuja con un doble recuadro. Las

transiciones se dibujan entre etapas como una lnea vertical partida por un segmento de

recta horizontal, al lado derecho de cada transicin se escriben el identificador de dicha

_____________________________________________________________________________

ITESM Campus Toluca CVH

1

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

transicin. Las acciones se escriben en un recuadro dibujado a la derecha de cada etapa y

conectado a la misma mediante una lnea, se utiliza un recuadro por cada accin.

La siguiente figura muestra el Grafcet de un proceso que consiste en colocar una foco en

una base con una ranura y un resorte en la parte inferior (derecha):

La accin de la etapa uno (etapa inicial con doble recuadro) es bajar el foco, se continua

esta accin hasta que se ha tocado el fondo, entonces se pasa a la etapa dos (y se deja de

hacer todo lo que se estuviera haciendo en la uno). La etapa dos consiste en girar el foco

para que quede acomodado en la hendidura y no se salga, al tocar con la pared derecha de

dicha hendidura se pasa a la etapa tres. La etapa tres no tiene ninguna accin, pero como es

una etapa diferente se ha dejado de meter presin hacia abajo y de girar hacia la derecha el

resorte ocasiona que la patilla del foco toque con la parte superior de la ranura, esto es la

transicin que indica que se ha terminado el proceso. Por lo general se cierra el ciclo

colocando un enlace entre la transicin tres y la uno cuando se requieren procesos

repetitivos, pero este no es el caso.

Secuenciadores

El diagrama de conexin de un secuenciador se realiza a partir del Grafcet. Se utiliza el

mismo nmero de mdulos de etapa que de etapas en el Grafcet, la entrada es por la parte

inferior izquierda (observe que los mdulos tienen lneas diagonales punteadas que indican

el flujo de la seal) y la salida por la parte superior. Por ejemplo, en el Grafcet de abajo la

entrada a la etapa 2 es a1, en el diagrama a1 se conecta a la izquierda del actuador 2

indicando que esta entrada lo activa, la salida es b+, a- se escribe en la parte superior del

actuador.

_____________________________________________________________________________

ITESM Campus Toluca CVH

2

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

Fsicamente los secuenciadores se componen del mdulo de cabeza, los mdulos de etapa,

el mdulo de desviacin y el mdulo de cola. El mdulo de cabeza es en donde se alimenta

al secuenciador, tiene un par de seales A y B que marcan el fin y principio del ciclo, estas

seales se deben unir con sus correspondientes A y B del mdulo de cola. El mdulo de

desviacin no es necesario en la mayora de las aplicaciones. Para el correcto

funcionamiento de los secuenciadores estos no deben presentar fugas y tener una presin

suficientemente alta (aprox. 80 psi). La siguiente figura muestra el diagrama fsico de los

secuenciadores.

Temporizadores

Su funcin es la de contar un cierto tiempo despus de haber recibido una seal de entrada

y entonces generar una seal de salida para indicar que el tiempo ha transcurrido. Al recibir

la seal de entrada comienza a llenarse de aire una cmara interna, el tiempo se ajusta

_____________________________________________________________________________

ITESM Campus Toluca CVH

3

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

regulando el caudal de aire que entra, cuando la cmara se llena dispara la salida. El

smbolo de un temporizador se ilustra a continuacin.

Material

Maletn de prcticas de neumtica.

Desarrollo

1. Construir y simular en Automation Studio un circuito que extiende y retrae el vstago

de un cilindro con un par de botones combinados con una compuerta OR y un par de

llaves combinadas con una compuerta AND.

Durante la prctica utilice los pulsadores verde y negro, las llaves de dos y tres posiciones y

el botn de emergencia para alimentar / inhibir todo el circuito.

Recuerde que si se aplica seal a ambas entradas de la vlvula 5/2 no se producir

movimiento.

2. Construir y simular en Automation Studio un circuito que extienda y retraiga un par

de cilindros con un botn, un par de sensores y tres secuenciadores. Ambos cilindros

estan inicialmente retrados. El botn marca el inicio de ciclo, el cilindro A se

_____________________________________________________________________________

ITESM Campus Toluca CVH

4

MANUAL DE PRCTICAS DEL LABORATORIO DE SISTEMAS LGICOS

_____________________________________________________________________________

ITESM Campus Toluca CVH

5

extiende, al llegar al final de la carrera se retrae automticamente, cuando este

completamente retrado se extiende y retrae automticamente el cilindro B,

finalmente se mantiene en espera de un nuevo ciclo (encendiendo un indicador visual).

3. Construir y simular un circuito que extienda y retraiga los tres cilindros de manera

similar a la del circuito dos, el ciclo comienza (o se reanuda) ya sea con la salida del

temporizador o utilizando un botn (diseo abierto al estudiante).

También podría gustarte

- ManualTecnicoAutoclaves JPS STE 18a 23LDocumento14 páginasManualTecnicoAutoclaves JPS STE 18a 23LGabriel Duran Diaz0% (2)

- Manual Audi q7 Descripcion GeneralDocumento35 páginasManual Audi q7 Descripcion GeneralJorge Antonio Guillen100% (1)

- Responsabilidad en Accidentes Del Trabajo U de ChileDocumento91 páginasResponsabilidad en Accidentes Del Trabajo U de Chiletincho_0026Aún no hay calificaciones

- Gencon IvDocumento24 páginasGencon Ivenesgar50% (4)

- Semaforo Con Focos A 120v Con Triac y Moc3010Documento9 páginasSemaforo Con Focos A 120v Con Triac y Moc3010magus_ga100% (1)

- Practicas2006 PDFDocumento32 páginasPracticas2006 PDFsepiaaaaAún no hay calificaciones

- Labo 2Documento13 páginasLabo 2Kevin Apaza SoriaAún no hay calificaciones

- b2 Montajes Basicos Sobre TableroDocumento26 páginasb2 Montajes Basicos Sobre TableroJuan Alberto Gallego MoralesAún no hay calificaciones

- Secuencias Inst. ResidencialesDocumento30 páginasSecuencias Inst. Residenciales840702100% (6)

- 001 - Practicas Domotica Con Logo!Documento2 páginas001 - Practicas Domotica Con Logo!José Luis Granero MontesinosAún no hay calificaciones

- Practica 08 - Instalación de Alumbrado Con LOGODocumento2 páginasPractica 08 - Instalación de Alumbrado Con LOGOJosé Luis Granero MontesinosAún no hay calificaciones

- Tesis-Doctoral-Sergio-Monge Sobre TicDocumento422 páginasTesis-Doctoral-Sergio-Monge Sobre Ticapi-3775726100% (2)

- Sentron Pac3200Documento8 páginasSentron Pac3200amds2011100% (1)

- Taller Arduino PDFDocumento72 páginasTaller Arduino PDFFredy ArandaAún no hay calificaciones

- Constantes y Variables BooleanasDocumento30 páginasConstantes y Variables BooleanasHeyner Romero DAún no hay calificaciones

- 0910 Soluciones para FormacionDocumento96 páginas0910 Soluciones para FormacionEnergy Sun BiocarAún no hay calificaciones

- Política CurricularDocumento92 páginasPolítica CurricularDelaliAún no hay calificaciones

- Sensores de Humedad y Temperatura DHT11 y DHT22 Con Arduino UNO - Robótica SandriaDocumento10 páginasSensores de Humedad y Temperatura DHT11 y DHT22 Con Arduino UNO - Robótica SandriarichardcoroAún no hay calificaciones

- Semaforo de Dos ViasDocumento8 páginasSemaforo de Dos ViasDiego HaroAún no hay calificaciones

- Curso - Introduccion Al PLC Micro 1Documento6 páginasCurso - Introduccion Al PLC Micro 1Manigoldo De la Cruz100% (2)

- PLC 1Documento48 páginasPLC 1Manuel Rivas100% (1)

- 1.6 Operacion Dinamica de Maquinas Electricas Mayo 2020 A PDFDocumento23 páginas1.6 Operacion Dinamica de Maquinas Electricas Mayo 2020 A PDFMaria CalleAún no hay calificaciones

- Tema 5 Algebra Booleana-1481579731Documento62 páginasTema 5 Algebra Booleana-1481579731Cristhian ZambranoAún no hay calificaciones

- Libro - FinalDocumento62 páginasLibro - FinalJhoana YucraAún no hay calificaciones

- Pro1 07SDocumento32 páginasPro1 07SJuan Fernando CarmonaAún no hay calificaciones

- As IDocumento13 páginasAs IlcastroqAún no hay calificaciones

- Trabajo Domótica PDFDocumento25 páginasTrabajo Domótica PDFAlberto Freire MartinezAún no hay calificaciones

- 2 Introducción PLCDocumento36 páginas2 Introducción PLCEduardo ArreguinAún no hay calificaciones

- Guía para La Socialización de Los Documentos Última Versión 4Documento26 páginasGuía para La Socialización de Los Documentos Última Versión 4Sandra MontoyaAún no hay calificaciones

- Grado de Electrificacion ElevadoDocumento2 páginasGrado de Electrificacion ElevadocualquieraqueseaAún no hay calificaciones

- 1 Tarea 4 Semestre (Automatización y PLC)Documento30 páginas1 Tarea 4 Semestre (Automatización y PLC)Jose Dirseu Lopez ReyesAún no hay calificaciones

- Programación de Controles Lógicos Programables (PLC) : Instrumentista Industrial Código: PL.3.4.2-10373/19 Edición 01Documento9 páginasProgramación de Controles Lógicos Programables (PLC) : Instrumentista Industrial Código: PL.3.4.2-10373/19 Edición 01jonatanAún no hay calificaciones

- Tesla Logo Marca 2008Documento6 páginasTesla Logo Marca 2008Liam JJ0% (1)

- Silabos INSTALACIONES ELECTRICASDocumento4 páginasSilabos INSTALACIONES ELECTRICASCarlos SanchezAún no hay calificaciones

- Proyecto Arduino+SensorDocumento13 páginasProyecto Arduino+SensorArmando Hernández50% (2)

- Control Del Flujo de Agua de Una Ducha Eléctrica Mediante Reconocimiento de Comandos de VozDocumento20 páginasControl Del Flujo de Agua de Una Ducha Eléctrica Mediante Reconocimiento de Comandos de VozTelmo GuamanAún no hay calificaciones

- Field BusDocumento27 páginasField BusAndre Williams Montenegro SalcedoAún no hay calificaciones

- Reporte de PLCDocumento14 páginasReporte de PLCErnesto VenturaAún no hay calificaciones

- GUIA Practica PLC 2Documento9 páginasGUIA Practica PLC 2tatocinoAún no hay calificaciones

- Catalogo - Arrancadores - Media - Tension PDFDocumento80 páginasCatalogo - Arrancadores - Media - Tension PDFisaac diazAún no hay calificaciones

- IndiceDocumento4 páginasIndiceraulraul82Aún no hay calificaciones

- Relé Programable LOGO 8 Siemens - Controlador ProgramableDocumento8 páginasRelé Programable LOGO 8 Siemens - Controlador ProgramableLeonardo MisaelAún no hay calificaciones

- Ejercicios de Programacic3b3n en Logo Trabajo en Clase FinalDocumento3 páginasEjercicios de Programacic3b3n en Logo Trabajo en Clase FinalYovell LòpezAún no hay calificaciones

- Labview Fabrica de Velas SimulacionDocumento14 páginasLabview Fabrica de Velas SimulacionAndrés BonillaAún no hay calificaciones

- Autómata Programable LOGO 230 RCDocumento11 páginasAutómata Programable LOGO 230 RCAlejandro Humberto García QuisbertAún no hay calificaciones

- 000359-00 Manual Uso Salduba FutureDocumento36 páginas000359-00 Manual Uso Salduba FuturemalejarojaslAún no hay calificaciones

- Informe de Funciones de Algebras BooleanasDocumento8 páginasInforme de Funciones de Algebras BooleanasKlaus CRAún no hay calificaciones

- Trabajo Rele PIDocumento54 páginasTrabajo Rele PIMartin GonzalezAún no hay calificaciones

- Proyecto FinalDocumento17 páginasProyecto FinalChristian DavidAún no hay calificaciones

- Manual de Interfaz ArduinoDocumento39 páginasManual de Interfaz ArduinoChristian MartínezAún no hay calificaciones

- Guía Circuitos de Corriente AlternaDocumento18 páginasGuía Circuitos de Corriente AlternaMarcos DuncanAún no hay calificaciones

- Fernando Carlos Anchante Rivadeneyra - Lab 1-2023-1 - Circuitos Digitales - Compuertas Logicas BásicasDocumento2 páginasFernando Carlos Anchante Rivadeneyra - Lab 1-2023-1 - Circuitos Digitales - Compuertas Logicas BásicasJOSE ISRAEL CHOQUE PERALTAAún no hay calificaciones

- Informe Previo Final 1Documento12 páginasInforme Previo Final 1jeanAún no hay calificaciones

- GUÍA cd1Documento11 páginasGUÍA cd1kleberAún no hay calificaciones

- LAB 1-2024-1 - CIRCUITOS DIGITALES - Compuertas Logicas BásicasDocumento2 páginasLAB 1-2024-1 - CIRCUITOS DIGITALES - Compuertas Logicas BásicasjairoalvaradohidalgoAún no hay calificaciones

- Sol Lab 1Documento22 páginasSol Lab 1Michael PomaAún no hay calificaciones

- Funciones Lógicas, Compuertas y CaracterísticasDocumento21 páginasFunciones Lógicas, Compuertas y CaracterísticasnanyrieraAún no hay calificaciones

- Digitales-Informe Previo 1Documento16 páginasDigitales-Informe Previo 1Anthony Ipanaqué50% (2)

- EP3 Tecnologías SD Vanegas Guiscafre Jose RobertoDocumento3 páginasEP3 Tecnologías SD Vanegas Guiscafre Jose RobertoRoberto VanguisAún no hay calificaciones

- EP3 Tecnologías SD Vanegas Guiscafre Jose RobertoDocumento3 páginasEP3 Tecnologías SD Vanegas Guiscafre Jose RobertoRoberto VanguisAún no hay calificaciones

- Informe Tecnico Cerradura ElectricaDocumento14 páginasInforme Tecnico Cerradura ElectricaYaritza CardenasAún no hay calificaciones

- Laboratorio N°2-Ensayo de Compuertas LogicasDocumento12 páginasLaboratorio N°2-Ensayo de Compuertas LogicasOmar Gomez Cruz0% (1)

- Inf TTL CmosDocumento3 páginasInf TTL CmosJuan Camilo RamirezAún no hay calificaciones