DocumentoFPGA pptcargado por

DocumentoFPGA pptcargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad Documento2. EEE R13 IV-I -- Revised as on 09-08-16cargado por

Documento2. EEE R13 IV-I -- Revised as on 09-08-16cargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad Documento4 ECE R13 IV-Icargado por

Documento4 ECE R13 IV-Icargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad DocumentoEca Lab Manual 15-11-2016cargado por

DocumentoEca Lab Manual 15-11-2016cargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad Documento8086 Processor Interruptscargado por

Documento8086 Processor Interruptscargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad Documento1 Darlington Pair Amplifiercargado por

Documento1 Darlington Pair Amplifiercargado por Sheikh Noor Mohammad

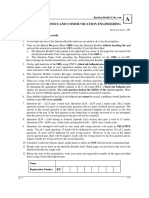

Sheikh Noor Mohammad![0% de Vlsi Design [Eee].Textmark (1) completado](https://s-f.scribdassets.com/images/progress/bar.png?932fa3dc0) DocumentoVlsi Design [Eee].Textmark (1)cargado por

DocumentoVlsi Design [Eee].Textmark (1)cargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad Documentovector calculus.pdfcargado por

Documentovector calculus.pdfcargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad DocumentoPaired Regionscargado por

DocumentoPaired Regionscargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad Documentoshadow removal using paired regions.pdfcargado por

Documentoshadow removal using paired regions.pdfcargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad Documento9a04306-Digital Logic Designcargado por

Documento9a04306-Digital Logic Designcargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad Documento9A04306 Digital Logic Design (2).pdfcargado por

Documento9A04306 Digital Logic Design (2).pdfcargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad DocumentoObul Reddy - Editcargado por

DocumentoObul Reddy - Editcargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad DocumentoObul Reddycargado por

DocumentoObul Reddycargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad Documentoobul (2)cargado por

Documentoobul (2)cargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad Documentovector calculus.pdfcargado por

Documentovector calculus.pdfcargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad Documento2 ECE II Year -- R15 Revised as on 27-08-2016cargado por

Documento2 ECE II Year -- R15 Revised as on 27-08-2016cargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad DocumentoGATE_EC_2013.pdfcargado por

DocumentoGATE_EC_2013.pdfcargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad DocumentoMicroprocessors Unit IIcargado por

DocumentoMicroprocessors Unit IIcargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad DocumentoNET syllabus 88.pdfcargado por

DocumentoNET syllabus 88.pdfcargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad DocumentoJntua CSE R13 Syllabuscargado por

DocumentoJntua CSE R13 Syllabuscargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad DocumentoContent.docxcargado por

DocumentoContent.docxcargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad DocumentoContent addressable memorycargado por

DocumentoContent addressable memorycargado por Sheikh Noor Mohammad

Sheikh Noor Mohammad

Documentos de Académico

Documentos de Profesional

Documentos de Cultura

![Vlsi Design [Eee].Textmark (1)](https://imgv2-2-f.scribdassets.com/img/document/337509464/149x198/6f79386bca/1485340378?v=1)