Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Semana10 Memoria03

Cargado por

Jean Carlo Canevello0 calificaciones0% encontró este documento útil (0 votos)

11 vistas20 páginasas

Título original

Semana10-Memoria03

Derechos de autor

© © All Rights Reserved

Formatos disponibles

PPT, PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoas

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PPT, PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

11 vistas20 páginasSemana10 Memoria03

Cargado por

Jean Carlo Canevelloas

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PPT, PDF, TXT o lea en línea desde Scribd

Está en la página 1de 20

Asignacin de memoria

(2)

Sistemas Operativos

Memoria virtual

La necesidad de ejecutar programas

que requeran ms memoria de que

se dispona en el sistema genero la

tcnica de memoria virtual propuesta

por Fotheringham en 1961.

La idea es mantener en memoria

fsica solamente la memoria que el

proceso est utilizando y el resto en

disco.

Memoria virtual

De esta forma, el programador se

despreocupaba de la limitacin de

memoria que impona el sistema.

La tcnica de memoria virtual

abstrae la memoria principal en un

gran arreglo uniforme de bytes.

Si bien es una tcnica muy potente,

el uso descuidado puede generar una

degradacin importante del sistema.

Memoria virtual

Cada proceso tiene un espacio de

direccionamiento virtual (virtual

address space).

Las direcciones de memoria que

genera el proceso son absolutas en

el espacio de direccionamiento.

Ej.: en un sistema de 32 bits realizando

un mapeo directo de direcciones, un

proceso tiene un espacio de

direccionamiento virtual de 232 = 4Gb.

La unidad de administracin de

memoria (MMU) es la encargada

de realizar la traduccin de

direcciones virtuales a fsicas.

Memoria virtual

Paginacin

La paginacin es una tcnica que divide a

la memoria fsica en particiones de

tamao fijo llamados marcos (frames).

A su vez, el espacio de direccionamiento

virtual es divido en unidades fijas del

mismo tamao que los frames (page size)

denominadas pginas (pages).

Las pginas tienen un tamao que es

potencia de 2 y, en general, son desde

512 bytes a 16 Mb.

Paginacin

En los sistemas que brindan paginacin, la

transferencia entre la memoria principal y

el disco es siempre en unidad de pgina.

Cuando un proceso ejecuta sus pginas

son cargadas en los frames de memoria

principal y en disco (seccin de swap).

Los frames en el swap tienen el mismo

tamao que los frames de memoria

principal.

Paginacin

Direccionamiento

Las direcciones virtuales en paginacin se

componen de un nmero de pgina (page

number) y un desplazamiento (offset).

El nmero de pgina es un ndice sobre

una tabla de pginas (page table) y el

desplazamiento es la referencia dentro del

frame.

La tabla de pgina contiene el mapeo del

frame correspondiente.

Paginacin

Paginacin

Soporte Hardware

La mayora de los sistemas operativos

asignan una tabla de pgina por

proceso.

Un puntero al comienzo de la tabla de

pgina es agregado al PCB del proceso.

Paginacin

Soporte Hardware

El uso de registros para alojar la tabla

tiene la ventaja del acceso rpido, pero

la cantidad de entradas es muy limitada.

Ej.: DEC PDP-11

Contaba con direcciones de 16bits y, por lo tanto,

su espacio de direccionamiento era de 64Kb.

El tamao de pgina era de 8Kb, por lo que la

tabla contaba con solamente 8 entradas

(dispuestas en los registros del procesador).

Paginacin

Soporte Hardware

En los sistemas actuales no es posible guardar todas las

entradas en registros de rpido acceso.

La tabla se mantiene en memoria principal y se asigna

un registro que apunta a la direccin base de la tabla

(PTBR Page Table Base Register).

La opcin del PTBR mejora el cambio de contexto entre

procesos ya que solo es necesario cambiar un registro

para acceder a la tabla de pgina.

Sin embargo, el acceso a memoria se duplica debido a

que es necesario primero acceder a la tabla para

obtener el nmero de frame y, posteriormente, al lugar

de memoria solicitado.

Paginacin

Soporte Hardware

La solucin es utilizar una pequea cache de la tabla de

pgina: TLB Translation Look-aside Buffer.

El cache TLB es asociativa y de rpido acceso.

Cada entrada consiste de dos partes: una clave (tag) y

un valor (el nmero de frame).

La bsqueda de un clave en la cache TLB es simultanea

entre todas las tags.

Si la clave es encontrada (TBL hit), inmediatamente se

genera la direccin buscada a partir del valor asociado.

En caso contrario (TBL miss), es necesario realizar el

acceso a memoria para obtener la entrada.

Posteriormente, se guarda el valor obtenido en la cache

TLB para posteriores accesos (principio de localidad).

Paginacin

Paginacin

Soporte a nivel hardware

Las TLB por lo general tienen pocas entradas (64 a

1024).

Algunas caches TLB agregan a cada entrada un

identificador de espacio de direccionamiento (ASID

Address Space IDentifier).

En la bsqueda de una clave solo sern tenidas en

cuenta las entradas cuyo ASID coincida con el del

proceso que est ejecutando en el procesador.

El uso del identificador permite que en la cache TLB

contengan entradas para varios procesos de forma

simultanea.

Si no se utiliza el ASID, en cada cambio de contexto es

necesario limpiar las entradas de la TLB, sino se

realizaran accesos equivocados a memoria.

Paginacin

Tiempo efectivo de acceso

La porcentaje de veces que un nmero de

pgina es encontrado en la cache TLB es

denominado hit ratio.

El tiempo efectivo de acceso se define

mediante la siguiente frmula:

EAT = hit ratio * (tiempo de bsqueda en TLB +

tiempo de acceso a memoria) + (1 hit ratio) * (2 *

tiempo de acceso a memoria).

La medida nos permite saber la ganancia de la

utilizacin de la cache TLB.

Paginacin

Proteccin

La tabla de pgina tiene una entrada por cada

pgina posible que tenga el proceso.

Es necesario identificar cuales son entradas

vlidas y cuales no.

La utilizacin de un bit de proteccin en cada

entrada determina si la pgina es vlida o

invlida (valid - invalid bit).

El acceso a una pgina cuyo bit marca que es

invlida, genera un trap a nivel del sistema

operativo.

Paginacin

También podría gustarte

- A#17 - Proyecto Integrdor 3Documento4 páginasA#17 - Proyecto Integrdor 3Diego LMAún no hay calificaciones

- Alemania - Ciudades VivasDocumento180 páginasAlemania - Ciudades VivasDreamsAvenue.comAún no hay calificaciones

- Arte Prehistoria (Recuperado)Documento68 páginasArte Prehistoria (Recuperado)David MailaAún no hay calificaciones

- TAJ MAHAL MaterialesDocumento6 páginasTAJ MAHAL MaterialesJhonatan CZAún no hay calificaciones

- Ficha-mart-ps-Valoramos La Labor de La MadreeDocumento1 páginaFicha-mart-ps-Valoramos La Labor de La Madreeジャン 宮殿100% (1)

- MercedesDocumento5 páginasMercedesAlvaro Ernesto ParedesAún no hay calificaciones

- Cuentos de TerrorDocumento7 páginasCuentos de TerrorDelly O DAún no hay calificaciones

- Tercero Cuarto ActividadDocumento3 páginasTercero Cuarto ActividadInes RiscoAún no hay calificaciones

- El Teclado y Sus PartesDocumento6 páginasEl Teclado y Sus Partes9545880988Aún no hay calificaciones

- Tipologias de Bienes Culturales InmueblesDocumento11 páginasTipologias de Bienes Culturales InmueblesJerzy ValentinAún no hay calificaciones

- TiahuanacoDocumento2 páginasTiahuanacoCristhianAún no hay calificaciones

- Arquitectura NeoclasicaDocumento16 páginasArquitectura NeoclasicaJUAN CARLOS PERICHE CASTROAún no hay calificaciones

- Comentario Complejo Funerario de GizehDocumento4 páginasComentario Complejo Funerario de GizehAHARCEAún no hay calificaciones

- Alfonso Ugarte Nació en La Ciudad de IquiqueDocumento3 páginasAlfonso Ugarte Nació en La Ciudad de IquiquePat Fr100% (1)

- Diapositiva Sobre La Memoria Ram Y Tarjetas PCIDocumento25 páginasDiapositiva Sobre La Memoria Ram Y Tarjetas PCIpenko769652Aún no hay calificaciones

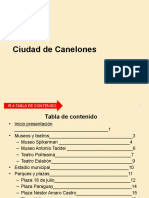

- Ciudad de Canelones AccesibleDocumento19 páginasCiudad de Canelones AccesibleKaren RepettoAún no hay calificaciones

- Infografia: Monumentos Historicos de VenezuelaDocumento8 páginasInfografia: Monumentos Historicos de VenezuelaEmely Hernandez100% (2)

- Papeles Falsos - Extracto-Páginas-5-22 PDFDocumento18 páginasPapeles Falsos - Extracto-Páginas-5-22 PDFLa VanguardiaAún no hay calificaciones

- Examen de Int. A La Historia Del Arte y Arquitectura 2 014 - 2 015Documento9 páginasExamen de Int. A La Historia Del Arte y Arquitectura 2 014 - 2 015Daniel Pérez100% (1)

- Recuérdame - Aryam ShieldsDocumento210 páginasRecuérdame - Aryam ShieldsAnyarit peñaAún no hay calificaciones

- Cementerio Presbítero Matías Maestro El 3 de JunioDocumento3 páginasCementerio Presbítero Matías Maestro El 3 de JunioAngela Hidalgo Vargas MachucaAún no hay calificaciones

- Memoria Ram PDFDocumento6 páginasMemoria Ram PDFivemox100% (2)

- Sesion 3 MemoriasDocumento34 páginasSesion 3 MemoriasJose RojasAún no hay calificaciones

- Plano Plaza Civica EtcDocumento3 páginasPlano Plaza Civica Etclilianaclaros83Aún no hay calificaciones

- Tema 11. Arquitectura FunerariaDocumento4 páginasTema 11. Arquitectura FunerariaJesús Ángel CarreñoAún no hay calificaciones

- Investigacion Piramide S Keops Mice RinoDocumento2 páginasInvestigacion Piramide S Keops Mice Rino'Charly Dzul SolisAún no hay calificaciones

- Carta EsquelaDocumento2 páginasCarta EsquelaJESSENIAAún no hay calificaciones

- Arquitectura MegaliticaDocumento17 páginasArquitectura Megaliticamaria marthaAún no hay calificaciones

- No Es Serio Este CementerioDocumento3 páginasNo Es Serio Este CementerioMarcela LizaolaAún no hay calificaciones

- Programa Oficial 16 Reunión Nacional de La Red Mexicana de Estudios de Espacios y Cultura Funerarios, A. C.Documento3 páginasPrograma Oficial 16 Reunión Nacional de La Red Mexicana de Estudios de Espacios y Cultura Funerarios, A. C.Diego A. Bernal B.Aún no hay calificaciones