Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Clase ADC-DAC - Version 1

Cargado por

AnNybell ChicaizaDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Clase ADC-DAC - Version 1

Cargado por

AnNybell ChicaizaCopyright:

Formatos disponibles

Conversores

Analgico/digital

Por Dr. Ing. Ariel Lutenberg

011100110

011100110

Conversores

Analgico/digital

Organizacin de la clase:

1. Repaso de

conversin A-D

2. Conversores

A-D

3. Conversores

D-A

1. Repaso de

conversin A-D

1. Introduccin a conversin A-D

Seal analgica y seal digital

La amplitud de una seal analgica puede tomar cualquier valor real.

Una seal digital toma valores discretos de un conjunto predeterminado.

1. Introduccin a conversin A-D

Ventajas de la seal digital

1. La seal puede replicarse sin perdida de calidad (CD, repetidores, etc).

2. Pueden detectarse y corregirse errores en la seal (ej. CD/DVD, CRC, etc.)

3. Procesamiento digital y compresin de la seal (MP3, JPG, etc.)

Desventajas de la seal digital

1. Se necesita una conversin analgica-digital y un conversin digital analgica.

2. La discretizacin introduce errores de cuantizacin.

1. Introduccin a conversin A-D

Introduccin

- Un conversor AD tiene como salida un valor digital

que indica la proporcin entre la seal analgica

de entrada y la tensin de referencia:

- El conversor discretiza la seal en n bits:

La cantidad posible de valores de salida

depende de la cantidad de bits:

#valores de salida: 2

n

La resolucin depende del nmero

de bits usado para cuantizar:

Quantum = LSB = FS/2

n

El error de cuantizacin depende

del nmero de bits usados:

Error cuantizacin = 1/2 LSB

1. Introduccin a conversin A-D

Errores de conversin

- Errores lineales: Son corregibles mediante ajustes sencillos:

- Errores no lineales: Son difciles de corregir:

Error de

offset

Error de

ganancia

Error de

alinealidad

Error de

alinealidad

1. Introduccin a conversin A-D

Terminologa

Resolucin del conversor

Es la mnima variacin en la seal de entrada que puede detectar el ADC.

Exactitud del conversor

Es la suma de todos los errores del ADC, incluyendo el error de cuantizacin.

Tiempo de conversin (t

c

)

Es el tiempo que requiere el ADC para convertir la seal de entrada.

Throughput rate

Es la cantidad mxima de conversiones que puede realizar el ADC (=1/t

c

)

1. Introduccin a conversin A-D

Circuito sample and hold (muestreo y retencin)

- Durante la conversin la seal de entrada debe permanecer estable:

Ejemplo

Para un ADC de 8 bits, con t

c

= 100s (10KHz) y FS = 2A, y con

resulta:

- Para salvar este problema

se utilizan circuitos Sample and Hold

que muestran la seal y retienen

su valor durante el tiempo

de conversin (memoria analgica).

max

( )

2

n

c

dV FS

dt t

s

sin(2 )

i

v A ft t =

2 cos(2)2

i

dv

fA ft fA

dt

t t t = s

2 1

2 12.4

2 2

n n

c c

A

fA f Hz

t t

t

t

s s = Esto es muy bajo!

1. Introduccin a conversin A-D

Acondicionamiento de la seal de entrada

- La seal a convertir debe aprovechar todo el rango de entrada del ADC:

Se aprovecha mejor la resolucin del ADC

Se minimiza el efecto de los errores del ADC

Ejemplo

Se tiene una seal con rango -10 a 10 Volts y un conversor con rango 0-5Volts.

- Los circuitos con operacionales son muy adecuados para escalar seales.

- Hoy en da esto viene muchas veces integrado en los ADCs.

1. Introduccin a conversin A-D

Caractersticas de los ADCs

Caractersticas de las entradas analgicas

de los conversores A-D:

Tipo de seal (tensin o corriente)

Polaridad (Unipolar, bipolar)

Nmero de canales

Rango de seal

Tensin de referencia (interna, externa)

Clock del conversor (interno, externo)

Deriva de la tensin de referencia

Caractersticas de las salidas digitales

de los conversores A-D:

Nmero de bits

Formato de la salida (paralelo, serie)

Conexin a bus

Niveles elctricos de la seal digital (5Volts, 3.3V, etc.)

Codificacin binaria (natural,2C,BCD)

2. Conversores A-D

2. Conversores A-D

Comparacin de tecnologas de ADC

La tecnologa a utilizar depende de los requisitos de la aplicacin.

Veamos las caractersticas de cada una de ellas

TECNOLOGA VELOCIDAD RESOLUCIN INMUN. RIUDO COSTO

Time Interleaving Muy rpido 4-10 bits No Alto

Flash Rpido 4-10 bits No Medio

Pipelined Subraging Rpido 10-16 bits No Alto

Succesive Approximation Medio 10-16 bits Escasa Bajo

Integrating Lento 12-18 bits Buena Bajo

Sigma-Delta Lento 12-24 bits Muy buena Bajo

2. Conversores A-D

Comparacin de tecnologas de ADC

2. Conversores A-D

Comparacin de tecnologas de ADC

Los conversores Slope ADCs son cada vez menos convenientes.

2. Conversores A-D

Comparacin de tecnologas de ADC

Adems el precio de los conversores se reduce ao tras ao

Veamos en detalle cada una de las tecnologas de conversores A-D

2. Conversores A-D

a. ADC Flash converters

Realiza la conversin de manera

inmediata en una nica operacin.

La salida de la cadena de

comparadores es

inherentemente digital.

La cadena de resistores

imposibilita ms de ~8 bits

de resolucin (255 resistores)

y/o impone un costo muy elevado.

2. Conversores A-D

a. ADC Flash converters (ejemplo)

2. Conversores A-D

a. ADC Flash converters (importancia del layout en la velocidad)

2. Conversores A-D

b. ADC Time Interleaved

La idea de estos conversores (TI-ADC) es usar un sistema de M canales en

paralelo, que convierten alternativamente a la seal y alimentan a un MUX.

El resultado es un conversor M veces ms rpido que cada conversor individual.

2. Conversores A-D

b. ADC Time Interleaved

2. Conversores A-D

b. ADC Time Interleaved

Es fundamental ecualizar los M canales y hay varias alternativas:

Los resultados

son muy

impresionantes

(ejemplo del

Advanced

Filter Bank del

AD12400):

2. Conversores A-D

c. ADC Succesive Aproximation

- Es apto para aplicaciones de baja

resolucin y velocidad.

- Por su bajo costo se suele integrar

en la mayora de microcontroladores

Su algoritmo interno es el siguiente:

2. Conversores A-D

c. ADC Succesive Aproximation (ejemplo)

2. Conversores A-D

d. ADC Pipelined subraging

Utilizan una estructura en cascada, tipo tubera (pipeline), donde la conversin se

realiza sucesivamente sobre fracciones cada vez menores de V

in

(subraging).

Por ejemplo, en un ADC subraging de 4 etapas de rango 0-1 Volts y una seal de

entrada de 0.7 Volts el funcionamiento sera el siguiente:

Ejercicio: repitan ustedes para el caso V

in

= 0.4 Volts.

1011

2. Conversores A-D

d. ADC Pipelined subraging (ejemplo)

Para un ADC subraging de 4 etapas de 1 bits y de rango 0-1 Volts, y una seal de

entrada de 0.4 Volts indique las tensiones y conversiones en cada etapa.

Resolucin

0.4V

-0.1

0.8V

0.3

0.6V

0.1

0.2V

-0.3

0 1 1 0 Output = 0110

1011

2. Conversores A-D

d.ADC Pipelined subraging

Implementacin para ms bits:

Los ADC pipelined

subranging dominan actualmente

las aplicaciones de alta velocidad

(>5 MSPS) en video, procesamiento

de imgenes, comunicaciones, etc.

2. Conversores A-D

d.ADC Pipelined subraging (ejemplo)

2. Conversores A-D

e. ADC - integracin

La seal de entrada se integra por un tiempo T (que se controla con R y C)

Luego el integrador se descarga con una tensin V

REF

conocida y se mide t

x

.

La conversin resulta de V

REF

,T y t

x

.

La resolucin depende de la cantidad de pulsos ck contabilizados durante t

x

.

Hay una relacin inversa entre resolucin y velocidad de conversin.

0

T

in

v dt

}

0

x

t

REF

V dt

}

in x REF

Tv t V =

x

in REF

t

v V

T

=

2. Conversores A-D

e. ADC - integracin

Ventaja: el ruido de frecuencia n/T es filtrado durante el proceso de integracin

Detalle: el valor de T depende de R y C, que varan con la temperatura y tienen

alta dispersin (sobre todo el capacitor)

2. Conversores A-D

e. ADC integracin (ejemplo)

2. Conversores A-D

f. ADC - Sigma Delta

Ver Simulacin Interactiva

ADCTutorial.jar

El lazo cerrado fuerza a que el valor

medio de B sea igual a V

IN

:

<B> = V

IN

La tensin <B> es controlada por la

densidad de unos y ceros del BIT DATA

STREAM en C :

| V

IN

C : |1 - +0

+ V

IN

C : |0 - +1

A partir de <C> se obtienen en D los

N-bits de salida mediante el filtro digital

y el decimador:

<C> D

OUT

2. Conversores A-D

f. ADC - Sigma Delta

Una resolucin de 24 bits implica medir una parte en 16.777.216 ( 0,059 ppm)

Para alcanzar esta resolucin es imprescindible reducir el ruido de cuantizacin.

Qu es el ruido

de cuantizacin?

2. Conversores A-D

f. ADC - Sigma Delta

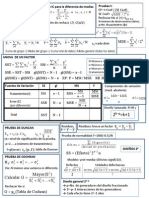

El error mximo de cuantizacin de un conversor

A/D ideal es de LSB

Considerando una distribucin uniforme de la

probabilidad de error:

Para una seal de entrada sinusoidal de

amplitud mxima:

Siendo la relacin seal/ruido cuantizacin:

() ( )

2 2

2 2

2

12

q

s

q

s

s q

t st dt

q

c

+

+

= =

}

12

RMS

q

c =

() ( )

2

sin2

2

N

q

vt ft t =

2

2 2

N

RMS

q

v =

()

10 10 10 10

()

()

3

10log 20log20log220log

2

N RMS

RMS

POTv

POT

v

SNR

c c

|| ||

||

= = =+

| |

|

|

\.

\. \.

6.02 1.76 SNR N dB = +

Para una resolucin de N Bits

Seal auxiliar propuesta para el error

2. Conversores A-D

f. ADC - Sigma Delta

Seal

Ruido de

cuantizacin

Potencia

espectral

Frecuencia

El proceso de conversin consta de:

Sobre-muestreo

Filtrado digital

Decimacin

Muestreando a la frecuencia de Nyquist:

Sobre-muestreando K veces, filtrando y

decimando:

10

2

6.021.7610log

2

s

s

Kf

SNRNdB

f

| |

=++

|

\ .

10

6.021.7610log SNRNdB K = + +

6.02 1.76 SNR N dB = +

fs

2

fs Kfs

2

Kfs

Se consigue mejorar la SNR en

un factor de K

Y esto no es igual

que promediar K

muestras?

La seal est mezclada con el ruido:

2. Conversores A-D

f. ADC - Sigma Delta

La ecuacin del lazo resulta:

Despejando la seal de salida:

+ f Y X (Q 0)

| f Y Q (X 0)

Seal

Ruido de

cuantizacin

Potencia

Frecuencia

1 1

X Qf

Y

f f

= +

+ +

( )

1

- Y XY Q

f

= +

fs

2

fs Kfs

2

Kfs

Modelo del ruido de cuantizacin:

Se reduce notablemente

el ruido de cuantizacin!!

2. Conversores A-D

f. ADC - Sigma Delta

Aumentando el orden del modulador se

obtienen mejores SNR:

1.76

6.02

SNR dB

ENOB

dB

=

Effective Number of Bits

Conversor - de segundo orden

Para comparar la SNR obtenida con

la de un conversor ideal se define:

2. Conversores A-D

f. ADC - Sigma Delta (ejemplo de diseo)

Digitalizar una seal de audio de

20Hz - 20kHz con una resolucin

de 16bits y una SNR de 80dB

Solucin:

Existen dos alternativas:

Utilizar un - de tercer orden.

Esto implica un K de 26:

fs = 20kHz x 2 x 26 = 1.04MHz

Utilizar un - de segundo orden.

Esto implica un K de 85:

fs = 20kHz x 2 x 84 = 3.36MHz

El ENOB ser de: (80dB 1.76dB)/6.02 = 13bits

- Slo 13bits de los 16bits contendrn informacin libre de ruido.

Importante: El - de 3 orden requiere complejos sistemas de estabilizacin del lazo.

26 85

2. Conversores A-D

f. ADC - Sigma Delta

Ventajas:

La mayor parte del sistema es digital:

- Posibilidad de alta integracin en C, DSP, etc.

- No existen derivas trmicas ni temporales.

- Bajo costo.

La alta tasa de sobre-muestreo y la baja precisin de la conversin analgica implica:

- No se requiere circuitos externos de sample & hold

- No se requieren filtros antialiasing (Ej. RC pasa-bajos)

El filtro digital permite obtener:

- Excelente figura de ruido

- Minimizacin del ruido en puntos crticos (Ej. 50/60 Hz)

- Nivel de ruido independiente de la amplitud de la seal

Es un diseo inherentemente monotnico y lineal

- Ideal para lazos cerrados de control

Desventajas:

Limitacin en la velocidad de conversin debido a la necesidad de sobremuestreo.

Problemas en sistemas multiplexados debido a la latencia del filtro digital:

- Sin embargo, en estos casos la solucin ms econmica y conveniente es

colocar un circuito integrado con varios Sigma-Delta incorporados.

2. Conversores A-D

f. ADC - Sigma Delta (ejemplo)

Figure 6. Schematic of the AD7793

2. Conversores A-D

f. ADC - Sigma Delta (ejemplo)

Figure 6. Schematic of the AD7793

2. Conversores A-D

f. ADC - Sigma Delta (simulacin en LTspice)

Figure 6. Schematic of the AD7793

3. Conversores D-A

3. Conversores D-A

Introduccin

Un DAC convierte una entrada digital a una seal analgica de salida

(generalmente voltaje).

3. Conversores D-A

a. DAC - Red de resistencias ponderadas

El siguiente circuito permite convertir una seal digital en una analgica:

El problema es que para lograr mucha resolucin se requiere resistencias de

mucha exactitud que cubran un rango muy amplio de valores.

3. Conversores D-A

b. DAC - Red de resistencias R-2R

El siguiente circuito slo utiliza resistores de valor R y 2R:

De esta manera ya no se requieren resistencias de mucha exactitud que cubran

un rango muy grande de valores, como el DAC de resistencias ponderadas.

3. Conversores D-A

Caracterizacin de DACs

Se ingresa con una seal sinusoidal y se analiza el resultado:

FIN.

También podría gustarte

- L4 FuncionesDocumento14 páginasL4 Funcionessandy choque matencioAún no hay calificaciones

- Codigos Error PanasonicDocumento2 páginasCodigos Error Panasonicmolino75100% (1)

- Franz Kafka, La MetamorfosisDocumento44 páginasFranz Kafka, La Metamorfosismissnts100% (1)

- Guía de Implementación - ATV312 Control en Profibus DP Mediante PLC Siemens S7300Documento29 páginasGuía de Implementación - ATV312 Control en Profibus DP Mediante PLC Siemens S7300Walter Medina LopezAún no hay calificaciones

- Manual de LabviewDocumento19 páginasManual de LabviewBecks Pio PioAún no hay calificaciones

- Componentes Supsuperficiales Del BECDocumento15 páginasComponentes Supsuperficiales Del BECMiguel DoroteoAún no hay calificaciones

- Infoplc Net Manual Formacion Vijeo DesignerDocumento130 páginasInfoplc Net Manual Formacion Vijeo DesignerCristóbal Eduardo Carreño MosqueiraAún no hay calificaciones

- Automatizacion ComponentesDocumento41 páginasAutomatizacion ComponentesPedro Martin Llaguento PortillaAún no hay calificaciones

- Resuelto Ejercicio 6 PDFDocumento6 páginasResuelto Ejercicio 6 PDFErick LopezAún no hay calificaciones

- INSTRUMENTACION Y CONTROL DE PROCESOS Unidad 1Documento11 páginasINSTRUMENTACION Y CONTROL DE PROCESOS Unidad 1GbgGbgAún no hay calificaciones

- Convertidores ADCDocumento15 páginasConvertidores ADCFERNANDO AYALA PEREZAún no hay calificaciones

- Labview PracticaDocumento4 páginasLabview PracticaSebastian RomeroAún no hay calificaciones

- SlurmDocumento55 páginasSlurmFerzz MontejoAún no hay calificaciones

- TEMA 9 Conversion AD DADocumento15 páginasTEMA 9 Conversion AD DAreanto87Aún no hay calificaciones

- MEDICIÓN TEMPERATURADocumento8 páginasMEDICIÓN TEMPERATURAJorge ChávezAún no hay calificaciones

- 3ra Experiencia Laboratorio de InstrumentacionDocumento33 páginas3ra Experiencia Laboratorio de InstrumentacionJesus Dennis Carlos Butron100% (1)

- Lenguaje s7 GraphDocumento30 páginasLenguaje s7 GraphJulioAún no hay calificaciones

- Probabilidad de Error de Símbolo en Modulaciones Digitales Banda Base Con Ruido AWGNDocumento7 páginasProbabilidad de Error de Símbolo en Modulaciones Digitales Banda Base Con Ruido AWGNRonnie EsparzaAún no hay calificaciones

- Guia Lab1 OPUDocumento8 páginasGuia Lab1 OPUJoan Manuel Quispe BordaAún no hay calificaciones

- 01 Manual de InstrumentacionDocumento144 páginas01 Manual de InstrumentacionJuan AlmeidaAún no hay calificaciones

- Comunicaciones II 21370Documento163 páginasComunicaciones II 21370darkmarkus10% (2)

- Informe Fisica 3. Leyes de KirchhoffDocumento5 páginasInforme Fisica 3. Leyes de KirchhoffNikolas Barreto VanegasAún no hay calificaciones

- Practicas ServofluidosDocumento8 páginasPracticas Servofluidosquieroleer888Aún no hay calificaciones

- Laboratorio 2Documento8 páginasLaboratorio 2Saúl UshiñaAún no hay calificaciones

- Lab 1 ElectronicosDocumento6 páginasLab 1 ElectronicosJHOSELIN NICOLS ASTAIZA TORRES100% (1)

- Laboratorio 7 ElectronciaDocumento13 páginasLaboratorio 7 ElectronciaEdgar William Six-NineAún no hay calificaciones

- Dac PonderadasDocumento1 páginaDac PonderadasDaniel AlcarazAún no hay calificaciones

- Creando El Proyecto Con Rsview y Rslogix 5000Documento16 páginasCreando El Proyecto Con Rsview y Rslogix 5000Juan Julio LLicaAún no hay calificaciones

- PSV Swagelok PDFDocumento2 páginasPSV Swagelok PDFJackAún no hay calificaciones

- Telefonia PCMDocumento108 páginasTelefonia PCMnejivanAún no hay calificaciones

- Medición de Piezas Con Software Visión Artificial de LabviewDocumento9 páginasMedición de Piezas Con Software Visión Artificial de Labviewvelasgugol100% (1)

- Lamp y MQTTDocumento12 páginasLamp y MQTTHenry PastuñaAún no hay calificaciones

- DAC en Escalera R - 2R (Entrega Preliminar)Documento31 páginasDAC en Escalera R - 2R (Entrega Preliminar)Luisito GeralvaAún no hay calificaciones

- Atando Cabos - Ejemplos Prácticos de Asociación, Agregación, Composición y Dependencia Con C#Documento7 páginasAtando Cabos - Ejemplos Prácticos de Asociación, Agregación, Composición y Dependencia Con C#Mauricio Rojas ValdiviaAún no hay calificaciones

- Bluetooth PIC PDFDocumento6 páginasBluetooth PIC PDFAbel EstevezAún no hay calificaciones

- DAC en escalera R/2RDocumento4 páginasDAC en escalera R/2RLuisito GeralvaAún no hay calificaciones

- Informe9 ValdviezoD LombeidaD LabRI GR31Documento8 páginasInforme9 ValdviezoD LombeidaD LabRI GR31Diego ValdiviezoAún no hay calificaciones

- PLC AvanzadoDocumento32 páginasPLC AvanzadoCristian Giovanni Gomez ParadaAún no hay calificaciones

- Carro Evasor de ObstaculosDocumento14 páginasCarro Evasor de ObstaculosMiguel Angel Barrera CardenasAún no hay calificaciones

- MANUAL DE MATLAB Y LABVIEW PARA ADQUISICIÓN Y ANÁLISIS DE DATOSDocumento22 páginasMANUAL DE MATLAB Y LABVIEW PARA ADQUISICIÓN Y ANÁLISIS DE DATOSDiego Frias ParedesAún no hay calificaciones

- Filtro FIR ReporteDocumento17 páginasFiltro FIR ReporteCarlos MelchorAún no hay calificaciones

- Contador ArduinoDocumento1 páginaContador ArduinoalanitotkdAún no hay calificaciones

- PCB FabricaciónDocumento95 páginasPCB FabricaciónSergio Andres VargasAún no hay calificaciones

- Cartilla Automatizacion Industrial y PLC 2013Documento67 páginasCartilla Automatizacion Industrial y PLC 2013albaizetaAún no hay calificaciones

- Bases de Datos Activas IIDocumento23 páginasBases de Datos Activas IIDaniel FrcAún no hay calificaciones

- Comunicación MQTT CODESYS AWS AnalyticsDocumento28 páginasComunicación MQTT CODESYS AWS AnalyticsSebastian PedrazaAún no hay calificaciones

- Arduino - Prácticas SensoresDocumento9 páginasArduino - Prácticas SensoresRafael DCAún no hay calificaciones

- Ga11 220501098 Aa1 Ev02Documento5 páginasGa11 220501098 Aa1 Ev02MORENO LÓPEZ LUIS DAVIDAún no hay calificaciones

- Actividad 4Documento8 páginasActividad 4Apolo MiyamizuAún no hay calificaciones

- Enlace Arduino - Matlab PDFDocumento3 páginasEnlace Arduino - Matlab PDFXavier MarinAún no hay calificaciones

- Carro Evasor de ObstaculosDocumento13 páginasCarro Evasor de ObstaculosFidel Angel Baquero LagosAún no hay calificaciones

- Implementación PID ArduinoDocumento16 páginasImplementación PID ArduinoDavids MallahuariAún no hay calificaciones

- Curso Básico Arduino - U1 - ProteusDocumento12 páginasCurso Básico Arduino - U1 - ProteusLuisAún no hay calificaciones

- Control de Velocidad Con LabVIEW y Arduino - Docx (RESUMIDO)Documento22 páginasControl de Velocidad Con LabVIEW y Arduino - Docx (RESUMIDO)Eugenio Puche SánchezAún no hay calificaciones

- Laboratorio Nro. 09Documento5 páginasLaboratorio Nro. 09Lucesita Alejandra SanchezAún no hay calificaciones

- Diseño de Maquinas de EstadoDocumento14 páginasDiseño de Maquinas de EstadoBayron Leandro Rosero HuertasAún no hay calificaciones

- Sensores y ActuadoresDocumento55 páginasSensores y ActuadoresEMILIANO BOMAYE ROQUEAún no hay calificaciones

- Guía Taller - Impedancia Fasorial - TEI - 80Documento3 páginasGuía Taller - Impedancia Fasorial - TEI - 80Nilson Camilo GonzalezAún no hay calificaciones

- Informe Proyecto de ElectrónicaDocumento5 páginasInforme Proyecto de ElectrónicaSebastián RiañoAún no hay calificaciones

- Conversor Analogico DigitalDocumento47 páginasConversor Analogico DigitalJhordanStepPascualAún no hay calificaciones

- Conversores A/D y D/A: Introducción a la conversión analógica-digital y digital-analógicaDocumento34 páginasConversores A/D y D/A: Introducción a la conversión analógica-digital y digital-analógicaJavier LeguizamonAún no hay calificaciones

- DAC y ADC: tipos, características y aplicaciones de los convertidores digital-analógico y analógico-digitalDocumento18 páginasDAC y ADC: tipos, características y aplicaciones de los convertidores digital-analógico y analógico-digitalRaul CruzAún no hay calificaciones

- Convertidor Convertidor Analógico Digital y Converidor de Digital A AnalogoDocumento11 páginasConvertidor Convertidor Analógico Digital y Converidor de Digital A AnalogoSandra Milena Nuñez CuadrosAún no hay calificaciones

- Convertidores AD y DADocumento51 páginasConvertidores AD y DAClei Shin100% (1)

- 7878524583fórmulas DoebDocumento3 páginas7878524583fórmulas DoebRACHEL BOSSAún no hay calificaciones

- Métodos numéricos EULER RK con MATLABDocumento6 páginasMétodos numéricos EULER RK con MATLABjulianpoluxAún no hay calificaciones

- Tesis CarlosGutibncerrezDocumento272 páginasTesis CarlosGutibncerrezCarlos Alberto NievesAún no hay calificaciones

- W34645746ejercicio 1 - GraficaDocumento2 páginasW34645746ejercicio 1 - GraficaRACHEL BOSSAún no hay calificaciones

- Nuevo Instructivo BcsDocumento5 páginasNuevo Instructivo Bcsenkil17Aún no hay calificaciones

- Alejandre Escalante Guadalupe Alvaro Obregon #627 Int Revol Lazaro Cardenas Y Priv Alvaro Obregon Revolucion Col PR Poza Rica, VerDocumento2 páginasAlejandre Escalante Guadalupe Alvaro Obregon #627 Int Revol Lazaro Cardenas Y Priv Alvaro Obregon Revolucion Col PR Poza Rica, VerRACHEL BOSSAún no hay calificaciones

- 1 s2.0 S0716864010705629Documento6 páginas1 s2.0 S0716864010705629Diego Tejada ChavezAún no hay calificaciones

- 7878524583fórmulas DoebDocumento3 páginas7878524583fórmulas DoebRACHEL BOSSAún no hay calificaciones

- 0plan de Vida y Carrera1 - 231Documento2 páginas0plan de Vida y Carrera1 - 231RACHEL BOSSAún no hay calificaciones

- '0987ñlkjv07-Turismo y SustentabilidadDocumento15 páginas'0987ñlkjv07-Turismo y SustentabilidadRACHEL BOSSAún no hay calificaciones

- CalendarioIngreso 2015-2Documento1 páginaCalendarioIngreso 2015-2RACHEL BOSSAún no hay calificaciones

- Dialnet 4835506Documento3 páginasDialnet 4835506RACHEL BOSSAún no hay calificaciones

- Manual PracticasDocumento49 páginasManual Practicastamagochi13Aún no hay calificaciones

- Ip3 PDFDocumento10 páginasIp3 PDFRACHEL BOSSAún no hay calificaciones

- 098765432temarios CompletosDocumento8 páginas098765432temarios CompletosRACHEL BOSSAún no hay calificaciones

- 51 Press IntegralesDocumento36 páginas51 Press IntegralesJorge Cruz GonzalezAún no hay calificaciones

- Correlacion EspectralDocumento5 páginasCorrelacion EspectralRACHEL BOSSAún no hay calificaciones

- 02calculo de Tensiones PrincipalesDocumento29 páginas02calculo de Tensiones PrincipalesChema Piñero VilelaAún no hay calificaciones

- Sintonizacion de ControladoresDocumento21 páginasSintonizacion de ControladoresZ Erandi Cortes RodriguezAún no hay calificaciones

- Microcontroladores - Ejercicio 1Documento4 páginasMicrocontroladores - Ejercicio 1RACHEL BOSSAún no hay calificaciones

- Ejercicio 1 - Simulación de Un Sistema Masa-ResorteDocumento8 páginasEjercicio 1 - Simulación de Un Sistema Masa-ResorteRACHEL BOSSAún no hay calificaciones

- Ana Doc Tec 01Documento22 páginasAna Doc Tec 01RACHEL BOSS100% (1)

- Técnicas GrupalesDocumento70 páginasTécnicas Grupalesjavinova841Aún no hay calificaciones

- Matlab 2Documento33 páginasMatlab 2Zereth Sahar Zav SalcidoAún no hay calificaciones

- Sumas y Restas ABN 2 DigitosDocumento1 páginaSumas y Restas ABN 2 DigitoslenbecarameloAún no hay calificaciones

- Sistemas Fuzzy en Entornos CrispDocumento74 páginasSistemas Fuzzy en Entornos CrispRACHEL BOSSAún no hay calificaciones

- Programación Con Bloques FuncionalesDocumento2 páginasProgramación Con Bloques FuncionalesRACHEL BOSSAún no hay calificaciones

- Manualtv LCD LG Rp-42px10Documento37 páginasManualtv LCD LG Rp-42px10Nonato Mendez Caceres0% (1)

- TablerosBajaTensiónCertificadosDocumento12 páginasTablerosBajaTensiónCertificadosLuz Angélica CelyAún no hay calificaciones

- Fuente Rsag7 820Documento2 páginasFuente Rsag7 820Aladino SanchezAún no hay calificaciones

- Amplificador Sumador RestadorDocumento4 páginasAmplificador Sumador RestadorGEAN CARLO RODRIGUEZ ROAAún no hay calificaciones

- Equipo - Angela. Sondeos Elã - Ctricos VerticalesDocumento22 páginasEquipo - Angela. Sondeos Elã - Ctricos VerticalesAndrés EfeAún no hay calificaciones

- Manual v2c TrydanDocumento12 páginasManual v2c TrydanstratosergioAún no hay calificaciones

- Amplificadores Fet en CascadaDocumento10 páginasAmplificadores Fet en CascadaKATHERINE MISHEL PAZ MUÑOZAún no hay calificaciones

- 08 - Ley de FaradayDocumento43 páginas08 - Ley de FaradayJulio RodriguezAún no hay calificaciones

- Proceso electrólisis cobreDocumento31 páginasProceso electrólisis cobreOliverJimenezAún no hay calificaciones

- Ingeniería Del ProyectoDocumento55 páginasIngeniería Del ProyectoAventurero dark0% (1)

- RuidoDocumento26 páginasRuidoTortasYBocaditosMochitaAún no hay calificaciones

- Modulo de Entrenamiento Empleando Software Logo PLCDocumento37 páginasModulo de Entrenamiento Empleando Software Logo PLCAnthony Delgado alonzoAún no hay calificaciones

- Generadores Permanentes MagneticosDocumento6 páginasGeneradores Permanentes MagneticosAdano MohanoAún no hay calificaciones

- 7 PDFDocumento16 páginas7 PDFhgcuAún no hay calificaciones

- Catalogo Anderson Conectores 2011Documento11 páginasCatalogo Anderson Conectores 2011svconstrucciones100% (1)

- Rectificadores No ControladosDocumento8 páginasRectificadores No ControladosMikhaelA.Rodriguez100% (1)

- Deflexion ElectricaDocumento18 páginasDeflexion ElectricaAlexandraMaierAún no hay calificaciones

- 06 TR 2 PDFDocumento8 páginas06 TR 2 PDFAndres Soriano JiménezAún no hay calificaciones

- REX640 Oper 2NGA000155 ESaDocumento140 páginasREX640 Oper 2NGA000155 ESaProteccion MedicionAún no hay calificaciones

- TIF Avance Con MetodologiaDocumento13 páginasTIF Avance Con MetodologiaRENATO JUDA POLO AÑORGAAún no hay calificaciones

- Resistencia CircuitosDocumento5 páginasResistencia CircuitosGabriel RamirezAún no hay calificaciones

- Guia Practica 1Documento5 páginasGuia Practica 1Jorge Luis HuaracaAún no hay calificaciones

- KF 04 - Clculo Simplificado de Corrientes de CortocircuitoDocumento4 páginasKF 04 - Clculo Simplificado de Corrientes de Cortocircuitomherold2Aún no hay calificaciones

- AC Circuit Analysis in 40 chars or lessDocumento49 páginasAC Circuit Analysis in 40 chars or lessCristhofer Javier TomaláAún no hay calificaciones

- Adp Pie Spyl 19005 e e Ete 001 Rev B TalaraDocumento46 páginasAdp Pie Spyl 19005 e e Ete 001 Rev B TalaraPatts MarcAún no hay calificaciones

- Guia 4-Circuitos en ParaleloDocumento6 páginasGuia 4-Circuitos en ParaleloDarwin TapuyoAún no hay calificaciones

- Historia y evolución del teléfonoDocumento11 páginasHistoria y evolución del teléfonoHamilton Dávila CórdobaAún no hay calificaciones