Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Lab Oratorio 2

Lab Oratorio 2

Cargado por

Nicko VivarDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Lab Oratorio 2

Lab Oratorio 2

Cargado por

Nicko VivarCopyright:

Formatos disponibles

Nicols Vivar ERC 7- B Diseo VLSI 1) Realizar un comparador de 4 bits y mostrar el resultado por tres LEDs.

Un circuito comparador combinatorio de 4 bits compara dos entradas binarias (A y B de 4 bits) para indicar la relacin de igualdad o desigualdad entre ellas por medio de "tres banderas lgicas" que corresponden a las relaciones A igual B, A mayor que B y A menor que B. Cada una de estas banderas se activara solo cuando la relacin a la que corresponde sea verdadera, es decir, su salida ser 1 y las otras dos producirn una salida igual a cero.

1 Comparador de 4 Bits

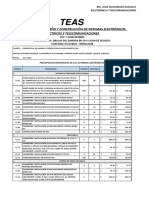

El circuito que se diseo se program a partir del circuito de la figura, como vemos posee 4 tipos de compuertas con varias entradas. Entre ellas se encuentran: 8 compuertas NOT de 1 entrada. 10 compuertas AND de 2 entradas. 2 compuertas AND de 3 entradas. 3 compuertas AND de 4 entradas. 4 compuertas NOR de 2 entradas. 2 compuertas OR de 4 entradas. Para la programacin se realizaron los 6 tipos de compuertas como VHDL Module con sus respectivas caractersticas. Despus, se crearon las funciones de cada compuerta dentro de cada modulo individual, para luego crear las conexiones entre las compuertas y as crear el comparador en el mdulo principal. Cabe recalcar la nomenclatura utilizada para cada una de las compuertas, por ejemplo, el nombre del modulo VHDL de una compuerta AND de 4 entradas sera: mi_and_4 y sus entradas seran entrada_and_4_1, entrada_and_4_2, entrada_and_4_3, entrada_and_4_4 y su salida sera salida_and_4_1. Esto a lo largo de todo el programa para evitar confusiones.

En esta imagen se pueden observar las 23 compuertas utilizadas para construir el comparador.

2 Sources Implementation

Se detallar cada una de las seis compuertas creadas: NOT:

Cabe mencionar que para las compuertas not se cre un bus de 4 compuertas para facilitar la conexin. AND_2

AND_3

AND_4

NOR_2

OR_4

Luego de crear los mdulos en el programa principal se declaran las entradas y salidas de todo el sistema.

Se crean los componentes para que se puedan juntar en el programa por medio de las seales.

Se crean las seales que son los caminos para las interconexiones.

Se crean los circuitos con nombre ui, enumerando a las partes dependiendo como se neceite conectarlas.

Se sintetiza el programa y se verifica que no se tengan errores de sintaxis y se puede realizar la simulacin

En el primer intervalo se observa que entrada B= entrada A por lo que a la salida se enciende el ltimo led, en el segundo intervalo B>A y se enciende el primer led, y al final se observa que B<A y se enciende el led de la mitad, comprobando que el circuito funciona correctamente. Ahora para grabar en la tarjeta se colocan los contrains y se finaliza el proceso.

3) Implementar un sumador de 8 bits a partir de full adder. No considerar acarreo de entrada. Mostrar el resultado por LEDs.

3Full Adder 2 bits

El circuito de la figura es un full adder de dos bits con un acarreo inicial y un acarreo final, como el ejercicio nos pide que sea un full adder de 8 bits, lo que hacemos en este programa es colocar en cascada 4 full adder de 2 bits, con el acarreo inicial yendo a 0 y los dems acarreos unidos, es decir el acarreo final del primer full adder es el acarreo inicial del segundo full adder, hasta obtener la salida de 4 bits. Para lograr esta conexin de 4 full adder de dos bits en cascada lo que se hizo fue construir un full adder como el de la figura, de la misma manera que se construy el primer comparador. Y luego juntarlos a travs de un programa principal que engloba a los cuatro full adder de dos bits, con la misma lgica de programacin que el comparador. Lista de Componentes, donde se ve que pares contiene al full adder completo y al full adder de dos bits que son: 2 compuertas AND de 2 entradas. 2 compuertas XOR de 2 entradas. 1 Compuerta OR de 2 entradas.

El modulo VHDL del full adder de 2 bits es: Entidad:

Componentes:

En el programa principal que se llama Full_Adder_Completo, se encuentra un solo componente que es el full adder. Y una sola seal que se necesit para interconectar al circuito por los acarreos.

Y las conexiones en cascada se realizaron asi:

Para luego obtener la simulacin el resultado:

Primer intervalo est: 1+1=2. Segundo intervalo est: 2+2=4. Tercer intervalo est: 4+4=8. Cuarto intervalo est: 8+8=10. Quinto intervalo est: hC+hC=18. Con lo que comprobamos la eficiencia del full adder. Para grabar en la tarjeta se utilizaron los siguientes contrains:

También podría gustarte

- CuadroAct3 Tema 3Documento2 páginasCuadroAct3 Tema 3Jose Luis RodriguezAún no hay calificaciones

- Trabajo Final Power BI AvanzadoDocumento2 páginasTrabajo Final Power BI AvanzadoHEC0% (1)

- Escenarios de Aprendizaje Con Gamificación.Documento6 páginasEscenarios de Aprendizaje Con Gamificación.Juan Domingo Farnós Miró100% (4)

- Catalogo 2021 EtiquetadoraDocumento20 páginasCatalogo 2021 EtiquetadoraRodrigo Perez100% (1)

- Reparar Vínculos Rotos A Datos - Excel For MacDocumento3 páginasReparar Vínculos Rotos A Datos - Excel For MacNIEAún no hay calificaciones

- VI PA L15 Comisionamiento ArranqueDocumento6 páginasVI PA L15 Comisionamiento ArranqueGerardoAún no hay calificaciones

- Sistemas Numéricos PosicionalesDocumento15 páginasSistemas Numéricos PosicionalesPau PSAún no hay calificaciones

- Ambientes OperativoDocumento8 páginasAmbientes OperativoJoaneli GonzalezAún no hay calificaciones

- Módulo 5 Redes Virtuales Redes 2Documento18 páginasMódulo 5 Redes Virtuales Redes 2Bruno EscalanteAún no hay calificaciones

- Inteligencia Artificial EsDocumento30 páginasInteligencia Artificial EsMedalith Cotrina CamposAún no hay calificaciones

- Trabajo Práctico N°2 D&D WebDocumento10 páginasTrabajo Práctico N°2 D&D WebCatalina SequeiraAún no hay calificaciones

- Portafolio FinalDocumento7 páginasPortafolio Finalalejandra higueraAún no hay calificaciones

- CA - Module - 20 Inteligencia de AmenazasDocumento21 páginasCA - Module - 20 Inteligencia de AmenazasGIAN FRANCO MONTENEGRO AYALAAún no hay calificaciones

- Entorno+gráfico+de+visual+basic+2013 Primera ParteDocumento19 páginasEntorno+gráfico+de+visual+basic+2013 Primera Partedabo15Aún no hay calificaciones

- Microsoft Power PointDocumento18 páginasMicrosoft Power PointLlencis ColónAún no hay calificaciones

- Administre Cuentas y Grupos de Windows Con PowerShell (TurboLabDocumento8 páginasAdministre Cuentas y Grupos de Windows Con PowerShell (TurboLabPablo JoseAún no hay calificaciones

- Actividad Integradora M1 - IntercionexionDocumento5 páginasActividad Integradora M1 - IntercionexionEl GafasAún no hay calificaciones

- Legislación Informática en ColombiaDocumento5 páginasLegislación Informática en Colombiajulices1Aún no hay calificaciones

- Storyline 3 - Configuración Del Tamaño de La DiapositivaDocumento7 páginasStoryline 3 - Configuración Del Tamaño de La DiapositivaWalter Zubiaur AlejosAún no hay calificaciones

- Diagrama de GanttDocumento4 páginasDiagrama de GanttJose ZuluagaAún no hay calificaciones

- Practica No 5Documento10 páginasPractica No 5Cristian OportaAún no hay calificaciones

- Política y Filosofia de Mantenimiento - Ozelada - 05 - 08 - 21 - Rev1Documento11 páginasPolítica y Filosofia de Mantenimiento - Ozelada - 05 - 08 - 21 - Rev1Oscar ZeladaAún no hay calificaciones

- Chat GPT Por IADocumento2 páginasChat GPT Por IAScribd JhonnyAún no hay calificaciones

- Programacion de Aplicaciones EMTRAFESADocumento37 páginasProgramacion de Aplicaciones EMTRAFESACESAR_CASTILLOHAún no hay calificaciones

- Manual de Buenas Practicas y Configuracion Del UtorrentDocumento11 páginasManual de Buenas Practicas y Configuracion Del UtorrentAlejandro Arenillas HerranAún no hay calificaciones

- Presupuesto Referencial CPJL Agencia YantzazaDocumento3 páginasPresupuesto Referencial CPJL Agencia YantzazaCristian Illescas AstudilloAún no hay calificaciones

- Tarea Intraclase 3 - HDGDocumento7 páginasTarea Intraclase 3 - HDGLuzbel TakagureAún no hay calificaciones

- SIl POLDocumento9 páginasSIl POLEIDYS BENITEZAún no hay calificaciones

- Gnuplot TutDocumento28 páginasGnuplot TutErith Alexander MuñozAún no hay calificaciones