Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Tema1 Prac2 Tests

Cargado por

edganoDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Tema1 Prac2 Tests

Cargado por

edganoCopyright:

Formatos disponibles

Requisitos mnimos para el boletn de prcticas B1.

2 de Estructura y Tecnologa de Computadores

Febrero de 2011

1.

Introduccin

En este documento se indica el conjunto mnimo de casos de prueba que deben superar los ejercicios entregados del boletn para poder ser evaluados. La memoria debe demostrar, mediante cronogramas y/o capturas de pantalla, que cada circuito entregado cumple los mnimos exigidos; de no ser as, el ejercicio no se tendr en cuenta y se calicar como 0. No obstante, para simplicar el trabajo, se debe tener en cuenta lo siguiente: Si la memoria demuestra que el ejercicio 4 cumple los requisitos mnimos, no ser necesario demostrar que el resto de ejercicios los cumplen. Si no se entrega el ejercicio 4 y s el 3, y la memoria demuestra que este ejercicio cumple los requisitos mnimos, no ser necesario demostrar que los ejercicios 1 y 2 los cumplen. Finalmente, si slo se entregan los ejercicios 1 y 2, ser necesario mostrar en la memoria que ambos cumplen los mnimos exigidos. Obviamente, adems de los casos de prueba aqu indicados, la memoria podr contener tambin cualquier otra prueba que el alumno haya considerado oportuno hacer.

2.

Ejercicio 1

El circuito de este ejercicio debe cumplir la tabla de verdad dada en la tabla B1.1 del boletn (ver pgina 27).

3.

Ejercicio 2

El circuito de este ejercicio debe cumplir la tabla de verdad dada por el mapa de Karnaugh que aparece en la pgina 32.

4.

Ejercicio 3

Las dos ALUs implementadas en este ejercicio (ALU1bit y ALUFinal) deben cumplir los casos de prueba que se dan en las siguientes tablas, es decir, para distintas combinaciones de los bits de control, las salidas obtenidas son las mostradas en las tablas (las salidas Overow y Comparacin slo aparecen en la ALU del bit de mayor peso, mientras que la salida AcS slo aparece en la ALU del resto de bits): Si Control = 000 (AND):

a 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

b 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

Entradas AcE Menor 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Resultado 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1

AcS 0 0 0 0 0 0 1 1 0 0 1 1 1 1 1 1

Salidas Overow 0 0 1 1 0 0 0 0 0 0 0 0 1 1 0 0

Comparacin 0 0 1 1 1 1 0 0 1 1 0 0 0 0 1 1

Si Control = 001 (OR):

Entradas AcE Menor 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Salidas Overow 0 0 1 1 0 0 0 0 0 0 0 0 1 1 0 0

a 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

b 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

Resultado 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1

AcS 0 0 0 0 0 0 1 1 0 0 1 1 1 1 1 1

Comparacin 0 0 1 1 1 1 0 0 1 1 0 0 0 0 1 1

Si Control = 010 (SUMA):

Entradas AcE Menor 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Salidas Overow 0 0 1 1 0 0 0 0 0 0 0 0 1 1 0 0

a 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

b 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

Resultado 0 0 1 1 1 1 0 0 1 1 0 0 0 0 1 1

AcS 0 0 0 0 0 0 1 1 0 0 1 1 1 1 1 1

Comparacin 0 0 1 1 1 1 0 0 1 1 0 0 0 0 1 1

Si Control = 110 (RESTA):

a 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

b 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

Entradas AcE Menor 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Resultado 1 1 0 0 0 0 1 1 0 0 1 1 1 1 0 0

AcS 0 0 1 1 0 0 0 0 1 1 1 1 0 0 1 1

Salidas Overow 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0

Comparacin 1 1 0 0 0 0 1 1 0 0 1 1 1 1 0 0

Si Control = 111 (SLT):

a 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 b 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 Entradas AcE Menor 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Resultado 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 AcS 0 0 1 1 0 0 0 0 1 1 1 1 0 0 1 1 Salidas Overow 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 Comparacin 1 1 0 0 0 0 1 1 0 0 1 1 1 1 0 0

5.

Ejercicio 4

La ALU de 8 bits implementada en este ejercicio, debe cumplir los casos de prueba que se dan en la siguiente tabla:

A (8 bits, hexadecimal) 03 03 04 78 F8 80 FF 55 57 57 5A 5A Entradas B (8 bits, hexadecimal) 04 04 04 79 FA 08 AA AA 5A 5A 5A 57 Control (3 bits, binario) 010 110 110 010 110 110 000 001 000 111 111 111 Resultado (8 bits, hexadecimal) 07 FF 00 F1 FE 78 AA FF 52 01 00 00 Salidas Desbordamiento (1 bit) 0 0 0 1 0 1 0 0 1 0 0 0 Cero (1 bit) 0 0 1 0 0 0 0 0 0 0 1 1

La gura 1 muestra una captura de pantalla en la que se aprecia claramente que el primer caso de prueba funciona. Por su parte, la gura 2 muestra un cronograma en el que se puede comprobar que los 5 primeros casos de prueba funcionan. 3

Figura 1: Captura de pantalla de la ALU terminada mostrando el correcto funcionamiento del primer caso de prueba.

Figura 2: Captura de un cronograma mostrando el correcto funcionamiento de los primeros 5 casos de prueba. w32 es el resultado de la operacin y w48 el desbordamiento.

También podría gustarte

- Ensayo de Analisis de Costos de Ciclo de VidaDocumento3 páginasEnsayo de Analisis de Costos de Ciclo de VidaJuan Carlos Zocko Olguin100% (1)

- Plan de Gestión de La CalidadDocumento3 páginasPlan de Gestión de La CalidadWilson Hanccocallo Usca100% (1)

- Naturaleza y Propósito de Los ModelosDocumento17 páginasNaturaleza y Propósito de Los ModelosClaudia PierriAún no hay calificaciones

- Mapa conceptual auditoría informáticaDocumento1 páginaMapa conceptual auditoría informáticaedward leon100% (1)

- Ganar Dinero Con AcortadoresDocumento3 páginasGanar Dinero Con AcortadoresMechanical Engineering ContributionsAún no hay calificaciones

- Aforo AduaneroDocumento3 páginasAforo AduaneroJuan Pablo Torres HerreraAún no hay calificaciones

- Solicitudes VariasDocumento7 páginasSolicitudes VariasEd QzAún no hay calificaciones

- Expresiones algebraicas 2o ESODocumento4 páginasExpresiones algebraicas 2o ESORodrigo Alonso Perez OrtuzarAún no hay calificaciones

- BandaMagnéticaAlmacenamientoInformaciónTiposDocumento9 páginasBandaMagnéticaAlmacenamientoInformaciónTiposDiego Francisco Mendoza FriasAún no hay calificaciones

- BGP PracticaDocumento28 páginasBGP PracticaPaola SalinasAún no hay calificaciones

- 15/febrero/2020. Unadm. Ing. en Desarrollo de Software: Programación Net IDocumento12 páginas15/febrero/2020. Unadm. Ing. en Desarrollo de Software: Programación Net IAntoniy StarkAún no hay calificaciones

- Ejercitarios Excel - Conceptos básicos, operaciones, funciones y formatosDocumento42 páginasEjercitarios Excel - Conceptos básicos, operaciones, funciones y formatosGeorge ArevalosAún no hay calificaciones

- Dam m06 Uf2 Pac1 RespuestasDocumento9 páginasDam m06 Uf2 Pac1 RespuestaskhsoldierAún no hay calificaciones

- Concepto de SeguridadDocumento6 páginasConcepto de SeguridadMiguel Angel Zapata MoralesAún no hay calificaciones

- Informe JclicDocumento33 páginasInforme JclicYoser MuñozAún no hay calificaciones

- 5.informe 2 - Redes Punto A PuntoDocumento6 páginas5.informe 2 - Redes Punto A PuntoJonathan MoralesAún no hay calificaciones

- Conclusiones y Recomendaciones David VargasDocumento2 páginasConclusiones y Recomendaciones David VargasDavidCaloAún no hay calificaciones

- Manual Android CreatorDocumento14 páginasManual Android CreatorPaul QuindeAún no hay calificaciones

- Consulta y recuperación CFDIDocumento15 páginasConsulta y recuperación CFDIRagde ZurcAún no hay calificaciones

- Clases de ConjuntoDocumento2 páginasClases de ConjuntoErwin PAAún no hay calificaciones

- ERIC base de datosDocumento12 páginasERIC base de datosDeivy René Hernández PérezAún no hay calificaciones

- Documentos de RequerimientosDocumento3 páginasDocumentos de Requerimientos3G Soluciones TecnologicasAún no hay calificaciones

- Norma ASARCODocumento3 páginasNorma ASARCOJorge Mauricio Levet100% (13)

- Videojuego RA con robot y móvilDocumento10 páginasVideojuego RA con robot y móvilGabriela VargasAún no hay calificaciones

- Manual Corel X7Documento50 páginasManual Corel X7RossAún no hay calificaciones

- Exportar Una Base de Datos en SQL Server A Otro Servidor SQL Server - Videlcloud PDFDocumento6 páginasExportar Una Base de Datos en SQL Server A Otro Servidor SQL Server - Videlcloud PDFJoar RoblesAún no hay calificaciones

- InvDocCam40Documento3 páginasInvDocCam40martinmaskorAún no hay calificaciones

- Mapa Conceptual Hipertexto TextoDocumento2 páginasMapa Conceptual Hipertexto TextoMaye TautivaAún no hay calificaciones

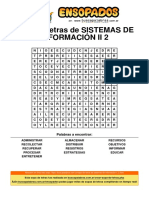

- Sopa de Letras de Sistemas de Información II 2Documento1 páginaSopa de Letras de Sistemas de Información II 2Alejandro Gutierrez0% (1)

- Pseudo Codigo AgendaDocumento2 páginasPseudo Codigo Agendafacster7Aún no hay calificaciones