Documentos de Académico

Documentos de Profesional

Documentos de Cultura

SOGrupoDTeoriaTema3 Parte1

Cargado por

bbaralucTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

SOGrupoDTeoriaTema3 Parte1

Cargado por

bbaralucCopyright:

Formatos disponibles

1

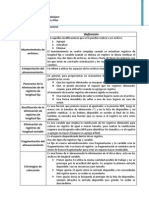

1. Conceptos generales

2. Esquemas de memoria basados en la

asignacin contigua

3. Recubrimientos (overlay)

4. Intercambio (swapping)

5. Organizacin de la Memoria Virtual

6. Gestin de la Memoria Virtual

7. Aspectos de implementacin en Unix

Tema 3. Organizacin y

Gestin de Memoria

2

Objetivos

B Conocer las distintas formas en las que el sistema operativo

puede organizar y gestionar la memoria fsica

B Saber en qu consiste y para qu se utiliza el mecanismo de

recubrimientos (overlays) y el intercambio (swapping)

B Entender qu es la Memoria Virtual y por qu se utiliza

B Conocer los mecanismos de paginacin, segmentacin y

segmentacin paginada y cmo se llevan a cabo en un

sistema con memoria virtual

B Comprender qu es la propiedad de localidad y su relacin

con el comportamiento de un programa en ejecucin

B Conocer la teora del conjunto de trabajo y el problema de la

hiperpaginacin

B Conocer cmo se implementan en Unix los conceptos

anterioes

3

1. Conceptos Generales

Jerarqua de Memoria

Objetivos generales

Espacio de direcciones lgico y

espacio de direcciones fsico

Carga absoluta y reubicacin

1.1 Jerarqua de Memoria

Dos principios sobre memoria:

Menor cantidad, acceso ms rpido

Mayor cantidad, menor coste por byte

As, los elementos frecuentemente accedidos se ponen

en memoria rpida, cara y pequea; el resto, en

memoria lenta, grande y barata.

CPU

Registros

Cach

Hardware

Memoria

Principal

Memoria

Auxiliar

Bus de memoria Bus de E/S

4

5

Conceptos sobre Cachs

B Cach - copia que puede ser accedida ms

rpidamente que el original

B Idea: hacer los casos frecuentes eficientes, los

caminos infrecuentes no importan tanto

B Acierto de cach: item en la cach

B Fallo de cach: item no en cach; hay que realizar la

operacin completa

B Tiempo de Acceso Efectivo (TAE) =

Probabilidad_acierto * coste_acierto +

Probabilidad_fallo * coste_fallo

B Funciona porque los programas no son aleatorios,

explotan la localidad principio de localidad

6

1.2 Objetivos generales

B Organizacin: cmo est dividida la memoria?

B Gestin: Dado un esquema de organizacin, qu

estrategias se deben seguir para obtener un

rendimiento ptimo?

Estrategias de asignacin

Estrategias de sustitucin (determinacin de qu zona

de memoria elegir para ser sustituida por otra)

Estrategias de bsqueda

B Proteccin

El SO de los procesos de usuario

Los procesos de usuario entre ellos

7

1.4 Carga absoluta y Reubicacin

Carga absoluta

Asignar direcciones fsicas

al programa en tiempo de

compilacin

Reubicacin

Capacidad de cargar y

ejecutar un programa en

un lugar arbitrario de la

memoria

Programa Fuente

Compilador

(y Encuadernador)

S.O.

Memoria Principal

X

N

Programa

Ejecutable

X

N

direcciones absolutas

Programa

Ejecutable

0

M

direcciones lgicas o relativas

?

es necesario

reubicarlo

Cargador

Cargador

8

Reubicacin esttica

Decisin de dnde

ubicar el programa en

tiempo de carga

El compilador

genera direcciones

lgicas (relativas)

direccin fsica = direccin de comienzo

+ direccin lgica

MOVE A, 100

0

M

Programa ejecutable

con direcciones lgicas

Memoria Principal

1000

1000 + M

MOVE A, 1100

9

Reubicacin dinmica

El compilador genera

direcciones lgicas

(relativas)

La traduccin de

direcciones lgicas a

fsicas se hace en

tiempo de ejecucin

direccin fsica = registro base +

direccin lgica

Memoria Principal

b

b + M

MOVE A, 100

CPU

Direccin

Lgica

+

Direccin

Fsica

Hardware

R.Base

b

10

Asignacin contigua y no contigua

Sistemas monoprogramados

Sistemas multiprogramados con

particiones:

- Particiones fijas

- Particiones variables

- Proteccin en sistemas multiprogramados

2. Esquemas de memoria basados

en la asignacin contigua

11

2.1 Asignacin contigua y no contigua

Podemos clasificar las organizaciones de memoria como:

B Contiguas - La asignacin de almacenamiento para un

programa se hace en un nico bloque de posiciones

continuas de memoria Particiones fijas y Particiones

variales

B No contiguas - Permiten dividir el programa en bloques

o segmentos que se pueden colocar en zonas no

necesariamente continuas de memoria principal

Paginacin, Segmentacin y Segmentacin paginada

12

2.2 Sistemas monoprogramados

B Memoria principal

dividida en dos partes:

S.O. residente

Proceso de usuario

B La asignacin contigua

en sistemas

monousuario

implementa proteccin

a travs del registro de

relocalizacin (o lmite)

SO

Proceso

de

usuario

No usada

CPU

a

registro

lmite

0

a

13

2.3 Sistemas multiprogramados

con particiones

B Existen varios procesos en memoria.

B El tamao mximo de cada proceso es el tamao de la

memoria fsica disponible.

B El esquema ms sencillo es dividir la memoria en

particiones cada una de las cuales puede ser ocupada

por un proceso. Existen dos formas de dividir la

memoria en particiones

Particiones fijas o estticas

Particiones variables o dinmicas

B La proteccin se obtiene a travs de los registros base

y lmite (sus valores para un proceso se guardan en su

PCB)

14

Particiones fijas

B El nmero y tamao de cada particin viene

establecido por el sistema y es constante

B Tamao de las particiones:

Particiones de igual tamao

Particiones de distinto tamao

B Estrategias de asignacin: proceso particin

Cola nica

Varias colas (particiones de distinto tamao)

15

Problema de las particiones fijas

B Uso de la memoria principal ineficiente.

Cualquier proceso, sin importar lo pequeo

que sea, ocupar una particin completa

B Fragmentacin: incapacidad del sistema

operativo para asignar posiciones de

memoria principal no utilizadas. Dos tipos:

interna y externa

B Problema de fragmentacin en particiones

fijas: Fragmentacin interna

16

Particiones variables

B Las particiones son variables en nmero y

tamao

B Cuando llega un proceso a memoria se le

asigna la memoria que necesita: se crea una

particin

B El SO mantiene informacin sobre las zonas

de memoria asignadas (tabla de particiones) y

las libres (huecos)

B Es necesario tener una estrategia de

asignacin y de gestin de espacio libre

17

Problema particiones variables

B Fragmentacin externa - existe el espacio

necesario para satisfacer una peticin pero no

es contiguo

B Compactacin - tcnica utilizada para reducir

la fragmentacin externa. Consiste en arrastrar

los contenidos de memoria a un lugar para

reunir toda la memoria libre en un bloque.

Problemas:

Requiere reubicacin dinmica

Consume recursos del sistema

El sistema se detiene mientras se realiza no se

puede hacer demasiado frecuentemente

18

Ejemplo fragmentacin externa

SO 148 k

896 k

SO 148 k

576 k

Proceso 1

320 k

SO 148 k

352 k

Proceso 1

320 k

Proceso 2 224 k

SO 128 k

268 k

Proceso 1

320 k

Proceso 2 224 k

Proceso 3

84 k

SO 148 k

268 k

Proceso 1

320 k

224 k

Proceso 3

64 k

SO 148 k

268 k

Proceso 1

320 k

Proceso 4

128 k

Proceso 3

64 k

96 k

SO 148 k

268 k

320 k

Proceso 4

128 k

Proceso 3

64 k

96 k

SO 148 k

268 k

230 k

Proceso 4

128 k

Proceso 3

64 k

96 k

Proceso 5

90 k

19

Particiones variables: Estrategias de

asignacin de espacio

B Cmo satisfacer una peticin de tamao n

desde una lista de huecos? Estrategias:

Primer ajuste asigna el primer hueco lo

suficientemente grande para satisfacer la peticin

Mejor ajuste asigna el hueco ms pequeo que

mejor se ajuste al espacio necesitado. Se debe

buscar en la lista entera, si no esta ordenada por

tamaos. Produce el hueco sobrante menor.

Peor ajuste - asigna el hueco mayor. Debemos

buscar en toda la lista. Produce el hueco sobrante

mayor

20

Ejemplo: Primer Ajuste

Sistema Operativo

Hueco de 16K

Hueco de 14K

Hueco de 5K

Hueco de 30K

0

a

b

c

d

e

f

g

Direc.

inicial

Lon-

gitud

a

c

e

g

16K

14K

5K

30K

Lista espacio libre

(orden por direcc.)

Solicitudes

13 K

Produce un hueco de 3K

21

Ejemplo: El Mejor Ajuste

Sistema Operativo

Hueco de 16K

Hueco de 14K

Hueco de 5K

Hueco de 30K

0

a

b

c

d

e

f

g

Direc.

inicial

Lon-

gitud

e

c

a

g

5k

14k

16k

30k

Lista espacio libre

(orden ascendente

tamao de hueco)

Solicitudes

13 K

Produce un hueco de 1K

22

Ejemplo: El Peor Ajuste

Sistema Operativo

Hueco de 16K

Hueco de 14K

Hueco de 5K

Hueco de 30K

0

a

b

c

d

e

f

g

Direc.

inicial

Lon-

gitud

g

a

c

e

30K

16K

14K

5K

Solicitudes

13 K

Lista espacio libre

(orden descendente

tamao de hueco)

Produce un hueco de 17K

23

Gestin de espacio libre

Estado actual

de la M.P.

MAPA DE BITS :

Divide la memoria principal en unidades

de asignacin y se utiliza un bit por cada

una de ellas que indica si est libre (0) u

ocupada (1)

1 1 1 1 1 0 0 0 1

1 1 1 1 1 1 1 1 1

0 0 1 1 1 0 0 .

D

C

B

A

5

10

15

20

25

LISTA ENCADENADA (O ENLAZADA) :

P (Particin)

H (Hueco)

Direccin

de comienzo

Tamao

P 0 5 H 6 3 P 8 6 P 14 4

H 18 2 P 20 3 H 24 3

24

Proteccin en sistemas

multiprogramados

Reubicacin esttica

Reubicacin dinmica

CPU

c

d

Memoria Principal

S.O.

Particin 1

Particin 2

Particin 3

Particin 4

Particin 5

0

a

b

c

d

e

R.Base

R.Lmite

25

3. Recubrimientos (overlays)

B Era un mecanismo para

ejecutar programas ms

grandes que la

memoria. En memoria

slo se tenan las

instrucciones y datos

que se necesitan en un

momento dado

B El SO no da soporte. Es

responsabilidad del

programador disear y

programar la estructura

de overlays

Memoria

Programa

SO

Cdigo y

datos

residentes

Inicializar

Procesar

Salir

Area de

recubri-

miento

1

2

3

26

4. Intercambio (Swapping)

B Intercambiar procesos entre memoria y un

almacenamiento auxiliar

B El almacenamiento auxiliar debe ser un disco

rpido con espacio para albergar las imgenes

de memoria de los procesos de usuario

B El factor principal en el tiempo de intercambio

es el tiempo de transferencia

B El intercambiador tiene las siguientes

responsabilidades:

Seleccionar procesos para retirarlos de MP

Seleccionar procesos para incorporarlos a MP

Gestionar y asignar el espacio de intercambio

27

Localizacin del espacio de

intercambio

B Intercambio Dinmico:

Un archivo de intercambio global del sistema

cubre las necesidades de intercambio de todos

los procesos

Problema: eleccin de su tamao

B Intercambio Esttico:

Existe un archivo de intercambio dedicado por

cada proceso intercambiable del sistema

Elimina el problema del tamao

No impone lmites al nmero de procesos

intercambiados

Problema: Necesita ms espacio en disco, los

accesos son ms lentos y los direccionamientos

son ms complicados

28

5. Organizacin de la

Memoria Virtual

Concepto de memoria virtual

Paginacin

Segmentacin

Segmentacin paginada

29

5.1 Concepto de memoria virtual

B Memoria Virtual

El tamao del programa, los datos y la pila

puede exceder la cantidad de memoria

fsica disponible para l.

Se usa un almacenamiento a dos niveles:

Memoria Principal partes del proceso

necesarias en un momento dado

Memoria Secundaria espacio de

direcciones completo del proceso

30

Concepto de memoria virtual (y II)

Es necesario:

saber qu se encuentra en memoria

principal

una poltica de movimiento entre MP y MS

B Adems, la memoria virtual

resuelve el problema del crecimiento

dinmico de los procesos

puede aumentar el grado de

multiprogramacin

31

Unidad de Gestin de Memoria

B La MMU (Memory Management Unit) es un

dispositivo hardware que traduce direcciones

virtuales a direcciones fsicas Este dispositivo

est gestionado por el SO!

B En el esquema MMU ms simple, el valor del

registro base se aade a cada direccin

generada por el proceso de usuario al mismo

tiempo que es enviado a memoria

B El programa de usuario trata slo con

direcciones lgicas; ste nunca ve direcciones

reales

32

Unidad de Gestin de Memoria (y II)

B Adems de la

traduccin, el MMU

deber:

- detectar si la

direccin aludida se

encuentra o no en

MP

- generar una

excepcin si no se

encuentra en MP

Tarjeta del procesador

Memoria

CPU

MMU

direccin

virtual

direccin

fsica

Controlador

de disco

BUS

33

5.2 Paginacin

B El espacio de direcciones fsicas de un proceso

puede ser no contiguo

B La memoria fsica se divide en bloques de

tamao fijo, denominados marcos de pgina. El

tamao es potencia de dos, de 0.5 a 8 Kb

B El espacio lgico de un proceso se divide en

bloques del mismo tamao, denominados

pginas

B Los marcos de pginas contendrn pginas de

los procesos

34

Paginacin (y II)

B Las direcciones lgicas, que son las que

genera la CPU se dividen en nmero de

pgina (p) y desplazamiento dentro de la

pgina (d)

B Las direcciones fsicas se dividen en

nmero de marco (m, direccin base del

marco donde est almacenada la pgina) y

desplazamiento (d)

p d

m d

35

Paginacin (y III)

B Cuando la CPU genere una direccin lgica

ser necesario traducirla a la direccin fsica

correspondiente, la tabla de pginas mantiene

informacin necesaria para realizar dicha

traduccin. Existe una tabla de pginas por

proceso

B Tabla de ubicacin en disco (una por proceso)

ubicacin de cada pgina en el

almacenamiento secundario

B Tabla de marcos de pgina, usada por el S.O. y

contiene informacin sobre cada marco de

pgina

36

Contenido de la tabla de pginas

Una entrada por cada pgina del proceso:

B Nmero de marco (direccin base del marco) en

el que est almacenada la pgina si est en MP

B Bit de presencia o bit vlido

B Bit de modificacin

B Modo de acceso autorizado a la pgina (bits de

proteccin)

n marco presencia modificacin proteccin

46 1 0 01

N de pgina

37

Ejemplo: contenido de la tabla de pginas

Memoria T.P.

secundaria

Memoria

Fsica

Pag3

Pag4

Pag10

Pag7

Pag1

Pag12

Pag1

Pag2

Pag3

Pag4

Pag5

Pag6

Pag7

Pag8

Pag9

Pag10

Pag11

pag12

8

-

1

2

-

-

6

3

-

5

-

10

1

2

3

4

5

6

7

8

9

10

Num.

Marco

1

2

3

4

5

6

7

8

9

10

11

12 Num. Pagina

1

0

1

1

0

0

1

0

0

1

-

1

N de

Marco

Bit de

presencia

...

...

...

...

...

...

...

...

...

...

...

...

38

Esquema de traduccin

m

DESPLAZAMIENTO

Direccin real

DESPLAZAMIENTO N. pagina

Direccin virtual

RBTP

m 1

N. de marco presencia modificacin pro.

TABLA DE PAGINAS

FALTA DE PAGINA

si

no

Presencia

= 1

si

no

Acceso autorizado?

excepcin

violacin de privilegios

Actualizar bit de

modificacin? (si/

no)

Dir. TUD

Tabla de Ubicacin en Disco

39

Falta de pgina

1. Bloquear proceso

2. Encontrar la ubicacin en disco de la pgina

solicitada (tabla de ubicacin en disco)

3. Encontrar un marco libre. Si no hubiera, se

puede optar por desplazar una pgina de MP

4. Cargar la pgina desde disco al marco de MP

5. Actualizar tablas (bit presencia=1, n marco, ...)

6. Desbloquear proceso

7. Reiniciar la instruccin que origin la falta de

pgina

40

Implementacin de la Tabla

de Pginas

B La tabla de pginas se mantiene en memoria

principal

B El registro base de la tabla de pginas (RBTP)

apunta a la tabla de pginas (suele

almacenarse en el PCB del proceso)

B En este este esquema:

cada acceso a una instruccin o dato

requiere dos accesos a memoria: uno a la

tabla de pginas y otro a memoria

un problema adicional viene determinado por

el tamao de la tabla de pginas

41

Tamao de la Tabla de Pginas

B Ejemplo:

Direccin virtual: 32 bits.

Tamao de pgina = 4 Kbytes (2

12

bytes).

-tamao del campo desplazamiento = 12 bits

-tamao nmero de pgina virtual = 20 bits

- N de pginas virtuales = 2

20

= 1,048,576!

B Solucin para reducir el tamao de la TP:

Paginacin multinivel

42

Paginacin multinivel

B Esta solucin opta por paginar las tablas de

pginas

B La particin de la tabla de pginas permite al

SO dejar particiones no usadas sin cargar

hasta que el proceso las necesita. Aquellas

porciones del espacio de direcciones que no

se usan no necesitan tener tabla de pgina

43

Paginacin a dos niveles

B Lo que hacemos es paginar la tabla de

pginas.

B La direccin lgica se divide en:

nmero de pgina (n bits):

un nmero de pgina p1 (=k)

desplazamiento de pgina p2 (=n-k)

desplazamiento de pgina d (m bits)

B As una direccin lgica es de la forma:

p1 p2 d

44

Esquema de paginacin a dos niveles

. . .

. . .

. . .

. . .

. . . . . .

p1 p2 d

Tabla de pginas

de primer nivel Tablas de pginas

de segundo nivel

Memoria

fsica

45

Ejemplo: Esquema de paginacin a

dos niveles

Memoria

secundaria

Memoria

Fsica

Pag3

Pag4

Pag1_TP

Pag10

Pag7

Pag3_TP

Pag1

Pag12

Pag1

Pag2

Pag3

Pag4

Pag5

Pag6

Pag7

Pag8

Pag9

Pag10

Pag11

pag12

8

-

1

2

1

2

3

4

5

6

7

8

9

10

Num.

Marco

1

2

3

3

--

7

Tabla de pag.

1 Nivel

-

-

6

-

-

5

-

10

Tablas de pag.

2 Nivel

Pag 1 de la TP

Pag 2 de la TP

Pag 3 de la TP

Num. de

pag de la

TP

1

2

3

4

1

2

3

4

1

2

3

4

46

Pginas compartidas

B Una copia de

cdigo de solo

lectura (reentrante)

compartido entre

varios procesos.

Ej. editores,

compiladores,

sistemas de

ventanas

ed 1

ed 2

ed 3

data 1

ed 1

ed 2

ed 3

data 2

ed 1

ed 2

ed 3

data 3

3

4

6

1

3

4

6

7

3

4

6

2

data 1

data 3

ed 1

ed 2

ed 3

data 2

0

1

2

3

4

5

6

7

8

9

Proceso P1

Proceso P2

Proceso P3

Tabla de

pginas

para P1

Tabla de

pginas

para P2

Tabla de

pginas

para P3

Memoria

47

5.3 Segmentacin

B Esquema de

organizacin de memoria

que soporta mejor la

visin de memoria del

usuario: un programa es

una coleccin de

unidades lgicas -

segmentos-, p. ej.

procedimientos,

funciones, pila, tabla de

smbolos, matrices, etc.

S1

S2

S3

S4

S1

S4

S3

S2

Espacio de

usuario

Memoria

fsica

48

Tabla de Segmentos

B Una direccin lgica es una tupla:

<nmero_de_segmento, desplazamiento>

B La Tabla de Segmentos aplica direcciones

bidimensionales definidas por el usuario en

direcciones fsicas de una dimensin. Cada

entrada de la tabla tiene los siguientes

elementos (aparte de presencia, modificacin y

proteccin):

base - direccin fsica donde reside el inicio

del segmento en memoria.

tamao - longitud del segmento.

49

Implementacin de la Tabla de

Segmentos

B La tabla de segmentos se mantiene en

memoria principal

B El Registro Base de la Tabla de Segmentos

(RBTS) apunta a la tabla de segmentos (suele

almacenarse en el PCB del proceso)

B El Registro Longitud de la Tabla de Segmentos

(STLR) indica el nmero de segmentos del

proceso; el n de segmento s, generado en una

direccin lgica, es legal si s < STLR (suele

almacenarse en el PCB del proceso)

50

Esquema de traduccin

S + d

Direccin real

d N. Segmento

Direccin virtual

FALTA DE

SEGMENTO

si

no

Acceso autorizado?

Excepcin

violacin de privilegios

Actualizar bit de

modificacin? (si/

no)

S t

D. base tamao presencia modif. pro.

TABLA DE SEGMENTOS

1

si

no

Presencia

= 1

si

no

d > t

Excepcin

acceso indebido

RBTS

Dir. TUD

Tabla de Ubicacin en Disco

51

5.4 Segmentacin Paginada

(NO ENTRAN PROBLEMAS)

B La variabilidad del tamao de los segmentos y

el requisito de memoria contigua dentro de un

segmento complica la gestin de MP y MS

B Por otro lado, la paginacin simplifica eso pero

complica ms los temas de comparticin y

proteccin (stos van mejor en segmentacin) .

B Algunos sistemas combinan ambos enfoques,

obteniendo la mayora de las ventajas de la

segmentacin y eliminando los problemas de

una gestin de memoria compleja

52

Esquema de traduccin

+

RBTS

s p d

d m

Tabla de Pginas

del segmento s

s : direccin base de la Tabla de

Pginas del segmento s

+

si

s t

d<t

Tabla de

Segmentos

direccin

virtual

presente?

m d

si

direccin

fsica

También podría gustarte

- Mantenimiento de Disco DuroDocumento8 páginasMantenimiento de Disco Duroobed Dominguez lopezAún no hay calificaciones

- Modulo Gestion de Bases de DatosDocumento150 páginasModulo Gestion de Bases de DatosDiego FernandoAún no hay calificaciones

- Diferencia Entre Fragmentación Interna yDocumento5 páginasDiferencia Entre Fragmentación Interna yCopito Max GarciaCastroAún no hay calificaciones

- SC-345 Sistemas Operativos IIDocumento258 páginasSC-345 Sistemas Operativos IIDan100% (3)

- Gestión memoria Linux vs WindowsDocumento16 páginasGestión memoria Linux vs WindowsJuan Ignacio TellecheaAún no hay calificaciones

- Cuadro CamparativoDocumento5 páginasCuadro CamparativoTecnologías Informáticos, computacionales.Aún no hay calificaciones

- Cátedra:: Sistemas Operativos Año 2020 Trabajo Práctico N 7Documento3 páginasCátedra:: Sistemas Operativos Año 2020 Trabajo Práctico N 7juan godoyAún no hay calificaciones

- Unidad 5. Recurso 1. Fragmantación de ArchivosDocumento8 páginasUnidad 5. Recurso 1. Fragmantación de ArchivosYRMA FAMILIA DE OLEOAún no hay calificaciones

- PRESENTACION2Documento43 páginasPRESENTACION2Josue SirlupuAún no hay calificaciones

- Tema 6Documento32 páginasTema 6Pedro SilvaAún no hay calificaciones

- Gestión de memoria: paginación, particionamiento y algoritmos de ubicaciónDocumento8 páginasGestión de memoria: paginación, particionamiento y algoritmos de ubicaciónsebas montalvo100% (1)

- Clase 08 - Unidad 4 Admin Mem PrincipalDocumento33 páginasClase 08 - Unidad 4 Admin Mem PrincipalCrhistopher Nuñez VargasAún no hay calificaciones

- Archivos Log Del SGBDocumento5 páginasArchivos Log Del SGBalberto alarcon resendiz100% (1)

- 1 Asir FH PDFDocumento14 páginas1 Asir FH PDFAngy Ortega FernándezAún no hay calificaciones

- Administración de Archivos y Memorias Foro 2Documento3 páginasAdministración de Archivos y Memorias Foro 2cuastecomatenayAún no hay calificaciones

- Mantenimiento de ArchivosDocumento1 páginaMantenimiento de Archivosmao-19899958100% (1)

- ¿Qué Es Un ArchivoDocumento7 páginas¿Qué Es Un ArchivoPabloAún no hay calificaciones

- Asignación de MemoriaDocumento29 páginasAsignación de MemoriaALEX100% (5)

- Fragmentacion VerticalDocumento19 páginasFragmentacion VerticalMarco Antonio Soria CastillejoAún no hay calificaciones

- Oracle Admin Is Trac Ion de Base de DatosDocumento204 páginasOracle Admin Is Trac Ion de Base de DatosAguedo HuamaniAún no hay calificaciones

- Trabajo de InvestigaciónDocumento16 páginasTrabajo de InvestigaciónDANIEL JESHUA CRUZ OLVERAAún no hay calificaciones

- Tema 3 - IsoDocumento12 páginasTema 3 - IsoGonzalo Leite PereiraAún no hay calificaciones

- Examen - Tema 1 - IsODocumento4 páginasExamen - Tema 1 - IsOFidelico Sanchez LopezAún no hay calificaciones

- Fragmentacion VerticalDocumento4 páginasFragmentacion VerticalPiero QsAún no hay calificaciones

- Historia y componentes de los computadoresDocumento45 páginasHistoria y componentes de los computadoresPablo García-Lluis Ramírez100% (1)

- PDF Sistemas Operativos Tema 5 Sistemas de ArchivosDocumento78 páginasPDF Sistemas Operativos Tema 5 Sistemas de ArchivosDiego Mejia Diego MejiaAún no hay calificaciones

- EXAMEN Final SISTEMAS OPERATIVOSDocumento4 páginasEXAMEN Final SISTEMAS OPERATIVOSJuan Carlos MoraAún no hay calificaciones

- Gestion de Memoria Secundaria TrabajoDocumento8 páginasGestion de Memoria Secundaria Trabajomariorks gonzalezAún no hay calificaciones

- Bases de Datos IDocumento170 páginasBases de Datos IJosé MartinezAún no hay calificaciones

- MAPA CONCEPTUAL Diferentes Técnicas de La Administración de Memoria Real.Documento2 páginasMAPA CONCEPTUAL Diferentes Técnicas de La Administración de Memoria Real.Cruz Vargas Miguel AngelAún no hay calificaciones