Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Tarea de Entrega Obligatoria #3

Cargado por

Tañis CardenasTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Tarea de Entrega Obligatoria #3

Cargado por

Tañis CardenasCopyright:

Formatos disponibles

Introducción a los Sistemas Lógicos y Digitales – Año 2020

Trabajo de entrega obligatoria Nº 3

La tarea permanecerá abierta durante los 90 minutos posteriores a su apertura.

Pasado dicho lapso de tiempo se dará por finalizada automáticamente y el sistema no admitirá

la carga de nuevos archivos.

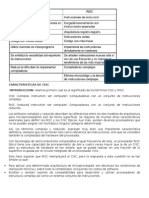

Se requiere implementar el siguiente circuito en un dispositivo lógico programable. El circuito conmuta

periódicamente entre las salidas de dos funciones lógicas (Sa y Sb). El tiempo de conmutación está

controlado por el bloque “Control” y la salida H es como se muestra en el diagrama de tiempos adjunto:

durante un período del reloj (denominado CLK) H=Sa y durante el siguiente período H=Sb. El ciclo se

repite indefinidamente y no tiene importancia qué función inicia la secuencia. Para optimizar la

temporización del circuito también se requiere colocar un registro tipo D a la salida. Este registro debe

cumplir los siguientes requerimientos:

• Ser activo con el flanco de subida del reloj CLK.

• Tener una entrada de Habilitación activa en alto:

[1] – Habilita el FF

[0] – Deshabilita el FF

• Tener una señal de reset asincrónico (RSTn_Asinc) activa en bajo.

• Tener una señal de reset sincrónico (RSTn_Sinc) también activa en bajo.

a) Diseñe la lógica del bloque “Control” y el registro de salida teniendo en cuenta los requerimientos

listados. Implemente en VHDL el diseño con Quartus II utilizando la menor cantidad de recursos

posible.

b) Utilizando ModelSim simule el diseño y compruebe que se comporta de la forma esperada. En la

simulación se debe visualizar el comportamiento de:

• La señal de Habilitación del FF.

• Las señales de reset del FF (RSTn_Asinc y RSTn_Sinc).

• La señal de salida del bloque “Control” M.

• La señal H.

• La señal de salida Out.

Habilitación

RSTn_Asinc

RSTn_Sinc

X Sa

Y Función A 0

Z

H

D Q Out

Sb 1

Función B FF

Control

CLK

Tabla de verdad de A y B

X Y Z Sa Sb

0 0 0 1 0

0 0 1 0 1 CLK

0 1 0 0 0

0 1 1 0 1

1 0 0 1 1 H Función A Función B Función A Función B

1 0 1 0 0

1 1 0 1 1

1 1 1 1 0

SUGERENCIAS:

- En la simulación de las señales de Habilitación y reset del FF puede utilizar la edición manual

de las formas de onda como fue visto en las clases prácticas.

- Para diseñar la lógica del bloque “Control” tenga en cuenta que la señal H conmuta a la mitad

de la frecuencia de la que lo hace la señal de reloj CLK. Ejercicios de prácticas anteriores

pueden ayudarle a resolver el problema.

- Identifique claramente los puertos de entrada y salida de la entidad y cuáles serán las SEÑALES

de interconexión internas.

En la tarea correspondiente de la plataforma Moodle deberá subir los siguientes archivos:

1) El archivo fuente VHDL de extensión *.vhd ó *.vhdl

2) Una captura de pantalla del esquema RTL generado por el sintetizador del Quartus II.

3) Una o las captura/s de pantalla de la simulación donde se visualicen todas las señales y

puertos de entrada y salida indicados.

El formato de los archivos de imagen puede ser *.jpg, *.jpeg ó *.bmp.

IMPORTANTE:

- Todos los archivos que adjunte deberán contener su apellido y número de alumno.

- En el caso de las fotos estos datos deben ser visibles dentro de las mismas.

- Puede adjuntar hasta 5 archivos no pudiendo superar los 10 MB entre todos ellos.

- Subir ÚNICAMENTE los archivos solicitados a fin de no sobrecargar los servidores.

También podría gustarte

- 12 03-DispPasivoDocumento16 páginas12 03-DispPasivoTañis CardenasAún no hay calificaciones

- TP2 2021Documento2 páginasTP2 2021Tañis CardenasAún no hay calificaciones

- Intro VHDL PDFDocumento76 páginasIntro VHDL PDFFelix Alfredo Vilchez TupayachiAún no hay calificaciones

- Laboratorio 2 Rajoy - Cardenas - Corregido - FNDocumento4 páginasLaboratorio 2 Rajoy - Cardenas - Corregido - FNTañis CardenasAún no hay calificaciones

- Islyd2017 - p4 Intro VHDLDocumento2 páginasIslyd2017 - p4 Intro VHDLrodmigan89Aún no hay calificaciones

- Notas Sobre Electrostatica VacioDocumento31 páginasNotas Sobre Electrostatica VacioTañis CardenasAún no hay calificaciones

- TP1 2023Documento46 páginasTP1 2023Tañis CardenasAún no hay calificaciones

- Parciales M1 CyODocumento12 páginasParciales M1 CyOTañis CardenasAún no hay calificaciones

- Tema 6 Registros de Desplazamiento 2009Documento25 páginasTema 6 Registros de Desplazamiento 2009Tañis CardenasAún no hay calificaciones

- ISLyD2017 P1Documento2 páginasISLyD2017 P1rodmigan89Aún no hay calificaciones

- Tarea de Entrega Opcional #3ADocumento1 páginaTarea de Entrega Opcional #3ATañis CardenasAún no hay calificaciones

- Cronograma Legal 1 Cuatrimestre 2020 FinalDocumento2 páginasCronograma Legal 1 Cuatrimestre 2020 FinalTañis CardenasAún no hay calificaciones

- 2019-09-19-195937-96 Introducción Al VHDLDocumento91 páginas2019-09-19-195937-96 Introducción Al VHDLTañis CardenasAún no hay calificaciones

- Derechos de las personasDocumento47 páginasDerechos de las personasTañis CardenasAún no hay calificaciones

- DerechoLaboralLCTDocumento80 páginasDerechoLaboralLCTTañis CardenasAún no hay calificaciones

- Derecho AdministrativoDocumento43 páginasDerecho AdministrativoTañis CardenasAún no hay calificaciones

- NotasClase17 2020Documento12 páginasNotasClase17 2020Tañis CardenasAún no hay calificaciones

- ModeloVonNeumannDocumento47 páginasModeloVonNeumannTañis CardenasAún no hay calificaciones

- Arquitectura 2021 Clase 4 - Mejoras ISA, Parte 1Documento22 páginasArquitectura 2021 Clase 4 - Mejoras ISA, Parte 1Tañis CardenasAún no hay calificaciones

- NotasClase19 2020Documento9 páginasNotasClase19 2020Tañis CardenasAún no hay calificaciones

- Derecho Procesal Ing - UNLPDocumento25 páginasDerecho Procesal Ing - UNLPDiego Conde PérezAún no hay calificaciones

- Muestreo y reconstrucción de señalesDocumento11 páginasMuestreo y reconstrucción de señalesTañis CardenasAún no hay calificaciones

- Arquitectura 2021 Clase 2 - Buses y El Ciclo de InstrucciónDocumento45 páginasArquitectura 2021 Clase 2 - Buses y El Ciclo de InstrucciónTañis CardenasAún no hay calificaciones

- Señales y sistemas: Análisis de señales periódicas y transformacionesDocumento17 páginasSeñales y sistemas: Análisis de señales periódicas y transformacionesTañis CardenasAún no hay calificaciones

- Tipos de SeñalesDocumento13 páginasTipos de SeñalesTañis CardenasAún no hay calificaciones

- NotasClase09 2019 PDFDocumento14 páginasNotasClase09 2019 PDFTañis CardenasAún no hay calificaciones

- Arquitectura 2021 Clase 3 - Lenguaje EnsambladorDocumento21 páginasArquitectura 2021 Clase 3 - Lenguaje EnsambladorMeli MonteroAún no hay calificaciones

- Arquitectura 2021 Clase 5 - Mejoras ISA, Parte 2Documento27 páginasArquitectura 2021 Clase 5 - Mejoras ISA, Parte 2Tañis CardenasAún no hay calificaciones

- Tipos de SeñalesDocumento13 páginasTipos de SeñalesTañis CardenasAún no hay calificaciones

- Silabo Del CursoDocumento6 páginasSilabo Del Cursodina241221Aún no hay calificaciones

- Programacion - Cap10 - Melanie Andrea Gatica SteeleDocumento5 páginasProgramacion - Cap10 - Melanie Andrea Gatica SteeleSilvestre MendozaAún no hay calificaciones

- Ensamblador: Instrucciones, declaraciones y proyectoDocumento9 páginasEnsamblador: Instrucciones, declaraciones y proyectoConne Minely Gil MoralesAún no hay calificaciones

- IntroduccionalosalgoritmosDocumento7 páginasIntroduccionalosalgoritmosJavier Angulo OsorioAún no hay calificaciones

- Sistemas OperativosDocumento2 páginasSistemas OperativosEver Medina GonzálezAún no hay calificaciones

- AUTO15Documento4 páginasAUTO15Copiapó AtacamaAún no hay calificaciones

- Antología de Lenguaje Ensamblador - SCM-0421Documento73 páginasAntología de Lenguaje Ensamblador - SCM-0421The-Game KinkiAún no hay calificaciones

- Lenguajes de Programacion de Un RobotDocumento6 páginasLenguajes de Programacion de Un RobotGabriel OrtizAún no hay calificaciones

- Actividad No. 1 - Inteligencia ArtificialDocumento7 páginasActividad No. 1 - Inteligencia Artificialاستنفورد والAún no hay calificaciones

- Virtualizacion de Serv. de InfraDocumento4 páginasVirtualizacion de Serv. de InfraDavi GarciaAún no hay calificaciones

- Tema 3. Gramaticas y LenguajesDocumento97 páginasTema 3. Gramaticas y LenguajesClaudia Esnarrizaga RodríguezAún no hay calificaciones

- Supervision NetworkingDocumento45 páginasSupervision NetworkingNoe Muñoz QuitoAún no hay calificaciones

- Configuracion Linux Parte 1Documento40 páginasConfiguracion Linux Parte 1EMANUEL UZIEL SALCEDO DURANAún no hay calificaciones

- Ping Traceroute EjerciciosDocumento3 páginasPing Traceroute EjerciciosFrancisco Félix Atoche BethencourtAún no hay calificaciones

- Semana 13. Comunicacion Serial Con El ComputadorDocumento4 páginasSemana 13. Comunicacion Serial Con El ComputadorIsmael GarciaAún no hay calificaciones

- Estructura de Un Programa FortranDocumento20 páginasEstructura de Un Programa Fortranalan1633Aún no hay calificaciones

- Análisis de AlgoritmosDocumento54 páginasAnálisis de AlgoritmosDIEGO GONZALO FERNANDEZ SANCHEZAún no hay calificaciones

- Patrones de Diseño de Software - DevExpertoDocumento11 páginasPatrones de Diseño de Software - DevExpertoJeal Djesús Obispo100% (1)

- Practica PL2 2014-2015Documento41 páginasPractica PL2 2014-2015Don LimonAún no hay calificaciones

- Laboratorio No. 1Documento8 páginasLaboratorio No. 1Xavier BolañosAún no hay calificaciones

- Julian Ramiro Lopez - Unidad 2 - Paso 3 - Comprensión Del ProyectoDocumento10 páginasJulian Ramiro Lopez - Unidad 2 - Paso 3 - Comprensión Del ProyectoJulian LopezAún no hay calificaciones

- Plan de DesarrolloDocumento73 páginasPlan de DesarrollooscarAún no hay calificaciones

- Trabajo en Clase N°4 Ejercicios de Optimización Con Programación No LinealDocumento2 páginasTrabajo en Clase N°4 Ejercicios de Optimización Con Programación No LinealGeovanny Efrain RamirezAún no hay calificaciones

- SGW1 Ia2 MMP Um SDocumento20 páginasSGW1 Ia2 MMP Um Sklever vallejoAún no hay calificaciones

- Curriculum JJHDocumento2 páginasCurriculum JJHjonso180323Aún no hay calificaciones

- Presentacion C++Documento43 páginasPresentacion C++Camilo Bravo0% (1)

- Descripcion Del Sistema ContableDocumento3 páginasDescripcion Del Sistema ContableshirlyAún no hay calificaciones

- DAW JqueryDocumento5 páginasDAW JqueryManuel Fernández MíguezAún no hay calificaciones

- Caracteristicas de CiscDocumento3 páginasCaracteristicas de CiscWilliam Fernando Garcia100% (1)

- Guía entrega equipos bodegaDocumento10 páginasGuía entrega equipos bodegaCristian HernandezAún no hay calificaciones