Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Tema 5. Familias Lógicas

Cargado por

E&GDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Tema 5. Familias Lógicas

Cargado por

E&GCopyright:

Formatos disponibles

Tema 5: Familias Lógicas.

ÍNDICE

1. CONCEPTOS PREVIOS 2

1.1. Circuitos Integrados (CI) ...................................................................................................................... 2

1.2. Encapsulados de los CI ........................................................................................................................... 2

1.3. Zócalos de conexión ................................................................................................................................ 2

1.4. Numeración de patillas ........................................................................................................................... 3

1.5. Estructura.................................................................................................................................................. 3

2. CARACTERÍSTICAS DE UNA FAMILIA LÓGICA 4

2.1. Tensión de alimentación (VCC)............................................................................................................... 4

2.2. Niveles de tensión de entrada y salida ............................................................................................. 5

2.3. Inmunidad al ruido .................................................................................................................................. 6

2.4. Disipación de potencia ........................................................................................................................... 7

2.5. Capacidad de carga (fan-out) .............................................................................................................. 7

2.6. Tiempo de propagación (tp)................................................................................................................... 8

3. FAMILIAS LÓGICAS 10

3.1. Familia lógica TTL .................................................................................................................................. 12

3.2. Familia lógica CMOS ............................................................................................................................. 13

3.3. Comparativa entre las familias lógicas TTL y CMOS ................................................................. 14

3.4. Nomenclatura ......................................................................................................................................... 15

4. DATOS DE CATÁLOGO 17

5. PUERTAS LÓGICAS 19

6. CONEXIÓN DEL CI EN LA PROTOBOARD 21

7. ESQUEMAS DE CI CON PUERTAS LÓGICAS 22

7.1. Puerta lógica NOT ................................................................................................................................ 22

7.2. Puerta lógica AND................................................................................................................................ 23

Encarnación Marín Caballero Página 1 de 23

Tema 5: Familias Lógicas.

1. CONCEPTOS PREVIOS

1.1. Circuitos Integrados (CI)

1.2. Encapsulados de los CI

1.3. Zócalos de conexión

Encarnación Marín Caballero Página 2 de 23

Tema 5: Familias Lógicas.

1.4. Numeración de patillas

Ejemplo: Circuito integrado con encapsulado DIP de 14 pines.

1.5. Estructura

Chip

Pines

Encarnación Marín Caballero Página 3 de 23

Tema 5: Familias Lógicas.

2. CARACTERÍSTICAS DE UNA FAMILIA LÓGICA

Cada una de las familias lógicas posee unas determinadas características.

A continuación, vamos a definir los principales parámetros y características de un circuito

lógico integrado.

Tensión de alimentación (VCC).

Niveles de tensión de entrada y salida.

Inmunidad al ruido.

Disipación de potencia.

Capacidad de carga (fan-out).

Tiempo de propagación (tp).

Estos parámetros los podremos encontrar en las hojas de características que nos facilitan los

fabricantes y que, en la actualidad, se encuentran con facilidad en Internet.

2.1. Tensión de alimentación (VCC)

Para que los circuitos lógicos integrados en un CI puedan funcionar, es necesario conectarlos a

una fuente de alimentación de corriente continua, que garantice que la tensión suministrada (VCC) al CI

permanezca lo más constante posible aunque varíe la intensidad de corriente suministrada por la misma.

El positivo de dicha fuente se suele conectar a la patilla del CI que aparece señalada como V CC y

el negativo a otra denominada GND (tierra o masa).

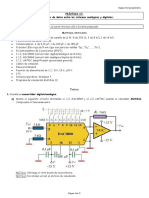

Ejemplo: Conexión de la fuente de alimentación a un CI de la serie 7408.

Ejemplo: Para la familia lógica TTL la tensión de alimentación es de +5 V, aunque se admite un

rango de tolerancia que varía entre 4,75 V y 5,25 V.

Ejemplo: Para la alimentación de los circuitos CMOS, se admite un rango de tensión mucho más

amplio, que varía entre los 3 V y los 15 V.

Encarnación Marín Caballero Página 4 de 23

Tema 5: Familias Lógicas.

2.2. Niveles de tensión de entrada y salida

Los niveles de tensión de entrada nos indican la tensión que deberemos aplicar a la entrada de

una puerta lógica para que ésta lo acepte como un estado lógico «1» ó «0».

En las hojas de características nos indican los valores límites que se corresponden a los niveles

lógicos, como son:

VIL (máx): máxima tensión de entrada (I) admisible para que la puerta interprete un «0» lógico o

un nivel bajo (L).

VIH (mín): mínima tensión de entrada (I) admisible para que la puerta interprete un «1» lógico o

un nivel alto (H).

Dado que las puertas lógicas se interconectan entre sí, es importante conocer la tensión que

suministra una puerta a su salida en los dos estados lógicos, para así asegurarnos de que puede activar a

las siguientes puertas que se conecten a su salida.

Los niveles de tensión de salida son:

VOL (máx): máxima tensión que aparece en la salida (O) para el estado lógico «0» lógico o nivel

alto (L).

VOH (mín): mínima tensión que aparece en la salida (0) para el estado lógico «1» lógico o un nivel

bajo (H).

Ejemplo: Niveles de tensión de entrada (a) y salida (b) de la serie TTL estándar.

Ejemplo: Niveles de tensión de entrada (a) y salida (b) de la serie CMOS 74HC.

Encarnación Marín Caballero Página 5 de 23

Tema 5: Familias Lógicas.

2.3. Inmunidad al ruido

El ruido se produce cuando aparecen variaciones indeseables en la tensión que manejan las

puertas lógicas. Este ruido puede ser producido por fluctuaciones bruscas en la tensión de la red

eléctrica, interferencias ocasionadas por campos electromagnéticos que se inducen en los conductores

de alimentación, etc.

La inmunidad al ruido de un circuito lógico nos indica su capacidad para tolerar ruido

(fluctuaciones de tensión no deseadas) sin que se vean afectados los valores lógicos de salida.

Por tanto, el margen de ruido en voltios (VN) que tolera un circuito lógico se puede calcular de

la siguiente forma:

VNH: margen de ruido para el nivel alto. VNH = VOH (mín) – VIH (mín)

VNL: margen de ruido para el nivel bajo. VNL = VIL (máx) – VOL (máx)

Ejemplo: Margen de ruido a nivel alto y bajo de la serie TTL estándar.

Ejemplo: Margen de ruido a nivel alto y bajo de la serie CMOS 74HC.

Observando el resultado de ambas familias, podemos deducir que la serie CMOS 74HC es más

inmune al ruido, ya que su margen es mayor.

Encarnación Marín Caballero Página 6 de 23

Tema 5: Familias Lógicas.

2.4. Disipación de potencia

Los circuitos lógicos consumen una cierta potencia cuando están en funcionamiento. Esta

potencia hace que los circuitos se calienten por efecto Joule, lo que provoca una elevación de su

temperatura, que podría dañar los dispositivos si no se diseñan adecuadamente .

Cada puerta se conecta a la tensión de alimentación V CC y consume cierta corriente mientras

funciona. Como cada puerta puede estar a nivel alto, en transición o a nivel bajo, podemos distinguir,

respectivamente, tres corrientes diferentes: ICCH, ICCT e ICCL.

En las hojas de características de los fabricantes de circuitos lógicos normalmente se indica la

disipación de potencia en mW por cada una de las puertas lógicas incluidas en el CI.

En antiguas familias lógicas como la TTL, la corriente de transición ICCT es despreciable en

comparación con las otras. Considerando que la puerta está aproximadamente el mismo tiempo a nivel

alto y a nivel bajo, la potencia media disipada vendrá dada por la siguiente expresión:

I CCH I CCL

Pm VCC

2

En nuevas familias lógicas como la CMOS , las corrientes ICCH e ICCL son despreciables en

comparación con la ICCT. Por tanto, la potencia media disipada es:

Pm VCC I CCT

Como la corriente ICCT es relativamente pequeña, la potencia disipada por las puertas CMOS es

también pequeña. Como es lógico, la potencia disipada aumenta con la frecuencia a la cual la salida de la

puerta cambia. Sin embargo, en los dispositivos TTL es independiente de la frecuencia.

La potencia disipada es importante por dos razones:

La primera, define la duración de la batería que las alimenta.

La segunda, la potencia disipada es proporcional al calor generado por el circuito integrado , y un

excesivo calentamiento puede provocar que la puerta genere valores de salida incorrectos.

Por ambas razones, se deben utilizar puertas que consuman lo menos posible.

Ejemplo: La familia TTL 74 posee una disipación de potencia por puerta de 10 mW y una

temperatura de funcionamiento de 0 ºC a +70 ºC.

Ejemplo: La familia CMOS 74HC posee una disipación de potencia mucho menor, del orden de

0,0025 mW. Trabajan en un rango de temperatura entre 40 ºC y +85 ºC.

2.5. Capacidad de carga (fan-out)

En el diseño de circuitos lógicos es muy habitual conectar varias entradas de otras puertas a la

misma salida de una puerta lógica. Dado que la corriente que puede suministrar la salida de una puerta

es limitada, si conectásemos más puertas de las indicadas por el fabricante, no se podría garantizar que

la tensión de salida de la misma sea suficiente para activar las puertas conectadas.

Si aumentamos el número de entradas que conectamos a la salida de una puerta lógica , el efecto

aumenta, llegando un momento en el que el nivel alto o el nivel bajo entra en la zona de incertidumbre y

aparece el correspondiente peligro de que los circuitos no lo interpreten correctamente.

Encarnación Marín Caballero Página 7 de 23

Tema 5: Familias Lógicas.

Así pues, el fan-out nos indica el número máximo de puertas que se pueden conectar a la salida

de otra puerta de la misma familia lógica, manteniendo el nivel de la salida. Es decir, la máxima carga

que una puerta puede soportar.

Al igual que el margen de ruido, hay fan-out a nivel alto y a nivel bajo.

I OH

FOH: fan-out a nivel alto. FO H

I IH

I OL

FOL: fan-out a nivel bajo. FO L

I IL

En la siguiente figura se pueden deducir fácilmente su cálculo.

Ejemplo: La familia TTL 74 posee un fan-out de 10 puertas para la salida de una puerta NOT.

Ejemplo: La familia CMOS 74HC posee un fan-out mucho mayor, del orden de 100 puertas.

2.6. Tiempo de propagación (tp)

Cuando aplicamos una señal de entrada a una puerta lógica y ésta cambia su estado lógico en la

salida transcurre un pequeño tiempo, que se conoce como tiempo de propagación. Este retardo limita el

funcionamiento de la puerta lógica cuando la señal de entrada cambia a gran velocidad , es decir, a

frecuencias de impulso elevadas. El tiempo de propagación se mide en nanosegundos (ns), o sea 10-9 s.

Por tanto, el tiempo de propagación es el tiempo que transcurre desde que se le aplica la señal

a la entrada de la puerta hasta que su salida cambia.

Ejemplo: Como se ve en el cronograma de la puerta NOT, hay un pequeño retardo de

propagación (transcurre un tiempo desde que se le aplica la señal a la entrada de la puerta hasta que su

salida cambia).

Encarnación Marín Caballero Página 8 de 23

Tema 5: Familias Lógicas.

Observando la anterior figura, podemos definir dos tiempos:

tpLH: tiempo que tarda la salida en pasar de nivel alto a nivel bajo.

tpHL: tiempo que tarda la salida en pasar de nivel bajo a nivel alto.

Así pues, el tiempo de propagación vendrá dado por la siguiente expresión:

t pLH t pHL

tp

2

Ejemplo: La familia TTL 74 posee un tiempo de propagación de 9 ns y una frecuencia máxima de

señal de 35 MHz (millones de impulsos por segundo).

Ejemplo: La familia CMOS 74HC posee un tiempo de propagación de 8 ns y una frecuencia

máxima de señal de 40 MHz.

Encarnación Marín Caballero Página 9 de 23

Tema 5: Familias Lógicas.

3. FAMILIAS LÓGICAS

Los circuitos integrados se dividen en familias lógicas.

Cada familia lógica particular está basada en un tipo particular de circuito.

Todos los elementos de una familia lógica son compatibles entre sí, es decir, operan con los

mismos niveles lógicos, pudiendo la salida de un elemento alimentar la entrada de otro.

Existen, principalmente, dos tipos familias lógicas:

Familias lógicas basadas en silicio, que es la dominante en la actualidad.

Familias lógicas basadas en arseniuro de galio (GaAs), para aplicaciones de muy alta velocidad.

En la siguiente figura se muestra una clasificación de circuitos integrados basados en silicio

según la tecnología de fabricación. Dentro de los circuitos integrados basados en este material

semiconductor se definieron dos categorías: la tecnología bipolar y la unipolar.

Los dispositivos de tecnología bipolar se caracterizan porque presentan unas altas velocidades

de operación gracias a los transistores de unión (BJTs), pero también son elevados los consumos de

potencia. Pertenecen a esta categoría las familias lógicas TTL y ECL (lógica de emisores acoplados).

Por lo que respecta a los dispositivos unipolares, los más importantes son los que se basan en los

dispositivos de efecto campo MOS. Dentro de esta tecnología se incluyen la MOS de canal n (nMOS),

la MOS de canal P (pMOS, que ha quedado obsoleta) y la tecnología MOS de simetría

complementaria (CMOS), en la que se integran los dos tipos de canales. La más empleada es la

tecnología CMOS por consumo de potencia y velocidad de operación.

Entre ambos tipos de tecnologías, unipolares y bipolares, se encuentra otra reciente

denominada BiCMOS, que permite disponer en un mismo circuito integrado dispositivos bipolares (para

las entradas y las salidas) y estructuras CMOS. El coste es superior al de la tecnología CMOS, pero

proporciona mejores corrientes de salida y mayor velocidad .

Encarnación Marín Caballero Página 10 de 23

Tema 5: Familias Lógicas.

El significado de las siglas de las familias lógicas es:

En la siguiente tabla se muestra un cuadro resumen de las familias lógicas más importantes.

Encarnación Marín Caballero Página 11 de 23

Tema 5: Familias Lógicas.

3.1. Familia lógica TTL

Encarnación Marín Caballero Página 12 de 23

Tema 5: Familias Lógicas.

3.2. Familia lógica CMOS

A continuación, se presentan algunas de las características más relevantes de las dos

subfamilias lógicas más utilizadas de CMOS.

Serie 74HC:

HC: High Speed CMOS (CMOS de alta velocidad).

No es compatible eléctricamente con la familia TTL, pero mejora el tiempo de propagación,

ofreciendo valores del orden de 18 ns. Se alimenta con tensiones comprendidas entre 2 y 6 V.

Serie 74HCT:

HCT: High Speed CMOS-TTL (CMOS a nivel TTL).

Tiene una serie de características similar a la anterior, con la ventaja de ser compatible

eléctricamente con la familia TTL. Su tensión de alimentación es de 5 V.

Encarnación Marín Caballero Página 13 de 23

Tema 5: Familias Lógicas.

3.3. Comparativa entre las familias lógicas TTL y CMOS

A la hora de seleccionar una determinada familia lógica para un determinado diseño, habrá que

tener en cuenta las características que mejor se adapten al mismo, teniendo en cuenta que siempre

será mejor:

Una gran densidad de integración.

Un mayor rango de la tensión de alimentación.

Un mayor margen de ruido o inmunidad al ruido.

Un menor consumo o disipación de potencia.

Una mayor capacidad de carga o fan-out.

Un menor tiempo de propagación.

Compatibilidad con otras familias lógicas.

Menor coste económico.

En la siguiente tabla se muestra una comparativa entre las características principales de las

familias lógicas TTL 74 y CMOS 74HC.

Encarnación Marín Caballero Página 14 de 23

Tema 5: Familias Lógicas.

En la siguiente tabla podemos ver una comparativa entre TTL y CMOS con 5 V de alimentación.

En la siguiente figura, se muestran algunas de las características más relevantes de las

familias lógicas TTL (74S y 74LS) y CMOS 74HCT más utilizadas en el mercado.

3.4. Nomenclatura

Encarnación Marín Caballero Página 15 de 23

Tema 5: Familias Lógicas.

Los CI que empiezan por el prefijo 54 pertenecen a la familia lógica TTL militar y están

especificados para trabajar dentro del rango de temperaturas de –55 ºC a 125 ºC, mientras que los que

empiezan con 74 pertenecen a la familia lógica TTL estándar y están limitados al rango de 0 ºC a 70 ºC.

NOTA: La familia TTL es identificada con la serie 7400, y la familia CMOS con la serie 4000.

En algunas puertas lógicas, antes del prefijo 74 ó 54, es posible que aparezca el identificativo

del fabricante:

SN: Texas Instrument.

MN: Motorola.

DM: National.

N: Signetics.

P: Intel.

H: Harris.

AMD: Advanced Micro Devices.

Y también al final de la nomenclatura puede aparecer una letra indicando el tipo de encapsulado:

D: SMD.

J: DIL cerámico.

N: DIP.

En la siguiente tabla se muestra el significado de los dos últimos dígitos en el número de

serie de un CI digital. Esta denominación es común para las familias TTL y CMOS.

Encarnación Marín Caballero Página 16 de 23

Tema 5: Familias Lógicas.

Ejemplo: Estructura interna de la puerta lógica NAND (SN7400).

SN7400N

SN: fabricante (Texas)

74: familia lógica (TTL estándar)

00: puerta lógica (NAND)

N: encapsulado (DIP)

4. DATOS DE CATÁLOGO

El fabricante en sus catálogos (u hojas de características) nos ofrece una serie de datos que

hay que tener muy en cuenta a la hora de diseñar un circuito. Estos son:

VCC y VDD: tensión continua de alimentación del circuito. Todos los circuitos integrados TTL se

alimentan con +5 V (VCC), pero en la familia CMOS podemos variar la tensión de alimentación

entre 3 y 18 V (VDD).

V0H: tensión que entrega un circuito a la salida cuando está a nivel alto.

V0L: tensión que entrega un circuito a la salida cuando está a nivel bajo.

I0H: corriente que entrega un circuito a la salida cuando está a nivel alto.

I0L: corriente que absorbe un circuito por la salida cuando está a nivel bajo.

VIH: tensión de entrada a nivel alto.

VIL: tensión de entrada a nivel bajo.

IIH: corriente que absorbe el circuito a la entrada cuando hay un nivel alto.

IIL: corriente que entrega el circuito a la entrada cuando hay un nivel bajo.

I0S: corriente que se mide a la salida cuando está a nivel alto y cortocircuitamos la salida.

ICCH: corriente continua que entrega la fuente de alimentación cuando la puerta está a nivel

alto.

ICCL: corriente continua que absorbe la fuente de alimentación cuando la puerta está a nivel

bajo.

Encarnación Marín Caballero Página 17 de 23

Tema 5: Familias Lógicas.

Convenio de signo de las corrientes y tensiones:

Existe un convenio de signo para indicar si la corriente entra en la puerta o si sale, y es el

siguiente: las corrientes entrantes en la puerta se consideran positivas, mientras que las corrientes

salientes se consideran negativas.

Todas estas tensiones y corrientes se miden y circulan de la siguiente forma:

Ejemplo: Hoja de características de la puerta lógica NAND.

La hoja de características de la puerta lógica NAND se pueden ver en las direcciones web es:

www.DatasheetCatalog.com

www.alldatasheet.es

Encarnación Marín Caballero Página 18 de 23

Tema 5: Familias Lógicas.

5. PUERTAS LÓGICAS

Cada puerta lógica está asociada a un símbolo lógico, una tabla de verdad y una expresión

booleana; que expresa el estado de su salida para cada combinación posible de las entradas.

Encarnación Marín Caballero Página 19 de 23

Tema 5: Familias Lógicas.

Los CI de las puertas lógicas ya mencionadas tienen las siguientes configuraciones internas, las

cuales presentamos para su posterior conexión:

Encarnación Marín Caballero Página 20 de 23

Tema 5: Familias Lógicas.

6. CONEXIÓN DEL CI EN LA PROTOBOARD

Los CI de la familia lógica TTL requieren de una alimentación regulada de 5 VCC.

El positivo de dicha fuente se suele conectar a la patilla 14 del CI que aparece señalada como

VCC y el negativo a la patilla 7 denominada GND (tierra o masa).

Ejemplo: Conexión de la fuente de alimentación al CI de la serie 74LS00.

Un LED (diodo emisor de luz) suele colocarse a la salida para indicarnos el estado. Además, se

coloca en serie una resistencia de limitación para mantener la corriente por debajo de la corriente

máxima del LED.

Ejemplo: Cuando la salida de la puerta NAND sea un nivel bajo, el LED se encenderá.

Encarnación Marín Caballero Página 21 de 23

Tema 5: Familias Lógicas.

7. ESQUEMAS DE CI CON PUERTAS LÓGICAS

7.1. Puerta lógica NOT

La puerta lógica NOT es el CI 7404, que tiene 6 puertas lógicas inversoras, distribuidas en

doble línea.

Si tenemos una señal de entada baja (L), tenemos una señal de 5 V a su salida y el LED se

enciende.

Si tenemos una señal de entada alta (H), no tenemos señal a su salida y el LED no se

enciende.

Encarnación Marín Caballero Página 22 de 23

Tema 5: Familias Lógicas.

7.2. Puerta lógica AND

La puerta lógica AND es el CI 7408, que tiene 4 puertas lógicas AND, distribuidas en doble

línea.

Si tenemos una señal baja (L) en una de las dos entradas, no tenemos señal a su salida y el

LED no se enciende.

Si tenemos una señal alta (H) en las dos entradas, tenemos una señal de 5 V a su salida y el

LED se enciende.

Encarnación Marín Caballero Página 23 de 23

También podría gustarte

- Práctica 3. Función Doble NegaciónDocumento4 páginasPráctica 3. Función Doble NegaciónE&GAún no hay calificaciones

- Práctica 2. Puertas Lógicas de La Familia Lógica CMOSDocumento7 páginasPráctica 2. Puertas Lógicas de La Familia Lógica CMOSE&GAún no hay calificaciones

- Práctica 8. Diseño e Implementación de Un Motor Con Elementos MSIDocumento2 páginasPráctica 8. Diseño e Implementación de Un Motor Con Elementos MSIE&GAún no hay calificaciones

- Tema 1. Elementos de Maniobra o de ControlDocumento19 páginasTema 1. Elementos de Maniobra o de ControlE&GAún no hay calificaciones

- Tema 7. Circuitos DigitalesDocumento4 páginasTema 7. Circuitos DigitalesE&GAún no hay calificaciones

- Tema 4.1. RelaciónDocumento4 páginasTema 4.1. RelaciónE&G100% (1)

- Práctica 7. Diseño e Implementación de Una Prensa Con Elementos MSIDocumento2 páginasPráctica 7. Diseño e Implementación de Una Prensa Con Elementos MSIE&GAún no hay calificaciones

- Tema 4.2. RelaciónDocumento1 páginaTema 4.2. RelaciónE&GAún no hay calificaciones

- Práctica 15. Circuitos Aritméticos. ComparadoresDocumento4 páginasPráctica 15. Circuitos Aritméticos. ComparadoresE&GAún no hay calificaciones

- Práctica 9. Diseño e Implementación de Un Semáforo Con Elementos MSIDocumento3 páginasPráctica 9. Diseño e Implementación de Un Semáforo Con Elementos MSIE&GAún no hay calificaciones

- Tema 6.3. RelaciónDocumento2 páginasTema 6.3. RelaciónE&G100% (1)

- Práctica 20. Registros de Almacenamiento y DesplazamientoDocumento1 páginaPráctica 20. Registros de Almacenamiento y DesplazamientoE&GAún no hay calificaciones

- Práctica 18. Biestables AsíncronosDocumento1 páginaPráctica 18. Biestables AsíncronosE&GAún no hay calificaciones

- Práctica 5. Diseño e Implementación de Una Alarma Con MultiplexoresDocumento2 páginasPráctica 5. Diseño e Implementación de Una Alarma Con MultiplexoresE&GAún no hay calificaciones

- Práctica 26. Circuitos Intermitentes Con TransistoresDocumento2 páginasPráctica 26. Circuitos Intermitentes Con TransistoresE&GAún no hay calificaciones

- Práctica 16. Unidad Aritmético-Lógica (ALU)Documento2 páginasPráctica 16. Unidad Aritmético-Lógica (ALU)E&GAún no hay calificaciones

- Práctica 11. Sistema de Transmisión de Datos Mediante Un Multiplexor y Un DemultiplexorDocumento2 páginasPráctica 11. Sistema de Transmisión de Datos Mediante Un Multiplexor y Un DemultiplexorE&GAún no hay calificaciones

- Práctica 19. Biestables SíncronosDocumento3 páginasPráctica 19. Biestables SíncronosE&GAún no hay calificaciones

- Tema 9. RelaciónDocumento4 páginasTema 9. RelaciónE&GAún no hay calificaciones

- Tema 3.1. RelaciónDocumento1 páginaTema 3.1. RelaciónE&GAún no hay calificaciones

- Práctica 1. Generador de Números Binarios en MultiSimDocumento2 páginasPráctica 1. Generador de Números Binarios en MultiSimE&GAún no hay calificaciones

- Tema 3. Álgebra de BooleDocumento12 páginasTema 3. Álgebra de BooleE&GAún no hay calificaciones

- Práctica 12. Display de 7 SegmentosDocumento5 páginasPráctica 12. Display de 7 SegmentosE&GAún no hay calificaciones

- Práctica 21. Contadores Asíncronos y SíncronosDocumento5 páginasPráctica 21. Contadores Asíncronos y SíncronosE&GAún no hay calificaciones

- Tipos de ContadoresDocumento1 páginaTipos de ContadoresE&G100% (1)

- Práctica 14. Circuitos Aritméticos. Sumadores y RestadoresDocumento7 páginasPráctica 14. Circuitos Aritméticos. Sumadores y RestadoresE&G100% (1)

- Práctica 17. Convertidores DA y ADDocumento3 páginasPráctica 17. Convertidores DA y ADE&GAún no hay calificaciones

- Práctica 28. Localización de AveríasDocumento1 páginaPráctica 28. Localización de AveríasE&GAún no hay calificaciones

- Tema 0. Instrumentos de MedidaDocumento2 páginasTema 0. Instrumentos de MedidaE&GAún no hay calificaciones

- Práctica 13. Generadores y Detectores de ParidadDocumento3 páginasPráctica 13. Generadores y Detectores de ParidadE&G100% (1)

- Tipos de Circuitos SecuencialesDocumento2 páginasTipos de Circuitos SecuencialesE&GAún no hay calificaciones

- Práctica 22. Reloj DigitalDocumento1 páginaPráctica 22. Reloj DigitalE&GAún no hay calificaciones

- Practicas Taller Electrico Ricardo PardoDocumento18 páginasPracticas Taller Electrico Ricardo PardoRicardo Gabriel Pardo Cueva67% (3)

- Tema 2. RelaciónDocumento1 páginaTema 2. RelaciónE&GAún no hay calificaciones

- Práctica 4. Diseño e Implementación de Circuitos LógicosDocumento2 páginasPráctica 4. Diseño e Implementación de Circuitos LógicosE&GAún no hay calificaciones

- Práctica 3. Función Doble NegaciónDocumento4 páginasPráctica 3. Función Doble NegaciónE&GAún no hay calificaciones

- Práctica 6. Diseño e Implementación de Una Alarma Con DecodificadoresDocumento2 páginasPráctica 6. Diseño e Implementación de Una Alarma Con DecodificadoresE&GAún no hay calificaciones

- MM420 ProgramaciónDocumento12 páginasMM420 ProgramaciónBRAULIOAún no hay calificaciones

- Microcontroladores PDFDocumento32 páginasMicrocontroladores PDFAmilcar AngamarcaAún no hay calificaciones

- Práctica 7. Circuitos de Entretenimiento Con Biestables BásicosDocumento2 páginasPráctica 7. Circuitos de Entretenimiento Con Biestables BásicosE&GAún no hay calificaciones

- Proyecto Final Semaforos Inteligentes Con El Microcontrolador PIC 16F877ADocumento5 páginasProyecto Final Semaforos Inteligentes Con El Microcontrolador PIC 16F877AJohnAndersonEspaña0% (1)

- Práctica 4. Diseño e Implementación de Una Alarma Con Puertas LógicasDocumento3 páginasPráctica 4. Diseño e Implementación de Una Alarma Con Puertas LógicasE&GAún no hay calificaciones

- Puertas LogicasDocumento13 páginasPuertas LogicasturinatecnologiaAún no hay calificaciones

- Informe 1 DACDocumento9 páginasInforme 1 DACJose ArmandoAún no hay calificaciones

- Práctica #06 de Infraestructura de Redes y Sistemas de Telefonía - Introducción A Las Redes WIFIDocumento5 páginasPráctica #06 de Infraestructura de Redes y Sistemas de Telefonía - Introducción A Las Redes WIFIAntonio Herrerías SanabriaAún no hay calificaciones

- Práctica 6. Circuito TurnomaticDocumento1 páginaPráctica 6. Circuito TurnomaticE&GAún no hay calificaciones

- Práctica 1. Iniciación A La Soldadura BlandaDocumento1 páginaPráctica 1. Iniciación A La Soldadura BlandaE&GAún no hay calificaciones

- GUIA Practica PLC 2Documento9 páginasGUIA Practica PLC 2tatocinoAún no hay calificaciones

- Calculo Seccion Cables Secciones de Los Cables ConductoresDocumento41 páginasCalculo Seccion Cables Secciones de Los Cables ConductoresIsmael Pachas RoncerosAún no hay calificaciones

- EJERCICIO - Automatización Puerta Garaje PDFDocumento1 páginaEJERCICIO - Automatización Puerta Garaje PDFugui81Aún no hay calificaciones

- Practica 6 AutomatizacionDocumento8 páginasPractica 6 Automatizacionstefany toroAún no hay calificaciones

- Temario Curso Tía Portal SiemensDocumento1 páginaTemario Curso Tía Portal SiemensFlavin MedinaAún no hay calificaciones

- Contador multi-instancia PLC S7-1200Documento30 páginasContador multi-instancia PLC S7-1200Jorge VargasAún no hay calificaciones

- Práctica 12. Circuitos Eléctricos BásicosDocumento2 páginasPráctica 12. Circuitos Eléctricos BásicosE&GAún no hay calificaciones

- Grafcet AutomatizaciónDocumento16 páginasGrafcet AutomatizaciónGerson HernándezAún no hay calificaciones

- Caracteristicas de Conexion de CompuertasDocumento6 páginasCaracteristicas de Conexion de CompuertasArthur Thony LtgAún no hay calificaciones

- Guia Rapid A Cast 60Documento24 páginasGuia Rapid A Cast 60Pablito Alfa GtAún no hay calificaciones

- Taller PLCSDocumento43 páginasTaller PLCSJose Luis Sovero AstoamanAún no hay calificaciones

- Ejemplo #1 (Instalación Colectiva) TELEVESDocumento22 páginasEjemplo #1 (Instalación Colectiva) TELEVESFabricio PedrielAún no hay calificaciones

- Tema 2. Familias LógicasDocumento15 páginasTema 2. Familias LógicasE&GAún no hay calificaciones

- Relación Tema 7. Problemas de Funciones Lineales. SolucionesDocumento4 páginasRelación Tema 7. Problemas de Funciones Lineales. SolucionesE&GAún no hay calificaciones

- Relación Tema 7. Funciones. Propiedades Globales. GráficasDocumento7 páginasRelación Tema 7. Funciones. Propiedades Globales. GráficasE&GAún no hay calificaciones

- Relación Tema 1. Números Racionales. ProblemasDocumento5 páginasRelación Tema 1. Números Racionales. ProblemasE&GAún no hay calificaciones

- Relación Tema 7. FuncionesDocumento2 páginasRelación Tema 7. FuncionesE&GAún no hay calificaciones

- Configurar La Wi-Fi de Mi CasaDocumento6 páginasConfigurar La Wi-Fi de Mi CasaE&GAún no hay calificaciones

- Relacion Tema 6. Problemas de Sistemas de Ecuaciones Lineales. ResueltosDocumento12 páginasRelacion Tema 6. Problemas de Sistemas de Ecuaciones Lineales. ResueltosE&GAún no hay calificaciones

- Relación Tema 7. Funciones. Propiedades GlobalesDocumento4 páginasRelación Tema 7. Funciones. Propiedades GlobalesE&GAún no hay calificaciones

- Relación Tema 8. Problemas de Ecuaciones 1er Grado. ResueltosDocumento10 páginasRelación Tema 8. Problemas de Ecuaciones 1er Grado. ResueltosE&GAún no hay calificaciones

- Tema 6. Expresiones Algebraicas. Polinomios y Fracciones AlgebraicasDocumento55 páginasTema 6. Expresiones Algebraicas. Polinomios y Fracciones AlgebraicasE&GAún no hay calificaciones

- Tema 7. EcuacionesDocumento25 páginasTema 7. EcuacionesE&GAún no hay calificaciones

- Relacion Tema 7. Problemas de Porcentajes. ResueltosDocumento2 páginasRelacion Tema 7. Problemas de Porcentajes. ResueltosE&GAún no hay calificaciones

- Relación Tema 5. Problemas de Ecuaciones 1er Grado. ResueltosDocumento9 páginasRelación Tema 5. Problemas de Ecuaciones 1er Grado. ResueltosE&G100% (1)

- Relación Tema 5. Ecuaciones 2º Grado. SolucionesDocumento2 páginasRelación Tema 5. Ecuaciones 2º Grado. SolucionesE&GAún no hay calificaciones

- Relación Tema 4. Problemas de Ecuaciones 2º GradoDocumento1 páginaRelación Tema 4. Problemas de Ecuaciones 2º GradoE&GAún no hay calificaciones

- Relación Tema 7. Ecuaciones 2º Grado. SolucionesDocumento2 páginasRelación Tema 7. Ecuaciones 2º Grado. SolucionesE&GAún no hay calificaciones

- Relación Tema 6. Fracciones Algebraicas. SolucionesDocumento1 páginaRelación Tema 6. Fracciones Algebraicas. SolucionesE&GAún no hay calificaciones

- Relación Tema 7. Ecuaciones 1er Grado. Problemas. ResueltosDocumento3 páginasRelación Tema 7. Ecuaciones 1er Grado. Problemas. ResueltosE&GAún no hay calificaciones

- Relación Tema 6. Polinomios. SolucionesDocumento4 páginasRelación Tema 6. Polinomios. SolucionesE&GAún no hay calificaciones

- Relación Tema 7. Ecuaciones 1er Grado. Problemas. SolucionesDocumento3 páginasRelación Tema 7. Ecuaciones 1er Grado. Problemas. SolucionesE&GAún no hay calificaciones

- Relación Tema 7. Problemas de Ecuaciones 2º Grado. SolucionesDocumento2 páginasRelación Tema 7. Problemas de Ecuaciones 2º Grado. SolucionesE&GAún no hay calificaciones

- Relacion Tema 5. Problemas de Ecuaciones 1er Grado. SolucionesDocumento3 páginasRelacion Tema 5. Problemas de Ecuaciones 1er Grado. SolucionesE&GAún no hay calificaciones

- Relación Tema 5. Ecuaciones 1er Grado. SolucionesDocumento3 páginasRelación Tema 5. Ecuaciones 1er Grado. SolucionesE&GAún no hay calificaciones

- Cuerpos Geométricos en La Vida CotidianaDocumento5 páginasCuerpos Geométricos en La Vida CotidianaE&GAún no hay calificaciones

- Relación Tema 8. Monomios. SolucionesDocumento2 páginasRelación Tema 8. Monomios. SolucionesE&GAún no hay calificaciones

- Relación Tema 8. Ecuaciones 1er Grado. SolucionesDocumento3 páginasRelación Tema 8. Ecuaciones 1er Grado. SolucionesE&GAún no hay calificaciones

- Formulario Tema 7. FuncionesDocumento1 páginaFormulario Tema 7. FuncionesE&GAún no hay calificaciones

- Relación Tema 7. Problemas de Porcentajes. SolucionesDocumento2 páginasRelación Tema 7. Problemas de Porcentajes. SolucionesE&G100% (1)

- Relación Tema 8. Lenguaje Algebraico. SolucionesDocumento4 páginasRelación Tema 8. Lenguaje Algebraico. SolucionesE&GAún no hay calificaciones

- Relación Tema 7. Porcentajes. ResueltosDocumento2 páginasRelación Tema 7. Porcentajes. ResueltosE&GAún no hay calificaciones

- Relación Tema 4. Problemas de Porcentajes Encadenados. SolucionesDocumento1 páginaRelación Tema 4. Problemas de Porcentajes Encadenados. SolucionesE&GAún no hay calificaciones

- Circuitos Logicos PLDs MemoriasDocumento47 páginasCircuitos Logicos PLDs MemoriasAntonio Vasquez VasquezAún no hay calificaciones

- Familias Logicas. TTL Transistor-TransisDocumento4 páginasFamilias Logicas. TTL Transistor-TransisMiguel Calle RomeroAún no hay calificaciones

- TL866II Instructions - En.esDocumento54 páginasTL866II Instructions - En.esantony592Aún no hay calificaciones

- Ejemplos de MicrocontroladoresDocumento24 páginasEjemplos de MicrocontroladoresVicky HernàndezAún no hay calificaciones

- Evolución de las máquinas de cálculo desde el ábaco a la computadora modernaDocumento6 páginasEvolución de las máquinas de cálculo desde el ábaco a la computadora modernaYisus TapieAún no hay calificaciones

- Hello WorldDocumento25 páginasHello WorldDaniel MoralesAún no hay calificaciones

- Marco Teorico ProyectoDocumento14 páginasMarco Teorico ProyectoDiegoD DuranAún no hay calificaciones

- Bitácora de TrabajoDocumento3 páginasBitácora de Trabajoduvan garciaAún no hay calificaciones

- Cuadro Comparativo Sobre Las Diversas Etapas Del SoftwareDocumento5 páginasCuadro Comparativo Sobre Las Diversas Etapas Del SoftwareMontero Montero AriasAún no hay calificaciones

- Interruptor Del Tacto y Toque El Circuito de on-OfF - Taringa!11Documento4 páginasInterruptor Del Tacto y Toque El Circuito de on-OfF - Taringa!11Arianny Gomez MonteroAún no hay calificaciones

- Introducción de Informática Jurídica - UDHDocumento13 páginasIntroducción de Informática Jurídica - UDHRIVERA VIVAR ANEL MARJORIEAún no hay calificaciones

- Introduction To 3D Integration: 1.1 IntroducciónDocumento3 páginasIntroduction To 3D Integration: 1.1 IntroducciónAdrián PilataxiAún no hay calificaciones

- Apuntes Audio LG DTforumDocumento136 páginasApuntes Audio LG DTforumAntonio Jose Rodriguez Alvarado100% (2)

- Caso Teradyne Corporation El Proyecto JaguarDocumento25 páginasCaso Teradyne Corporation El Proyecto JaguarSergio FaiadAún no hay calificaciones

- Navegando hacia la sociedad del conocimientoDocumento48 páginasNavegando hacia la sociedad del conocimientoComprasyPermutas RochaLapalomaAún no hay calificaciones

- Diapositivas de La Tercera Generacion de ComputacionDocumento8 páginasDiapositivas de La Tercera Generacion de ComputacionAngel Santos100% (1)

- Letreros LuminososDocumento44 páginasLetreros Luminososjuan cardonaAún no hay calificaciones

- Capitulo 10Documento41 páginasCapitulo 10usuario33848576Aún no hay calificaciones

- l0585 Historias ForbesDocumento29 páginasl0585 Historias ForbesDaniel Fernando VargasAún no hay calificaciones

- Informe de CompusDocumento4 páginasInforme de CompusWilliam Santiago CH TenesacaAún no hay calificaciones

- Act. 8 Generaciones de ComputadorasDocumento3 páginasAct. 8 Generaciones de ComputadorasMarco AldanaAún no hay calificaciones

- Practica ProbabilidadDocumento6 páginasPractica ProbabilidadJobian GutierrezAún no hay calificaciones

- EJERCICIOS2 de La TóDocumento5 páginasEJERCICIOS2 de La Tóm_angeles_lopezAún no hay calificaciones

- CD 6180Documento148 páginasCD 6180Oscar Antonio Flores JuarezAún no hay calificaciones

- Generaciones de La ComputadoraDocumento16 páginasGeneraciones de La ComputadoraAndreina RosalesAún no hay calificaciones

- CI Digitales DocenteDocumento32 páginasCI Digitales DocenteJhonatan Vela HAún no hay calificaciones

- Cuestionario Historia de La Computación DAE205Documento2 páginasCuestionario Historia de La Computación DAE205irene floresAún no hay calificaciones

- History - of - Semiconductors TraducidoDocumento7 páginasHistory - of - Semiconductors TraducidoRuben Dario Mart�nez Casta�edaAún no hay calificaciones

- Cosmos La Fisica Del FuturoDocumento10 páginasCosmos La Fisica Del FuturoJoanne WellsAún no hay calificaciones

- Material de Hardware y SoftwareDocumento36 páginasMaterial de Hardware y SoftwareEUGENIA GALARZAAún no hay calificaciones