Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Circuito ALU 74LS181

Cargado por

Señor PopoDescripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Circuito ALU 74LS181

Cargado por

Señor PopoCopyright:

Formatos disponibles

ESCUELA PROFESIONAL DE INGENIERIA DE SISTEMAS

ARQUITECTURA DE COMPUTADORAS

UNIVERSIDAD PRIVADA DE TACNA

FACULTAD DE INGENIERIA

ESCUELA PROFESIONAL DE INGENIERIA DE SISTEMAS

CUARTO SEMESTRE

ASIGNATURA: ÁREA DE CONOCIMIENTO:

Arquitectura de computadoras (Laboratorio) Infraestructura de Redes

Docente: Ing. Alex Yanqui Constancio

Práctica 1 Circuito integrado ALU

Alumno:

Grupo de Laboratorio: Calificación:

OBJETIVO(S):

Reconocer el Circuito integrado de unidad Aritmética Lógica

Configurar ALU 74LS181 en el virtualizador

1. DESCRIPCION:

a. OBJETIVO

Complementar el estudio de los circuitos aritméticos.

Estudio, implementación y comprobación de las características operativas

de la unidad aritmética y lógica ALU 74LS181.

b. MATERIALES Y SOFTWARE DE SIMULACIÓN REQUERIDOS

Proteus Isis v.8.6 o superior

Simulador de circuitos digitales

Ing. Alex Yanqui Constancio

1

ESCUELA PROFESIONAL DE INGENIERIA DE SISTEMAS

ARQUITECTURA DE COMPUTADORAS

2. MARCO TEORICO:

2.1 INTRODUCCIÓN

La unidad aritmética lógica (UAL o ALU) es el órgano operativo del

microprocesador puede realizar operaciones tanto aritméticas como lógicas entre

un par de operandos de N bits, se compone en dos módulos: la unidad aritmética

y la unidad lógica. Para seleccionar la operación que se quiere realizar

normalmente estos dispositivos poseen unas entradas de selección.

En la arquitectura de un microprocesador, la unidad aritmética y lógica opera con

datos de N bits el cual posee dos vías para el acceso de datos:

Acceso directo desde el bus interno del microprocesador.

Acceso al acumulador con el cual trabaja habitualmente.

Además tiene una comunicación con los diferentes bits de registro de estados.

2.2 CIRCUITOS INTEGRADOS ARITMETICOS

Los circuitos aritméticos básicos, debido a su gran uso en multiples aplicaciones,

los encontramos en forma de IC (en una pastilla). El circuito sumador total típico

lo encontramos en forma de 4 sumadores completos independientes o como un

sumador de 4 bits capaz de sumar dos palabras binarias de 4 bits.

Si combinamos los circuitos sumadores totales con otros circuitos lógicos,

obtendremos:

• Sumadores-restadores

• Multiplicadores

• ALU (unidades lógicas-aritméticas de multiples utilidades)

Ing. Alex Yanqui Constancio

2

ESCUELA PROFESIONAL DE INGENIERIA DE SISTEMAS

ARQUITECTURA DE COMPUTADORAS

2.3 CARACTERISTICAS DEL 7483

Es un circuito integrado que realiza la función de sumador total, efectúa la suma

de dos números binarios de 4 bits.

2.4 SUMADOR DE DOS PALABRAS DE 4 BITS

Los 4 bits de la palabra A se introducen por sus correspondientes entradas;

análogamente, se introduce la palabra B por sus correspondientes entradas.

El Carry de entrada lo ponemos a masa ya que no tenemos ningún acarreo

anterior.

Por las salidas obtendremos el resultado de la suma en binario. Si el resultado

llevase acarreo en el último miembro, en el carry de salida saldria un 1 lógico.

Este es el uso más corriente que tiene este circuito integrado.

2.5 RESTADOR DE DOS PALABRAS DE 4Bits

Los cuatro inversores convierten la palabra B a su forma en complemento a 1.

Poner el acarreo de entrada a 1 lógico es lo mismo que si sumamos +1 al

sustraendo, con esto conseguimos el complemento a 2 del sustraendo; luego, se

suman minuendo y sustraendo y hemos efectuado la resta; en este caso, el

acarreo de salida se descarta.

2.6 SUMADOR-RESTADOR DE DOS PALABRAS DE 4Bits

Hemos observado que los circuitos sumadores son bastante parecidos. Si los

combinamos de una forma adecuada, obtendremos un circuito versátil que podrá

sumar o restar a nuestra voluntad.

2.7 LA UNIDAD ARITMÉTICA LÓGICA: ALU (ARITHMETIC LOGIC UNIT)

En esta sección de la CPU se realizan las operaciones aritméticas, lógicas, de

desplazamiento, de rotación de incremento. Uno de los operandos que

intervienen en la operación a efectuar por la ALU, procede de un registro llamado

Acumulador.

El otro operando llega desde cualquier parte del sistema y se carga en un registro

auxiliar. En el común de los microprocesadores, el resultado de la operación de la

ALU se deposita en el Acumulador, que, por este motivo, se emplea doblemente.

Ing. Alex Yanqui Constancio

3

ESCUELA PROFESIONAL DE INGENIERIA DE SISTEMAS

ARQUITECTURA DE COMPUTADORAS

Un registro especial, denominado Registro de Estado, dispone de una serie de

bits que actúan como señalizadores de alguna característica especiales que se

haya producido en la última operación efectuada por la ALU.

La ALU necesita recibir 4 señales que seleccionan la operación, más otra (M) que

determina si es de tipo lógico o aritmético. Las señales que seleccionan la

operación proceden del código OP de la instrucción que entra desde el bus

externo de datos e instrucciones.

2.8 RESUMEN DE LAS CARACTERÍSTICAS DE OPERACIÓN DEL C.I.

74LS181

Programando adecuadamente las líneas de selección (S3 S2 S1 S0) y la de

modo (M) junto con la de acarreo previo (Cn), la ALU puede ejecutar 16

operaciones lógicas y 32 operaciones aritméticas diferentes con los datos A=A3

A2 A1 A0 B=B3 B2 B1 B0. Estas operaciones, con sus respectivos códigos de

selección, se relacionan en la siguiente tabla. Se consideran tanto las entradas

como las salidas son activas en alto. Para programar el dispositivo como

generador de funciones lógicas, la entrada se lectora de modo (M) debe estar a

nivel alto. La operación lógica deseada se programa mediante un código de 4 bits

de la forma S3 S2 S1 S0 aplicado a las entradas selectoras de función. El estado

de Cn es indiferente.

Por ejemplo, para realizar la operación lógica A XOR B, si A= 1011 y B = 0001, la

línea M debe estar en 1 lógico y las líneas S3 S2 S1 S0 deben tener el código

0110.

Ing. Alex Yanqui Constancio

4

ESCUELA PROFESIONAL DE INGENIERIA DE SISTEMAS

ARQUITECTURA DE COMPUTADORAS

Cada bit de la palabra de salida F = F3F2F1F0 es el resultado de la operación

XOR de cada bit de la palabra A con el correspondiente bit de la palabra B. Es

decir, F3 =A3 XOR B3, F2 = A2 XOR B2 y así sucesivamente. Por tanto, F =

1010.

Para programar la ALU como generadora de funciones aritméticas, la línea M

debe llevarse a nivel bajo con el fin de habilitar los acarreos internos. La suma de

A y B, por ejemplo, se realiza cuando el código de las entradas de selección de

función es 1001. La entrada de acarreo Cn es activa en bajo.

Si la suma produce un acarreo de salida (Cn+4) igual a 1, esté también será

activo en bajo. La ALU utiliza un sistema interno de generación de acarreos

conocido como carry look ahead (acarreo anticipado), que no requiere que la

suma sea calculada en su totalidad antes de establecer la naturaleza del acarreo

resultante.

A continuación se presenta la tabla de operaciones de este integrado.

Operación de ALU 74LS181 en Lógica positiva

Datos activos con nivel alto

Selectores de

Funciones Operaciones Aritméticas: M = 0

función S3 S2 S1 Lógicas

S0 M=1 CN = 1 (sin acarreo) CN = 0 (con acarreo)

0000 F = A’ F=A F = A plus 1

0001 F = (A + B)’ F=A+B F = (A + B) plus 1

0010 F = A’.B F = A + B’ F = (A + B’) plus 1

o

0011 F=0 F = -1 (C 2) F=0

0100 F = (A.B)’ F = A plus A.B’ F = A plus A.B’ plus 1

0101 F = B’ F = (A + B) plus A.B’ F = (A + B) plus A.B’ plus 1

0110 F=AB F=A–B-1 F=A–B

0111 F = A.B’ F = A.B’ - 1 F = A.B’

1000 F = A’ + B F = A plus A.B F = A plus A.B plus 1

1001 F = (A B)’ F = A plus B F = A plus B plus 1

1010 F=B F = (A + B’) plus A.B F = (A + B’) plus A.B plus 1

1011 F = A.B F = A.B - 1 F = A.B

1100 F=1 F = A plus A F = A plus A plus 1

1101 F = A + B’ F = (A + B) plus A F = (A + B) plus A plus 1

1110 F=A+B F = (A + B’) plus A F = (A + B’) plus A plus 1

1111 F=A F=A-1 F=A

Ing. Alex Yanqui Constancio

5

ESCUELA PROFESIONAL DE INGENIERIA DE SISTEMAS

ARQUITECTURA DE COMPUTADORAS

La función de cada uno de los pines de este C.I. se describe a continuación:

A3:A2:A1:A0 Entradas del primer operando,

B3:B2:B1:B0 Entradas del segundo operando,

S3:S2:S1:S0 Selectores de función: mediante éstas se selecciona la función que ha de

realizar el circuito.

F3:F2:F1:F0 Salidas de la ALU, donde se tendrán los resultados.

M: Selector de Modo: sirve para determinar la operación a realizar, Si M=1

realiza operaciones lógicas y realiza operaciones aritméticas si M=0.

Cn: Entrada de acarreo activa en nivel bajo.

A=B: Es una salida de colector abierto e indica cuándo las cuatro salidas están a

nivel ALTO. Si se selecciona la operación aritmética de la resta, esta salida

se activará cuando ambos operandos son iguales.

G: Acarreo de generación. En operación aritmética de la suma, esta salida

indica que la salida F es mayor o igual a 16, y en la resta F es menor que

cero.

P: Acarreo de propagación. En la operación aritmética de la suma, esta salida

indica que F es mayor o igual a 15 y en la resta que F es menor que cero.

G y P se utilizan para acoplar varios circuitos integrados del tipo 74181 en

cascada empleando el método de propagación en paralelo.

Cn+4 Es el acarreo de salida.

3. MONTAJE

a) Semisumador y sumador completo

A

1 U2:A

1 S

B 3

2 ?

1

74LS386 C

?

U1:A

1

3

2

74LS08

A1

1 U3:A

1

B1 3

2

0 U2:B

74LS386 5 S1

C IN 4

6 ?

1

74LS386

U1:B

4 C OUT

6

5 ?

74LS08

Ing. Alex Yanqui Constancio

6

ESCUELA PROFESIONAL DE INGENIERIA DE SISTEMAS

ARQUITECTURA DE COMPUTADORAS

b) Sumador 7483

1

1 ?

U4

1 5

A0 S0

4

?

3 1

A1 S1 ?

14 13

0 12

A2

A3

S2

S3

10

?

6

B0

2

B1

15

0 11

B2

B3

7 9

0 C0 C4 ?

74283

0

1

c) RESTADOR CON 7483

0

?

0 U4

5 4 ?

0 3

A0 S0

1

14

A1 S1

13 ?

1 12

A2 S2

10

A3 S3 ?

6

B0

2

B1

15

B2

11

0 B3

7 9

0 C0 C4 ?

74283

1

0

d) SUMADOR BCD CON 7483

U6 U7

SW1 10 9 10 9

8

A1 S1

6 8

A1 S1

6 0

3

C 3

1

A2

A3

A4

S2

S3

S4

2

15

3

1

A2

A3

A4

S2

S3

S4

2

15 1

SW2 11 11 1

2

B1 B1

7 7

3

C 4

B2

B3 U4:A 4

B2

B3

0

16 74LS32 16

B4 B4

13 14 13 14

C0 C4 C0 C4 0

74LS83 74LS83

3

U5:A

1

3

2 U4:B

4

74LS08 6

5

74LS32

Ing. Alex Yanqui Constancio

7

ESCUELA PROFESIONAL DE INGENIERIA DE SISTEMAS

ARQUITECTURA DE COMPUTADORAS

e) SUMADOR BCD CON 7483

SW4 SW3

8

C 3

C VCC

U1 U2 U3

10 9 10 9 10 9

8

A1

A2

S1

S2

6 8

A1

A2

S1

S2

6 8

A1

A2

S1

S2

6 1

3 2 3 2 3 2

1

A3

A4

S3

S4

15 1

A3

A4

S3

S4

15 1

A3

A4

S3

S4

15 0

11

B1

11

B1

11

B1

0

7 7 7

4

B2

B3

4

B2

B3

4

B2

B3

0

16 16 16

B4 B4 B4

13 14 13 14 13 14

C0 C4 C0 C4 C0 C4 1

74LS83 74LS83 74LS83

f) SUMADOR/RESTADOR CON 7483

Dispositivos

8

C 10

U14

A1 S1

9 10

U16

A1 S1

9

8 6 8 6

A2 S2 A2 S2

3 2 3 2

A3 S3 A3 S3

1 15 1 15

3

C 11

A4

B1

S4

11

A4

B1

S4

7 U7:D 7

U15:A B2 B2

4 12 4

B3 B3

1 16 11 16

B4 B4

3 13

2 13 14 U8:C 13 14

C0 C4 C0 C4

74LS08 9

74LS86 74LS83 U17:A 8 74LS83

U4:B 1 10

4 3

6 2 74LS32

5

74LS08

74LS86

U8:D

U4:C 12

9 11 U17:B

8 13 4

10 6

74LS32 5

74LS86

U4:D 74LS08

12

11

13 U9:B

0-SUMA / 1-RESTA 74LS86 3 4

1 7404

Ing. Alex Yanqui Constancio

8

ESCUELA PROFESIONAL DE INGENIERIA DE SISTEMAS

ARQUITECTURA DE COMPUTADORAS

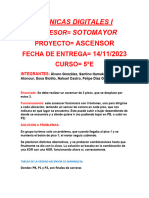

g) CONFIGURAR ALU 74181

Dispositivos usados

DSW1 U2

OFF ON

8 1 7 13

A QA

7 2 1 12

B QB

6 3 2 11

C QC

5 4 6 10

D QD

4 9

BI/RBO QE

DIPSW_4 5 15

RBI QF

3 14

LT QG

7447

DSW2 U3

OFF ON

8 1 7 13

A QA

7 2 1 12

B QB

6 3 2 11

C QC

5 4 6 10

D QD

4 9

BI/RBO QE

DIPSW_4 5 15

RBI QF

3 14

LT QG

7447

DSW4

OFF ON

4 1

3 2

DIPSW_2

U1 U4

2 9 7 13

A0 F0 A QA

23 10 1 12

A1 F1 B QB

21 11 2 11

A2 F2 C QC

19 13 6 10

A3 F3 D QD

4 9

BI/RBO QE

1 14 5 15

B0 A=B RBI QF

22 16 3 14

B1 CN+4 LT QG

20 17

B2 G

18 15 7447

B3 P

7

DSW3 CN

OFF ON

8 1 6

S0

7 2 5

S1

6 3 4

S2

5 4 3

S3

8

M

DIPSW_4

BAT1 74HC181 R

5V 220

Desarrolle La Tabla De Verdad Del Alu 74181

Ing. Alex Yanqui Constancio

9

ESCUELA PROFESIONAL DE INGENIERIA DE SISTEMAS

ARQUITECTURA DE COMPUTADORAS

4. CUESTIONARIO

1. Realice un circuito sumador / restador de 8 bits

2. Modifique el circuito del alu 74181 con Thumbswitch hex.

3. Realice un circuito con alu 74181 de 8 bits.

Ing. Alex Yanqui Constancio

1

0

También podría gustarte

- Exámen 3 Circuitos DigitalesDocumento2 páginasExámen 3 Circuitos DigitalesalfredocorAún no hay calificaciones

- Circuitos 1.8 A 1.24Documento8 páginasCircuitos 1.8 A 1.24Isabela VázquezAún no hay calificaciones

- Lab Nº3 - Corte y Saturación - 2011-IDocumento2 páginasLab Nº3 - Corte y Saturación - 2011-IBruno Adolfo Castillo SoteloAún no hay calificaciones

- Evaluación de Proyectos TelecomDocumento10 páginasEvaluación de Proyectos TelecomYony Mallkol Arnoldo Mamani KispeAún no hay calificaciones

- Tarea 3 - Fundamentos de Electronica DigitalDocumento17 páginasTarea 3 - Fundamentos de Electronica DigitalAndres CristanchoAún no hay calificaciones

- Contador Descendente de 0 A 99 Usando Display Cátodo Común.Documento3 páginasContador Descendente de 0 A 99 Usando Display Cátodo Común.carlosAún no hay calificaciones

- Informe Laboratorio4 NMartinezDocumento9 páginasInforme Laboratorio4 NMartinezNicky Martinez SalazarAún no hay calificaciones

- Ejercicio Diodo ExamenDocumento3 páginasEjercicio Diodo ExamenAlexander Merejildo TomaláAún no hay calificaciones

- ProyectosDocumento8 páginasProyectosSantiago ArciniegasAún no hay calificaciones

- Informe Deber Antena Dipolo LargoDocumento2 páginasInforme Deber Antena Dipolo LargoJorgeSandoval50% (2)

- Simular enrutamiento estático y dinámicoDocumento15 páginasSimular enrutamiento estático y dinámicoEddylsonAún no hay calificaciones

- Practica#1Documento13 páginasPractica#1Ismael ReyesAún no hay calificaciones

- Transistores NPN y PNPDocumento12 páginasTransistores NPN y PNPnahomisssAún no hay calificaciones

- Informe 1Documento17 páginasInforme 1Jhon Cerna F.Aún no hay calificaciones

- Practica 6Documento12 páginasPractica 6hector blancoAún no hay calificaciones

- 13 Tipos de Funciones MatemáticasDocumento47 páginas13 Tipos de Funciones MatemáticasJimmy Alexander Muñoz ForeroAún no hay calificaciones

- MEDICIÓN TEMPERATURA CON DSPICDocumento9 páginasMEDICIÓN TEMPERATURA CON DSPICJesus Rosas MontalvoAún no hay calificaciones

- Reporte de Práctica (Compuertas Lógicas)Documento5 páginasReporte de Práctica (Compuertas Lógicas)Riki MontenegroAún no hay calificaciones

- Simplificación de funciones booleanas y compuertas lógicasDocumento3 páginasSimplificación de funciones booleanas y compuertas lógicasAlex De la TorreAún no hay calificaciones

- Circuitos Multiplicadores de VoltajeDocumento4 páginasCircuitos Multiplicadores de VoltajeJorgeNitalesAún no hay calificaciones

- Comunicacion Matlab-ArduinoDocumento4 páginasComunicacion Matlab-ArduinoRichard ArturoAún no hay calificaciones

- Amplificadores DiferencialesDocumento6 páginasAmplificadores DiferencialesAngel PaulAún no hay calificaciones

- Implementación de videojuego con FPGA y ArduinoDocumento15 páginasImplementación de videojuego con FPGA y ArduinoSantiago González100% (1)

- 6 Circuitos Combinacionales P ImprimirDocumento36 páginas6 Circuitos Combinacionales P ImprimirFabian AcostaAún no hay calificaciones

- Labort Sistemas DigitalesDocumento25 páginasLabort Sistemas DigitalesJuan FieeAún no hay calificaciones

- Laboratorio 2 Electrónica IIIDocumento7 páginasLaboratorio 2 Electrónica IIIEliana MariaAún no hay calificaciones

- E3Documento3 páginasE3Linda Esmeralda Torres RiosAún no hay calificaciones

- Actividad 6. Decodificadores PDFDocumento12 páginasActividad 6. Decodificadores PDFAntonio SolanesAún no hay calificaciones

- Instrucciones Aritmeticas At89s52Documento8 páginasInstrucciones Aritmeticas At89s52ElBuenDany0% (1)

- Teoria Sistemas Digitales 2Documento69 páginasTeoria Sistemas Digitales 2Joaquin De La RosaAún no hay calificaciones

- Preg 2 ParedesDocumento5 páginasPreg 2 ParedesjuanAún no hay calificaciones

- Laboratorio n4 de Sumador Multiplexor y DemultiplexorDocumento11 páginasLaboratorio n4 de Sumador Multiplexor y DemultiplexorSantos Zosimo Ocas GoicocheaAún no hay calificaciones

- Guia de Laboratorio 5,6,7,8 Corte 2 Electrónica 2Documento6 páginasGuia de Laboratorio 5,6,7,8 Corte 2 Electrónica 2Bryan David Caceres DuarteAún no hay calificaciones

- Abecedario 8086Documento7 páginasAbecedario 8086Luis de JesusAún no hay calificaciones

- Unidad 1 - Familias Logicas de ICDocumento15 páginasUnidad 1 - Familias Logicas de ICCarlos OrtegaAún no hay calificaciones

- Sistemas Digitales CombinacionalesDocumento18 páginasSistemas Digitales CombinacionalesjesusAún no hay calificaciones

- Digitales FinalDocumento6 páginasDigitales FinalDaniela MartinezAún no hay calificaciones

- Inversor - 4013 - CopiarDocumento6 páginasInversor - 4013 - CopiarEdgardo Irusta100% (1)

- INFORME IEEE de Semaforo Vehicular y Peatonal Con PIC 16F877ADocumento3 páginasINFORME IEEE de Semaforo Vehicular y Peatonal Con PIC 16F877ASanti HernandezAún no hay calificaciones

- Informe Final Malca 1Documento5 páginasInforme Final Malca 1Edwin ToledoAún no hay calificaciones

- LAB1Documento3 páginasLAB1OscarAún no hay calificaciones

- Preparatorio Laboratorio de Sistemas Digitales Practica 11Documento8 páginasPreparatorio Laboratorio de Sistemas Digitales Practica 11Felipe AndinoAún no hay calificaciones

- Informe Previo FINALDocumento21 páginasInforme Previo FINALYury Rojas CarbajalAún no hay calificaciones

- Problemas Resuelto Decos y MuxDocumento5 páginasProblemas Resuelto Decos y MuxRuben Cruz Aique100% (1)

- Preparatorio Sistemas Digitales Practica 9Documento3 páginasPreparatorio Sistemas Digitales Practica 9Jorge ParraAún no hay calificaciones

- Laboratorio 3.5 PresiónDocumento4 páginasLaboratorio 3.5 PresiónERIK GABRIEL FALCON CAPILLAAún no hay calificaciones

- Codificadores, decodificadores y comparadores: principios básicosDocumento18 páginasCodificadores, decodificadores y comparadores: principios básicosAnthony MartinezAún no hay calificaciones

- Clase CMOS Y TTLDocumento66 páginasClase CMOS Y TTLerteduAún no hay calificaciones

- Informe 2 Repaso Teorema de MorganDocumento5 páginasInforme 2 Repaso Teorema de MorganGüerrëröYöylëAún no hay calificaciones

- Laboratorio 3 MicroelectronicaDocumento8 páginasLaboratorio 3 MicroelectronicaAlvaro SegoviaAún no hay calificaciones

- VHDL - Descripción Serie ComportamentalDocumento19 páginasVHDL - Descripción Serie ComportamentalErika Erikja100% (1)

- Instrucciones Basicas de QbasicDocumento8 páginasInstrucciones Basicas de QbasicJonathan BautistaAún no hay calificaciones

- Informe Previo N°01Documento5 páginasInforme Previo N°01Luis ValenzuelaAún no hay calificaciones

- Algebra de Boole y simplificación de funciones lógicas con Mapas de KarnaughDocumento64 páginasAlgebra de Boole y simplificación de funciones lógicas con Mapas de KarnaughmanuelAún no hay calificaciones

- Preinforme Usc Simple Parte2 Grupo l3 Etn801Documento7 páginasPreinforme Usc Simple Parte2 Grupo l3 Etn801Carlos B CaballeroAún no hay calificaciones

- Instrucción ADDLWDocumento2 páginasInstrucción ADDLWHector Calisaya HuarcayaAún no hay calificaciones

- Solucion Experiencia 01 - Teoria de Control Automatico 02Documento10 páginasSolucion Experiencia 01 - Teoria de Control Automatico 02JHOEL RENE MAMANI HUANCAAún no hay calificaciones

- Señales básicas, muestreo e interpolaciónDocumento4 páginasSeñales básicas, muestreo e interpolaciónLuis NunezAún no hay calificaciones

- Lab 06 Circuitos Digitales UNMSMDocumento10 páginasLab 06 Circuitos Digitales UNMSMDianaAún no hay calificaciones

- Informe1.1 17358 Condor Gomez Lluglla PerdomoDocumento15 páginasInforme1.1 17358 Condor Gomez Lluglla PerdomodjperdomoAún no hay calificaciones

- Laboratorio 11 - Transacciones en SQL Server - EnunciadosDocumento13 páginasLaboratorio 11 - Transacciones en SQL Server - EnunciadosSeñor PopoAún no hay calificaciones

- Heredia HISDocumento228 páginasHeredia HISSeñor PopoAún no hay calificaciones

- SISTEMAS - Jorge Luis Mendoza CarrilloDocumento106 páginasSISTEMAS - Jorge Luis Mendoza CarrilloSeñor PopoAún no hay calificaciones

- Lab 3.1 - Compuertas LogicasDocumento8 páginasLab 3.1 - Compuertas LogicasSeñor PopoAún no hay calificaciones

- Actividad de Modelamiento MatemáticoDocumento1 páginaActividad de Modelamiento MatemáticoSeñor PopoAún no hay calificaciones

- Implementación de diseño lógico de base de datos de presupuestosDocumento24 páginasImplementación de diseño lógico de base de datos de presupuestosSeñor PopoAún no hay calificaciones

- IO aplicada en problemas de suministro de piezasDocumento3 páginasIO aplicada en problemas de suministro de piezasSeñor PopoAún no hay calificaciones

- Hoja de Desarrollo Del Examen de UnidadDocumento1 páginaHoja de Desarrollo Del Examen de UnidadSeñor PopoAún no hay calificaciones

- CORRUPCIONDocumento16 páginasCORRUPCIONSeñor PopoAún no hay calificaciones

- ECOSISTEMASDocumento45 páginasECOSISTEMASgiuliannaAún no hay calificaciones

- Clase MP 08-06-21Documento16 páginasClase MP 08-06-21Señor PopoAún no hay calificaciones

- Clase MP 21-06-21Documento15 páginasClase MP 21-06-21Señor PopoAún no hay calificaciones

- Clase MP 28-06-21Documento89 páginasClase MP 28-06-21Señor PopoAún no hay calificaciones

- Examen de EntradaDocumento1 páginaExamen de EntradaSeñor PopoAún no hay calificaciones

- 3s Recursos NaturalesDocumento31 páginas3s Recursos NaturalesGian carlos Cairo gonzalezAún no hay calificaciones

- 4s ANP SPCDocumento37 páginas4s ANP SPCSeñor PopoAún no hay calificaciones

- 4s ANP SPCDocumento37 páginas4s ANP SPCSeñor PopoAún no hay calificaciones

- Lab 1.3 MemoriasDocumento8 páginasLab 1.3 MemoriasSeñor Popo100% (1)

- Ecosistemas desérticos y lomas costeras del PerúDocumento47 páginasEcosistemas desérticos y lomas costeras del PerúSeñor PopoAún no hay calificaciones

- 05 - Patrones de Arquitectura Más UtilizadosDocumento7 páginas05 - Patrones de Arquitectura Más UtilizadosSeñor PopoAún no hay calificaciones

- Introducción a la Arquitectura de SoftwareDocumento28 páginasIntroducción a la Arquitectura de SoftwareSeñor PopoAún no hay calificaciones

- 1s ECOLOGIADocumento53 páginas1s ECOLOGIASeñor PopoAún no hay calificaciones

- Cronograma - Arq - ADocumento3 páginasCronograma - Arq - ASeñor PopoAún no hay calificaciones

- 04 - Patrones de ArquitecturaDocumento26 páginas04 - Patrones de ArquitecturaSeñor PopoAún no hay calificaciones

- OPENGLDocumento9 páginasOPENGLSeñor PopoAún no hay calificaciones

- FD01-EPIS-Informe de Factibilidad de Proyecto-ForMATODocumento8 páginasFD01-EPIS-Informe de Factibilidad de Proyecto-ForMATOSeñor PopoAún no hay calificaciones

- Proyecto Primitivas de DespliegueDocumento12 páginasProyecto Primitivas de DespliegueSeñor PopoAún no hay calificaciones

- Prueba de Entrada Del Curso de Programación IDocumento1 páginaPrueba de Entrada Del Curso de Programación IJUAN CARLOS M LAún no hay calificaciones

- Eva Practica Uni 2 Introweb I 2020 - IDocumento7 páginasEva Practica Uni 2 Introweb I 2020 - ISeñor PopoAún no hay calificaciones

- Compuertas Lógicas: Operaciones AND, OR, NOT, NAND, NOR, XOR y sus Tablas de VerdadDocumento6 páginasCompuertas Lógicas: Operaciones AND, OR, NOT, NAND, NOR, XOR y sus Tablas de VerdadCristian Morales EspinozaAún no hay calificaciones

- Clase 74121 Y 122Documento21 páginasClase 74121 Y 122Carlos Luis CrespoAún no hay calificaciones

- S5 - VG - Electronica IIDocumento6 páginasS5 - VG - Electronica IIVictor Hugo Guzmán SilvaAún no hay calificaciones

- Informe 1 Sistemas DigitalesDocumento4 páginasInforme 1 Sistemas DigitalesDavid RozoAún no hay calificaciones

- Circuitos Combinacionales VHDLDocumento20 páginasCircuitos Combinacionales VHDLNick CohechaAún no hay calificaciones

- Circuitos digitales - Multiplexores, Demultiplexores, Sumadores y RestadoresDocumento5 páginasCircuitos digitales - Multiplexores, Demultiplexores, Sumadores y RestadoresDaniel Quesada Bejarano100% (1)

- HDL MsiDocumento11 páginasHDL Msijoflores13Aún no hay calificaciones

- Articulo Cientifico IndiceDocumento1 páginaArticulo Cientifico IndiceDiego JeanPierreAún no hay calificaciones

- CPLD FpgaDocumento24 páginasCPLD FpgaKerry Mayer Nolasco HuamánAún no hay calificaciones

- Venta de Circuitos Integrados Digitales - Electrosoft MéxicoDocumento20 páginasVenta de Circuitos Integrados Digitales - Electrosoft MéxicoFausto JoséAún no hay calificaciones

- Evaluacion Final - Escenario 8 - Primer Bloque-Teorico - Practico - Sistemas Digitales y Ensambladores - (Grupo1)Documento24 páginasEvaluacion Final - Escenario 8 - Primer Bloque-Teorico - Practico - Sistemas Digitales y Ensambladores - (Grupo1)Lizandro Carvajal RamosAún no hay calificaciones

- Entrega Laboratorio Compuertas LogicasDocumento8 páginasEntrega Laboratorio Compuertas LogicasJose Luis ZabaletaAún no hay calificaciones

- Puerta LógicaDocumento5 páginasPuerta LógicaMarcelo TorresAún no hay calificaciones

- PRACTICA 1 LaboratorioDigitalDocumento23 páginasPRACTICA 1 LaboratorioDigitalRonald Molina FariasAún no hay calificaciones

- Compuertas Lógicas y Tablas de Verdad PDFDocumento18 páginasCompuertas Lógicas y Tablas de Verdad PDFAndrea BullonAún no hay calificaciones

- Sumadores y Comparadores - Cuaderno de InformesDocumento13 páginasSumadores y Comparadores - Cuaderno de InformeszonneikoAún no hay calificaciones

- Prac2 Eq5 4av5Documento9 páginasPrac2 Eq5 4av5Alex CarmonaAún no hay calificaciones

- Descripción de Un Circuito Lógico Digital en VHDLDocumento32 páginasDescripción de Un Circuito Lógico Digital en VHDLlouisAún no hay calificaciones

- Puerta NOR: SímbolosDocumento5 páginasPuerta NOR: SímbolosCesar Idvorsky Gutiérrez CachiqueAún no hay calificaciones

- ALU en Lenguaje VHDLDocumento9 páginasALU en Lenguaje VHDLMartinez Ortiz Carlos DanielAún no hay calificaciones

- Ascensor G2Documento6 páginasAscensor G2David Elías PretelAún no hay calificaciones

- TALLER ELECTRÓNICA DIGITAL 2 SahagúnDocumento9 páginasTALLER ELECTRÓNICA DIGITAL 2 SahagúnErnesto GuevaraAún no hay calificaciones

- Compuertas lógicas y sus funcionesDocumento8 páginasCompuertas lógicas y sus funcionesworm9999Aún no hay calificaciones

- Unidad03 LogicaCombinacionalDocumento76 páginasUnidad03 LogicaCombinacionalmatias molinaAún no hay calificaciones

- 08-Compuertas LogicasDocumento7 páginas08-Compuertas LogicasadayadaiAún no hay calificaciones

- Problemas de circuitos digitalesDocumento14 páginasProblemas de circuitos digitalesJessica Karina Farinango UshiñaAún no hay calificaciones

- Tarea 3 Grupo 243004 1 PDFDocumento85 páginasTarea 3 Grupo 243004 1 PDFjonathanAún no hay calificaciones

- Practica3-2023, Con ExplicacionesDocumento16 páginasPractica3-2023, Con ExplicacionesValen IstvanAún no hay calificaciones

- Dispositivos Logicos ProgramablesFRA v3Documento24 páginasDispositivos Logicos ProgramablesFRA v3brandon gomezAún no hay calificaciones

- Taller 1 Compuertas LógicasDocumento8 páginasTaller 1 Compuertas LógicasMary Yamile Rodriguez CruzAún no hay calificaciones