Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Arquitectura de Computadora

Cargado por

Jose J Pérez López0 calificaciones0% encontró este documento útil (0 votos)

41 vistas7 páginasarquitectura de computadora

Título original

ARQUITECTURA DE COMPUTADORA

Derechos de autor

© © All Rights Reserved

Formatos disponibles

PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoarquitectura de computadora

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

41 vistas7 páginasArquitectura de Computadora

Cargado por

Jose J Pérez Lópezarquitectura de computadora

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Está en la página 1de 7

INSTITUTO TECNOLOGICO DE

NUEVO LEÓN

INGENIERIA EN SISTEMAS

COMPUTACIONALES

SEMESTRE 5°

ARQUITECTURA DE COMPUTADORAS

UNIDAD 1 TAREA 3

“ARQUITECTURA DE COMPUTADORA”

JOSE JAVIER PEREZ LOPEZ

18480559

ING. ROBERTO JOSEPH ARAGUZ GARCIA

GUADALUPE N.L, A 30 SEPTIEMBRE DE 2020

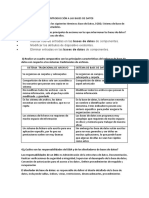

Arquitectura de Von Neumann.

Tradicionalmente los sistemas con microprocesadores se basan en esta

arquitectura, en la cual la unidad central de proceso (CPU), está conectada a

una memoria principal única (casi siempre sólo RAM) donde se guardan las

instrucciones del programa y los datos. A dicha memoria se accede a través de

un sistema de buses único (control, direcciones y datos).

En un sistema con arquitectura Von Neumann el tamaño de la unidad de datos

o instrucciones está fijado por el ancho del bus que comunica la memoria con la

CPU. Así un microprocesador de 8 bits con un bus de 8 bits tendrá que manejar

datos e instrucciones de una o más unidades de 8 bits (bytes) de longitud. Si

tiene que acceder a una instrucción o dato de más de un byte de longitud, tendrá

que realizar más de un acceso a la memoria. El tener un único bus hace que el

microprocesador sea más lento en su respuesta, ya que no puede buscar en

memoria una nueva instrucción mientras no finalicen las transferencias de datos

de la instrucción anterior.

Los ordenadores con arquitectura Von Neumann constan de las siguientes

partes:

Arquitectura Harvard.

Este modelo, que utilizan los Microcontroladores PIC, tiene la unidad central de

proceso (CPU) conectada a dos memorias (una con las instrucciones y otra con

los datos) por medio de dos buses diferentes.

Una de las memorias contiene solamente las instrucciones del programa

(Memoria de Programa), y la otra sólo almacena datos (Memoria de Datos).

Ambos buses son totalmente independientes lo que permite que la CPU pueda

acceder de forma independiente y simultánea a la memoria de datos y a la de

instrucciones. Como los buses son independientes estos pueden tener distintos

contenidos en la misma dirección y también distinta longitud. También la longitud

de los datos y las instrucciones puede ser distinta, lo que optimiza el uso de la

memoria en general.

Para un procesador de Set de Instrucciones Reducido, o RISC (Reduced

Instrucción Set Computer), el set de instrucciones y el bus de memoria de

programa pueden diseñarse de tal manera que todas las instrucciones tengan

una sola posición de memoria de programa de longitud. Además, al ser los buses

independientes, la CPU puede acceder a los datos para completar la ejecución

de una instrucción, y al mismo tiempo leer la siguiente instrucción a ejecutar.

Arquitectura Segmentada.

Las arquitecturas segmentadas o con segmentación del cauce buscan mejorar

el desempeño realizando paralelamente varias etapas del ciclo de instrucción al

mismo tiempo. El procesador se divide en varias unidades funcionales

independientes y se dividen entre ellas el procesamiento de las instrucciones.

Para comprender mejor esto, supongamos que un procesador simple tiene un

ciclo de instrucción sencillo consistente solamente en una etapa de búsqueda

del código de instrucción y en otra etapa de ejecución de la instrucción. En un

procesador sin segmentación del cauce, las dos etapas se realizarían de manera

secuencial para cada una de las instrucciones, como lo muestra la siguiente

figura.

Arquitectura de multiprocesamiento.

Cuando se desea incrementar el desempeño más allá de lo que permite la

técnica de segmentación del cauce (limite teórico de una instrucción por ciclo de

reloj), se requiere utilizar más de un procesador para la ejecución del programa

de aplicación.

Las CPU de multiprocesamiento se clasifican de la siguiente manera

(Clasificación de Flynn):

● SISO – (Single Instruction, Single Operand) computadoras Monoprocesador

● SIMO – (Single Instruction, Multiple Operand) procesadores vectoriales,

Exenciones MMX

● MISO – (Multiple Instruction, Single Operand) No implementado

● MIMO – (Multiple Instruction, Multiple Operand) sistemas SMP, Clusters,

GPUs

Procesadores vectoriales – Son computadoras pensadas para aplicar un mismo

algoritmo numérico a una serie de datos matriciales, en especial en la simulación

de sistemas físicos complejos, tales como simuladores para predecir el clima,

explosiones atómicas, reacciones químicas complejas, etc., donde los datos son

representados como grandes números de datos en forma matricial sobre los que

se deben se aplicar el mismo algoritmo numérico.

Arquitectura Vectorial.

El encadenamiento aumenta la velocidad de proceso, pero aún se puede mejorar

añadiendo técnicas como el supersescalado. Esta técnica permite hacer

paralelas las mismas etapas sobre instrucciones diferentes. Un procesador

superescalar puede ejecutar más de una instrucción a la vez. Para ésto es

necesario que existan varias unidades aritmeticológicas, de punto flotante y de

control. El proceso que sigue el micro es transparente al programa, aunque el

compilador puede ayudar analizando el código y generando un flujo de

instrucciones optimizado. Veamos cómo se ejecutarían las instrucciones en un

procesador superescalar de que tiene duplicadas las subunidades que lo

componen:

Arquitectura Pipe-Line.

La arquitectura pipe-line se aplica en dos lugares de la máquina, en la CPU y en

la UAL. Veamos en que consiste el pipe-line y tratemos de entender porque el

pipe-line mejora el rendimiento de todo el sistema. Veamos una CPU no

organizada en pipe-line:

Ya hemos mencionado que una de las formas de lograr operaciones

concurrentes en un procesador se utilizan dos técnicas básicas: paralelismo y

pipelining. El paralelismo conseguía la concurrencia multiplicando la estructura

del hardware tantas veces como sea posible, de modo que las diferentes etapas

del proceso se ejecuten simultáneamente. Pipelining consiste en desdoblar la

función a realizarse en varias partes, asignándole al hardware correspondiente

a cada una de las partes también llamadas etapas. Así como el agua fluye a

través de una tubería (pipeline) las instrucciones o datos fluyen a través de las

etapas de un computador digital pipeline a una velocidad que es independiente

de la longitud de la tubería (número de etapas del pipeline) y depende solamente

de la velocidad a la cual los datos e instrucciones pueden ingresar al pipeline.

BIBLIOGRAFIAS CONSULTAS.

Tarea 3 - Modelos de Arquitectura de Cómputo - Arquitectura de Computadoras.

(s. f.). sites.google.com. Recuperado 24 de septiembre de 2020, de

https://sites.google.com/site/arquitecturacomputadorasunahcu/tareas/tarea-3---

modelos-de-arquitectura-de-computo

Computadoras, A. (s. f.). 1.1 Modelos de arquitecturas de cómputo. Blogspot.

Recuperado 24 de septiembre de 2020, de http://itcv-arquitectura-de-

computadoras.blogspot.com/2014/11/1.html

Tipos de Arquitecturas. (2016, 9 agosto). Arquitectura de Computadoras.

https://is603arquicom2016.wordpress.com/tipos-de-arquitecturas/

Tarea 3 - Modelos de Arquitectura de Cómputo - Arquitectura de Computadoras.

(s. f.). sites.google.com. Recuperado 24 de septiembre de 2020, de

https://sites.google.com/site/arquitecturacomputadorasunahcu/tareas/tarea-3---

modelos-de-arquitectura-de-computo

También podría gustarte

- Tecnicas de Modulacion Digital2Documento13 páginasTecnicas de Modulacion Digital2Jose J Pérez LópezAún no hay calificaciones

- Técnicas de Modulación AnalógicaDocumento6 páginasTécnicas de Modulación AnalógicaJose J Pérez LópezAún no hay calificaciones

- Técnicas de Modulación DigitalDocumento5 páginasTécnicas de Modulación DigitalJose J Pérez LópezAún no hay calificaciones

- Tarea 1 U1Documento7 páginasTarea 1 U1Jose J Pérez LópezAún no hay calificaciones

- Conversion Analogico & DigitalDocumento11 páginasConversion Analogico & DigitalJose J Pérez LópezAún no hay calificaciones

- Conversion Analogico & Digital2Documento3 páginasConversion Analogico & Digital2Jose J Pérez LópezAún no hay calificaciones

- Componentes Internos PDFDocumento8 páginasComponentes Internos PDFJose J Pérez LópezAún no hay calificaciones

- Equipo de ComputoDocumento14 páginasEquipo de ComputoJose J Pérez LópezAún no hay calificaciones

- Protocolos & EstándaresDocumento10 páginasProtocolos & EstándaresJose J Pérez LópezAún no hay calificaciones

- Componentes Internos PDFDocumento8 páginasComponentes Internos PDFJose J Pérez LópezAún no hay calificaciones

- Organización y arquitectura de computadoras: modos de direccionamiento y ciclo de instrucciónDocumento14 páginasOrganización y arquitectura de computadoras: modos de direccionamiento y ciclo de instrucciónJose J Pérez LópezAún no hay calificaciones

- Medios Guiados 2Documento4 páginasMedios Guiados 2Jose J Pérez LópezAún no hay calificaciones

- Cable directo vs cruzadoDocumento4 páginasCable directo vs cruzadoJose J Pérez LópezAún no hay calificaciones

- ANALISISDocumento5 páginasANALISISJose J Pérez LópezAún no hay calificaciones

- Medios Guiados 1Documento5 páginasMedios Guiados 1Jose J Pérez LópezAún no hay calificaciones

- Producto: Que Consiste enDocumento2 páginasProducto: Que Consiste enJose J Pérez LópezAún no hay calificaciones

- Fundamentos de Telecomunicaciones: Emisor, Receptor y MediosDocumento7 páginasFundamentos de Telecomunicaciones: Emisor, Receptor y MediosJose J Pérez LópezAún no hay calificaciones

- Capacidad de Transmisión de Un Canal y Perturbaciones en La TransmisiónDocumento4 páginasCapacidad de Transmisión de Un Canal y Perturbaciones en La TransmisiónJose J Pérez LópezAún no hay calificaciones

- Cualquier ArchivoDocumento1 páginaCualquier ArchivoJose J Pérez LópezAún no hay calificaciones

- La Informatica Tarea 2.2 IronelyDocumento3 páginasLa Informatica Tarea 2.2 IronelyAmarante gonzalez rojasAún no hay calificaciones

- Área 3Documento7 páginasÁrea 3Julieth IguadAún no hay calificaciones

- 02-Manejo de Archivos Con InputStream y OutputStreamDocumento11 páginas02-Manejo de Archivos Con InputStream y OutputStreamjosepalacio497Aún no hay calificaciones

- Eva 5645036Documento17 páginasEva 5645036Melisa Consuelo Hidalgo CastilloAún no hay calificaciones

- AnálisisDocumento10 páginasAnálisiswarashirleyAún no hay calificaciones

- AP05 AA6 EV04 Elaboracion Clausulas Tecnicas ContratacionDocumento15 páginasAP05 AA6 EV04 Elaboracion Clausulas Tecnicas ContratacionMaria Vargas100% (2)

- Evaluación Diagnóstica Revisión Del IntentoDocumento29 páginasEvaluación Diagnóstica Revisión Del IntentoGEORGE RONDA100% (1)

- 11 Grado Tecnologia 2PDocumento10 páginas11 Grado Tecnologia 2PCharlis ZarzaAún no hay calificaciones

- Salvoconducto o Guías de Movilización Desde La App AUNAPDocumento15 páginasSalvoconducto o Guías de Movilización Desde La App AUNAProbinsonAún no hay calificaciones

- HP DesignJet T250Documento2 páginasHP DesignJet T250Manuel RabanalAún no hay calificaciones

- Sistemas Digitales y Periféricos Extra 2Documento7 páginasSistemas Digitales y Periféricos Extra 2Misael Ayala0% (1)

- Ev1.Utec - edu.Uy-Cuestionario de VC 2 Semana 5 Attempt ReviewDocumento4 páginasEv1.Utec - edu.Uy-Cuestionario de VC 2 Semana 5 Attempt ReviewguhAún no hay calificaciones

- Capítulo 3 - Variables en PowerShellDocumento3 páginasCapítulo 3 - Variables en PowerShelldirecthitAún no hay calificaciones

- Teleasistencia Help Line PDFDocumento4 páginasTeleasistencia Help Line PDFDanilo LarzoneiAún no hay calificaciones

- Las 5 Reglas de Oro Ante El Riesgo Eléctrico. TrabajoDocumento5 páginasLas 5 Reglas de Oro Ante El Riesgo Eléctrico. TrabajoZarra R.S.Aún no hay calificaciones

- Series IV Calculo IntegralDocumento15 páginasSeries IV Calculo IntegralLuis QuintanaAún no hay calificaciones

- Parte 3Documento16 páginasParte 3DominikAún no hay calificaciones

- Funciones Máximo y Mínimo en CDocumento20 páginasFunciones Máximo y Mínimo en CRogerOrihuelaAún no hay calificaciones

- Aportaciones Sobre Las TIC-Daniel CamposDocumento19 páginasAportaciones Sobre Las TIC-Daniel CamposDaniel CamposAún no hay calificaciones

- Análisis Sobre Módulos de Seguridad en ApacheDocumento6 páginasAnálisis Sobre Módulos de Seguridad en ApacheLizbeth Gianella Egusquiza VicenteAún no hay calificaciones

- in VitroDocumento8 páginasin VitroDaniel AriasAún no hay calificaciones

- OSHA 30 Capitulo 12Documento16 páginasOSHA 30 Capitulo 12grorbinAún no hay calificaciones

- Clase 1.conceptos - de - Bases - de - DatosDocumento47 páginasClase 1.conceptos - de - Bases - de - DatosKimberly LeandroAún no hay calificaciones

- EncuestaDocumento11 páginasEncuestaFOTOS GRADUADOSAún no hay calificaciones

- Profesional CreativoDocumento12 páginasProfesional CreativoAaron Mendoza SianquezAún no hay calificaciones

- Exposición TF CI1B Matematica Basica UpcDocumento7 páginasExposición TF CI1B Matematica Basica UpcLucas Muñoz100% (1)

- Sistema Bikefit Analisis BiomecanicoDocumento33 páginasSistema Bikefit Analisis BiomecanicoLeo Vasquez BlasAún no hay calificaciones

- Base de Datos - TP 3Documento3 páginasBase de Datos - TP 3ABIGAIL SAJAMAAún no hay calificaciones

- Estructruas de Papel 1Documento3 páginasEstructruas de Papel 1Jhon J Galan RAún no hay calificaciones

- Deber LagrangeDocumento2 páginasDeber LagrangeValerie CevallosAún no hay calificaciones