Documentos de Académico

Documentos de Profesional

Documentos de Cultura

LaboratorioDis1 PDF

Cargado por

IvanTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

LaboratorioDis1 PDF

Cargado por

IvanCopyright:

Formatos disponibles

1

Universidad Distrital Francisco José de Caldas. Facultad de Ingeniería

Sanabria

Informe de Laboratorio #1 – Cronometro

Ivan Sanabria 20172007037

I. OBJETIVOS Cuando llega a 1001 en lugar de pasar al siguiente estado

▪ Realizar la visualización de un cronometro con 4 1010, inicia un nuevo ciclo a partir de 0000.

display de 7 segmentos. La figura 1 nos muestra un contador de décadas BCD

▪ Comprender el funcionamiento de los diferentes síncrono, hecho con flip-flops tipo JK.

componentes utilizados, contadores,

decodificadores , Flip Flops entre otros.

▪ Analizar la elaboración de 2 pulsadores con el fin

de pausar o hacer continuar la cuenta del

cronometro y un segundo pulsador que sirva para la

toma de tiempo parcial.

▪ Aprender a manejar el Software PSoc Creator para

programar chip de la psoc, para un uso eficiente.

II. MATERIALES

Figura 1 Contador de 0-9 BCD

A. Psoc 5lp

B. Simulador Logicsim

III. MARCO TEÓRICO

Decodificador BCD a 7 segmentos

Este decodificador se aparta de la definición general ya

que cada combinación de valores de las entradas activa

varias salidas, en lugar de una sola. Tiene cuatro líneas de

entrada en código BCD y salidas capaces de excitar un

display de siete segmentos para representar cualquier dígito

de 0 a 9. Figura 2 Contador de 0-5 BCD

Multiplexor:

De la misma forma que hay dos tipos de decodificadores Un multiplexor es un dispositivo que permite dirigir la

existen dos tipos de display de 7 segmentos, unos cuyos información digital procedente de diversas fuentes a una

segmentos se activan con un 1, llamado display de 7 única línea para ser transmitida a través de dicha línea a un

segmentos de cátodo común, y otro cuyos segmentos se destino común.

activan con un cero, llamado display de 7 segmentos de

Disponemos de una serie de líneas de entrada, y una sola

ánodo común. Evidentemente, decodificador y display tienen línea de salida. La posición del conmutador, que es

que ser del mismo tipo para poder ser conectados. controlable, determinará la señal de entrada que aparezca en

la línea de salida. Un multiplexor consta de varias entradas y

Los displays de 7 segmentos son dispositivos que se una salida, y mediante un mecanismo de selección, una

utilizan para visualizar información. Cada segmento de un entrada se transfiere a la salida.

display está constituido por un LED que, al activarse, es

decir, cuando circula una corriente a través suyo, se ilumina.

El tipo de conexión de estos LED es lo que determina si el

display de 7 segmentos es de ánodo común o de cátodo

común.

Contador BCD

Un contador de décadas BCD, dispone de una secuencia Figura 3 Multiplexor de 2 a 1

binaria que no es completa. Va desde 0000 hasta 1001.

2

Universidad Distrital Francisco José de Caldas. Facultad de Ingeniería

Sanabria

IV. DESCRIPCIÓN FUNCIONAL

El circuito funciona con 4 display 7, los cuales están

conectados a 4 contadores 2 de 0-9 y 2 de 0-5, con el fin de VI. SIMULACIONES

tener una cuenta máxima de 59:59. Se anexa a la carpeta de archivos Psoc un video y un

archivo con la simulación.

Para la realización del primer pulsador se hizo un arreglo

de compuestas junto a un Flip-Flop Tipo D con el fin de VII. CONCLUSIONES

generar un “Switch” con el pulsador. El esquema se muestra ▪ Se comprueba que a partir de la práctica logramos

en la Figura 4, donde la salida de compuerta and es la entrada comprender el funcionamiento del decodificador y

de reloj del primer contador . contador aplicado a nivel de compuertas.

▪ Todo el diseño, aunque de complejidad moderada, se

logró realizarse sin problemas con la herramienta

escogidas a utilizar el software PSoC Creator donde se

evidenció que cualquier error en las especificaciones de

los pines digitales de entrada y salida podían evitar la

ejecución del proyecto.

Figura 4 Esquema Interruptor 1 ▪ Se corrorboro que el elemento adecuado para

seleccionar una funcion de varias es un Mux

Para el interruptor 2, con ayuda de un multiplexor de dos ▪ De la práctica logramos concluir que al reducir y

bits para cada salida de cada contador A3 A2 A1 A0 estas teniendo los conceptos claros del funcionamiento de un

son la entrada 1 de un mux, para la segunda entrada del mux decodificador y contador se puede realizar el diseño y

se realizo un arreglo con flip flips tipo D y compuertas, con ejecución de un cronometro con botones mediante la

el fin de poder almacenar el ultimo estado de cada señal A3 herramienta PSoC.

A2 A1 A0, el reloj de estos Flips Flops es la señal del REFERENCIAS

pulsador, adicional mente se realizo un esquema igual al ▪ [1] R. J. T. y. N. S. Widmer., Sistemas digitales.

Interruptor 1 para el selector del mux, esto se podrá visualizar Principios y aplicaciones, Prentice Hall

en la Figura 5. ▪ [2] D. D. Gajski (1997), Principios de diseño digital,

Madrid: Prentice Hall

▪ [3] M. M. Mano, Lógica digital y diseño de

computadoras, Prentic H

Figura 5 Esquema Interruptor 2

V. DESCRIPCIÓN ESTRUCTURAL

A continuación, se muestra en la Figura 5, el esquema

completo del cronometro.

Figura 5 Esquema Cronometro

3

Universidad Distrital Francisco José de Caldas. Facultad de Ingeniería

Sanabria

También podría gustarte

- Diseño e implementación de codificador decimal a BCD y multiplexor de 8 entradasDocumento3 páginasDiseño e implementación de codificador decimal a BCD y multiplexor de 8 entradasAndres CastellanosAún no hay calificaciones

- Laboratorio 5 Electronica III V2Documento8 páginasLaboratorio 5 Electronica III V2CRISTIAN CAMILO MORALES SOLISAún no hay calificaciones

- Programacion de Microcontroladores en Bascom AvrDocumento10 páginasProgramacion de Microcontroladores en Bascom AvrTany Rocker0% (1)

- Contador 0-9 en PLD con Quartus IIDocumento3 páginasContador 0-9 en PLD con Quartus IILuis MorenoAún no hay calificaciones

- Contador de 2 BitsDocumento7 páginasContador de 2 BitsOmar Del Valle VillaAún no hay calificaciones

- DecoDocumento7 páginasDecoJeimss MoraAún no hay calificaciones

- Electronica DigitalDocumento7 páginasElectronica DigitalGilson Daniel MaloAún no hay calificaciones

- Dado electrónico con PIC16F877A y display de 7 segmentosDocumento8 páginasDado electrónico con PIC16F877A y display de 7 segmentosPaul Romero Riera100% (1)

- Convertidor BCD códigoDocumento4 páginasConvertidor BCD códigoKaren LópezAún no hay calificaciones

- Diseño de circuito lógico para tablero electrónico de basquetbolDocumento5 páginasDiseño de circuito lógico para tablero electrónico de basquetbolAdrian CardenasAún no hay calificaciones

- Laboratorio #4Documento5 páginasLaboratorio #4A jugar yaAún no hay calificaciones

- Informe Laboratorio #5 SDDocumento10 páginasInforme Laboratorio #5 SDBenjo CalleAún no hay calificaciones

- Diseño DigitalDocumento7 páginasDiseño DigitalLUIS BARRERAAún no hay calificaciones

- Resumen Técnico Del Análisis de Resultados Diseño y Simulación de Un Contador Ascendente y Descendente de L 0 Al 9Documento12 páginasResumen Técnico Del Análisis de Resultados Diseño y Simulación de Un Contador Ascendente y Descendente de L 0 Al 9TAPUYO CHAPIRO DARWINAún no hay calificaciones

- Informe 6Documento2 páginasInforme 6Duo Doble AAún no hay calificaciones

- Informe AdcDocumento14 páginasInforme AdcJuaanGoo AlvarezAún no hay calificaciones

- Display de 7 SegmentosDocumento9 páginasDisplay de 7 SegmentosLuis PeñaAún no hay calificaciones

- LAB1Documento4 páginasLAB1Pedro Jesus Silva VillamilAún no hay calificaciones

- Informe 6-NicDocumento3 páginasInforme 6-NicJuliandavid QuinteromedinaAún no hay calificaciones

- Practica 4Documento15 páginasPractica 4stefany toroAún no hay calificaciones

- Informe-8 Marca ZambranoDocumento10 páginasInforme-8 Marca ZambranoPatricio OrdoñezAún no hay calificaciones

- Generador Lector de Señales Pantalla LCD en Lenguaje CDocumento5 páginasGenerador Lector de Señales Pantalla LCD en Lenguaje CCamilo NasAún no hay calificaciones

- Laboratorio IVDocumento7 páginasLaboratorio IVJuan Fernando Ceballos SilvaAún no hay calificaciones

- Infor de TTL 7404, 7408 y 7432Documento15 páginasInfor de TTL 7404, 7408 y 7432frandyAún no hay calificaciones

- 3 LCD AdcDocumento21 páginas3 LCD Adcjhonny espitiaAún no hay calificaciones

- Práctica 3_ Téllez_Aviles_AdairDocumento11 páginasPráctica 3_ Téllez_Aviles_AdairAdair TéllezAún no hay calificaciones

- Pines para Leds stm32F746Documento4 páginasPines para Leds stm32F746JUAN LAITON CABREJOAún no hay calificaciones

- Laboratorio 4 y 5Documento7 páginasLaboratorio 4 y 5Johan RMAún no hay calificaciones

- Display 7 Segmentos, LCD y Teclado Sistema de SeguridadDocumento12 páginasDisplay 7 Segmentos, LCD y Teclado Sistema de SeguridadMarco A RichterAún no hay calificaciones

- Reporte laboratorios contador 99-00Documento3 páginasReporte laboratorios contador 99-00Maríale PolancoAún no hay calificaciones

- Display 7 segmentos y programación en CDocumento9 páginasDisplay 7 segmentos y programación en CDaniel MateAún no hay calificaciones

- Diseño de circuito lógico de tablero electrónico de basquetbolDocumento5 páginasDiseño de circuito lógico de tablero electrónico de basquetbolAdrian CardenasAún no hay calificaciones

- Informe 1Documento9 páginasInforme 1Yih LibedAún no hay calificaciones

- Practica RelojDocumento7 páginasPractica RelojcjAún no hay calificaciones

- Laboratorio 2 DigitalDocumento9 páginasLaboratorio 2 DigitalCamila RojasAún no hay calificaciones

- Trabajo Colaborativo Final. Electronica DigitalDocumento13 páginasTrabajo Colaborativo Final. Electronica Digitalmguadalupe2Aún no hay calificaciones

- Universidad Tecnol Gica de El Salvador PDFDocumento20 páginasUniversidad Tecnol Gica de El Salvador PDFBrayan ValienteAún no hay calificaciones

- DecodificadoresDocumento9 páginasDecodificadoresEdwin Quispe ToaquizaAún no hay calificaciones

- P5-Ángel Clara-Guzmán Arenívar-Ochoa Arias-Valdebran CruzDocumento36 páginasP5-Ángel Clara-Guzmán Arenívar-Ochoa Arias-Valdebran CruzJuan CarlosAún no hay calificaciones

- Informe 2..1Documento10 páginasInforme 2..1RICHARD ALEXANDER PAUCAR FONSECAAún no hay calificaciones

- Informe ScadaDocumento3 páginasInforme ScadaLuis AssiaAún no hay calificaciones

- Sistema Minimo y Programacion BasicaDocumento9 páginasSistema Minimo y Programacion BasicaDaifred GutiérrezAún no hay calificaciones

- Informe Dado ElectronicoDocumento3 páginasInforme Dado ElectronicoPaul Romero RieraAún no hay calificaciones

- Informe 4Documento3 páginasInforme 4CristianCamiloAún no hay calificaciones

- Práctica 6 IMPARESDocumento3 páginasPráctica 6 IMPARESjorge quintero galindoAún no hay calificaciones

- Cerradura y Display Con ArduinoDocumento6 páginasCerradura y Display Con ArduinoEDUARDO HUERTA FLORESAún no hay calificaciones

- Practica 7Documento12 páginasPractica 7Sebastian MayorgaAún no hay calificaciones

- Cálculo básico con TTLDocumento8 páginasCálculo básico con TTLMarcelo Urquieta ClaureAún no hay calificaciones

- HB Codificador de Teclado MatricialDocumento2 páginasHB Codificador de Teclado MatricialHeribertoBretadoAún no hay calificaciones

- Implementación de un multiplicador de 2 bits en CDocumento6 páginasImplementación de un multiplicador de 2 bits en CDiego BonecchiAún no hay calificaciones

- Circuitos_CombinacionalesDocumento4 páginasCircuitos_CombinacionalesBeymar CondoriAún no hay calificaciones

- Cronometro Digital Con PsoCDocumento4 páginasCronometro Digital Con PsoCSEBASTIAN DAVID PINTOR AHUMADAAún no hay calificaciones

- Contador FotoeléctricoDocumento12 páginasContador FotoeléctricoAlexDanielAún no hay calificaciones

- CalculadoraDocumento6 páginasCalculadorajuanAún no hay calificaciones

- Laboratorio 3: Circuitos aritméticos y lógicosDocumento6 páginasLaboratorio 3: Circuitos aritméticos y lógicosEdgar ImanAún no hay calificaciones

- Reloj Digital con Circuitos IntegradosDocumento5 páginasReloj Digital con Circuitos IntegradosRonald ChiaraAún no hay calificaciones

- Práctica 7. Temporizador 1 Como TemporizadorDocumento14 páginasPráctica 7. Temporizador 1 Como TemporizadorVALERIA ZIMBRON NAVARROAún no hay calificaciones

- Practica-Contador de 0-7 VHDLDocumento13 páginasPractica-Contador de 0-7 VHDLR He MaAún no hay calificaciones

- Contador Modelo 10-24ABR23Documento5 páginasContador Modelo 10-24ABR23Nicolas PassiniAún no hay calificaciones

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- Laboratori Od Is 5Documento3 páginasLaboratori Od Is 5IvanAún no hay calificaciones

- Laboratori Od Is 4Documento3 páginasLaboratori Od Is 4IvanAún no hay calificaciones

- LaboratorioDis1 PDFDocumento3 páginasLaboratorioDis1 PDFIvanAún no hay calificaciones

- Laboratorio 5Documento5 páginasLaboratorio 5IvanAún no hay calificaciones

- Laboratorio SubirDocumento8 páginasLaboratorio SubirIvanAún no hay calificaciones

- Laboratorio SubirDocumento8 páginasLaboratorio SubirIvanAún no hay calificaciones

- Laboratorio SubirDocumento8 páginasLaboratorio SubirIvanAún no hay calificaciones

- Ejercicios de AlgoritmosDocumento9 páginasEjercicios de Algoritmoslucas100% (1)

- MPA-02-P-12 ADMON DE HISTORIAS LABORALES v2Documento4 páginasMPA-02-P-12 ADMON DE HISTORIAS LABORALES v2Roger YanezAún no hay calificaciones

- Modelo FurpsDocumento2 páginasModelo FurpsandrewsowenAún no hay calificaciones

- Presentacion ManualDocumento23 páginasPresentacion Manualastrith gonzalezAún no hay calificaciones

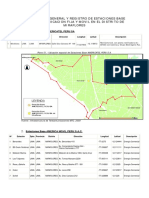

- Información General y Registro de Estaciones Base en MirafloresDocumento7 páginasInformación General y Registro de Estaciones Base en Mirafloreseljmago12Aún no hay calificaciones

- Refinería minimiza costos comprando petróleo crudoDocumento5 páginasRefinería minimiza costos comprando petróleo crudoJose Luis Condori PintoAún no hay calificaciones

- Definiciones de Funciones 1,2,3 (Hacer Formulario)Documento11 páginasDefiniciones de Funciones 1,2,3 (Hacer Formulario)Eduardo ChampinAún no hay calificaciones

- El Hombre DesechableDocumento1 páginaEl Hombre DesechableFreddy Castillo OsorioAún no hay calificaciones

- Canaima Educativo 2do GradoDocumento7 páginasCanaima Educativo 2do GradoAndrsn de JesusAún no hay calificaciones

- Simulación de procesos de venta en tienda Joshoa para optimizar tiempo de esperaDocumento60 páginasSimulación de procesos de venta en tienda Joshoa para optimizar tiempo de esperaKevin RonaldAún no hay calificaciones

- Montaje de cibercafés CONALEPDocumento35 páginasMontaje de cibercafés CONALEPadguerrerog1Aún no hay calificaciones

- MochillerDocumento7 páginasMochillerDavid Miguel Gutierrez ToroAún no hay calificaciones

- .... Quiñones Lorena OrdenDocumento1 página.... Quiñones Lorena OrdenEliana Vanessa BUESAQUILLO GALEANOAún no hay calificaciones

- Proteccion SistemicaDocumento18 páginasProteccion SistemicaRonny RojasAún no hay calificaciones

- Historia DotaDocumento16 páginasHistoria DotaLuis ACAún no hay calificaciones

- Trts0062spa 1007Documento302 páginasTrts0062spa 1007Omar Alberto Vicenteño Sanchez100% (2)

- Bitácora 2022.1Documento12 páginasBitácora 2022.1Isabella Calle ArroyaveAún no hay calificaciones

- Quinga Preparatorio4 GR4 2 SDDocumento6 páginasQuinga Preparatorio4 GR4 2 SDJesica QuingaAún no hay calificaciones

- Tutorial de Configuración de Fusibles para AVRDocumento6 páginasTutorial de Configuración de Fusibles para AVRIssac Andrade100% (1)

- WebQuest Sobre Formatos de Audio y VídeoDocumento6 páginasWebQuest Sobre Formatos de Audio y VídeoAlex Vega SuárezAún no hay calificaciones

- F2 Acta de Verificación de Requerimientos Técnicos y Funcionales de Acuerdo Al ISO 12207Documento2 páginasF2 Acta de Verificación de Requerimientos Técnicos y Funcionales de Acuerdo Al ISO 12207Rafael100% (5)

- DH-J2000-63-DH-J2000 Manual Español Con Ajuste PDFDocumento8 páginasDH-J2000-63-DH-J2000 Manual Español Con Ajuste PDFDavid CoronadoAún no hay calificaciones

- Blockbuster RESUMENDocumento3 páginasBlockbuster RESUMENpolly80s50% (2)

- Ipc LjeDocumento85 páginasIpc LjeEdiriosAún no hay calificaciones

- Tecnologia e Informatica Clei 5 Guia 1 Periodo 2Documento15 páginasTecnologia e Informatica Clei 5 Guia 1 Periodo 2yofa menaAún no hay calificaciones

- Catalogo Precios ETP III - Nacional 2023-06-09Documento83 páginasCatalogo Precios ETP III - Nacional 2023-06-09Hector RodriguezAún no hay calificaciones

- 3 Live CD - Usb.Documento8 páginas3 Live CD - Usb.pquirozg9565Aún no hay calificaciones

- Evidencia de Aprendizaje. Modelado de FuncionesDocumento6 páginasEvidencia de Aprendizaje. Modelado de FuncionesLuis Velazquez VazquezAún no hay calificaciones

- Administarcion MonetariaDocumento19 páginasAdministarcion MonetariaAriadna ArandiaAún no hay calificaciones

- Aplicación TIC enfermería áreas profesionalDocumento8 páginasAplicación TIC enfermería áreas profesionalBRAYAN DAVID CASTILLO PALACIOSAún no hay calificaciones