Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Informe 12

Informe 12

Cargado por

Diana0 calificaciones0% encontró este documento útil (0 votos)

4 vistas2 páginasTítulo original

Informe_12

Derechos de autor

© © All Rights Reserved

Formatos disponibles

PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

4 vistas2 páginasInforme 12

Informe 12

Cargado por

DianaCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Está en la página 1de 2

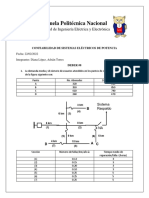

IMPLEMENTACION DE CIRCUITOS

ASINCRONICOS DE N BITS CON VHDL

Practica N°12 - Informe

Reinaldo David Carrera Valencia

Christian Andrés Beltrán Farinango

Diana López

CP – Sistemas Digitales _ GR5

Objetivos

• Familiarizar a estudiante con el diseño de circuitos contadores asincrónicos

• Creación de contadores usando flip-flops y compuertas lógicas

• Crear contadores tipo Ripple-clock mediante flip-flos y compuertas lógicas

1- Crear el código VHDL que permita emular el funcionamiento de flop-flop D 7474 y

presente su simulación (utilice la arquitectura VHDL que crea conveniente

2. utilizando flip-flops tipo J-K diseñar un contador asincrónico módulo 167 con control

ascendente – descendente y control de arranque y detención. Presente su diseño simulado en

paquete computacional LogicSim/Proteus.

Conclusiones

• La práctica nos ayuda a familiarizarnos con el diseño de circuitos contadores

asincrónicos su implementación en una tarjeta FPGA

• Se concluyó que para la creación de contadores asincrónicos puede usar flip-flpos y

compuertas lógicas las cuales se han programado en VHDL.

También podría gustarte

- Deber7 LópezDiana TorresAdriánDocumento5 páginasDeber7 LópezDiana TorresAdriánDianaAún no hay calificaciones

- Deber8 Lopez TorresDocumento11 páginasDeber8 Lopez TorresDianaAún no hay calificaciones

- Carta GarciaDocumento1 páginaCarta GarciaDianaAún no hay calificaciones

- IELR653 D10 CalculoflechaDocumento2 páginasIELR653 D10 CalculoflechaDianaAún no hay calificaciones

- CE Prepa10 PDFDocumento2 páginasCE Prepa10 PDFDianaAún no hay calificaciones

- Informe 9Documento3 páginasInforme 9DianaAún no hay calificaciones

- Simulación de Curvas Caracteristicas SCR, TRIAC, DiacDocumento3 páginasSimulación de Curvas Caracteristicas SCR, TRIAC, DiacDianaAún no hay calificaciones

- CE Prepa10 PDFDocumento2 páginasCE Prepa10 PDFDianaAún no hay calificaciones

- ME - Informe1 EPNDocumento5 páginasME - Informe1 EPNDianaAún no hay calificaciones

- Practica2 EPNDocumento4 páginasPractica2 EPNDianaAún no hay calificaciones