Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Fase 2

Cargado por

JUAN SEBASTIAN RUIZ SUAREZTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Fase 2

Cargado por

JUAN SEBASTIAN RUIZ SUAREZCopyright:

Formatos disponibles

Fase 2 - Presentar solución al problema del amplificador de baja señal con JFET

Suponga que trabaja para una compañía que diseña, prueba, fabrica y comercializa

instrumentos electrónicos. Su segunda asignación es presentar trabajando en equipo con

cuatro compañeros, una solución llamada amplificador de baja señal con JFET, el cual

permite restaurar señales débiles en los diferentes circuitos de transmisión y recepción

de información las especificaciones dadas para el diseño son las siguientes:

Señal de entrada: 300mV a 1Khz.

Referencia del JFET: J201

ID= 327uA, VD= 4.6V, VGS (off)= -1.5V, VCC= 20V.

De catálogo se tiene que: IDSS puede Variar de 1mA a 100mA… para este diseño se

trabajara IDSS=3mA.

El equipo de trabajo cuenta con 3 semanas para presentar un informe a la empresa, en él

mismo, es obligatorio se evidencie una fundamentación teórica, una argumentación y la

validación de la solución. Además, de ser aprobada la propuesta, se deberá realizar una

implementación real y para ello se contará con acceso a los laboratorios.

Actividades a desarrollar

Individuales:

1. Fundamentación Teórica.

(Primera Semana)

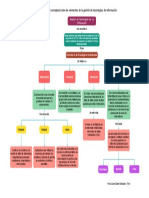

Figura No. 1. Diagrama Esquemático del Amplificador

Fuente Autor.

Primero definiremos cada elemento de nuestro circuito

Capacitor: también conocido como condensador utilizado en electrónica como

almacenador de energía y como filtro de la corriente para evitar el rizado dentro de un

circuito

Fuente Vcc: fuente de corriente continúa

Fuente AC: Fuente de corriente alterna

Resistencia: Es aquel dispositivo en electrónica el cual se opone al paso de corriente

eléctrica a través de el

Potenciómetro: Es una resistencia variable, su resistencia puede variar dependiendo el

valor que se le de

JFET: También denominado Transistor de Efecto de Campo. Su nombre proviene del

acrónimo inglés Junction Field Effect Transistor. La principal característica de este tipo

de transistores es que prácticamente no requieren de corriente de entrada en su terminal

de control. Permite el paso, o no, de corriente entre sus terminales Source (Fuente) y

Drain (Drenador) mediante la aplicación de voltaje en su terminal Gate (Puerta). Al no

necesitar corrientes de polarización, como ocurre con los transistores bipolares, se

puede reducir el número de componentes externos necesarios para hacerlo funcionar.

Consiguen velocidades de conmutación (tiempo de paso de conducción a no conducción

y viceversa) mayores que los transistores bipolares, por lo que se usan preferentemente

en Electrónica Digital.

Fuente: https://tallerelectronica.com/transistor-jfet/

Argumentación

Inicialmente tenemos un circuito alimentado con una fuente de corriente continua de

20V, esta fuente nos alimentara nuestro circuito, para poder tener un correcto

funcionamiento. Siguiendo con el análisis encontramos que tenemos una entrada de una

señal sinusoidal 300mV a 1Khz.luego pasa por un condensador de acopio el cual tiene

la función de estabilizar un poco más la señal que está pasando por él y eliminar señales

no deseadas, de allí la señal pasa por nuestro transistor JFET que luego de configurado

tiene como función amplificarnos la señal que está pasando por el luego más adelante en

el drenaje del JFET tenemos un condensador de 10uF con la misma sunción estabilizar

la señal obtenida del JFET y eliminarnos señales parasitas de la señal ya amplificada y

en la fuente tenemos una resistencia variable el cual nos servirá para variar el valor de la

tensión que pasa por el JFET y que entregaremos al último tramo en el cual

encontraremos la señal amplificada

(Segunda Semana).

Datos

Señal de entrada: 300mV a 1Khz.

Referencia del JFET: J201

ID= 327uA

VD= 4.6V

VGS (off)= -1.5V

VCC= 20V

De catálogo se tiene que: IDSS puede Variar de 1mA a 100mA… para este diseño se

trabajara IDSS=3mA.

Dadas Las Fórmulas:

RD = (VCC – VD) / ID VGS = - ID∙ RS AV = -Gm∙ RD

RS = VGS (off) / IDSS RG = Entre 1 y 2 MΩ Gm = ID / VGS

1.1 Argumentar matemáticamente el diseño presentado realizando los siguientes

cálculos.

-Estudiante 2:

b.) Calcular la resistencia del drenaje RS.

RS = VGS (off) / IDSS

−1.5V

𝑅𝑠 = = −0.5𝑘Ω

3mA

También podría gustarte

- Fundamentos de MetasploitDocumento38 páginasFundamentos de MetasploitOscar TardencillaAún no hay calificaciones

- Paso 5 Presentacion de ResultadosDocumento16 páginasPaso 5 Presentacion de ResultadosFener Marin Lopez Daza83% (12)

- PIA DE MICROECONOMIA eDocumento24 páginasPIA DE MICROECONOMIA ePedro JuarezAún no hay calificaciones

- 2incursionoenlaculturadigital 434206 299Documento7 páginas2incursionoenlaculturadigital 434206 299JUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Aporte Individual LogicaDocumento13 páginasAporte Individual LogicaJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Evaluacion FinalDocumento19 páginasEvaluacion FinalJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Comunidades Virtuales de Aprendizaje en RedDocumento2 páginasComunidades Virtuales de Aprendizaje en RedJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- AporteDocumento14 páginasAporteJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Aporte ColaborativoDocumento4 páginasAporte ColaborativoAndres Rivera HigueraAún no hay calificaciones

- Punto #4Documento3 páginasPunto #4JUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Fase 9 201424 16Documento26 páginasFase 9 201424 16JUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- RTADocumento5 páginasRTAJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Estrategias de AprendizajeDocumento1 páginaEstrategias de AprendizajeJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Ejercicio 2Documento3 páginasEjercicio 2JUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Paso 4 Joseluis CastroDocumento7 páginasPaso 4 Joseluis CastroJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Actividad 2Documento5 páginasActividad 2JUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- AnsesDocumento9 páginasAnsesJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- MediaDocumento6 páginasMediaJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Actividad 2Documento3 páginasActividad 2JUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- SimulacionDocumento2 páginasSimulacionJUAN SEBASTIAN RUIZ SUAREZ100% (1)

- Introducción a conceptos básicos de enrutamiento y direccionamientoDocumento6 páginasIntroducción a conceptos básicos de enrutamiento y direccionamientoJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Formulas A UtilizarDocumento3 páginasFormulas A UtilizarJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- IDocumento3 páginasIJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Req 1Documento3 páginasReq 1JUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- RRRRDocumento1 páginaRRRRJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Tarea 1 64Documento27 páginasTarea 1 64JUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- ResistenciaDocumento6 páginasResistenciaJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Fuente AcDocumento4 páginasFuente AcJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Ejercicio 1Documento2 páginasEjercicio 1JUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- ObjetivosDocumento8 páginasObjetivosJUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Trabajo Fase 2Documento11 páginasTrabajo Fase 2JUAN SEBASTIAN RUIZ SUAREZAún no hay calificaciones

- Aporte DDocumento6 páginasAporte DAndres ManosalvaAún no hay calificaciones

- Examen de Segunda Unidad 2022.1Documento7 páginasExamen de Segunda Unidad 2022.1MANUEL ESPINOZAAún no hay calificaciones

- Mantención Básica de MotosierraDocumento4 páginasMantención Básica de MotosierraEliycheque PanirariAún no hay calificaciones

- Tarea9 LogisticaDocumento7 páginasTarea9 LogisticaElisa Muñoz ZaldivarAún no hay calificaciones

- Sistema de rastreo de pedidos mejora servicio Domino'sDocumento7 páginasSistema de rastreo de pedidos mejora servicio Domino'sJos Antonio Rojas AguirreAún no hay calificaciones

- PETROLEOS MEXICANOS NORMAS PARA PROYECTO DE OBRAS CONSTRUCCION DE CANALIZACIONES ELECTRICAS SUBTERRANEASDocumento96 páginasPETROLEOS MEXICANOS NORMAS PARA PROYECTO DE OBRAS CONSTRUCCION DE CANALIZACIONES ELECTRICAS SUBTERRANEASServando PerezAún no hay calificaciones

- Laboratorio 7Documento18 páginasLaboratorio 7Jean PaúlAún no hay calificaciones

- Georreferenciacion Viviendas AisladasDocumento17 páginasGeorreferenciacion Viviendas AisladasFISICORAN ING.CIVILAún no hay calificaciones

- BT AGCO ManualDocumento12 páginasBT AGCO ManualEvert Vargas TorrezAún no hay calificaciones

- MECAF: Un Nuevo Paradigma para La Formalización de La Administración EmpresarialDocumento3 páginasMECAF: Un Nuevo Paradigma para La Formalización de La Administración EmpresarialGrupo Calipso SAAún no hay calificaciones

- IndicadoresLogroUDTopografiaDocumento2 páginasIndicadoresLogroUDTopografiaCAROL GABRIELA CUSIHUALLPA LOPEZAún no hay calificaciones

- Continuidad y Cambio Año 2 No 26 Noviembre (Primera Quincena) 2013Documento42 páginasContinuidad y Cambio Año 2 No 26 Noviembre (Primera Quincena) 2013lcsilvassAún no hay calificaciones

- Plan estratégico Sodimac PerúDocumento14 páginasPlan estratégico Sodimac PerúJose Miguel HerreraAún no hay calificaciones

- Mapa Conceptual de GTIDocumento1 páginaMapa Conceptual de GTIDaniel Eduardo Pech CanulAún no hay calificaciones

- Soluciones Tec para Generar Valor EIAODocumento38 páginasSoluciones Tec para Generar Valor EIAOAdalberto NavarroAún no hay calificaciones

- Regla Mason diagrama complejo FTDocumento3 páginasRegla Mason diagrama complejo FTAntonela CapittiniAún no hay calificaciones

- Estilos de Liderazgo y Compromiso OrganizacionalDocumento75 páginasEstilos de Liderazgo y Compromiso OrganizacionalIPROIDEASAún no hay calificaciones

- Inv 6 ResumenDocumento5 páginasInv 6 ResumenJuliana GrilloAún no hay calificaciones

- Plataformas de Trabajo ChimeneasDocumento15 páginasPlataformas de Trabajo ChimeneasPoint GarciaAún no hay calificaciones

- 2017 Manual OfflineDocumento15 páginas2017 Manual OfflinePedro SaitAún no hay calificaciones

- Ramirez y Paiva Desarrollo de Talento HumanoDocumento17 páginasRamirez y Paiva Desarrollo de Talento HumanoeapinedoAún no hay calificaciones

- Normas de DiseñoDocumento1 páginaNormas de DiseñoDaniel PulgarAún no hay calificaciones

- Ascensores en UruguayDocumento15 páginasAscensores en UruguayDebora SotoAún no hay calificaciones

- Gestion de La InnovacionDocumento56 páginasGestion de La InnovacionpaoloalejandroAún no hay calificaciones

- Monitoreo de Los Empleados en Las RedesDocumento3 páginasMonitoreo de Los Empleados en Las RedesAlejandro Francisco EstrellaAún no hay calificaciones

- ComunicaciónDocumento5 páginasComunicaciónYainer FlorezAún no hay calificaciones

- Comparacion y Caracteristicas Windows Vs LinuxDocumento7 páginasComparacion y Caracteristicas Windows Vs Linuxsatdae0% (1)

- Acuerdo Metropolitano No. 008 de 2000Documento48 páginasAcuerdo Metropolitano No. 008 de 2000Jhon CardozoAún no hay calificaciones

- 7 Aea3647 c1 ApunteacademicoDocumento7 páginas7 Aea3647 c1 Apunteacademicomarco seguelAún no hay calificaciones