Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Laboratorio

Cargado por

CarlosVillavicencioGDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Laboratorio

Cargado por

CarlosVillavicencioGCopyright:

Formatos disponibles

DISEÑO DIGITAL – Labroratorio No 5 UNMSM-FIE

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

FACULTAD DE INGENIERIA ELECTRONICA

ESCUELA DE ELECTRONICA

LABORATORIO No5: “Estilo Estructural”

ESTILO ESTRUCTURAL

El estilo estructural nos permite realizar un diseño digital utilizando

componentes anteriormente elaborados (ya compilados y almacenados en

la biblioteca work) ó componentes desarrollados por los fabricantes de los

FPGAs ó CPLDs que se encuentran en una biblioteca. El diseño se realiza

como si se tratará de una lista de conexiones entre las entradas y salidas de

los diversos componentes.

Para utilizar un componente hay que declararlo previamente. La sintaxis es

la siguiente:

component nombre [is]

[generic (lista de genericos);]

[port (lista de puertos);]

end component [nombre];

La referencia a un componente es una sentencia concurrente que se ejecuta

en paralelo con las demás sentencias concurrentes cada vez que se

produzca un evento en algunas señales conectadas a sus puertos de

entrada.

La sintaxis de referencia a un componente (instanciación) es:

etiq_ref: nombre_componente {generic map (lista de asociación);}

{port map (lista_asociación);]

Restricciones de asociación:

- Ambos tipos (tipos de local y real) deben ser iguales.

- Modo (in,out,inout,buffer) deben ser compatibles (aceptar el flujo de

información en esa dirección).

Los genéricos(Generic):

- Se utiliza para definir y declarar propiedades o constantes del módulo

que están siendo declarados en la entidad.

- Pasa información desde el entorno a nuestro unidad de diseño la cual

no varía en función del tiempo.

- Muy utilizado para la creación de diseños generalizados.

Generalmente se utiliza para definir un contador de módulo N, tiempos de

propagación intrínseco de la puerta, retardo debido a la carga, carga a la

salida de las puertas (fanout), etc.

Ing° Alfredo Granados Ly 1

DISEÑO DIGITAL – Labroratorio No 5 UNMSM-FIE

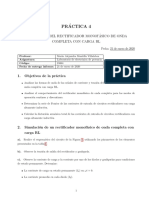

El siguiente ejemplo muestra el año 2012 en los 4 display a segmentos,

utilizamos para ello el circuito llamado Visor diseñado previamente. Primero

diseñaremos el contador binario de 2 bits que genere de manera

automática los valores para los selectores:

Ing° Alfredo Granados Ly 2

DISEÑO DIGITAL – Labroratorio No 5 UNMSM-FIE

Ing° Alfredo Granados Ly 3

DISEÑO DIGITAL – Labroratorio No 5 UNMSM-FIE

Para el contador utilizaremos un proceso, la salida del proceso será una

señal de 2 bits llamada CUENTA ,que se unirá con la entrada Q del circuito

llamado VISOR. También se crearán 4 señales internas que tomarán los

valores fijos de:

N1 <= “0010” y se unirá a la entrada A del circuito VISOR.

N2 <= “0000” y se unirá a la entrada B del circuito VISOR.

N3 <= “0000” y se unirá a la entrada C del circuito VISOR.

N4 <= “0100” y se unirá a la entrada D del circuito VISOR.

La interconexión del circuito VISOR con las diferentes señales se realiza

respetando la secuencia de los puertos tal como fue declarado en la

entidad, es lo que se conoce como asociación por posición.

TRABAJANDO CON MAX+PLUS II

La biblioteca Altera del Max+Plus II contiene varios paquetes que incluyen

entre otros componentes a los dispositivos de la serie 74XXX. Para utilizar

estos componentes deberá añadir en sus programas las siguientes

sentencias:

Utilizando los componentes del paquete MaxPlus2 implementar el siguiente

circuito:

Ing° Alfredo Granados Ly 4

DISEÑO DIGITAL – Labroratorio No 5 UNMSM-FIE

USO DE LA BIBLIOTECA DE MODULOS PARAMETRIZADOS:

En esta parte se describirá la forma de tratar a los componentes

parametrizados mediante el uso de una de las megafunciones de Altera,

dando un ejemplo de los pasos a seguir para emplearlas dentro de su diseño.

Utilizando Memorias con VHDL:

Abra el archivo LPM_PACK.VHD que se encuentra en

C:\MAXPLUS2\VHDL87\LPM, y busque el componente: LPM_ROM. El componente

se lista a continuación:

Ing° Alfredo Granados Ly 5

DISEÑO DIGITAL – Labroratorio No 5 UNMSM-FIE

Utilizando e componente LPM_ROM se le pide implementar la siguiente

memoria de 16x4 bits

TRABAJO FINAL:

Ing° Alfredo Granados Ly 6

DISEÑO DIGITAL – Labroratorio No 5 UNMSM-FIE

1. Implemente un circuito utilizando el estilo estructural que permita

utilizar la salida del 74393 como generador de direcciones para una

memoria de 256 x 7.

2. Implemente el siguiente circuito utilizando el estilo estructural:

Donde:

W es un registro de 8 bits.

El banco de registros está compuesto de 4 registros de 8 bits c/u.

(R0,R1....R7)

El ALU puede realizar 4 operaciones aritméticas: ADD, SUB, INC,

DEC.

El ALU también puede realizar 4 operaciones lógicas: AND, OR,

XOR , NOT

Indicar los bits de control para manejar la Ruta de Datos mostrada en el gráfico

anterior. Presentar la simulación para realizar las siguientes operaciones:

ADD R1,R2,R3

INC R2

XOR R2,R3,R3

DEC R1

NOT R2

Nota: Cada uno de los componentes debe ser diseñado utilizando el estilo

algoritmico e interconectado utilizando el estilo estructural.

Ing° Alfredo Granados Ly 7

También podría gustarte

- SumatoriaDocumento1 páginaSumatoriaCarlosVillavicencioGAún no hay calificaciones

- Indicaciones-Monografia MicroelectronicaDocumento2 páginasIndicaciones-Monografia MicroelectronicaAlfred cas RamirezAún no hay calificaciones

- Ejercicio 1 09.05.2018Documento1 páginaEjercicio 1 09.05.2018Sergio MarceloAún no hay calificaciones

- Manual Antenas Traducido Cap1Documento14 páginasManual Antenas Traducido Cap1CarlosVillavicencioGAún no hay calificaciones

- MCMDocumento3 páginasMCMCarlosVillavicencioGAún no hay calificaciones

- Micro RadaresDocumento8 páginasMicro RadaresCarlosVillavicencioGAún no hay calificaciones

- Indicaciones-Monografia MicroelectronicaDocumento2 páginasIndicaciones-Monografia MicroelectronicaAlfred cas RamirezAún no hay calificaciones

- 03 Final ElectroIDocumento10 páginas03 Final ElectroICarlosVillavicencioGAún no hay calificaciones

- Modulo FPGA + CPLD PDFDocumento36 páginasModulo FPGA + CPLD PDFCarlosVillavicencioGAún no hay calificaciones

- Los 7 SaberesDocumento1 páginaLos 7 SaberesCarlosVillavicencioGAún no hay calificaciones

- Guía onda cilíndricaDocumento4 páginasGuía onda cilíndricaCarlosVillavicencioGAún no hay calificaciones

- Problemas de Ruta de Datos PDFDocumento31 páginasProblemas de Ruta de Datos PDFCarlosVillavicencioGAún no hay calificaciones

- Desbloquear OfficeDocumento1 páginaDesbloquear OfficeCarlosVillavicencioGAún no hay calificaciones

- Ejercicio 4 ProbaDocumento1 páginaEjercicio 4 ProbaCarlosVillavicencioGAún no hay calificaciones

- Examen Sustitutorio 2012-2Documento1 páginaExamen Sustitutorio 2012-2CarlosVillavicencioGAún no hay calificaciones

- Examen Parcial 2013 IDocumento2 páginasExamen Parcial 2013 ICarlos Bustamante ChacchaAún no hay calificaciones

- Examen Sustitutorio 2013-IDocumento2 páginasExamen Sustitutorio 2013-ICarlosVillavicencioGAún no hay calificaciones

- Modulo FPGA + CPLD PDFDocumento36 páginasModulo FPGA + CPLD PDFCarlosVillavicencioGAún no hay calificaciones

- 1.2 Est. Descrip 1-13 Probab y EstadDocumento4 páginas1.2 Est. Descrip 1-13 Probab y EstadCarlosVillavicencioGAún no hay calificaciones

- Laboratorio No4 - Diseño Digital - UNMSM (2012-II)Documento11 páginasLaboratorio No4 - Diseño Digital - UNMSM (2012-II)Marco RíosAún no hay calificaciones

- Lab 4Documento16 páginasLab 4Luis Ignacio Ramirez MartinezAún no hay calificaciones

- Cerradura LectronicaDocumento20 páginasCerradura LectronicaCarlosVillavicencioGAún no hay calificaciones

- Proyecto Final Cerradura ElectronicaDocumento8 páginasProyecto Final Cerradura ElectronicaCarlosVillavicencioGAún no hay calificaciones

- Proyecto Programacion AvanzadaDocumento1 páginaProyecto Programacion AvanzadaCarlosVillavicencioGAún no hay calificaciones

- Examen Sustitutorio 2015 - IIDocumento1 páginaExamen Sustitutorio 2015 - IICarlosVillavicencioGAún no hay calificaciones

- Ultima ExpoDocumento5 páginasUltima ExpoCarlosVillavicencioGAún no hay calificaciones

- Aproximación de la suma de variables aleatorias a la distribución normalDocumento3 páginasAproximación de la suma de variables aleatorias a la distribución normalCarlosVillavicencioGAún no hay calificaciones

- Plan de TrabajoDocumento2 páginasPlan de TrabajoCarlosVillavicencioGAún no hay calificaciones

- Cerradura LectronicaDocumento20 páginasCerradura LectronicaCarlosVillavicencioGAún no hay calificaciones

- Docenotas 1999 15 PDFDocumento72 páginasDocenotas 1999 15 PDFIrving Jose Vazquez Quezada100% (1)

- PFG Marketingdigitalt&lDocumento83 páginasPFG Marketingdigitalt&lalvinAún no hay calificaciones

- c9 PDF RP Rueda CifradoDocumento8 páginasc9 PDF RP Rueda CifradoJosé Miguel Galeano PájaroAún no hay calificaciones

- Análisis Operacional en Vissim para Una IntersecciónDocumento16 páginasAnálisis Operacional en Vissim para Una IntersecciónBryan CancimanceAún no hay calificaciones

- Curriculum Vitae Frank AullaDocumento19 páginasCurriculum Vitae Frank Aullamateo aullaAún no hay calificaciones

- Esquema Normas UpelDocumento7 páginasEsquema Normas UpelKatiuska MendezAún no hay calificaciones

- Simulación de rectificador monofásico de onda completa con carga RLDocumento3 páginasSimulación de rectificador monofásico de onda completa con carga RLFabian ValenciaAún no hay calificaciones

- Diagrama de Gantt LeandroDocumento4 páginasDiagrama de Gantt LeandroLeandro C UgAún no hay calificaciones

- Sociales Cuadernillo Segundo Año de BachilleratoDocumento8 páginasSociales Cuadernillo Segundo Año de BachilleratoAxel Fx57% (7)

- Tarea 14 Algoritmo Snoopy y Protocolos de Memoria CacheDocumento22 páginasTarea 14 Algoritmo Snoopy y Protocolos de Memoria CacheMike OjedaAún no hay calificaciones

- Infografía Trabajo Remoto Simple Verde ClaroDocumento2 páginasInfografía Trabajo Remoto Simple Verde Claromonse glezAún no hay calificaciones

- AV1 T2 Equipo1Documento25 páginasAV1 T2 Equipo1UrielAún no hay calificaciones

- Registro Evaluación Salida Educación Primaria Secundaria MoyobambaDocumento5 páginasRegistro Evaluación Salida Educación Primaria Secundaria MoyobambaPiter Galoc TelloAún no hay calificaciones

- Catálogo Mayo IDocumento209 páginasCatálogo Mayo IJD94 - Música ElectrónicaAún no hay calificaciones

- Proyecto de Radio EscolarDocumento8 páginasProyecto de Radio EscolarFernandoAgostinhoPereiraAún no hay calificaciones

- Qué Es NodejsDocumento9 páginasQué Es NodejsDiego Tapia100% (1)

- Ingeniería en minería: Ventilación, peligros y tipos de extintoresDocumento24 páginasIngeniería en minería: Ventilación, peligros y tipos de extintoresDalia Gonzalez AcostaAún no hay calificaciones

- Funciones ElementalesDocumento21 páginasFunciones ElementalesArturo FuentesAún no hay calificaciones

- Mat II 2018 Modelo 1 ExamenDocumento4 páginasMat II 2018 Modelo 1 Examendoctor_leeAún no hay calificaciones

- Xx-xxx-001 Recepcion Materia PrimaDocumento4 páginasXx-xxx-001 Recepcion Materia PrimaAngela Chumioque GarciaAún no hay calificaciones

- Instancia GeneralDocumento1 páginaInstancia GeneralCOLEGIO DEL SANTÍSIMO -BARQUISIMETO-VENEZUELAAún no hay calificaciones

- 30 Libros de Álgebra en PDF para Consultar Gratis - Enclave CientíficoDocumento8 páginas30 Libros de Álgebra en PDF para Consultar Gratis - Enclave CientíficoMarcelo LunaAún no hay calificaciones

- Book Dibujo - Búsqueda de GoogleDocumento1 páginaBook Dibujo - Búsqueda de GoogleFERNANDA DIAZ BARRIGAAún no hay calificaciones

- Iniciar Curso de ExcelDocumento16 páginasIniciar Curso de ExcelJulio Carrion ContrerasAún no hay calificaciones

- Cableado Estructurado-UCVDocumento85 páginasCableado Estructurado-UCVpepe100% (1)

- Matriz, Metodologica PreinversionDocumento1 páginaMatriz, Metodologica Preinversioniracax002Aún no hay calificaciones

- Curso PLC Allen Bradley RSLogix 500Documento3 páginasCurso PLC Allen Bradley RSLogix 500Carlos Eduardo JaenAún no hay calificaciones

- INFORMATICA TrabajoDocumento31 páginasINFORMATICA Trabajojhon pavaAún no hay calificaciones

- Produccion 1 Eje 3Documento7 páginasProduccion 1 Eje 3Jeison MaciasAún no hay calificaciones

- Analisisestructuralbibliografia 090914160046 Phpapp01Documento3 páginasAnalisisestructuralbibliografia 090914160046 Phpapp01Sara ArceAún no hay calificaciones