Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Multiplicador24 2

Cargado por

CristianQuispeVentura0 calificaciones0% encontró este documento útil (0 votos)

13 vistas2 páginaselectronica fiee unmsm

Título original

multiplicador24-2

Derechos de autor

© © All Rights Reserved

Formatos disponibles

TXT, PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoelectronica fiee unmsm

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como TXT, PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

13 vistas2 páginasMultiplicador24 2

Cargado por

CristianQuispeVenturaelectronica fiee unmsm

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como TXT, PDF, TXT o lea en línea desde Scribd

Está en la página 1de 2

// DSCH 2.

6c

// 11/06/2017 12:35:36 a.m.

// C:\Users\Cristian\Downloads\multiplicador24-2.sch

module multiplicador24-2( ci1,A0,A1,A2,A3,B0,B1,B2,

B3,SP3,SP0,SP1,SP2,ci2,ci3,display17,

display16,display15,display14,display13,display12,display11,display10,carry1);

input ci1,A0,A1,A2,A3,B0,B1,B2;

input B3,SP3,SP0,SP1,SP2,ci2,ci3;

output

display17,display16,display15,display14,display13,display12,display11,display10;

output carry1;

wire w40,w41,w42,w43,w44,w45,w46,w47;

wire w48,w49,w50,w51,w52,w53,w54,w55;

wire w56,w57,w58,w59,w60,w61,w62,w63;

wire w64,w65,w66,w67,w68,w69,w70,w71;

and #(1) and2(w17,A0,B1);

and #(1) and2(w27,A3,B1);

and #(1) and2(w29,A2,B1);

and #(1) and2(w8,A1,B0);

and #(1) and2(w18,A2,B0);

and #(1) and2(w22,A3,B0);

and #(1) and2(w13,A0,B0);

and #(1) and2(w37,A1,B1);

nand #(4) nand3_FA1(w11,w40,w41,w42);

xor #(4) xor2_FA2(w12,w43,w10);

nand #(4) nand2_FA3(w40,SP1,w8);

nand #(4) nand2_FA4(w41,SP1,w10);

nand #(4) nand2_FA5(w42,w8,w10);

xor #(4) xor2_FA6(w43,w8,SP1);

nand #(4) nand3_FA7(w10,w44,w45,w46);

xor #(4) xor2_FA8(display10,w47,ci1);

nand #(4) nand2_FA9(w44,SP0,w13);

nand #(4) nand2_FA10(w45,SP0,ci1);

nand #(4) nand2_FA11(w46,w13,ci1);

xor #(4) xor2_FA12(w47,w13,SP0);

nand #(4) nand3_FA13(w20,w48,w49,w50);

xor #(4) xor2_FA14(w21,w51,w11);

nand #(4) nand2_FA15(w48,SP2,w18);

nand #(4) nand2_FA16(w49,SP2,w11);

nand #(4) nand2_FA17(w50,w18,w11);

xor #(4) xor2_FA18(w51,w18,SP2);

nand #(4) nand3_FA19(carry1,w52,w53,w54);

xor #(4) xor2_FA20(w25,w55,w20);

nand #(4) nand2_FA21(w52,SP3,w22);

nand #(4) nand2_FA22(w53,SP3,w20);

nand #(4) nand2_FA23(w54,w22,w20);

xor #(4) xor2_FA24(w55,w22,SP3);

nand #(4) nand3_FA25(w31,w56,w57,w58);

xor #(4) xor2_FA26(display13,w59,w30);

nand #(4) nand2_FA27(w56,w25,w29);

nand #(4) nand2_FA28(w57,w25,w30);

nand #(4) nand2_FA29(w58,w29,w30);

xor #(4) xor2_FA30(w59,w29,w25);

nand #(4) nand3_FA31(display15,w60,w61,w62);

xor #(4) xor2_FA32(display14,w63,w31);

nand #(4) nand2_FA33(w60,ci3,w27);

nand #(4) nand2_FA34(w61,ci3,w31);

nand #(4) nand2_FA35(w62,w27,w31);

xor #(4) xor2_FA36(w63,w27,ci3);

nand #(4) nand3_FA37(w39,w64,w65,w66);

xor #(4) xor2_FA38(display11,w67,ci2);

nand #(4) nand2_FA39(w64,w12,w17);

nand #(4) nand2_FA40(w65,w12,ci2);

nand #(4) nand2_FA41(w66,w17,ci2);

xor #(4) xor2_FA42(w67,w17,w12);

nand #(4) nand3_FA43(w30,w68,w69,w70);

xor #(4) xor2_FA44(display12,w71,w39);

nand #(4) nand2_FA45(w68,w21,w37);

nand #(4) nand2_FA46(w69,w21,w39);

nand #(4) nand2_FA47(w70,w37,w39);

xor #(4) xor2_FA48(w71,w37,w21);

endmodule

// Simulation parameters in Verilog Format

always

#10 ci1=~ci1;

#20 SP3=~SP3;

#30 SP0=~SP0;

#40 SP1=~SP1;

#50 SP2=~SP2;

#60 ci2=~ci2;

#70 ci3=~ci3;

// Simulation parameters

// ci1 CLK 10 10

// A0 CLK 20 20

// A1 CLK 30 30

// A2 GND

// A3 GND

// B0 CLK 40 40

// B1 CLK 50 50

// B2 GND

// B3 GND

// SP3 CLK 60 60

// SP0 CLK 70 70

// SP1 CLK 80 80

// SP2 CLK 90 90

// ci2 CLK 100 100

// ci3 CLK 110 110

También podría gustarte

- Compresor ChicagoDocumento4 páginasCompresor ChicagoCristianQuispeVenturaAún no hay calificaciones

- Repuestos Criticos AsepticaDocumento12 páginasRepuestos Criticos AsepticaCristianQuispeVenturaAún no hay calificaciones

- Instalacion de Maquina OzonoDocumento6 páginasInstalacion de Maquina OzonoCristianQuispeVenturaAún no hay calificaciones

- Lineas de AcoplamientoDocumento5 páginasLineas de AcoplamientoCristianQuispeVenturaAún no hay calificaciones

- Acoplamientos de Impedancias en Guias de OndaDocumento5 páginasAcoplamientos de Impedancias en Guias de OndaCristianQuispeVenturaAún no hay calificaciones

- Informe de PotenciaDocumento11 páginasInforme de PotenciaCristianQuispeVenturaAún no hay calificaciones

- Proyecto de PotenciaDocumento6 páginasProyecto de PotenciaCristianQuispeVenturaAún no hay calificaciones

- Informe Previo de PuentesDocumento6 páginasInforme Previo de PuentesCristianQuispeVenturaAún no hay calificaciones

- Informeprevio 3 Cristianquispeventura 12190027Documento4 páginasInformeprevio 3 Cristianquispeventura 12190027CristianQuispeVenturaAún no hay calificaciones

- Resumen 1Documento10 páginasResumen 1patoAún no hay calificaciones

- Prueba 6° Guido - Quiebre DemocraciaDocumento3 páginasPrueba 6° Guido - Quiebre Democraciagabiota_200588% (17)

- Sucursales BanamexDocumento3 páginasSucursales BanamexViktor Torres0% (1)

- Fernández Latour de Botas Olga Estudio Preliminar de El Torito de Los MuchachosDocumento16 páginasFernández Latour de Botas Olga Estudio Preliminar de El Torito de Los MuchachosRocíoOteroAún no hay calificaciones

- Link Super Criatura GuerreraDocumento4 páginasLink Super Criatura GuerreraGoju Shorei Max Oñate DojoAún no hay calificaciones

- Guía 2 Técnicas de Conteo-2-4Documento3 páginasGuía 2 Técnicas de Conteo-2-4Angie Poloche Ramirez100% (1)

- Por Quién Doblan Las CampanasDocumento1 páginaPor Quién Doblan Las CampanasEdith CerbinoAún no hay calificaciones

- Byron Serrano Diagrama de GanttDocumento9 páginasByron Serrano Diagrama de GanttNatalia SerranoAún no hay calificaciones

- La Armadura CompletaDocumento2 páginasLa Armadura CompletaSánchez JEAún no hay calificaciones

- Trabajo Academico - OFIMATICA II - UAPDocumento14 páginasTrabajo Academico - OFIMATICA II - UAPMarcos Santiago AhumadaAún no hay calificaciones

- Histori Adela Comp 82 ArchDocumento702 páginasHistori Adela Comp 82 ArchMatias MatsAún no hay calificaciones

- Hoja de Poderes Del Guerrero Psíquico D&Amp D - ViuhDocumento4 páginasHoja de Poderes Del Guerrero Psíquico D&Amp D - ViuhJose Augusto Orasma SierraAún no hay calificaciones

- Despiece LP 9-20 PDocumento16 páginasDespiece LP 9-20 PvictorhernandezregaAún no hay calificaciones

- El Imperio Romano 1Documento27 páginasEl Imperio Romano 1Luppus SumAún no hay calificaciones

- El Ultimo Enemigo (Richard Hillary)Documento17 páginasEl Ultimo Enemigo (Richard Hillary)bombardieri84100% (1)

- Rafael José Urdaneta FaríasDocumento5 páginasRafael José Urdaneta Faríaspadrino135Aún no hay calificaciones

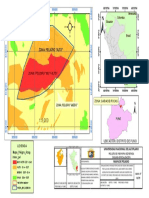

- Mapa Peligro AzogDocumento1 páginaMapa Peligro AzogJusto CanazaAún no hay calificaciones

- Empresas HabilitadasDocumento3 páginasEmpresas HabilitadasCarlos MolloAún no hay calificaciones

- Breve Biografía Del General Choi Hong HiDocumento5 páginasBreve Biografía Del General Choi Hong HiXiomarly Gutiérrez MolinaAún no hay calificaciones

- Ultimos Honores de La BanderaDocumento5 páginasUltimos Honores de La Banderallina86Aún no hay calificaciones

- Trabajo de Cipriano CastroDocumento19 páginasTrabajo de Cipriano Castrocarlosraulgonzalez100% (1)

- Raz. Lógico - MiscelaneaDocumento2 páginasRaz. Lógico - MiscelaneaNiurka Luana y Andriuk Sebastián Hernandez CisnerosAún no hay calificaciones

- Textos de Esa Espiga Sembrada en CaraboboDocumento8 páginasTextos de Esa Espiga Sembrada en Caraboboramon emilioAún no hay calificaciones

- Permiso de Trabajo en AlturaDocumento4 páginasPermiso de Trabajo en AlturaDARIAN ALVAREZ MORALESAún no hay calificaciones

- CÉSAR, Cayo Julio César Octavio Augusto - (Frases - Citas.famosas - Celebres)Documento2 páginasCÉSAR, Cayo Julio César Octavio Augusto - (Frases - Citas.famosas - Celebres)Juan Carlos PalczewiczAún no hay calificaciones

- Papelucho Historiador 5°Documento6 páginasPapelucho Historiador 5°AngieAún no hay calificaciones

- 04 Operaciones Con Fracciones - Libro de TrabajoDocumento5 páginas04 Operaciones Con Fracciones - Libro de TrabajoRobert Salazar ValverdeAún no hay calificaciones

- 08 - Comportamiento en El CombateDocumento45 páginas08 - Comportamiento en El Combatecatalan0104Aún no hay calificaciones

- Sendero Luminoso y Mrta 16 de Julio - Docx TerminadoDocumento29 páginasSendero Luminoso y Mrta 16 de Julio - Docx TerminadoAlizon Valencia Chura100% (1)

- PDF - DIC - Aperturas Tiendas - Navidad IIDocumento4 páginasPDF - DIC - Aperturas Tiendas - Navidad IIAlexandra Vallejos OrnayAún no hay calificaciones

- La Hoguera BárbaraDocumento15 páginasLa Hoguera BárbaraPedro Saad Herrería67% (3)