Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Final Diferencial

Cargado por

PaulDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Final Diferencial

Cargado por

PaulCopyright:

Formatos disponibles

AMPLIFICADOR DIFERENCIAL

Objetivos

Experimentar las propiedades del amplificador diferencial.

Materiales y equipo

- Osciloscopio

- Multímetro digital

- Generador de señales

- Punta de prueba de osciloscopio

- Protoboard

- Cables de conexiones diversos

- Transformador con toma central

- Transistores

- Resistores

- Potenciómetros

- Condensadores

- Computadora con Multisim

1.- Introducción

El amplificador diferencial es un circuito que constituye parte fundamental de muchos

amplificadores y comparadores y es la etapa clave de la familia lógica ECL. En este tema se

describen y analizan diferentes tipos de amplificadores diferenciales basados en dispositivos

bipolares.

2.- Análisis de un amplificador diferencial básico bipolar

El amplificador diferencial constituye la etapa de entrada más típica de la mayoría de los

amplificadores operaciones y comparadores, siendo además el elemento básico de las puertas

digitales de la familia lógica ECL.

En la figura 6.1.a aparece la estructura básica de este amplificador. Uno de sus aspectos más

importantes es su simetría que le confiere unas características muy especiales de análisis y diseño.

Por ello, los transistores Q1 y Q2 deben ser idénticos, aspecto que únicamente se logra cuando el

circuito está fabricado en un chip. Realizar este amplificador con componentes discretos pierde sus

principales propiedades al romperse esa simetría. A continuación se realiza un análisis de este

amplificador, primero en continua y luego en alterna donde se introducen los conceptos de

configuración en modo común y modo diferencial.

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

2.1.- Análisis en continua

En el caso de que vi1 y vi2 sean componentes de pequeña señal, y suponiendo que hFE>>1,

entonces se puede extraer del circuito de la figura 6.1.a la siguiente relación

La simetría del circuito y el hecho de que Q1 y Q2 son transistores idénticos hace que IE1=IE2=IE de

forma Que

La ecuación de recta de carga estática se obtiene aplicando KVL a la malla colector-emisor de los

Transistores:

Laboratorio de Circuitos Electroó nicos II Paó gina 2

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Esta recta se encuentra dibujada en la figura 6.1.b. La situación del punto de trabajo define los

límites de variación de señal de entrada y el rango de funcionamiento lineal permisible. La máxima

amplitud de salida se consigue cuando VCEQ=VCC.

2.2.- Análisis de las configuraciones en modo común y diferencial

La simetría del amplificador diferencial permite simplificar su

Análisis convirtiendo las tensiones de entrada en tensiones de

entrada de modo común y modo diferencial. Además, estos

conceptos están en consonancia con las aplicaciones típicas del

amplificador operacional que se suele utilizar para amplificar la

diferencia entre las dos señales de entrada. La tensión de entrada

en modo diferencial (vid) y modo común (vic) se definen como

A su vez, estas tensiones vid y vic dan lugar a dos tensiones

de salida, en modo diferencial (vod) y modo común (voc), definidas

de una manera similar como

Con la definición de las tensiones en modo diferencial y modo común, el amplificador diferencial

tiene dos ganancias, una en modo diferencial (Ad) y otra en modo común (Ac) definidas como

La aplicación de estos conceptos permite transformar el circuito de la figura 6.1.a en el de la figura

6.2.

Este nuevo circuito presenta unas propiedades de simetría que facilita su análisis mediante la

aplicación del principio de superposición a las entradas en modo diferencial y común

independientemente.

• Ganancia en modo diferencial

En la figura 6.3 se muestra el circuito equivalente simplificado del amplificador diferencial cuando

únicamente se considera modo diferencial a la entrada. El análisis del circuito establece las

siguientes ecuaciones

Laboratorio de Circuitos Electroó nicos II Paó gina 3

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Resolviendo las ecuaciones de 6.7 se llega fácilmente a la siguiente relación

siendo la única solución posible

resultando que

ve = 0

esta ecuación indica que la tensión de pequeña señal en el emisor de los transistores es nula, es

decir, que ese nudo se comporta como un nudo de masa virtual; no hay que confundirla con la

masa real del circuito.

Por consiguiente, analizar el circuito de la figura 6.3 es equivalente a analizar los circuitos

equivalentes del amplificador diferencial en modo diferencial mostrados en las figuras 6.4.a y

6.4.b. La ganancia en tensión en modo diferencial de este amplificador es

Laboratorio de Circuitos Electroó nicos II Paó gina 4

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

La impedancia de entrada del circuito de la figura 6.4 es Zi=hie. Por consiguiente, la impedancia de

entrada vista a través de los dos terminales de entrada diferencial es

Ganancia en modo común

En la figura 6.5 aparece el circuito equivalente del amplificador diferencial cuando únicamente se

considera modo común a la entrada. Para obtener un circuito más simplificado se va a determinar

en primer lugar las impedancias equivalentes Ze1 y Ze2 vista a través de los emisores de los

transistores Q1 y Q2. Estas impedancias se definen como

Analizando el circuito de la figura 6.5 se obtiene la siguiente ecuación

Laboratorio de Circuitos Electroó nicos II Paó gina 5

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

que permite demostrar que

Por otra parte, la tensión ve se puede expresar como

y utilizando las ecuaciones anteriores fácilmente se demuestra que

Luego, los emisores de Q1 y Q2 “ven” una resistencia equivalente de forma que el circuito de la

figura 6.5 se transforma en los circuitos equivalentes más sencillos mostrados en la figuras 6.6.a y

6.6.b. Fácilmente se demuestra que la ganancia en modo común es

• Relación de rechazo en modo común

Un amplificador diferencial ideal tiene una tensión de salida proporcional a vid y no depende de la

componente en modo común (Ac=0). En la práctica no sucede así y para medir esa desviación se

introduce el concepto de relación de rechazo en modo común RRMC; en inglés common-mode

rejection ratio o CMRR. Se define la RRMC como la relación entre la ganancia en modo diferencial y

modo común

Laboratorio de Circuitos Electroó nicos II Paó gina 6

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

que a veces se expresa en decibelios como

3.- Amplificador diferencial bipolar con fuente de corriente

En la etapa diferencial anterior una RRMC muy elevada exige una RE grande; en el caso ideal RRMC

si RE . Sin embargo, la polarización del transistor es fuertemente dependiente del valor de

esta resistencia. Una alternativa que se utiliza en la práctica consiste en sustituir la resistencia RE

por una fuente de corriente. De esta manera, la polarización del circuito puede realizarse con

facilidad y la RRMC es muy elevada ya que una fuente de corriente presenta una impedancia

interna muy alta.

En la figura 6.7.a se muestra un amplificador diferencial polarizado con una fuente de corriente de

valor IEE.

Esta corriente se reparte simétricamente en ambos transistores resultando que en continua

Laboratorio de Circuitos Electroó nicos II Paó gina 7

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Cuando se aplica una tensión de entrada diferencial, la suma de corriente en ambos transistores se

mantiene constante a IEE, es decir,

Esto significa que un incremento de corriente en un transistor origina una disminución de corriente

en la misma proporción en el otro transistor. La gráfica de la figura 6.7.b presenta la característica

de transferencia del amplificador cuando se aplica una tensión en modo diferencial. Este circuito

opera con tensiones máximas de entrada en modo diferencial bajas; del orden de 100mV~4VT.

Superado este valor uno de los transistores se corta y por el otro circula toda la corriente IEE. Las

características de transferencia son lineales en una pequeña región de operación (±2VT). Una

modificación de este amplificador para que trabaje con tensiones en modo diferencial

mayores consiste en añadir una resistencia de emisor tal como se describe en la figura 6.8.a. Este

circuito mantiene la simetría de un amplificador diferencial aumentando el rango de tensiones de

entrada. Este efecto se puede observar claramente en la figura 6.8.b en donde la característica de

transferencia tiene un rango de entrada lineal mayor según aumenta RE. El inconveniente es que la

ganancia en modo diferencial disminuye. Para este circuito, se puede demostrar que si hre=hoe=0,

la ganancia en modo diferencial vale

Valores razonables de RE deben estar comprendidos entre 50 a 100Ω ya que con valores grandes la

Ad se reduce excesivamente.

3.1.- Amplificador diferencial con carga activa

Laboratorio de Circuitos Electroó nicos II Paó gina 8

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Las fuentes de corriente pueden ser utilizadas como carga activa en un amplificador diferencial. El

espejo de corriente es el circuito que mejor se adapta al tener una resistencia interna no

demasiado elevada la cual elimina problemas de polarización y mantiene una ganancia muy alta.

La figura 6.9.a muestra la estructura de un amplificador diferencial que tiene una carga activa

constituida por el espejo de corriente formado por los transistores PNP Q3, Q4 y Q5. Por

necesidades de polarización la intensidad de referencia de este espejo tiene que ser la mitad de IEE

ya que las intensidades de colector de Q1 y Q4, y Q2 y Q3 deben ser idénticas.

Fácilmente se puede comprobar aplicando las propiedades de simetría del amplificador diferencial

que la ganancia en modo diferencial es

donde hoep y hoen es la resistencia de salida de un transistor PNP y NPN respectivamente.

En la figura 6.9.b se presenta un amplificador diferencial con una carga activa constituida por un

espejo de corriente (Q3,Q4) que necesita menos dispositivos que el caso anterior. Tiene una única

salida que proporciona una conversión de entrada diferencial-salida simple (differential to single-

ended conversion) y, aunque en principio se rompe la simetría del amplificador diferencial, este

circuito tiene una ganancia en modo diferencial.

1) ¿Qué características resaltantes ofrece el amplificador diferencial?

El circuito del amplificador diferencial es una conexión de muy grande aceptación y

uso en unidades de circuitos integrados.

Laboratorio de Circuitos Electroó nicos II Paó gina 9

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Se puede utilizar este amplificador como un modo inversor (La salida está

desfasada 1800 con respecto a la entrada), o modo o modo no inversor (la salida no

tiene una desfase con respecto a la entrada), o modo diferencial cuando utiliza los

dos modos anteriores.

La característica principal del amplificador diferencial es la ganancia muy grande

cuando se aplican señales opuestas a las entradas, en comparación con la muy

pequeña ganancia obtenida con entradas comunes.

El amplificador diferencial posee una gran estabilidad e inmunidad a las señales

interferentes.

Se usa este amplificador para amplificar las señales en medios ruidosos, o sea el

ruido es atenuado en este amplificador (Modo común, ganancia de voltaje

pequeña) y la señal es amplificada (Modo diferencial, ganancia de voltaje es alta)

En la figura aparece la estructura básica de este amplificador. Uno de sus aspectos

más importantes es su simetría que le confiere unas características muy especiales

de análisis y diseño. Por ello, los transistores Q1 y Q2 deben ser idénticos, aspecto

que únicamente se logra cuando el circuito está fabricado en un chip. Realizar este

amplificador con componentes discretos pierde sus principales propiedades al

romperse esa simetría

2) Encontrar los puntos de reposo del amplificador a experimentar de la figura 3a y 3b.

Laboratorio de Circuitos Electroó nicos II Paó gina 10

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Como nos piden los

puntos de reposo, entonces trabajaremos en d.c

I EE

=I C1 I C 1 =I C2

Se sabe que: 2 ; y también que

Laboratorio de Circuitos Electroó nicos II Paó gina 11

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Operando en la malla de

RB y R E , obtenemos:

I B 1 RB +0 . 7+220 I C 1 +50 I C 1 +I EE R E=12 V

I B 1 .1 K Ω+0 .7 +(220+50 )Ω. I C +I EE . 4 .7 K Ω=12V

I B 1 .1 K Ω+0 .7 +270 Ω.( β . I B 1 )+2 β. I B 1 . 4 .7 K Ω=12V

I B 1 =6 .2 μA

I C1 =200 . I B1 =1 .24 mA

⇒ I EE=2 . 48 mA

En los puntos de reposo:

V CE 1 =V CC −I C1 . RC =12−1. 24 mA(1 k )=10 .76 V

V B =6 .2 mV

26 mV

re=

Ic 1

re=20. 97

Laboratorio de Circuitos Electroó nicos II Paó gina 12

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Como nos piden los puntos de reposo, trabajaremos en DC:

Trabajamos primero en la parte marcada, realizaremos divisor de voltaje:

12(4.7 K W)

VB = - = -5.81V

4.7 K W + 5 K W

VE = VB - VBE = -5.81 - 0.7 � VE = -6.51

VE - ( -VEE )

I EE = = 1.4mA

3.9 K W

I EE = 1.4mA

I EE

= I C1 = I C 2 � I EE = 2 I C1 = 2 I C 2

2

I C1 = b ( I B1 )

I C1 = 0.7 mA

I C1 = b ( I B1 ) � I B1 = 3.5m A

VB1 = 3.5m A *1K W = 3.5mV

VCE1 = VCC - I C1 ( RC ) = 12 - 0.7 *1 = 11.3V

Laboratorio de Circuitos Electroó nicos II Paó gina 13

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

3) Considerando que V1 y V2 son dos señales de la misma magnitud pero desfasadas una

con respecto a la otra 180°, encontrar Ad, Ac, V0, Zi, Z0, CMRR.

Configuración modo común:

Determinando la ganancia de voltaje: Av

Vo=−β Ib 1Rc1

Vi=Ib 1β(re )+ β Ib1(0.22k )+β Ib1(50)+( β Ib 1+ β Ib2)(4.7k )

Vo

Av=

Vi

−1000 β Ib 1

Av=

9690.97 β Ib1

Av=−0.1031

Laboratorio de Circuitos Electroó nicos II Paó gina 14

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Determinación de la impedancia de entrada en modo común:

Zi=β (re )+β 220+50 β +2 β( 4 . 7 k )

Zi=β (22 . 97+270+9400 )

Zi=1938 . 452 k

Determinación de la impedancia de salida en modo común:

Zo=Rc

Zo=1 k

Configuración modo diferencial

Determinación de la ganancia de voltaje en modo diferencial:

Vo = -ΒIB1.Rc1

Vd = IB1 βre + β IB1*270 + β IB1 (Re//(270+re)) = β IB1 (re + 270 + Re//(270+re))

Pero VD = 2V1

Ad = vo/vd = vo/2v1 = -Rc/ 2(re + 270 + Re//(P+re))=- 0.88135

Ad = -0.88135

Laboratorio de Circuitos Electroó nicos II Paó gina 15

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Determinación de la impedancia de entrada en modo diferencial:

Zid = β (re + P + Re// (270+re)) =113.48 KΩ

Zid = 113.48 KΩ

Determinación de la impedancia de salida en modo diferencial:

Zo = Rc = 1KΩ

CMRR = Ad/Ac = -0.88135/ -0.1031 = 8.5484

Configuración en modo común

Laboratorio de Circuitos Electroó nicos II Paó gina 16

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Esta en paralelo con la fuente 1.4mA

hoe= 25 uS → 1/hoe = 40 KΩ

El procedimiento es el mismo para el circuito a solo ahora el R E es 40kW

Determinando la ganancia de voltaje:

Vo = -β IB1.Rc1

V1 = IB1βre + β IB1*270 +( β IB1 + βIb2)Re = β IB1 (re + 270 + Re)

Ac = VO/V1 = -Rc/(re + 270 +2Re)=-0.01245 Ac = -0.01245

Impedancia de entrada en modo común:

ZiMC = β (re + P + 2Re) =

200(22.26+270+80000) = 1938.452 KΩ

ZiMC = 16.058 MΩ

Impedancia de salida en modo común:

Zo = Rc = 1KΩ

Configuración en modo diferencial:

Vo = -β IB1.Rc1

V1 = IB1βre + ΒIB1*270 + β IB1 (Re// (270+re)) = β IB1 (re + P + Re//(270+re))

Pero Vd = 2V1

Ad = vo/v1 = vo/2vd = -Rc/ 2(re + 270 + Re//(270+re))= -0.85851

Laboratorio de Circuitos Electroó nicos II Paó gina 17

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Ad = -0.85851.

Impedancia de entrada en modo común:

Zid = β (re + 270 + Re//(270+re)) =113.48 KΩ Zid = 113.48 KΩ

Determinación de la impedancia de salida en modo común: Zo = Rc = 1KΩ

CMRR = Ad/Ac = -0.85851/ -0.01245 = 68.957

4) ¿Qué ventajas se obtiene al utilizar una fuente de corriente en lugar de la resistencia del

emisor?

El uso de una fuente de corriente en lugar de una resistencia de emisor determina de modo

directo el valor final de mi corriente en la configuración del amplificador diferencial y como

este valor es el de continua, una fuente de este tipo el valor de esta permanece constante y la

ganancia se mantiene estable.

Sabemos que una fuente de corriente constante posee una alta impedancia con lo que

equivalentemente tendríamos una R E alta. Dado que

R

¿

¿

¿

−hfe∗Rc∗1

∗( Rg ∨¿ Rb )

Rg

A c=

¿

Vemos que al aumentar la resistencia R E la ganancia en modo común disminuye y en

consecuencia el CMRR del amplificador crece.

Laboratorio de Circuitos Electroó nicos II Paó gina 18

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Simulación:

Laboratorio de Circuitos Electroó nicos II Paó gina 19

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Preguntas adicionales

1. ¿QUE ES UN AMPLIFICADOR OPERACIONAL?

Es amplificador electrónico de alta ganancia acoplado en corriente

continua que tiene dos entradas y una salida. En esta configuración, la salida

Laboratorio de Circuitos Electroó nicos II Paó gina 20

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

del dispositivo es, generalmente, de cientos de miles de veces mayor que la

diferencia de potencial entre sus entradas.

2. Aplicaciones de amplificadores diferenciales

El par diferencial es una base fundamental para la electrónica analógica.

Los amplificadores operacionales y comparadores de tensión se basan en él.

Así mismo, los multiplicadores analógicos, empleados en calculadoras

analógicas y en mezcladores, están basados en pares diferenciales.

Los amplificadores de transconductancia también, básicamente, son pares

diferenciales.

En Electrónica digital, la tecnología ECL se basa en un par diferencial.

Muchos circuitos de interfaz y cambiadores de nivel se basan en pares

diferenciales.

3. ¿Cómo funciona un amplificador diferencial?

El amplificador diferencial básico tiene 2 entradas V1 y V2. Si la tensión de

V1 aumenta, la corriente del emisor del transistor Q1 aumenta (acordarse que

IE = BxIB), causando una caída de tensión en Re. Si la tensión de V2 se

mantiene constante, la tensión entre base y emisor del transistor Q2

disminuye, reduciéndose también la corriente de emisor del mismo transistor.

Esto causa que la tensión de colector de Q2 (Vout+) aumente. La entrada V1

es la entrada no inversora de un amplificador operacional. Del mismo modo

cuando la tensión en V2 aumenta, también aumenta la la corriente de colector

del transistor Q2, causando que la tensión de colector del mismo transistor

disminuya, (Vout+) disminuye. La entrada V2 es la entrada inversora del

amplificador operacional. Si el valor de la resistencia RE fuera muy grande,

obligaría a la suma de las corrientes de emisor de los transistores Q1 y Q2, a

mantenerse constante, comportándose como una fuente de corriente. Entonces,

al aumentar la corriente de colector de un transistor, disminuirá la corriente de

colector del otro transistor. Por eso cuando la tensión V1 crece, la tensión en

V2 decrece.

4. ¿Cuáles son los métodos de trabajo del amplificador diferencial?

Laboratorio de Circuitos Electroó nicos II Paó gina 21

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Modo Diferencial

Para V1=V2 y suponiendo F>>1, las corrientes de colector y emisor de cada

etapa son iguales. Todas estas corrientes tienen magnitudes iguales

(aproximadamente) a IEE/2 debido a la simetría del circuito y a la

despreciable corriente que circula por RE. Si incrementamos V1 en v/2 y

simultáneamente disminuimos V2 en v/2, la señal de salida aumenta en v

advertir que el circuito funciona en modo lineal mientras v<4VT.

Modo Común

Consideremos que las dos tensiones V1 y V2 aumentan en v/2. La tensión

diferencial Vd permanece nula mientras que Ic1 e Ic2 son iguales. No obstante

la tensión VE aumenta.

Por lo tanto dependiendo de la señal de entrada, el amplificador diferencial

actúa o bien como etapa en emisor común o bien como etapa en emisor común

con resistencia de emisor. Por lo tanto la ganancia de esta etapa es

notablemente mayor en el funcionamiento como modo diferencial que como

modo común. Normalmente los amplificadores diferenciales se diseñan de

forma que a efectos prácticos sólo resulten amplificadas las señales

diferenciales.

Amplificador diferencial con fuente de corriente o fuente de espejo.

5. diferencia entre un amplificador operacional y un diferencial

El amplificador diferencial es un tipo de configuración que tiene el

amplificador operacional y también se puede hacer con transistores,

simplemente se toma señal tanto por la entrada positiva como por la negativa

para que el resultado a la salida sea la diferencia de estas dos, mas bien si hay

amplificador operacional y comparadores, el comparador es también un

Laboratorio de Circuitos Electroó nicos II Paó gina 22

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

operacional pero especial para ser usado como comparador, cosa que realiza

también el amplificador operacional

Mediciones:

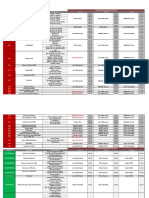

A CMRR

Modo

Ac = 0.252

común

CASO I 0.76dB

Modo

Ad = 0.275

diferencial

Modo

Ac = 0.107

común

CASO II 0.55dB

Modo

Ad = 0.114

diferencial

Modo

Ac = 0.00012

común

CASO III 64.5dB

Modo

Ad = 0.2014

diferencial

Conclusiones:

El comportamiento del amplificador varía de acuerdo al tipo de entrada que se use, ya sea

en modo común o modo diferencial.

Al variar los valores de las resistencias, las amplitudes de las señales se ven afectadas— lo

cual era de esperarse—tanto en el modo común como en el modo diferencial.

Laboratorio de Circuitos Electroó nicos II Paó gina 23

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

(Universidad del Perú, Decana de América)

FACULTAD DE INGENIERIA ELECTRÓNICA Y ELÉCTRICA

Del mismo modo, al cambiar la RE por una fuente de corriente, ésta alteró la forma inicial

de la señal.

La ganancia de este amplificador es mayor en su modo diferencial (entradas de valores

opuestos) que en su modo común (entradas de igual valor).

Observación

Un transformador puede utilizarse para desfasar dos señales.

Laboratorio de Circuitos Electroó nicos II Paó gina 24

También podría gustarte

- Amplificador Diferencial BipolarDocumento18 páginasAmplificador Diferencial BipolarROCIOAún no hay calificaciones

- Laboratorio Circuitos Electronicos2 Unmsm-Previo-Amplificador DiferencialDocumento20 páginasLaboratorio Circuitos Electronicos2 Unmsm-Previo-Amplificador DiferencialGersonPaulinhoSulcaAún no hay calificaciones

- Amplificador Diferencial 1Documento17 páginasAmplificador Diferencial 1Yerko ArayaAún no hay calificaciones

- Amplificador DiferencialDocumento13 páginasAmplificador DiferencialisraelvaldiviesogarcAún no hay calificaciones

- Practica #7Documento10 páginasPractica #7Marcos ThompsonAún no hay calificaciones

- Amplificador Diferencial01Documento19 páginasAmplificador Diferencial01JOSEADANAún no hay calificaciones

- Practica #8 Elian Triviño VeraDocumento9 páginasPractica #8 Elian Triviño VeraElian Triviño100% (1)

- Amplificador Diferencial - Edgar Uriel Hernández MartínezDocumento7 páginasAmplificador Diferencial - Edgar Uriel Hernández MartínezEdgar Uriel Hernández MartínezAún no hay calificaciones

- ELECTRONICA Practica 7 Amplificador Base Comun Colector ComunDocumento9 páginasELECTRONICA Practica 7 Amplificador Base Comun Colector ComunMian Chauca ApazaAún no hay calificaciones

- Informe Previo 2 - Electronicos IIDocumento13 páginasInforme Previo 2 - Electronicos IIAlexDanielAún no hay calificaciones

- Laboratorio 6 Informe ANALOGICA 2Documento24 páginasLaboratorio 6 Informe ANALOGICA 2PERA peraAún no hay calificaciones

- Proyecto Amplificador de Audio y VumetroDocumento18 páginasProyecto Amplificador de Audio y VumetroJosé Luis Poma100% (1)

- Lab 8 EA1Documento5 páginasLab 8 EA1Sergio RomeroAún no hay calificaciones

- INFORME PREVIO 3 TeoriaDocumento6 páginasINFORME PREVIO 3 TeoriaJanpier Franco Pizarro NonalayaAún no hay calificaciones

- Lab 2 de CE II - Ckto RC, RL Serie UltimDocumento20 páginasLab 2 de CE II - Ckto RC, RL Serie UltimGUSTAVO JESUS ANSELMO SUCAPUCAAún no hay calificaciones

- Dispositivos Lab2 PEREZDocumento8 páginasDispositivos Lab2 PEREZJoséPérezCamposAún no hay calificaciones

- S03.s5 - Amplif Diferencial 1Documento55 páginasS03.s5 - Amplif Diferencial 1davidAún no hay calificaciones

- "Año de La Unidad, La Paz y El Desarrollo": Universidad Nacional Del Centro Del PerúDocumento23 páginas"Año de La Unidad, La Paz y El Desarrollo": Universidad Nacional Del Centro Del Perúwilll reyyAún no hay calificaciones

- Informe Electronica II. Amplificadores DiferencialesDocumento19 páginasInforme Electronica II. Amplificadores DiferencialesJuan SotoAún no hay calificaciones

- Laboratorio Amplificador Con BJTDocumento14 páginasLaboratorio Amplificador Con BJTTextos de Ingenieria100% (6)

- Tarea 2 Lab de Electrónica II Isaias Primera v28177287Documento12 páginasTarea 2 Lab de Electrónica II Isaias Primera v28177287Gabriel PrimeraAún no hay calificaciones

- Practica #2Documento6 páginasPractica #2CrisTian VelepuchaAún no hay calificaciones

- Laboratorio N 5 Respuesta en Amplificadores Multietaapa en CascadaDocumento9 páginasLaboratorio N 5 Respuesta en Amplificadores Multietaapa en CascadaNico PerezAún no hay calificaciones

- Experiencia N°1 - Configuración en Casacada (Previo)Documento12 páginasExperiencia N°1 - Configuración en Casacada (Previo)luis piscoyaAún no hay calificaciones

- Pre reporte #1 grupo 1_RevisadoDocumento20 páginasPre reporte #1 grupo 1_RevisadogrgregAún no hay calificaciones

- Informe Amplificador BJTDocumento5 páginasInforme Amplificador BJTnanodan47Aún no hay calificaciones

- Transformador monofásico: Parámetros y regulaciónDocumento24 páginasTransformador monofásico: Parámetros y regulaciónHector LafuenteAún no hay calificaciones

- Amplificador diferencial: Características y aplicacionesDocumento9 páginasAmplificador diferencial: Características y aplicacionesLeonardo CabreraAún no hay calificaciones

- Pratica 4 DispositivosDocumento48 páginasPratica 4 DispositivosGARCIA SALINAS LUIS GERMANAún no hay calificaciones

- Laboratorio 10 Amplificador Realimentado, Configuración Derivación SerieDocumento12 páginasLaboratorio 10 Amplificador Realimentado, Configuración Derivación SerieJessica FernandezAún no hay calificaciones

- OsciladoresDocumento10 páginasOsciladoresJuan CarlosAún no hay calificaciones

- MOSFET AmplificadoresDocumento5 páginasMOSFET AmplificadoresDavid Santiago Daza QuirogaAún no hay calificaciones

- PROYECTOFINALDocumento17 páginasPROYECTOFINALGiancarlo PossumAún no hay calificaciones

- Transformadores 2 CorteDocumento10 páginasTransformadores 2 CorteGilberto AlvarezAún no hay calificaciones

- Informe N°3 - ANÁLISIS DE CA DE UN BJTDocumento8 páginasInforme N°3 - ANÁLISIS DE CA DE UN BJTOmar Ruiz Rodríguez100% (1)

- 7mo Informe Previo L. Analógicos 2017-2Documento6 páginas7mo Informe Previo L. Analógicos 2017-2Miguel Angel Pajuelo VillanuevaAún no hay calificaciones

- Practicas 1-12 Diseño Con Transistores - 23Documento30 páginasPracticas 1-12 Diseño Con Transistores - 23MarcoAún no hay calificaciones

- Informe 5Documento10 páginasInforme 5Cristian Aste PintoAún no hay calificaciones

- Mendoza Yale Benjamin Elias Simulaciones 2Documento22 páginasMendoza Yale Benjamin Elias Simulaciones 2mr banano tvAún no hay calificaciones

- 7.2 Regimen Transitorio RLCDocumento23 páginas7.2 Regimen Transitorio RLCRicardo Alcántara CamposAún no hay calificaciones

- Informe 6 DispoDocumento15 páginasInforme 6 Dispokarlita_pamelaAún no hay calificaciones

- Laboratorio 03Documento11 páginasLaboratorio 03Pool Nolasco RamirezAún no hay calificaciones

- Amplificador Emisor Comun PDFDocumento5 páginasAmplificador Emisor Comun PDFKevin Esleiter LeónAún no hay calificaciones

- Guía 7 Lab de Termohidráulica Aplicada PDFDocumento9 páginasGuía 7 Lab de Termohidráulica Aplicada PDFsanchezohxAún no hay calificaciones

- Practica 1 Circuitos SDocumento16 páginasPractica 1 Circuitos SMIGUEL ANGEL DIAZ INIGUEZAún no hay calificaciones

- Informe 1 Electronicos 2Documento6 páginasInforme 1 Electronicos 2FRANCO DANILO VERA TRUJILLOAún no hay calificaciones

- Polarización de Un Amplificador Monoetapa en Emisor Común: Punto de Funcionamiento, hFE y Hfe .Documento11 páginasPolarización de Un Amplificador Monoetapa en Emisor Común: Punto de Funcionamiento, hFE y Hfe .IsabelAún no hay calificaciones

- Previo 1Documento6 páginasPrevio 1Joel DitAún no hay calificaciones

- N 3Documento6 páginasN 3Juan Alexander100% (1)

- Amplifidor Retroalimentado Voltaje en SerieDocumento22 páginasAmplifidor Retroalimentado Voltaje en SerieErnesto Ezequiel Lamby DelgadoAún no hay calificaciones

- Amplificador Diferencial JFET and CompueDocumento12 páginasAmplificador Diferencial JFET and CompueEmily JulianaAún no hay calificaciones

- Amplificadores acoplados directa y capacitivamenteDocumento13 páginasAmplificadores acoplados directa y capacitivamenteLeo ZamoraAún no hay calificaciones

- UL Electrónica III Práctica 01Documento10 páginasUL Electrónica III Práctica 01Mafe SanchezAún no hay calificaciones

- Informe Calidad Energía Eléctrica ArmónicosDocumento19 páginasInforme Calidad Energía Eléctrica ArmónicosFabian Torres DuarteAún no hay calificaciones

- Amplificador emisor seguidor: medición de impedancia y gananciaDocumento6 páginasAmplificador emisor seguidor: medición de impedancia y gananciaCarlos JuradoAún no hay calificaciones

- Transistores en Bajas FrecuenciasDocumento19 páginasTransistores en Bajas Frecuenciasmoises labarcaAún no hay calificaciones

- Amplificadores Darlington, Cascodo y DiferencialDocumento12 páginasAmplificadores Darlington, Cascodo y DiferencialRoberto Rocca JuárezAún no hay calificaciones

- S06.s1Laboratorio 01amplificador de Simetria ComplementariaDocumento20 páginasS06.s1Laboratorio 01amplificador de Simetria ComplementariaDIEGO ESTEFANO PICHIHUA CARRERAAún no hay calificaciones

- Armónicas en Sistemas Eléctricos IndustrialesDe EverandArmónicas en Sistemas Eléctricos IndustrialesCalificación: 4.5 de 5 estrellas4.5/5 (12)

- Informe1 Maquinas Eléctricas3Documento7 páginasInforme1 Maquinas Eléctricas3PaulAún no hay calificaciones

- Informe 8Documento8 páginasInforme 8PaulAún no hay calificaciones

- Máquinas Eléctricas Informe 2 y 3Documento6 páginasMáquinas Eléctricas Informe 2 y 3PaulAún no hay calificaciones

- Semana 01 ElectrostaticDocumento35 páginasSemana 01 ElectrostaticPaulAún no hay calificaciones

- Previo 4Documento8 páginasPrevio 4PaulAún no hay calificaciones

- Circuito equivalente del transformador: Modelos y cálculo de parámetrosDocumento29 páginasCircuito equivalente del transformador: Modelos y cálculo de parámetrosPaulAún no hay calificaciones

- SssssDocumento1 páginaSssssPaulAún no hay calificaciones

- Lenguaje-SINONIMIA, ANTONIMIA, POLISEMIA, HOMONIMIA, PARONIMIADocumento1 páginaLenguaje-SINONIMIA, ANTONIMIA, POLISEMIA, HOMONIMIA, PARONIMIAPaulAún no hay calificaciones

- Trip TicoDocumento2 páginasTrip TicoPaulAún no hay calificaciones

- Electricos 2 FIEEDocumento11 páginasElectricos 2 FIEEPaulAún no hay calificaciones

- How To Use The FL Studio Mixer (Traducido Al Español)Documento12 páginasHow To Use The FL Studio Mixer (Traducido Al Español)TANA CULtUREAún no hay calificaciones

- LG 22le3320 PDFDocumento206 páginasLG 22le3320 PDFJuanjoAún no hay calificaciones

- Wireless Workshop 15-05-19Documento106 páginasWireless Workshop 15-05-19fmorocotoAún no hay calificaciones

- g0100-05 Sistema de Medicion de Energia Electrica Centralizada en GabineteDocumento43 páginasg0100-05 Sistema de Medicion de Energia Electrica Centralizada en GabineteCesar Augusto Morales Romero100% (1)

- Presentacion Actual Jvs ConsultoresDocumento4 páginasPresentacion Actual Jvs ConsultoresPablo Alejandro Salinas ZepedaAún no hay calificaciones

- Semaforo Con Moc y TriacDocumento13 páginasSemaforo Con Moc y TriacSantiago VillacresAún no hay calificaciones

- Protección de sistemas eléctricos de potencia y relés de sobrecorrienteDocumento55 páginasProtección de sistemas eléctricos de potencia y relés de sobrecorrienteFer LopezAún no hay calificaciones

- Practica 5 2-2021 ADocumento2 páginasPractica 5 2-2021 AMauricio PérezAún no hay calificaciones

- Laboratorio de Sistemas Electromecanicos 2Documento4 páginasLaboratorio de Sistemas Electromecanicos 2CRISTHIAN CAMILO ROA CALLEAún no hay calificaciones

- Graficas de Hardware para DibujarDocumento9 páginasGraficas de Hardware para DibujarFabiola Taracena33% (3)

- Manual Del FabricanteDocumento19 páginasManual Del Fabricanteedith hurtadoAún no hay calificaciones

- Medidor de Componentes SMDDocumento4 páginasMedidor de Componentes SMDAlbertoAún no hay calificaciones

- Tabla de EscalamientoDocumento5 páginasTabla de EscalamientoHiram Cmi BautistaAún no hay calificaciones

- Configurar Drive Simovert VCDocumento22 páginasConfigurar Drive Simovert VCDiego ArmandoAún no hay calificaciones

- Diplomado en Telecomunicaciones - Medios de TransmisiónDocumento33 páginasDiplomado en Telecomunicaciones - Medios de TransmisiónKatherin Angel DuqueAún no hay calificaciones

- LMSAT Manual EspaolDocumento18 páginasLMSAT Manual EspaolJose Luis Moran ChinchayAún no hay calificaciones

- Hardware - Wikipedia, La Enciclopedia LibreDocumento10 páginasHardware - Wikipedia, La Enciclopedia LibreKaaAún no hay calificaciones

- Módulo1Hardware RTN 905950A980Documento145 páginasMódulo1Hardware RTN 905950A980Jaime Garcia De ParedesAún no hay calificaciones

- Cap5 Pu18Documento29 páginasCap5 Pu18Sabrina RepettoAún no hay calificaciones

- Sistema de Incendio Eco FuturoDocumento6 páginasSistema de Incendio Eco FuturoPablo José Delgado CarrasquelAún no hay calificaciones

- Circuitos de Interconexión Entre Dos Arduinos Con Adaptadores 485 2Documento20 páginasCircuitos de Interconexión Entre Dos Arduinos Con Adaptadores 485 2Frank LeonAún no hay calificaciones

- Arquitectura Del ComputadorDocumento1 páginaArquitectura Del ComputadorJose MedinaAún no hay calificaciones

- Manual Central Piston NeoDocumento15 páginasManual Central Piston NeoOsmar Santillan100% (1)

- Competencias de Mecatronica AplicadaDocumento2 páginasCompetencias de Mecatronica AplicadanahumAún no hay calificaciones

- LAB N°02 Electrónica Analógica y DigitalDocumento15 páginasLAB N°02 Electrónica Analógica y DigitalWanderley Felix Lopez QuirozAún no hay calificaciones

- Medicion de Ruido Con OsciloscopioDocumento3 páginasMedicion de Ruido Con OsciloscopioLolo fernandezAún no hay calificaciones

- Redes de Cable Sub & Per1uDocumento43 páginasRedes de Cable Sub & Per1uMagda QsAún no hay calificaciones

- Manual LG DR165Documento50 páginasManual LG DR165ugiyfiulfyAún no hay calificaciones

- 1º El Registro de Prestadores de Servicios de Certificación DependeDocumento13 páginas1º El Registro de Prestadores de Servicios de Certificación DependeEdgar Tuco VillalobosAún no hay calificaciones

- Diac y DimmerDocumento13 páginasDiac y DimmerUlt DincyclistAún no hay calificaciones