Documentos de Académico

Documentos de Profesional

Documentos de Cultura

RT 21053112017

Cargado por

Raunaq0 calificaciones0% encontró este documento útil (0 votos)

35 vistas1 páginaYuuig hui

Título original

Rt 21053112017

Derechos de autor

© © All Rights Reserved

Formatos disponibles

PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoYuuig hui

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

35 vistas1 páginaRT 21053112017

Cargado por

RaunaqYuuig hui

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Está en la página 1de 1

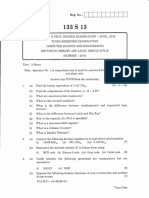

Code No: RT21053 R13 SET - 1

II B. Tech I Semester Supplementary Examinations, Oct/Nov- 2017

DIGITAL LOGIC DESIGN

(Com. to CSE, IT)

Time: 3 hours Max. Marks: 70

Note: 1. Question Paper consists of two parts (Part-A and Part-B)

2. Answer ALL the question in Part-A

3. Answer any THREE Questions from Part-B

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

PART –A

1. a) What are the advantages of 2’s complement? (3M)

b) Prove (3M)

c) Implement function using 2X1 MUX (4M)

d) Write the difference between combinational circuit and sequential circuit (4M)

e) Draw the 3 bit Ripple counter logical diagram (4M)

f) Write the difference between PLA and PAL (4M)

PART -B

2. a) Convert the following numbers to decimal. (10101001.0101)2 , (12020)3 , (8M)

(1023.2)4 , (40123)5 , (0.354)6 , (45)7 , (8.3)9 , (A10)12

b) Explain about Weighted and non-weighted codes (8M)

3. a) For the Boolean function (8M)

F = x z + z + xy + w y + wxy

(i) Obtain the truth table of F. (ii) Use Boolean algebra to simplify the function

to a minimum number of literals

b) Draw the multiple-level NAND circuit for the following expression: (8M)

w (x + y + z) + xyz

4. a) Explain about Ripple Adder/Subtractor using 2’s complement method (8M)

b) Design a 4 input priority encoder with input D0 having the highest priority and (8M)

D3 the lowest priority.

5. a) What are the limitations of JK flip flop? Explain how can eliminated those (8M)

limitations

b) Conversion of JK flip flop to SR flip flop (8M)

6. a) What is the difference between a serial and parallel transfer? Explain how to (8M)

convert serial data to parallel and parallel to serial.

b) Design a synchronous BCD counter with JK flip-flop (8M)

7. A Combinational circuit defined by functions (16M)

Implement circuit with PAL

1 of 1

WWW.MANARESULTS.CO.IN

|''|'''||''||'''||||

También podría gustarte

- RT 21053112016Documento4 páginasRT 21053112016RaunaqAún no hay calificaciones

- STLD Previous PapersDocumento24 páginasSTLD Previous PapersRaju Vericherla100% (1)

- WWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic DesignDocumento4 páginasWWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic Designbadiganti tejakrishnaAún no hay calificaciones

- 08AB303 - DIGITAL LOGIC CIRCUITSDocumento3 páginas08AB303 - DIGITAL LOGIC CIRCUITSChandru RamaswamyAún no hay calificaciones

- Computer Networks Exam QuestionsDocumento1 páginaComputer Networks Exam QuestionsMurali Krishna ChanapathiAún no hay calificaciones

- RT 22022042017Documento8 páginasRT 22022042017YasyrAún no hay calificaciones

- WWW - Manaresults.co - In: II B. Tech I Semester Supplementary Examinations, May - 2019 Switching Theory and Logic DesignDocumento2 páginasWWW - Manaresults.co - In: II B. Tech I Semester Supplementary Examinations, May - 2019 Switching Theory and Logic DesignismavrocksAún no hay calificaciones

- Computer Organization Exam QuestionsDocumento5 páginasComputer Organization Exam QuestionssanjuzebraAún no hay calificaciones

- Data Structures Question PaperDocumento2 páginasData Structures Question PaperPoojaAún no hay calificaciones

- 08AB303 DIGITAL LOGIC CIRCUITSDocumento4 páginas08AB303 DIGITAL LOGIC CIRCUITSChandru RamaswamyAún no hay calificaciones

- Btech Ec 3 Sem Digital Logic Design Nec 309 2016 17Documento4 páginasBtech Ec 3 Sem Digital Logic Design Nec 309 2016 17Vishesh Kumar SinghAún no hay calificaciones

- Code No: R1621042 - B. Tech I Semester Supplementary Exams October/November 2020Documento2 páginasCode No: R1621042 - B. Tech I Semester Supplementary Exams October/November 2020VEMANA DHANESHAún no hay calificaciones

- Switching Theory and Logic Design Exam QuestionsDocumento4 páginasSwitching Theory and Logic Design Exam QuestionsrangerAún no hay calificaciones

- Question Paper Code:: (10×2 20 Marks)Documento2 páginasQuestion Paper Code:: (10×2 20 Marks)kenny kannaAún no hay calificaciones

- VI Sem Jun-July 2005Documento10 páginasVI Sem Jun-July 2005Suraj KumarAún no hay calificaciones

- 2022 Dec. ECT203-CDocumento2 páginas2022 Dec. ECT203-CAthul RamAún no hay calificaciones

- Veermata Jijabai Technological Institute: End Semester Examination December 2018 SEM-I, First Year MCADocumento3 páginasVeermata Jijabai Technological Institute: End Semester Examination December 2018 SEM-I, First Year MCApradnya kingeAún no hay calificaciones

- 08AB303 DIGITAL LOGIC CIRCUITS_1Documento3 páginas08AB303 DIGITAL LOGIC CIRCUITS_1Chandru RamaswamyAún no hay calificaciones

- 9A04306 Digital Logic Design3Documento1 página9A04306 Digital Logic Design3Mahaboob SubahanAún no hay calificaciones

- Data Communication Exam QuestionsDocumento2 páginasData Communication Exam Questionsanon_914773339Aún no hay calificaciones

- BCA 5th Sem Dec 2019Documento10 páginasBCA 5th Sem Dec 2019lolol lololAún no hay calificaciones

- II B. Tech II Semester Supplementary Examinations, Dec - 2015 Advanced Data StructuresDocumento1 páginaII B. Tech II Semester Supplementary Examinations, Dec - 2015 Advanced Data StructuresChristina RobinsonAún no hay calificaciones

- Switching Theory and Logic DesignDocumento8 páginasSwitching Theory and Logic DesignVenkat ChadalavadaAún no hay calificaciones

- B.Tech II Year I Semester (R13) Regular & Supplementary Examinations December 2015Documento1 páginaB.Tech II Year I Semester (R13) Regular & Supplementary Examinations December 2015jayarami reddy pAún no hay calificaciones

- Advanced Data Structures2015Documento4 páginasAdvanced Data Structures2015Christina RobinsonAún no hay calificaciones

- 3330 MergedDocumento8 páginas3330 MergedHamit BisaneAún no hay calificaciones

- QBank DPSD cs2202Documento6 páginasQBank DPSD cs2202kunarajAún no hay calificaciones

- 07af303 - Digital Integrated Circuits and Logical DesignDocumento3 páginas07af303 - Digital Integrated Circuits and Logical DesignChandru RamaswamyAún no hay calificaciones

- Switching Theory and Logic Design - June-2015Documento55 páginasSwitching Theory and Logic Design - June-2015Rama HarithaAún no hay calificaciones

- Digital Electronics & Fundamentals of Microprocessor: B.E. (Information Technology) Third Semester (C.B.S.)Documento2 páginasDigital Electronics & Fundamentals of Microprocessor: B.E. (Information Technology) Third Semester (C.B.S.)Hamit BisaneAún no hay calificaciones

- 3 Hours / 70 Marks: Seat NoDocumento4 páginas3 Hours / 70 Marks: Seat No58 EX Ramawat PankajAún no hay calificaciones

- CS3CO29-EC-EI3CO07-IT3CO09-OE00005 Digital ElectronicsDocumento3 páginasCS3CO29-EC-EI3CO07-IT3CO09-OE00005 Digital Electronicschouhanraman822Aún no hay calificaciones

- Ii Ece B I SemDocumento52 páginasIi Ece B I SemElectronics & communication engineering AstcAún no hay calificaciones

- STLDDocumento2 páginasSTLDANUPAMA PonnuAún no hay calificaciones

- Advance Data Structure qp-16Documento4 páginasAdvance Data Structure qp-16Christina RobinsonAún no hay calificaciones

- Digital Logic Design Exam Questions and AnswersDocumento38 páginasDigital Logic Design Exam Questions and AnswersRajesh ViswanadhamAún no hay calificaciones

- Control Systems May 2017Documento7 páginasControl Systems May 2017Department of Electronics and Communication Engineering AKNUAún no hay calificaciones

- Campusexpress - Co.in: Set No. 1Documento8 páginasCampusexpress - Co.in: Set No. 1skssushAún no hay calificaciones

- B.Tech II Year I Semester (R13) Supplementary Examinations June 2017Documento2 páginasB.Tech II Year I Semester (R13) Supplementary Examinations June 2017Kareem KhanAún no hay calificaciones

- Digital Logic Design Exam QuestionsDocumento2 páginasDigital Logic Design Exam QuestionsKareem KhanAún no hay calificaciones

- 2011 Apr Cert CNTDocumento4 páginas2011 Apr Cert CNTmichaelmikealAún no hay calificaciones

- CS 801D PDFDocumento4 páginasCS 801D PDFarnab paulAún no hay calificaciones

- 07a50503 ComputergraphicsDocumento5 páginas07a50503 Computergraphics02871a0536Aún no hay calificaciones

- NR 410101 Computer Aided AnalysisDocumento8 páginasNR 410101 Computer Aided AnalysisSrinivasa Rao GAún no hay calificaciones

- Data Communication and Networking - Sem 8 - Elex - MUDocumento9 páginasData Communication and Networking - Sem 8 - Elex - MU111ashwinAún no hay calificaciones

- Ecs-301 Digital Logic Design 2010-11Documento4 páginasEcs-301 Digital Logic Design 2010-11Satyedra MauryaAún no hay calificaciones

- RT22055052016Documento4 páginasRT22055052016ksai.mbAún no hay calificaciones

- STLD PDFDocumento2 páginasSTLD PDFANUPAMA PonnuAún no hay calificaciones

- WWW - Manaresults.Co - In: (Common To CSE, IT)Documento2 páginasWWW - Manaresults.Co - In: (Common To CSE, IT)Suresh ThallapelliAún no hay calificaciones

- Ect203 Logic Circuit Design, December 2022Documento2 páginasEct203 Logic Circuit Design, December 2022ShakiraAún no hay calificaciones

- Computer Organization Nov 2020Documento1 páginaComputer Organization Nov 2020Sai BabaAún no hay calificaciones

- Ect203 Logic Circuit Design, December 2021Documento2 páginasEct203 Logic Circuit Design, December 2021instapc0210Aún no hay calificaciones

- CS QPDocumento9 páginasCS QPPankti PatelAún no hay calificaciones

- Nov 2017Documento1 páginaNov 2017ad599066Aún no hay calificaciones

- WWW - Manaresults.Co - In: Operations ResearchDocumento2 páginasWWW - Manaresults.Co - In: Operations ResearchDevaraj AstroAún no hay calificaciones

- WWW - Manaresults.Co - In: I B. Tech. II Semester Regular Examinations, April/May - 2017 Data StructuresDocumento4 páginasWWW - Manaresults.Co - In: I B. Tech. II Semester Regular Examinations, April/May - 2017 Data StructuresRavi KrishnaAún no hay calificaciones

- From Microstructure Investigations to Multiscale Modeling: Bridging the GapDe EverandFrom Microstructure Investigations to Multiscale Modeling: Bridging the GapDelphine BrancherieAún no hay calificaciones

- Evolutionary Algorithms for Mobile Ad Hoc NetworksDe EverandEvolutionary Algorithms for Mobile Ad Hoc NetworksAún no hay calificaciones

- Enterprise Monopsony Market Oligopoly Competition Good Service Substitute Goods Monopoly Price Marginal Cost Monopoly ProfitDocumento2 páginasEnterprise Monopsony Market Oligopoly Competition Good Service Substitute Goods Monopoly Price Marginal Cost Monopoly ProfitRaunaqAún no hay calificaciones

- Code 972412Documento3 páginasCode 972412Raunaq100% (1)

- Ui17ec16 MatlabcodesDocumento6 páginasUi17ec16 MatlabcodesRaunaqAún no hay calificaciones

- Text of YrDocumento1 páginaText of YrRaunaqAún no hay calificaciones

- Text OfyDocumento1 páginaText OfyRaunaqAún no hay calificaciones

- Docs/CSEOSLNotes2013 PDFDocumento119 páginasDocs/CSEOSLNotes2013 PDFRitesh AkhandeAún no hay calificaciones

- QuiDocumento3 páginasQuiRaunaqAún no hay calificaciones

- Text of YrDocumento1 páginaText of YrRaunaqAún no hay calificaciones

- QuickyDocumento2 páginasQuickyRaunaqAún no hay calificaciones

- Text OfyDocumento1 páginaText OfyRaunaqAún no hay calificaciones

- k7 KeyDocumento1 páginak7 KeyRaunaqAún no hay calificaciones

- Electronics Theory - Two-Port NetworksDocumento29 páginasElectronics Theory - Two-Port Networksilluminatissm100% (3)

- JEE Main 2018 Question Paper Code A PDFDocumento19 páginasJEE Main 2018 Question Paper Code A PDFRaunaqAún no hay calificaciones

- JEE Main 2018 Question Paper Code A PDFDocumento19 páginasJEE Main 2018 Question Paper Code A PDFRaunaqAún no hay calificaciones

- Release Notes: Confidential and Proprietary InformationDocumento6 páginasRelease Notes: Confidential and Proprietary InformationRaunaqAún no hay calificaciones

- New Microsoft Word DocumentDocumento2 páginasNew Microsoft Word DocumentRaunaqAún no hay calificaciones

- ProbingDocumento2 páginasProbingRaunaqAún no hay calificaciones

- RavenDocumento1 páginaRavenRaunaqAún no hay calificaciones

- Head 1Documento2 páginasHead 1RaunaqAún no hay calificaciones

- PHP Assignment 1Documento2 páginasPHP Assignment 1Raunaq100% (1)

- Content at MeDocumento1 páginaContent at MeRaunaqAún no hay calificaciones

- Notes On Digital ElectronicsDocumento72 páginasNotes On Digital ElectronicsMaheshAún no hay calificaciones

- Logical operators and propositions in mathematicsDocumento112 páginasLogical operators and propositions in mathematicsZyrelle AgullanaAún no hay calificaciones

- 128x8 ROM from 4 32x8 ROMs with decoderDocumento3 páginas128x8 ROM from 4 32x8 ROMs with decodervinod3457Aún no hay calificaciones

- Number System ProjectDocumento9 páginasNumber System ProjectJohn NgwokeAún no hay calificaciones

- AddersDocumento5 páginasAddersShanuj GargAún no hay calificaciones

- Submitted by Mehtab Qasim Roll # 49345 Submitted To Sir - Shahzad Rana Subject DLD GCUF Community CollegeDocumento13 páginasSubmitted by Mehtab Qasim Roll # 49345 Submitted To Sir - Shahzad Rana Subject DLD GCUF Community CollegeRaja Muhammad Talha BhattiAún no hay calificaciones

- Digital Electronics Lab ManualDocumento108 páginasDigital Electronics Lab Manualkunaraj88% (17)

- Digital Logic Fundamentals ExplainedDocumento24 páginasDigital Logic Fundamentals ExplainedTrần Thái SơnAún no hay calificaciones

- Digital Circuits and DesignDocumento72 páginasDigital Circuits and DesigntonyAún no hay calificaciones

- Verilog Operators GuideDocumento4 páginasVerilog Operators GuideECE TheivanayakiAún no hay calificaciones

- PFC Workshop 01 Co Dap AnDocumento4 páginasPFC Workshop 01 Co Dap Antrương nhuAún no hay calificaciones

- Karnaugh Map - Don't Care Conditions - Tabulation Method: Simplification TechniquesDocumento31 páginasKarnaugh Map - Don't Care Conditions - Tabulation Method: Simplification TechniquesMithun GoudaAún no hay calificaciones

- Introduction To Gates AssignmentDocumento6 páginasIntroduction To Gates AssignmentyasintharaAún no hay calificaciones

- CMSC250 Discrete Math Circuits PDFDocumento18 páginasCMSC250 Discrete Math Circuits PDFakeller680Aún no hay calificaciones

- Pertemuan I. Sistem DigitalDocumento6 páginasPertemuan I. Sistem DigitalEddy PurwokoAún no hay calificaciones

- Number SystemsDocumento36 páginasNumber SystemsIsrael EliasAún no hay calificaciones

- Bits Pilani: Digital Systems (Combinational Circuit) Rktiwary ManoDocumento39 páginasBits Pilani: Digital Systems (Combinational Circuit) Rktiwary Manorktiwary256034Aún no hay calificaciones

- CH10-COA10e - Computer Arithmetic PDFDocumento56 páginasCH10-COA10e - Computer Arithmetic PDFNILUH PUTU VANIA DYAH SARASWATIAún no hay calificaciones

- Digital Logic Design: Assignment 1 Due Date: 10.12.2020 (Thursday)Documento3 páginasDigital Logic Design: Assignment 1 Due Date: 10.12.2020 (Thursday)muktikantaAún no hay calificaciones

- Question 1 (20 Points) : Answer 1) .............. Answer 2) .............Documento6 páginasQuestion 1 (20 Points) : Answer 1) .............. Answer 2) .............Amin DhouibAún no hay calificaciones

- CSC 214 Digital DesignDocumento22 páginasCSC 214 Digital Designfaliciahassan3100% (1)

- (Up, Down and Modn) CountersDocumento76 páginas(Up, Down and Modn) CountersAashik ShaikAún no hay calificaciones

- 8 PLC Program To Implement ExcessDocumento5 páginas8 PLC Program To Implement ExcessMaria GuerreroAún no hay calificaciones

- Logic Connectives Negation Conditional BiconditionalDocumento14 páginasLogic Connectives Negation Conditional BiconditionalSiti mukaromahAún no hay calificaciones

- Lecture 13 - Conditionals and Iteration - 5301Documento20 páginasLecture 13 - Conditionals and Iteration - 5301leo7075375118Aún no hay calificaciones

- DLD 2nd Chapter KeyDocumento15 páginasDLD 2nd Chapter KeyAnnas AfzalAún no hay calificaciones

- Digital Principles UNIT 1 FinalDocumento86 páginasDigital Principles UNIT 1 FinalSathish Kumar0% (1)

- Dpco Lab ManualDocumento53 páginasDpco Lab ManualBELMER GLADSON Asst. Prof. (CSE)Aún no hay calificaciones

- Logic Sheet 1 AnswersDocumento9 páginasLogic Sheet 1 AnswersAhmedGamalAún no hay calificaciones

- Computer Number SystemDocumento67 páginasComputer Number Systemdemise201_728142800Aún no hay calificaciones