Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Practica 11 Sintesis Tarjeta FPGA

Cargado por

Niza VidalDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Practica 11 Sintesis Tarjeta FPGA

Cargado por

Niza VidalCopyright:

Formatos disponibles

Práctica 11

Instituto Tecnológico de Lerma

Ingeniería Electrónica

ASIGNATURA:

DISEÑO DIGITAL CON VHDL

PRÁCTICA No. 11

“SINTESIS DE UN CIRCUITO EN UNA TARJETA CPLD o FPGA”

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 1

Práctica 11

1.1 INTRODUCCIÓN.

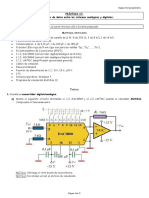

1.1.1 Dispositivos lógicos programables de alto nivel de integración

Los PLD de alto nivel de integración se crearon con el objeto de integrar mayor cantidad

de dispositivos en un circuito (sistema en un chip SOC). Se caracterizan por la reducción de

espacio y costo, además de ofrecer una mejora sustancial en el diseño de sistemas

complejos, dado que incrementa la velocidad y las frecuencias de operación.

1.1.2 Dispositivos lógicos programables (CPLD)

Un circuito CPLD consiste en un arreglo de múltiples PLD agrupados como bloques en un

chip. También a estos dispositivos se le conoces con EPLD (Enhanced PLD: PLD mejorado),

Súper PAL, Mega PAL, etc. Se califican como de alto nivel de integración, ya que tienen

una gran capacidad equivalente a unos 50 PLD.

En su estructura básica, cada CPLD contiene múltiples bloques lógicos (similares al

GAL22V10) conectados por medio de señales canalizadas desde la interconexión

programable (PI). Esta unidad PI se encarga de interconectar los bloques lógicos y los

bloques de entrada/salida del dispositivo sobre las redes apropiadas (Fig. 11.1).

Figura 11.1 Arquitectura básica de un CPLD

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 2

Práctica 11

1.2. COMPETENCIAS A DESARROLLAR.

• El estudiante será capaz de Programar y comparar el funcionamiento de un circuito

combinacional, en una tarjeta FPGA (o CPLD) de acuerdo con las especificaciones

técnicas del fabricante.

1.3 DESCRIPCIÓN DE LAS TARJETAS FPGA (O CPLD).

1.3.1 Descripción de la tarjeta MAX II (ALTERA).

Figura 1.2 Aspecto físico de la tarjeta con el USB Blaster

Especificaciones:

Modelo LC Soft CPLD EPM240T100C5N Junta de Desarrollo Mini

CPLD EPM240T100C5N

Voltaje de entrada DC 5V

JTAG Pines 5X2;

Puerto Con Byte-Blaster/USB Blaster

Circuito de rearme Con botón de reinicio

Pines IO Todos los pines de CPLD son disponibles

Crystal 8 MHz

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 3

Práctica 11

1.3.2 Descripción de la tarjeta MachXO3 Starter Kit (Lattice semiconductor).

Especificaciones:

• Tarjeta MachXO3L/LF es una tarjeta de 3” x 3”

— MachXO3 FPGA – LCMXO3L-6900C-5BG256C (NVCM Based) or LCMXO3LF-6900C-

5BG256C (Flash Based)

— USB mini-B connector for power and programming

— 4-Mb Serial Flash Memory for boot image and dual-boot support.

— Eight LEDs

— 4-position DIP switch

— Momentary push button switch

— 40-hole prototype area

— Four 2 x 20 expansion header landings for general I/O, JTAG, and external power

— 1 x 8 expansion header landing for JTAG

— 1 x 6 expansion header landing for SPI/I2C

— 3.3 V and 1.2 V supply rails

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 4

Práctica 11

1.4 MATERIAL Y EQUIPO.

MATERIAL

A). EPM240 Miniboard o MachXO3L/LF

B). Programador Altera USB Blaster (solo si se utiliza Altera)

C). Protoboard

D). Cables dupont, hembra-macho, macho-macho

E). 2 Leds

F). Resistencias

G). Push Botón

F). Fuente de corriente directa (12 V)

1.5 Procedimiento

1.5.1 Procedimiento para utilizar la tarjeta de Altera

1) Iniciar un nuevo proyecto en Quartus II.

Figura 11.3 Creación de un nuevo proyecto

2) Una vez que especificaron el nombre, la ubicación de su proyecto y sigan los pasos

correspondientes hasta llegar a la siguiente ventana:

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 5

Práctica 11

Figura 11.4 Selección de tarjeta

Se muestra la ventana para seleccionar la tarjeta a utilizar, y el modelo del CPLD, que es

específicamente el que se muestra en azul.

Cuando ya se hace la selección se le da Next.

3) Y como solo estamos utilizando una sola herramienta, en esta ventana damos Next.

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 6

Práctica 11

Figura 11.5

4) Finish.

Figura 11.6

5) La presente práctica es elaborar un programa en VHDL y sintetizar un circuito

correspondiente en la tarjeta MAX II.

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 7

Práctica 11

Entonces se debe crear un nuevo proyecto. Como queremos ilustrar el método de ingreso

esquemático, elegimos la opción Block Diagram/Schematic y hacemos clic en OK.

Figura 11.7 Elección de tipo de archivo de diseño.

Inmediatamente la ventana para crear el circuito se abre.

6) El circuito a crear es el siguiente:

Figura 11.8 Circuito para la Captura esquemática

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 8

Práctica 11

A continuación se evalúa el circuito, de manera que se tendrá que obtener la tabla de

verdad correspondiente.

Z Y X F1 F2

0 0 0 0 1

0 0 1 0 0

0 1 0 0 1

0 1 1 1 1

1 0 0 1 0

1 0 1 1 0

1 1 0 0 0

1 1 1 1 1

Se asigna las variables al esquema, las entradas y las salidas. A partir de dicha asignación

se realiza el proceso de análisis y síntesis.

7) Asignación de pines

Assignments |Pins

La siguiente ventana se muestra el recuadro donde aparecen las variables, entradas y las

salidas del esquema, para asignárselo a la CPLD.

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 9

Práctica 11

Figura 11.9

8) Después de la asignación de pines, compila el programa.

9) Es momento de armar físicamente el circuito, teniendo la descripción del arreglo de

compuertas, y su respectivo esquemático en Quartus ll. Conectando las entradas y salidas

en la tarjeta MAX ll. Como se muestra en la figura 6.10

CONFIGURACIÓN DE LOS PINES A LA PROTOBOARD

Recuerde que la tarjeta debe ser alimentada externamente y la protoboard también. En la

siguiente figura podemos apreciar que la tarjeta MAX II indica cómo van en los pines,

donde se alimenta y que pines van a tierra.

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 10

Práctica 11

USB blaster

9-12 V dc

Figura 11.10

CONEXIÓN DE LA TARJETA A LA PC

1) Conectar el USB Blaster, directamente a la tarjeta y a la PC.

2) También es necesario alimentar la tarjeta con una fuente CD de 9 a 12 v.

Cuando se hagan los dos pasos anteriores.

3) Diríjase a la barra de menú, tools/pragrammer.

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 11

Práctica 11

Figura 11.11

4) Selecciona la opción Hardware Setup... De inmediato se mostrará el recuadro, la fig.

6.12. Ahí mismo, en Currently selected hardware, seleccione USB blaster 0,

close.

Figura 11.12

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 12

Práctica 11

5) Seleccione la columna de program/configure, los archivos del programa a descargar.

Figura 11.13

6) A continuación vaya a la barra de menú del recuadro de la fig. 6.14 y de clic en

Processing/JTAG Chain Debugger, se mostrará una nueva ventana con respecto a la

configuración del USB blaster.

Figura 11.14

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 13

Práctica 11

Figura 11.15

7) En el recuadro de la fig. 6.15, de clic en Test JTAG Chain y luego de clic en Start, el cual

es donde se detecta la tarjeta. Cerramos la ventana.

Figura 11.16

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 14

Práctica 11

8) Una vez programada la GAL, comprueba la salida del circuito con respecto a la tabla de

verdad que en un inicio hallaste. Anota los resultados.

1. 5.2 Procedimiento para utilizar la tarjeta Lattice

1) Para utilizar la tarjeta MachX03LF Starter Kit del fabricante Lattice, se deberá de

emplear la información técnica disponible del fabricante y la que proporciona el docente

titular de la materia, para todo el procedimiento de síntesis y programación de la tarjeta.

2) El circuito a programar en esta tarjeta es el mismo que se utilizó en el caso del uso de la

tarjeta de Altera, mismo que se presenta a continuación.

Figura 11.7 “Circuito a programar en la tarjeta MachX03LF Starter Kit

Ing. Fernando A. Escalante Guerrero Diseño Digital con VHDL 15

También podría gustarte

- Guia 2Documento26 páginasGuia 2Kenide ArroyoAún no hay calificaciones

- Info6 PDFDocumento9 páginasInfo6 PDFPEDRO DAVID PESANTEZ PESANTEZAún no hay calificaciones

- Práctica 7 Electrónica Digital IIDocumento3 páginasPráctica 7 Electrónica Digital IIOctavio MontoyaAún no hay calificaciones

- Práctica Introducción A Los PLDDocumento15 páginasPráctica Introducción A Los PLDAlex RMAún no hay calificaciones

- FPGA Cyclone II guíaDocumento28 páginasFPGA Cyclone II guíaPedro LandaetaAún no hay calificaciones

- Display de 7 SegmentosDocumento9 páginasDisplay de 7 SegmentosLuis PeñaAún no hay calificaciones

- prac2XilinxISEsumrest PDFDocumento19 páginasprac2XilinxISEsumrest PDFOliver Cruz AranibarAún no hay calificaciones

- Práctica 1 - Circuito Combinacional en VHDLDocumento13 páginasPráctica 1 - Circuito Combinacional en VHDLAlvaro LCAún no hay calificaciones

- Practica 1 Xilinix Ise Design2019bDocumento11 páginasPractica 1 Xilinix Ise Design2019bJaime GarciaAún no hay calificaciones

- Práctica 1Documento5 páginasPráctica 1Jorge Miguel Barajas BustamanteAún no hay calificaciones

- Taco MetroDocumento25 páginasTaco MetrofernndaAún no hay calificaciones

- Practica 3 Micro DisplayDocumento12 páginasPractica 3 Micro DisplaySergio Abraham Trejo PerezAún no hay calificaciones

- Dmpa Once.Documento10 páginasDmpa Once.CRIS ERIK ARISTE MANRIQUEAún no hay calificaciones

- Grupo 9Documento9 páginasGrupo 9Joseph Games YTAún no hay calificaciones

- Practica 05 - Introduccion A La Programacion de FPGAsDocumento6 páginasPractica 05 - Introduccion A La Programacion de FPGAsJoel AmezquitaAún no hay calificaciones

- Guia # 1Documento31 páginasGuia # 1Rigoberto AmayaAún no hay calificaciones

- Practica 1.2Documento9 páginasPractica 1.2yoqsanAún no hay calificaciones

- Manual Completo de CPLDDocumento24 páginasManual Completo de CPLDEvelyn MoranAún no hay calificaciones

- Tarjeta Adquisicion de DatosDocumento20 páginasTarjeta Adquisicion de DatosJorge LoboAún no hay calificaciones

- Guia 1 SDI215Documento20 páginasGuia 1 SDI215joel.arnoldolopezAún no hay calificaciones

- UNIDAD ARITMETICO LOGICA Con VHDLDocumento6 páginasUNIDAD ARITMETICO LOGICA Con VHDLAldo Vergara RAún no hay calificaciones

- CD PR11 DecodificadoresDocumento15 páginasCD PR11 DecodificadoresSamuel Larrinaga MoranAún no hay calificaciones

- Reductor de Frecuencia PDFDocumento8 páginasReductor de Frecuencia PDFAlejandro AlvarezAún no hay calificaciones

- Informe 3 Módulos LCDDocumento15 páginasInforme 3 Módulos LCDJhon LozadaAún no hay calificaciones

- Cargador Universal de Pics y Memorias EepromDocumento5 páginasCargador Universal de Pics y Memorias EepromMarcos STAún no hay calificaciones

- Implementación en Baysys 3Documento8 páginasImplementación en Baysys 3Pedro Jose Diaz RojasAún no hay calificaciones

- Informe de Laboratorio 1Documento6 páginasInforme de Laboratorio 1Andres SuarezAún no hay calificaciones

- Laboratorio de Electrónica IiDocumento15 páginasLaboratorio de Electrónica IiLeonardoAún no hay calificaciones

- Universidad Autónoma Metropolitana: Práctica #5Documento12 páginasUniversidad Autónoma Metropolitana: Práctica #5Cira NietoAún no hay calificaciones

- Term o MetroDocumento24 páginasTerm o MetrorichardAún no hay calificaciones

- Práctica 17. Convertidores DA y ADDocumento3 páginasPráctica 17. Convertidores DA y ADE&GAún no hay calificaciones

- Informe Robo y MicroDocumento17 páginasInforme Robo y MicrojefersonAún no hay calificaciones

- Implementa circuitos con LCDDocumento7 páginasImplementa circuitos con LCDANGEL “ANGELspaceX” lopezAún no hay calificaciones

- Pract Lab Ardu v2Documento77 páginasPract Lab Ardu v2Juan GomezAún no hay calificaciones

- Diseño de Sistemas Electrónicos Digitales Avanzados: Ángel GrediagaDocumento37 páginasDiseño de Sistemas Electrónicos Digitales Avanzados: Ángel GrediagaHi HiutoAún no hay calificaciones

- Tarea 4 Circuitos Secuenciales - 243004 - 32. Yuly - Figueredo.Documento22 páginasTarea 4 Circuitos Secuenciales - 243004 - 32. Yuly - Figueredo.MiGue DAzaAún no hay calificaciones

- Conver de Cod BCD A 7 SegDocumento18 páginasConver de Cod BCD A 7 SegPedro LandaetaAún no hay calificaciones

- Practica 01 - Introduccion A La Compuertas LogicasDocumento4 páginasPractica 01 - Introduccion A La Compuertas LogicasPaul Arturo Marmol RodriguezAún no hay calificaciones

- Implementación lógica compuertas FPGADocumento6 páginasImplementación lógica compuertas FPGAJose Luis Erazo DuranAún no hay calificaciones

- L10 FpgaDocumento23 páginasL10 FpgaGonzalo PereyraAún no hay calificaciones

- Informe de PicDocumento18 páginasInforme de PicWilder Carrasco MolleAún no hay calificaciones

- Practica 1 - MMDocumento11 páginasPractica 1 - MMNúñez Esparza Jesús ArturoAún no hay calificaciones

- Guia 1 para Sistemas Digitales de La UESDocumento20 páginasGuia 1 para Sistemas Digitales de La UESEduardo100% (1)

- Programación de PLD Con WincuplDocumento14 páginasProgramación de PLD Con Wincuplsergio jimenezAún no hay calificaciones

- Microcontroladores PIC Parte 3Documento70 páginasMicrocontroladores PIC Parte 3number2013Aún no hay calificaciones

- Práctica 9. Diseño e Implementación de Un Semáforo Con Elementos MSIDocumento3 páginasPráctica 9. Diseño e Implementación de Un Semáforo Con Elementos MSIE&GAún no hay calificaciones

- Guía didáctica de aprendizaje para el desarrollo de aplicaciones con microcontroladores PIC de 8 bits usando la plataforma PIC DISCOVERYDocumento82 páginasGuía didáctica de aprendizaje para el desarrollo de aplicaciones con microcontroladores PIC de 8 bits usando la plataforma PIC DISCOVERYgermanAún no hay calificaciones

- P1 AMN LMyM Gpo.2Documento10 páginasP1 AMN LMyM Gpo.2Nestor AriasAún no hay calificaciones

- Programación Arduino C LEDDocumento31 páginasProgramación Arduino C LEDAlfredo Valladares100% (1)

- ALTIUMDocumento5 páginasALTIUMSergio VeraAún no hay calificaciones

- Netduino 111106222316 Phpapp01Documento31 páginasNetduino 111106222316 Phpapp01Rodrigo OrellanaAún no hay calificaciones

- SED P6 EnunciadoDocumento10 páginasSED P6 Enunciadocarlos condeAún no hay calificaciones

- Relog DigitalDocumento10 páginasRelog DigitalRafael TecaxcoAún no hay calificaciones

- Quartus IIDocumento20 páginasQuartus IIedcAún no hay calificaciones

- Práctica 1. Laboratorio de Control y Robótica. Isaac Villamares QuirozDocumento14 páginasPráctica 1. Laboratorio de Control y Robótica. Isaac Villamares QuirozIsaac VillamaresAún no hay calificaciones

- Practica No 5 LAB PIC18F MPLABX 2019Documento5 páginasPractica No 5 LAB PIC18F MPLABX 2019Ader Hariel Treminio MontoyaAún no hay calificaciones

- Trabajo IndividualDocumento9 páginasTrabajo IndividualAxelAún no hay calificaciones

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- Compilador C CCS y Simulador Proteus para Microcontroladores PICDe EverandCompilador C CCS y Simulador Proteus para Microcontroladores PICCalificación: 2.5 de 5 estrellas2.5/5 (5)

- Manual Básico Hidraulica Festo PDFDocumento46 páginasManual Básico Hidraulica Festo PDFVicente Manuel Angulo Gutiérrez69% (13)

- Valvulas HidraulicasDocumento27 páginasValvulas HidraulicasJaime EspinozaAún no hay calificaciones

- 3 PDFDocumento24 páginas3 PDFRaphael Ruiz RamosAún no hay calificaciones

- Tipo de InvestigaciónDocumento2 páginasTipo de InvestigaciónNiza VidalAún no hay calificaciones

- Las Redes de Quinta GeneraciónDocumento5 páginasLas Redes de Quinta GeneraciónNiza VidalAún no hay calificaciones

- Brochure Hidraulica NavalDocumento20 páginasBrochure Hidraulica NavalNiza VidalAún no hay calificaciones

- Manual Sistemas Combustible Motores Electronicos CaterpillarDocumento73 páginasManual Sistemas Combustible Motores Electronicos CaterpillarRichar HoypensarasenmiAún no hay calificaciones

- FichasDocumento4 páginasFichasNiza VidalAún no hay calificaciones

- ET - Cat Electronic Technician - Manual Del Usuario - EF - CATERPILLARDocumento82 páginasET - Cat Electronic Technician - Manual Del Usuario - EF - CATERPILLARpevare91% (82)

- Instrumentos para La Recoleccion de DatosDocumento8 páginasInstrumentos para La Recoleccion de DatosNiza VidalAún no hay calificaciones

- Fichas de Trabajo y BibliográficasDocumento5 páginasFichas de Trabajo y BibliográficasNiza VidalAún no hay calificaciones

- Ingredientes para pastel de Navidad 18cmDocumento2 páginasIngredientes para pastel de Navidad 18cmNiza VidalAún no hay calificaciones

- ITL-AC-PO-008-09 FORMATO Reporte de Evaluacion Final de R PDocumento2 páginasITL-AC-PO-008-09 FORMATO Reporte de Evaluacion Final de R PNiza VidalAún no hay calificaciones

- Ingredientes para pastel de Navidad 18cmDocumento2 páginasIngredientes para pastel de Navidad 18cmNiza VidalAún no hay calificaciones

- Prueba Módulo 2 Tema 1Documento3 páginasPrueba Módulo 2 Tema 1Niza VidalAún no hay calificaciones

- Informe Practica 1 SensorDocumento5 páginasInforme Practica 1 SensorNiza VidalAún no hay calificaciones

- Rectificador Monofásico ControladoDocumento3 páginasRectificador Monofásico ControladoNiza VidalAún no hay calificaciones

- Ejercicios Examen MatemáticasDocumento7 páginasEjercicios Examen MatemáticasNiza VidalAún no hay calificaciones

- Compen Sad orDocumento9 páginasCompen Sad orNiza VidalAún no hay calificaciones

- Prueba Módulo 1 Tema 1Documento2 páginasPrueba Módulo 1 Tema 1JC RTAún no hay calificaciones

- Itl-Ac-po-008-08 Formato de Evaluacion y Seguimiento R PDocumento3 páginasItl-Ac-po-008-08 Formato de Evaluacion y Seguimiento R PNiza VidalAún no hay calificaciones

- Ejercicios Examen MatemáticasDocumento7 páginasEjercicios Examen MatemáticasNiza VidalAún no hay calificaciones

- ITL-AC-PO-008-09 FORMATO Reporte de Evaluacion Final de R PDocumento2 páginasITL-AC-PO-008-09 FORMATO Reporte de Evaluacion Final de R PNiza VidalAún no hay calificaciones

- Esta Di SticaDocumento16 páginasEsta Di SticaNiza VidalAún no hay calificaciones

- Itl-Ac-Po-008-06 Estructura Del Proyecto2015Documento3 páginasItl-Ac-Po-008-06 Estructura Del Proyecto2015Niza VidalAún no hay calificaciones

- ActuadoresDocumento16 páginasActuadoresNiza VidalAún no hay calificaciones

- ANEXO XXVIII Estructura Del Reporte Final R PDocumento1 páginaANEXO XXVIII Estructura Del Reporte Final R PNiza VidalAún no hay calificaciones

- Tarea Analisis de Sistemas de Control Nivel e IntrusionDocumento4 páginasTarea Analisis de Sistemas de Control Nivel e IntrusionNiza VidalAún no hay calificaciones

- Informe Practica 1 SensorDocumento5 páginasInforme Practica 1 SensorNiza VidalAún no hay calificaciones

- Control 1Documento3 páginasControl 1Niza VidalAún no hay calificaciones

- Que Es HardwareDocumento19 páginasQue Es HardwareBenjamin Santos Salinas100% (1)

- FSM AsmDocumento46 páginasFSM AsmFernando GuiraudAún no hay calificaciones

- Preinforme 3Documento12 páginasPreinforme 3Wilmer OscoAún no hay calificaciones

- ForoDocumento2 páginasForoJefry MateusAún no hay calificaciones

- Lista de Precios BG-1Documento2 páginasLista de Precios BG-1Isac MartinezAún no hay calificaciones

- S04 S1-MaterialDocumento34 páginasS04 S1-MaterialJohn Zegarra OlanoAún no hay calificaciones

- GersoDocumento11 páginasGersoramiro1ecvictorlevanAún no hay calificaciones

- NotasCompletas Sobre FpgaDocumento172 páginasNotasCompletas Sobre FpgaAntonio Melendez100% (1)

- 5.3 Factores de Calidad (Atributos de Calidad Externos e Internos)Documento4 páginas5.3 Factores de Calidad (Atributos de Calidad Externos e Internos)amayasamuel04Aún no hay calificaciones

- Sonicwall InformationDocumento6 páginasSonicwall InformationGorka ValeroAún no hay calificaciones

- Diseño de circuitos lógicos combinacionales para control de memoria RAM de 32x32 bits en LogisimDocumento11 páginasDiseño de circuitos lógicos combinacionales para control de memoria RAM de 32x32 bits en LogisimWilmer Vasquez0% (1)

- Ejemplo de Clases en C++Documento10 páginasEjemplo de Clases en C++ruperana100% (12)

- Taller 1 Digitales IiDocumento5 páginasTaller 1 Digitales IiKelly GomezxdedAún no hay calificaciones

- ReelesDocumento5 páginasReelesChristopher EnriquezAún no hay calificaciones

- Selección Mezclador Audio Banda MúsicaDocumento3 páginasSelección Mezclador Audio Banda MúsicaVictor Alvarez LopezAún no hay calificaciones

- Qu Es IPCopDocumento14 páginasQu Es IPCopclandestino_co9723Aún no hay calificaciones

- Capa de Red: Introducción Al Enrutamiento Interno de AS en Internet OSPF (Open Shortest Path First)Documento16 páginasCapa de Red: Introducción Al Enrutamiento Interno de AS en Internet OSPF (Open Shortest Path First)xX-CROMA69-XxAún no hay calificaciones

- 1°proyecto - 1ros Semana 5Documento18 páginas1°proyecto - 1ros Semana 5Jairo GuanotoaAún no hay calificaciones

- Redes de computadoras: Conectando dispositivos en una LAN domésticaDocumento7 páginasRedes de computadoras: Conectando dispositivos en una LAN domésticaGary MirandaAún no hay calificaciones

- Microsoft 365Documento2 páginasMicrosoft 365michael LeonAún no hay calificaciones

- Arquitectura de RedesDocumento60 páginasArquitectura de Redesvincen16.vaAún no hay calificaciones

- 12 Reglas Estructura DatosDocumento4 páginas12 Reglas Estructura DatosIvan Edgar BeniqueAún no hay calificaciones

- Manual de instrucciones HD TV 42 PlasmaDocumento40 páginasManual de instrucciones HD TV 42 PlasmachoneroAún no hay calificaciones

- Herencia PDFDocumento15 páginasHerencia PDFBrianAún no hay calificaciones

- Manual de Operaciones Basicas en AS400Documento25 páginasManual de Operaciones Basicas en AS400Cristian Valle RoncerosAún no hay calificaciones

- Mapa Conceptual - GA1-220501046-AA1-EV01Documento1 páginaMapa Conceptual - GA1-220501046-AA1-EV01Ana MariaAún no hay calificaciones

- Examen Final-Opcion BDocumento5 páginasExamen Final-Opcion BKevin LlanosAún no hay calificaciones

- 2.1.3.10 Lab - Install The Motherboard in A ComputerDocumento11 páginas2.1.3.10 Lab - Install The Motherboard in A ComputerJuan Sebastian Soto Moreno100% (1)

- Cómo funciona un pendrive: Guía completaDocumento13 páginasCómo funciona un pendrive: Guía completaNilda Jose Martinez VasquezAún no hay calificaciones

- Pro Mark 2Documento2 páginasPro Mark 2Gerardo Lopez Zamora100% (1)