Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Ac 1 U2 Resumen Cauich

Cargado por

Oscar CauichTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Ac 1 U2 Resumen Cauich

Cargado por

Oscar CauichCopyright:

Formatos disponibles

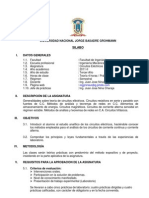

Instituto Tecnolgico Superior Progreso

Ingeniera en Sistemas Computacionales

SEMESTRE:

Quinto

MATERIA:

ARQUITECTURA DE COMPUTADORAS

TRABAJO:

Resumen

PROFESOR:

EDGAR ALEJANDRO SAGUNDO DUARTE

PRESENTA:

Cauich Pech Oscar Silvino

MATRICULA:

04162321

CORREO ELECTRNICO:

oscarkorg@gmail.com

CORREO ELECTRNICO:

FECHA DE ENTREGA:

PROGRESO, YUCATN, MXICO A 18 SEPTIEMBRE DEL 2017

Resumen

Los registros del CPU son el nivel superior de la jerarqua de memoria, no se puede acceder tan

fcilmente, se divide en 2 tipos de registros, no es accesible para el programador as nada ms, las

arquitecturas proporcionaran los conjuntos de restricciones, hay registros de uso general, se

pueden utilizar para almacenar nicamente datos, se les impone restricciones, hay registros

especializados, si hay un numero grande codifica mas y un numero menor de registros atrae

problemas para el programador y la memoria, hay procesadores como los RISC con un gran

numero de registros, los PC contienen la direccin de la instruccin, los IR la instruccin, las MAR

la ubicacin de memoria, las MBR guarda los datos, las psw las condiciones, hay tcnicas para las

instrucciones para superponer varias entre si en su ejecucin, las instrucciones se dividen en

partes mas pequeas para trabajar en elloy estas conforman una tubera,sus tiempos son ciclos de

reloj lo que tarda en mover una instruccin, las etapas en las tuberas no siempre son mejor si son

mas porque esto aumenta la sobrecarga en la informacin mvil, esto hace que la complejidad del

procesador aumente,las tuberas traen riesgos consigo, si una instruccin se estanca las dems

que vienen de tras de ella se terminaran estancando, hay tres tipos de peligros, estructurales, de

datos y controlar los datos, los estructurales suceden cuando la memoria se solicita por mas de

una instruccin al mismo tiempo pero si ya esta esta en la tubera no acepta otra para la misma,

hay penalidades, pero para evitar los riesgos estructurales se duplican los registros y para evitar

los peligros se proporciona la cache de datos e instrucciones independientes, los peligros de

control dan una penalidad cuando la sucursal aun no es tomada porque se reserva y no se puede

continuar hasta que esta este disponible

Los principales componentes de la CPU son: Control Unidad, ALU y conjunto de registros. Son

Interconectados a travs del bus interno de la CPU. La interconexin con mdulos externos se

realiza mediante el Bus del Sistema. Seales de control emitidas por el La unidad de control

coordina la funcionalidad y los datos flujo dentro de la CPU y entre CPU y mdulos.

El conjunto de registros id el nivel superior de la memoria jerarqua. Slo una parte de los

registros es visible por el usuario. Los registros visibles del usuario pueden ser de uso general o

especializado.

Las instrucciones son ejecutadas por la CPU secuencia de pasos. La ejecucin de la instruccin

puede ser sustancialmente acelerado por el pipelining de la instruccin.

Una tubera se organiza como una sucesin de N etapas. En un momento determinado N

instrucciones pueden ser activo dentro de la tubera.

Se evita mantener una tubera a su velocidad mxima por los peligros de la tubera. Los riesgos

estructurales se conflictos de recursos. Los peligros de datos son producidos por dependencias de

datos entre instrucciones. Controlar peligros se producen como consecuencia de la instrucciones

También podría gustarte

- Relacion de Voltaje y CorrienteDocumento13 páginasRelacion de Voltaje y CorrienteEdwin SizaAún no hay calificaciones

- Curso Gratuito de Planificación Estratégica Con BSC DesignerDocumento12 páginasCurso Gratuito de Planificación Estratégica Con BSC DesignerOscar CauichAún no hay calificaciones

- Indicadores y CMI de Gobierno CorporativoDocumento41 páginasIndicadores y CMI de Gobierno CorporativoOscar CauichAún no hay calificaciones

- Cálculo de KPIs y Cuadro de Mando - Guía CompletaDocumento35 páginasCálculo de KPIs y Cuadro de Mando - Guía CompletaOscar CauichAún no hay calificaciones

- Boletin Backlog CursoDocumento2 páginasBoletin Backlog CursoOscar CauichAún no hay calificaciones

- Backlog de MantenimientoDocumento70 páginasBacklog de MantenimientoOscar CauichAún no hay calificaciones

- ElectoralDocumento12 páginasElectoralOscar CauichAún no hay calificaciones

- EjercicioAnalisis DisenoHotelMasReservadoDocumento12 páginasEjercicioAnalisis DisenoHotelMasReservadoOscar CauichAún no hay calificaciones

- Tienda Musical ExamenDocumento16 páginasTienda Musical ExamenOscar CauichAún no hay calificaciones

- Taller de Robótica Submarina: Manual de Construcción de Un ROVDocumento36 páginasTaller de Robótica Submarina: Manual de Construcción de Un ROVOscar CauichAún no hay calificaciones

- Sistema TuristicoDocumento52 páginasSistema Turisticobabson27Aún no hay calificaciones

- Convocatoria Seeds of The FutureDocumento4 páginasConvocatoria Seeds of The FuturesteelyheadAún no hay calificaciones

- Manual Mando Cast v02 PDFDocumento25 páginasManual Mando Cast v02 PDFEnriqueAún no hay calificaciones

- Mapa de ProcesosDocumento1 páginaMapa de ProcesosMario RestrepoAún no hay calificaciones

- Revision TecnicaDocumento5 páginasRevision TecnicaCésar Ojeda AlvaradoAún no hay calificaciones

- Intercambiador de Calor 2da UnidadDocumento27 páginasIntercambiador de Calor 2da UnidadMiller Ccanccapa MacedoAún no hay calificaciones

- Taller Fi SicaDocumento7 páginasTaller Fi SicaDavid BedoyaAún no hay calificaciones

- ER2 Cas - ManualDocumento29 páginasER2 Cas - Manualyovany yzquiel100% (1)

- COT 3505-2021 (1) Gina CPCDocumento2 páginasCOT 3505-2021 (1) Gina CPCRoberto RevinsacAún no hay calificaciones

- Potenciación Del Aprendizaje Por Medio Del Proyecto de Aula Con Saberes Transversales. Jenny Paola Quiroga RamírezDocumento9 páginasPotenciación Del Aprendizaje Por Medio Del Proyecto de Aula Con Saberes Transversales. Jenny Paola Quiroga RamírezAnonymous xqUJw92lzHAún no hay calificaciones

- Lista de Cotejo 3BDocumento2 páginasLista de Cotejo 3BJuan Antonio Anaya MoreyraAún no hay calificaciones

- Presentación Del Curso Ingeniería de Las TelecomunicacionesDocumento7 páginasPresentación Del Curso Ingeniería de Las TelecomunicacionesMónica RodríguezAún no hay calificaciones

- Circuitos ElectricosDocumento5 páginasCircuitos ElectricosVlado Abel Ccamapaza100% (1)

- Reglamento General de Inspección Del Trabajo y Aplicación de SancionesDocumento4 páginasReglamento General de Inspección Del Trabajo y Aplicación de Sancionescarlos islasAún no hay calificaciones

- Aprendo A Escribir PDFDocumento200 páginasAprendo A Escribir PDFMirian Soria SanchezAún no hay calificaciones

- Articulo de Opinion Cultura AmbientalDocumento6 páginasArticulo de Opinion Cultura AmbientalSergio Salazar REAL100% (2)

- Ficha Tecnica Corte DirectoDocumento5 páginasFicha Tecnica Corte DirectoJohanna Castellanos BrugésAún no hay calificaciones

- Especificaciones Tecnicas Cobertor SolarDocumento21 páginasEspecificaciones Tecnicas Cobertor SolarAnonymous eujmrqdUKAún no hay calificaciones

- Proyecto Hidroelectrica El QuimboDocumento37 páginasProyecto Hidroelectrica El QuimboLauritha QuitianAún no hay calificaciones

- Taller BSC y SGCDocumento4 páginasTaller BSC y SGCSandy Carolina Alarcon SaenzAún no hay calificaciones

- Introduccion A Microsoft WordDocumento10 páginasIntroduccion A Microsoft WordkikeveladoAún no hay calificaciones

- Diseño de Mezclas CompletoDocumento34 páginasDiseño de Mezclas CompletoDario Tapia CaballeroAún no hay calificaciones

- Presentación CHARLA PPP 2021-2Documento20 páginasPresentación CHARLA PPP 2021-2Nansi Guerreo SanchezAún no hay calificaciones

- Español - ¡Y Era Bueno!Documento4 páginasEspañol - ¡Y Era Bueno!Mauricio JiménezAún no hay calificaciones

- Mapa Sobre Biopolímeros Capaces de Reemplazar A Los Plásticos TradicionalesDocumento6 páginasMapa Sobre Biopolímeros Capaces de Reemplazar A Los Plásticos TradicionalesAlexander PalominoAún no hay calificaciones

- Siede I Democracia Educación en Valores y Desafios de La EpoDocumento11 páginasSiede I Democracia Educación en Valores y Desafios de La EpotitareliAún no hay calificaciones

- Ficha Tecnica - Pocket Colorimeter DR300Documento2 páginasFicha Tecnica - Pocket Colorimeter DR300Hector balcazar cuyaAún no hay calificaciones

- Prueba Teórica Microsoft AccessDocumento2 páginasPrueba Teórica Microsoft Accessramiro4cnuriabastusAún no hay calificaciones

- Informe 3 MciDocumento14 páginasInforme 3 MciKevin VilchezAún no hay calificaciones

- Constitución SAC - FaraDocumento4 páginasConstitución SAC - FaraRosaRomoQuispeAún no hay calificaciones

- CRVH T 12 0.75HP4 2100rpm (208 230 - 3) 3511Documento2 páginasCRVH T 12 0.75HP4 2100rpm (208 230 - 3) 3511MIGUELAún no hay calificaciones