Documentos de Académico

Documentos de Profesional

Documentos de Cultura

VHDL Implementación de Un Contador

Cargado por

mam0l1naTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

VHDL Implementación de Un Contador

Cargado por

mam0l1naCopyright:

Formatos disponibles

Escuela Universitaria de Informática

INTEGRACION DE SISTEMAS

Práctica nº 10

Implementación de:

Contador ascendente modulo 6

En un dispositivo GAL22V10

Madrid 09 Marzo 2010 Página 1 / 9

Escuela Universitaria de Informática

1.- Requisitos del sistema.

Diseño, desarrollo, verificación, implementación y programación en la GAL

22V10 o la PALCE22V10, de un circuito contador, ascendente módulo 6, con señal de

inicialización activa a nivel alto.

El desarrollo se hará con WinCUPL y como entrada a la herramienta la misma que

para los circuitos combinacionales, es decir, utilizar la metodología de entrada al diseño

mediante expresiones booleanas.

Definiciones.

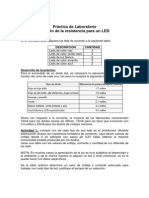

Dispositivos

GAL22V10 ATF22V10B ATF22V10

(Lattice) (Atmel - C

DIP Military)

DIP (Atmel)

DIP

Figura 1.

Notas figura nº 1: Las entradas se representan con “I” e “IN”.

Madrid 09 Marzo 2010 Página 2 / 9

Escuela Universitaria de Informática

Se seleccionan los formatos de encapsulado DIP que nos

proporcionan los fabricantes.

Se muestran los dispositivos de Atmel por que utilizamos la

herramienta WinCupl del mismo fabricante y en esta herramienta, no

disponemos de dispositivos genéricos y sólo incluye sus productos.

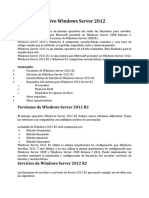

Macrocelda

Figura 2.

Notas figura nº 2: Se representa el esquema general de la macrocelda, obtenido de los

Data Sheets de Lattice.

La macrocelda puede actuar en dos modos:

1. Modo registrado, se recogen las salidas del biestable

(Multiplexor 4 a 1)

• Activas a nivel bajo S0 = 0 S1 = 0.

• Activas a nivel alto S0 = 1 S1 = 0.

El feedback se recogerá de la salida negada del biestable

(Multiplexor 2 a 1).

2. Modo combinacional se obvian las salidas del

biestable (Multiplexor 4 a 1)

• Activas a nivel bajo S0 = 1 S1 = 0.

• Activas a nivel alto S0 = 1 S1 = 1.

Madrid 09 Marzo 2010 Página 3 / 9

Escuela Universitaria de Informática

El feedback se recogerá de la salida de la puerta triestado

(Multiplexor 2 a 1).

Cuerpo teórico.

Se va a hacer uso del álgebre de Boole para las ecuaciones canónicas y

de la tabla de verdad para su cálculo.

a. Diagrama de estados.

S0

S0 000

S5 S1 S1 001

S2 010

S3 011

S4 100

S5 101

S4 S2

S3

Las transiciones entre estados se producirán por flanco ascendente de la

señal de reloj.

Por claridad en el diagrama de estados se omite el paso de cualquier estado

al S0 cuando se introduce un “1” por la entrada de inhibición activa a nivel

alto.

Se calcula el nº de biestables necesarios para implementar el contador.

Siendo:

M Módulo.

n Número de biestables necesarios para implementar el

contador.

Aplicando la fórmula

n = 3 biestables

Las macroceldas del dispositivo GAL 22V10 están implementadas con

biestables de tipo D con señal de reloj activa por flanco de subida, con

Madrid 09 Marzo 2010 Página 4 / 9

Escuela Universitaria de Informática

entradas Asynchronous Reset (AR) y Synchronous Preset (SP), por lo tanto

utilizaremos biestables tipo D en el diseño del contador.

Variables del dispositivo.

Las salidas que nos interesan de los biestables son las salidas activa a nivel

alto Q , y como entradas tendremos las D por tanto:

Variables de entrada del sistema:

D0 Entrada D al biestable nº 0.

D1 Entrada D al biestable nº 1.

D2 Entrada D al biestable nº 2.

ini Señal de inicialización del dispositivo activa a nivel alto.

Variables de salida del sistema:

Q0 Salida Q del biestable nº 0.

Q1 Salida Q del biestable nº 1.

Q2 Salida Q del biestable nº 2.

Tabla de Verdad.

Para simplificar la exposición vamos a unir las tablas de transición

entre estados con la de excitación de las entradas.

Al tratarse de biestables de tipo D, coincidirán los valores de la tabla

de transición de t + 1 con la de excitación para alcanzar dichos valores.

Tabla de transición de estados Tabla de excitación

E stado actual E stado siguiente

Entradas

t t+ 1

ini Q2 Q1 Q0 Q2 Q1 Q0 D2 D1 D0

0 0 0 0 0 0 1 0 0 1

0 0 0 1 0 1 0 0 1 0

0 0 1 0 0 1 1 0 1 1

0 0 1 1 1 0 0 1 0 0

0 1 0 0 1 0 1 1 0 1

0 1 0 1 0 0 0 0 0 0

0 1 1 0 X X X X X X

0 1 1 1 X X X X X X

1 X X X 0 0 0 0 0 0

Estado prohibido

Estado prohibido

Madrid 09 Marzo 2010 Página 5 / 9

Escuela Universitaria de Informática

Ecuación Canónica.

Entrada D0:

Entrada D1:

Entrada D2:

Implementación.

Madrid 09 Marzo 2010 Página 6 / 9

Escuela Universitaria de Informática

Se realiza mediante el programa WinCUPL.

Mediante este programa se generará el fichero .pld correspondiente y se

creará el fichero .si con los datos de entrada de simulación.

Finalmente obtendremos la salida gráfica para la función introducida en

el .pld.

Gráficamente el dispositivo quedaría conectado como se muestra

en la figura siguiente:

CLK Q2

E Q1

Q0

Madrid 09 Marzo 2010 Página 7 / 9

Escuela Universitaria de Informática

El fichero .pld mencionado es el mostrado en la siguiente figura:

La salida es:

field salidas = [q2..q0];

salidas.ar = 'b'000;

salidas.sp = 'b'000;

q2.d = (!i & q2 & !q1 & !q0) # (!i & !q2 & q1 & q0);

q1.d = (!i & !q2 & !q1 & q0) # (!i & !q2 & q1 & !q0);

q0.d = (!i & !q2 & !q0) # (!i & !q1 & !q0);

Madrid 09 Marzo 2010 Página 8 / 9

Escuela Universitaria de Informática

El código del fichero simulación es el siguiente:

La salida gráfica obtenida tras la simulación es la siguiente:

en la figura se puede comprobar que las salidas coinciden con el código introducido

en el fichero de simulación: cuando E vale 1 todas las variables aparecen a cero; en el

resto de valores se puede apreciar E a 0 y el comienzo de la cuenta (de 1 a 4), después

se activa de nuevo E y en el siguiente pulso hacemos la cuenta completa (hasta 5).

Madrid 09 Marzo 2010 Página 9 / 9

También podría gustarte

- Sumador Completo de 4 BITSDocumento16 páginasSumador Completo de 4 BITSDaniel Sanchez75% (4)

- Labview & PicDocumento43 páginasLabview & Piclucian lunaAún no hay calificaciones

- Unidad 3,4 EnsambladorDocumento13 páginasUnidad 3,4 EnsambladorPérez Oso100% (1)

- Digital systems implementation with WinCUPLDocumento90 páginasDigital systems implementation with WinCUPLpalmerosd100% (1)

- Informe Sumador Restador 4 BitsDocumento13 páginasInforme Sumador Restador 4 BitsZulma Russi100% (3)

- ModularizacionDocumento18 páginasModularizacionsaulrb_329497Aún no hay calificaciones

- Decodificador 7447Documento2 páginasDecodificador 7447d-fbuser-44131765100% (3)

- ComSerial PIC-PC USARTDocumento8 páginasComSerial PIC-PC USARTDavid Mercado BAún no hay calificaciones

- Memoria Ram 6116Documento5 páginasMemoria Ram 6116Koky Hernandez Suarez50% (2)

- TP Anual 2019 Historia Del Diseño IndustrialDocumento9 páginasTP Anual 2019 Historia Del Diseño IndustrialJulian MosqueraAún no hay calificaciones

- Alu VHDLDocumento21 páginasAlu VHDLFrodo AlejandroAún no hay calificaciones

- Practica 2 PicoBlazeDocumento24 páginasPractica 2 PicoBlazeAntonio David EscobarAún no hay calificaciones

- Semaforo (Digitales)Documento8 páginasSemaforo (Digitales)Diego Perez FargeAún no hay calificaciones

- Como Medir Los TransistoresDocumento2 páginasComo Medir Los Transistoresxtron100% (1)

- Tarea4 Fpga S HD FDDocumento11 páginasTarea4 Fpga S HD FDIvan DuranAún no hay calificaciones

- Manual XilinxDocumento15 páginasManual XilinxPakitoCachorrosAún no hay calificaciones

- Programación de Circuitos Lógicos en VHDLDocumento26 páginasProgramación de Circuitos Lógicos en VHDLCheynAún no hay calificaciones

- Lab 5Documento8 páginasLab 5juan pablo rojas ruizAún no hay calificaciones

- Diseño de Un Decodificador Binario-Decimal A Bases de Compuertas Basicas y Display 7 SegmentosDocumento12 páginasDiseño de Un Decodificador Binario-Decimal A Bases de Compuertas Basicas y Display 7 SegmentosGustavo Adolfo Mestra Garay75% (4)

- Fpga y PLD, VHDL y VerilogDocumento6 páginasFpga y PLD, VHDL y VerilogLuis PintadoAún no hay calificaciones

- Aplicaciones de Circuitos DigitalesDocumento15 páginasAplicaciones de Circuitos DigitalesAlex Pomier AliagaAún no hay calificaciones

- PLD - Clase 4 - CUPL Quick StartDocumento18 páginasPLD - Clase 4 - CUPL Quick StarthjcabreraAún no hay calificaciones

- Contador Del 00 Al 99Documento7 páginasContador Del 00 Al 99Sigur Svenska83% (6)

- Implementación de funciones lógicas mediante PAL y VHDLDocumento12 páginasImplementación de funciones lógicas mediante PAL y VHDLgustavogomez4505Aún no hay calificaciones

- Introducción a VHDLDocumento34 páginasIntroducción a VHDLAnel VallarinoAún no hay calificaciones

- Control de Fase DirectoDocumento7 páginasControl de Fase DirectoMaricelaCrisMJAún no hay calificaciones

- Tema 10 Multiplexores y DemultiplexoresDocumento23 páginasTema 10 Multiplexores y DemultiplexoresCarlos juan carlosAún no hay calificaciones

- Trabajo Final1 - VHDLDocumento7 páginasTrabajo Final1 - VHDLElyel Surco M0% (1)

- Plan de Trabajo 2015 Operaciones IIDocumento14 páginasPlan de Trabajo 2015 Operaciones IIGastón PellizzariAún no hay calificaciones

- Guia Flip Flop VHDLDocumento16 páginasGuia Flip Flop VHDLViridiana Fernandez CarreonAún no hay calificaciones

- Diseño e Implementación de Un Multiplicador IterativoDocumento9 páginasDiseño e Implementación de Un Multiplicador IterativoMarco TorresAún no hay calificaciones

- VHDL TutorialDocumento40 páginasVHDL TutorialvoltersasAún no hay calificaciones

- Practica 5 Contador de 0 A 3 JK Con PausaDocumento7 páginasPractica 5 Contador de 0 A 3 JK Con PausaFrancisco Javier Vázquez Espinoza100% (1)

- Multimetro Digital Con Pic 16F877A - Libros, Simuladores, Tutoriales Y Mucho MásDocumento9 páginasMultimetro Digital Con Pic 16F877A - Libros, Simuladores, Tutoriales Y Mucho MásArmando Campos SalazarAún no hay calificaciones

- VHDLDocumento24 páginasVHDLErik RomeroAún no hay calificaciones

- Lenguaje EnsambladorDocumento72 páginasLenguaje Ensambladorvictorvaldes24100% (4)

- 6 Circuitos Combinacionales P ImprimirDocumento36 páginas6 Circuitos Combinacionales P ImprimirFabian AcostaAún no hay calificaciones

- Lenguaje HibridoDocumento34 páginasLenguaje Hibridoviosjx0% (1)

- Introducción al lenguaje de programación LadderDocumento9 páginasIntroducción al lenguaje de programación Ladderjose marquezAún no hay calificaciones

- Diseno SecuencialDocumento28 páginasDiseno SecuencialJacqueline Ponce Pinos100% (4)

- Informe 1 DACDocumento9 páginasInforme 1 DACJose ArmandoAún no hay calificaciones

- Circuitos aritméticos binariosDocumento76 páginasCircuitos aritméticos binariosChampa Jiménez de CostanillasAún no hay calificaciones

- Parcial Final DigitalesDocumento19 páginasParcial Final Digitalespaula garzonAún no hay calificaciones

- Proyecto de Encriptado Con DsPICDocumento5 páginasProyecto de Encriptado Con DsPICAnnie1388Aún no hay calificaciones

- Regulador de Voltaje ACDocumento1 páginaRegulador de Voltaje ACCitio LogosAún no hay calificaciones

- ADC Con Pico-BlazeDocumento13 páginasADC Con Pico-BlazeIvan RomoAún no hay calificaciones

- Tema 6 Teclado Digital DecimalDocumento4 páginasTema 6 Teclado Digital Decimal2mercedesAún no hay calificaciones

- Practica LEDSDocumento3 páginasPractica LEDSAlvaro MartínezAún no hay calificaciones

- Sumador Completo 1 Y4 BitsDocumento9 páginasSumador Completo 1 Y4 BitsNelson López100% (1)

- 4.4 Programación Del Puerto ParaleloDocumento4 páginas4.4 Programación Del Puerto ParaleloFrank Diaz100% (1)

- Linea Del Tiempo Diseno IndustrialDocumento14 páginasLinea Del Tiempo Diseno IndustrialalvorareAún no hay calificaciones

- Practica6 Organización y Arquitectura de ComputadorasDocumento17 páginasPractica6 Organización y Arquitectura de ComputadorasEduardo RojasAún no hay calificaciones

- Resonancia y Lugares GeométricosDocumento58 páginasResonancia y Lugares GeométricosJuan Carlos100% (1)

- Interrupciones de Los Pic16f8xxxDocumento11 páginasInterrupciones de Los Pic16f8xxxtony100% (1)

- Maquinas MooreDocumento35 páginasMaquinas MooreDaniel GuerraAún no hay calificaciones

- Informe 7Documento33 páginasInforme 7Jonathan RuizAún no hay calificaciones

- Laboratorio 07Documento11 páginasLaboratorio 07Kewin Sánchez SánchezAún no hay calificaciones

- Practica 9Documento15 páginasPractica 9Renato Beltran CaceresAún no hay calificaciones

- Demultiplexor y MultiplexorDocumento6 páginasDemultiplexor y MultiplexorStwart EspinozaAún no hay calificaciones

- Guia 2Documento19 páginasGuia 2Carlos del CampoAún no hay calificaciones

- Guía Del UsuarioDocumento117 páginasGuía Del Usuariomam0l1naAún no hay calificaciones

- Curso Gratis Desarrollo Web Front End MiscursosyformacionDocumento3 páginasCurso Gratis Desarrollo Web Front End Miscursosyformacionmam0l1naAún no hay calificaciones

- Corto Maltes, Manara, Dylan y Eisner en cómics clásicosDocumento1 páginaCorto Maltes, Manara, Dylan y Eisner en cómics clásicosmam0l1naAún no hay calificaciones

- MOTIVACIONDocumento5 páginasMOTIVACIONmam0l1naAún no hay calificaciones

- La Economía Catalana y El Bulo Del IndepentismoDocumento19 páginasLa Economía Catalana y El Bulo Del Indepentismomam0l1naAún no hay calificaciones

- Gestión seguridad informática empresaDocumento2 páginasGestión seguridad informática empresamam0l1naAún no hay calificaciones

- ExplotacionDocumento5 páginasExplotacionmam0l1naAún no hay calificaciones

- Auditori ADocumento11 páginasAuditori Amam0l1naAún no hay calificaciones

- Práctica 11Documento2 páginasPráctica 11mam0l1naAún no hay calificaciones

- Esquema DirectorDocumento6 páginasEsquema Directormam0l1naAún no hay calificaciones

- C SeguridadDocumento26 páginasC Seguridadmam0l1naAún no hay calificaciones

- Práctica 6 AnclasDocumento2 páginasPráctica 6 Anclasmam0l1naAún no hay calificaciones

- Organigrama de EmpresaDocumento2 páginasOrganigrama de Empresamam0l1naAún no hay calificaciones

- Audio y VídeoDocumento3 páginasAudio y Vídeomam0l1naAún no hay calificaciones

- Práctica 5 Capas y PáginasDocumento2 páginasPráctica 5 Capas y Páginasmam0l1naAún no hay calificaciones

- Práctica 20-ResueltaDocumento2 páginasPráctica 20-Resueltamam0l1naAún no hay calificaciones

- Práctica 4 Creación HTML Con ColorDocumento2 páginasPráctica 4 Creación HTML Con Colormam0l1naAún no hay calificaciones

- Práctica 3 Creación HTMLDocumento2 páginasPráctica 3 Creación HTMLmam0l1naAún no hay calificaciones

- TEO 05 Arquitecturas Capas y NivelesDocumento13 páginasTEO 05 Arquitecturas Capas y NivelesFrank PizarroAún no hay calificaciones

- IMPORTANTE Manual y OtrosDocumento4 páginasIMPORTANTE Manual y OtrosRolando Venegas VenegasAún no hay calificaciones

- Sistema Operativo Windows Server 2012Documento5 páginasSistema Operativo Windows Server 2012Raul GonzalesAún no hay calificaciones

- Fundamentos de RedesDocumento8 páginasFundamentos de RedesSebastian MendozaAún no hay calificaciones

- Computacion - 4to AñoDocumento2 páginasComputacion - 4to AñoSergio GonzalezAún no hay calificaciones

- Prep Informàtica Sem 33 G3Documento3 páginasPrep Informàtica Sem 33 G3Lorena OsorioAún no hay calificaciones

- Cuento OsitoDocumento20 páginasCuento OsitoBea TrizAún no hay calificaciones

- Practicas REDOLOG Tema4Documento8 páginasPracticas REDOLOG Tema4rikotonAún no hay calificaciones

- GW Complete Manual ES PDFDocumento92 páginasGW Complete Manual ES PDFAroa ChansAún no hay calificaciones

- Laboratorio Clases en PythonDocumento15 páginasLaboratorio Clases en PythonCarlos RiveroAún no hay calificaciones

- Lab 1 Operaciones AritmeticasDocumento14 páginasLab 1 Operaciones AritmeticasWilmerRojasAún no hay calificaciones

- Medidas de CapacidadDocumento25 páginasMedidas de CapacidadBero BojórquezAún no hay calificaciones

- Proyecto Sistema FerreteriaDocumento39 páginasProyecto Sistema FerreteriaEduard TorresAún no hay calificaciones

- Programación en EnsambladorDocumento4 páginasProgramación en EnsambladorPedro Franklin MeranAún no hay calificaciones

- Plan de Estudios InformaticaDocumento4 páginasPlan de Estudios InformaticaRandy Huarcacho CondoriAún no hay calificaciones

- Recuperación Tecnología ESO 2o pendientesDocumento25 páginasRecuperación Tecnología ESO 2o pendientesLola ZambranaAún no hay calificaciones

- HackersDocumento115 páginasHackersJorge Patricio Rodriguez Rodriguez100% (1)

- Exam 0405Documento18 páginasExam 0405Camilo Ayala GomezAún no hay calificaciones

- Lenguaje Algoritmico 5Documento24 páginasLenguaje Algoritmico 5anon-68902Aún no hay calificaciones

- Tipos de Gráficas y UsosDocumento6 páginasTipos de Gráficas y UsosDaniel PaniaguaAún no hay calificaciones

- Presentación Robot E-PuckDocumento5 páginasPresentación Robot E-PuckPatricio FuentealbaAún no hay calificaciones

- Discusión Sobre Lo Que Constituye La Evaluación Formativa Basada en Un Ejemplo. M1 - U2-Foro - 2 Tarea Luis A. Cauna AnquiseDocumento2 páginasDiscusión Sobre Lo Que Constituye La Evaluación Formativa Basada en Un Ejemplo. M1 - U2-Foro - 2 Tarea Luis A. Cauna AnquiseLuis Cauna AnquiseAún no hay calificaciones

- Propuesta Capacitación Ofimatica, Trabajo en Equipo y LIderazgoDocumento5 páginasPropuesta Capacitación Ofimatica, Trabajo en Equipo y LIderazgoAngel herrera saraAún no hay calificaciones

- 4 Tipos de OrganigramaDocumento6 páginas4 Tipos de OrganigramaMarinita GarciaAún no hay calificaciones

- Reliable UAV LiDAR YellowScan SurveyorDocumento2 páginasReliable UAV LiDAR YellowScan Surveyorpablo carvajalAún no hay calificaciones

- Informe de Instalacion UbuntuDocumento6 páginasInforme de Instalacion UbuntuAlexander CajasAún no hay calificaciones

- C3Documento3 páginasC3Notlim MarulandaAún no hay calificaciones

- Configuración Escritorio y Asistencia remotos WindowsDocumento5 páginasConfiguración Escritorio y Asistencia remotos WindowsMc JordanAún no hay calificaciones

- Modelo IoarDocumento3 páginasModelo IoarkevinrubinalagunaAún no hay calificaciones

- Funciones para RedondearDocumento5 páginasFunciones para Redondear2162120028 MARIA CAMILA CUADRADO AVILA ESTUDIANTE ACTIVOAún no hay calificaciones