Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Tarea 2

Cargado por

Juan R Ayala-OlivaresTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Tarea 2

Cargado por

Juan R Ayala-OlivaresCopyright:

Formatos disponibles

INAOE, primer cuatrimestre 2016. Diseo de circuitos integrados analgicos I.

Yojanes Andrs Rodrguez Velsquez.

Diseo y anlisis de una topologa de amplificacin de dos etapas

En el presente informe se presentan los resultados en el diseo del circuito

presentado en la figura 1, un amplificador de dos etapas donde se tiene

inicialmente un seguidor de fuente (M 1) seguido de una amplificador de

transconductancia (M2), para el cual se hace un anlisis del punto de operacin

segn los parmetros requeridos con respecto a lo que se espera de su

ganancia en AC y comportamiento en pequea seal. Posteriormente se hace

una simulacin del circuito en DC, AC y un barrido en DC de la entrada para

comparar los resultados obtenidos con los planteados en el diseo inicial.

La tecnologa utilizada para el montaje de este circuito es de 0.5 m con una

alimentacin mxima de 5 V. En la tabla 1 se muestran los parmetros de nivel

1 que caracterizan la tecnologa y fueron utilizados para este diseo.

Figura 1. Topologa del circuito analizado

Parmetro

NMOS

PMOS

Kn [uA]

114.6

37.8

Vtho [V]

0.68

0.93

Lambda [mV-1]

15.1

46.4

1/2

Gamma [V ]

0.49

0.56

Tab. 1. Parmetros de los transistores de 5 V en la tecnologa de 0.5 m.

Antes de iniciar el diseo se establecen algunas caractersticas de

funcionamiento del circuito y de lo que se espera en AC. La alimentacin se

toma dual para un Vdd de 2.5 V y un Vss de -2.5 V, se establece una ganancia

de 10 V/V para la carga mnima R L que es de 10 K por lo que de este valor en

adelante la ganancia del sistema debe aumentar; se utiliza una corriente de

100 A a travs de M1, M2, MD y MKI, la corriente de MI ser de 200 A y la que

se utilice en los transistores de copia M A, MB y Mc ser de 20 A. Adicionalmente

se tiene en cuenta un voltaje de saturacin para los transistores que actan

como fuente de corriente (MI, MKI, y MD) alrededor de 0.1 V, dependiendo de

cuanto sea el VGS que deba usar cada transistor de acuerdo a la topologa.

Como inicialmente se tiene una carga de 10 K, se desprecian las impedancias

de salida del transistor M 2 y la fuente de corriente en la ecuacin de ganancia,

adicionalmente se considera que el nodo de salida del seguidor de fuente (V I)

es un nodo de baja impedancia, y tomando M 1 y M2 como iguales la ganancia

se aproxima como sigue:

Av =

V I V out 1

(g R )

V VI

2 m2 L

()

Tomando la ganancia como 10 V/V y tomando la ecuacin de transconductancia

para M2 se obtiene un W/L2:

INAOE, primer cuatrimestre 2016. Diseo de circuitos integrados analgicos I.

Yojanes Andrs Rodrguez Velsquez.

gm 2 = 2 2 k n

W

I

L 2 D2

2

W

1

2 Av

=

=174.52

L 2 2 kn I D2 R L

( )

De esta forma la transconductancia gm2 es de 2 mS, a partir de la cual se

calcula el voltaje de saturacin requerido:

V SAT 2=V SAT 1=

2 I D2

=0.1V

gm2

De aqu que el voltaje V GS1 y VGS2 sean de 0.78 V dejando un V DSI de 1.72 V y un

VDS1 de 3.28 V que se utiliza para calcular la relacin de aspecto de M 1 a partir

de la ecuacin de corriente en saturacin:

2 I D1

W

=

=166.34

L 1 k n (V SAT 1)2 ( 1+ n V DS 1 )

Para el clculo de los transistores tipo n que hacen el espejo de corriente se

toma un VSATI de 0.32 V, obteniendo as un V GSI y VGSA=VDSA de 1 V debido a que

se requiere un alto flujo de corriente en M I, 200 A, no siendo as en el caso de

MA por el cual va a circular una corriente de 20 A por ende la relacin de

corrientes ser de 1 a 10. Se calculan las dimensiones de estos dos transistores

como sigue:

2 I DI

W

=

=33.23

L I k n (V SATI )2 ( 1+ n V DSI )

W

1 W 1+ n V DSA

=

=3.36

L A 10 L I 1+ n V DSI

Para la fuente de corriente formada por los transistores tipo p se utiliza un

espejo de corriente cascode. Donde se toma un voltaje de saturacin en M KI y

MD de 0.34 V para completar un margen de 4 V en la excursin de salida, de

esta forma se obtiene que el V SG de MB, MC, MD y MKI es de 1.27 V al igual que el

VSD de los mismos transistores. Con estos valores y la corriente de 20 A para

MB y MC y 100 A para MD y MKI se obtienen las dimensiones de estos

transistores como sigue:

2 I DKI

W

W

=

=

=43.32

L KI L D k p (V SATKI )2 ( 1+ p V DSKI )

INAOE, primer cuatrimestre 2016. Diseo de circuitos integrados analgicos I.

Yojanes Andrs Rodrguez Velsquez.

2 I DB

W

W

=

=

=7.3

L B L C k p (V SATB )2 ( 1+ p V DSB )

Para el clculo de RP se tiene en cuenta que soporta una corriente de 20 A y

una tensin de 1.46 V, se obtiene una resistencia de 73 K. Para el caso de

diseo se ajustan los valores encontrados de W/L de acuerdo a las dimensiones

mnimas de la tecnologa, de esta forma en este trabajo se toman L y W como

mltiplos enteros de 0.6 m. Debido a la caracterizacin que se hizo

previamente para el parmetro lambda se utiliza el mltiplo 5 para L, y W se

ajusta de acuerdo a los parmetros hallados. Los valores finales de la relacin

de aspecto de cada transistor se muestran en la tabla 2.

M1

M2

MI

MA

MB

MC

MD

163.6

175.2

26.8

3.4

9.6

9.6

46.4

Tabla 2. Relacin de aspecto de los transistores utilizados.

W/L

MKI

46.4

Con estos parmetros se simula el circuito y se comprueba que todos los

transistores estn en saturacin y en el punto de operacin diseado, para lo

cual luego de los ajustes mostrados en la tabla 2 se obtienen los resultados

esperados en DC, estos se muestran en el apndice A.

Posteriormente se procede a comparar los resultados diseados en AC del

sistema con los obtenidos, inicialmente para una carga de 10 K y

posteriormente para el circuito sin carga. Se espera una ganancia de 20 dB

para el circuito con carga y de 52 dB para el circuito sin carga debido a la alta

impedancia de salida que tiene la configuracin. Para el clculo del ancho de

banda se toman las capacitancias extradas en la simulacin luego de

especificar las reas de drenaje y fuente; teniendo en cuenta que existen tres

nodos de importancia para el flujo de la seal se calculan la capacitancia y

resistencia equivalentes de ese nodo para finalmente hallar el polo dominante

del sistema. Debido a que en el nodo Vin no se estn involucrando resistencias

de entrada no se tiene en cuenta este nodo para el clculo de las constantes

de tiempo, para los dems nodos tendremos:

Nodo VI

C I =C GS 2+ CGD I +C DBI =173.79 pF

RI =

1

1

/

/ r o 1 / r oI 250

gm1 gm2

I =C I R I =43.45 ns

Nodo VOUT

COUT =C GD 2+C D B 2 +C G D K I +C DBKI =1.96 pF

INAOE, primer cuatrimestre 2016. Diseo de circuitos integrados analgicos I.

Yojanes Andrs Rodrguez Velsquez.

ROUT r o KI / g m 2 r o 2

( g1 / r

m2

o1

))

/ r o 2 649.58 K

OUT =COUT ROUT =1.27 s

Como se puede notar la mayor se da en el nodo de salida, por lo que

podemos reducir la limitacin de frecuencia a este nodo tomndolo como el

que provee el polo dominante, de esta forma tendramos que la frecuencia de

corte para el circuito sin carga sera:

2 (OUT )=125 KHz

1

f c

En la figura 2 se muestra la respuesta en frecuencia del circuito sin carga,

donde se puede observar que la frecuencia de corte se encuentra en 295 KHz,

lo cual muestra falta de precisin en la aproximacin de las capacitancias

internas de los transistores, sin embargo se tiene un acercamiento a la

frecuencia real. En cuanto a la ganancia del sistema, se tiene un valor de 51.61

dB.

Para el caso del circuito con carga cambiara la en el nodo de salida debido al

cambio de resistencia:

OUT =C OUT (ROUT / R L )=19.3 n s

A partir de las dos constantes de tiempo se obtiene una frecuencia de 2.54

MHz. En la figura 3 se observan los resultados para el sistema con una carga

de 10 K, en este caso la ganancia obtenida es de 18.68 dB y la frecuencia de

corte es de 3.28 MHz.

Figura 2. Anlisis AC del circuito sin carga.

INAOE, primer cuatrimestre 2016. Diseo de circuitos integrados analgicos I.

Yojanes Andrs Rodrguez Velsquez.

Figura 3. Anlisis Ac del circuito con carga de 10 K.

Finalmente se hace un barrido en DC variando la seal de entrada para

comprobar el rango de excursin de la seal a la salida y entrada, y comprobar

la linealidad del mismo en la zona de operacin.

Figura 4. Barrido en DC para el circuito con carga de 10 K

En la curva mostrada en la figura 4 se observa que el rango de excursin de la

seal no es muy amplio, de hecho solo se limita a 1 V entre -0.5 V y 0.5 V, este

resultado es muy pequeo en comparacin a los 5 V que se tienen de

alimentacin, por ende el circuito debe ser reajustado para obtener un mayor

rango dinmico a la salida de la seal.

INAOE, primer cuatrimestre 2016. Diseo de circuitos integrados analgicos I.

Yojanes Andrs Rodrguez Velsquez.

El caso del circuito sin carga se muestra en la figura 5, donde se evidencia una

descompensacin en el ciclo negativo de la seal tanto en rango de excursin

como en linealidad ya que no coinciden las pendientes de la curva en la parte

positiva y negativa de la salida, por ende la seal en tiempo presentar

distorsin. Estos problemas de manejo de seal son fuertes, por lo que se debe

cambiar el diseo ya sea en los parmetros del mismo o ajustando la topologa

con el fin de mejorar la respuesta del mismo.

Figura 5. Barrido en DC para el circuito sin carga.

Apndice A

Punto de operacin de los transistores.

INAOE, primer cuatrimestre 2016. Diseo de circuitos integrados analgicos I.

Yojanes Andrs Rodrguez Velsquez.

También podría gustarte

- 5 PLAN DE TUTORIA OkDocumento19 páginas5 PLAN DE TUTORIA OkJulio Marcial Calderon YupanquiAún no hay calificaciones

- Remodelación oficinas Latam nave 600Documento12 páginasRemodelación oficinas Latam nave 600JC MALLQUIAún no hay calificaciones

- Manual Inmunizaciones API2017 Print4abr2017-3Documento348 páginasManual Inmunizaciones API2017 Print4abr2017-3Marcos Quispe KapaAún no hay calificaciones

- Clase 3 Numerologia SirianaDocumento40 páginasClase 3 Numerologia SirianaKaro PincheiraAún no hay calificaciones

- Pánico EscénicoDocumento3 páginasPánico EscénicocarolinaAún no hay calificaciones

- Guia Ciclo Iii Unidades de Longitud - MetroDocumento4 páginasGuia Ciclo Iii Unidades de Longitud - MetrowilsonAún no hay calificaciones

- Trabadas Tomo IDocumento28 páginasTrabadas Tomo IYulian159 NoseAún no hay calificaciones

- Distribucion de Planta - Practica Calificada 20191ADocumento5 páginasDistribucion de Planta - Practica Calificada 20191AKevin VidalAún no hay calificaciones

- Recursos naturales renovables y no renovablesDocumento4 páginasRecursos naturales renovables y no renovablesEricka Cobox100% (1)

- Prueba Sexto Basico Historia 2Documento5 páginasPrueba Sexto Basico Historia 2vasobeanAún no hay calificaciones

- CeromerosDocumento22 páginasCeromerosCaro OrtegaAún no hay calificaciones

- Administracion FinancieraDocumento2 páginasAdministracion FinancieraMary VeraAún no hay calificaciones

- Especialidades Scouts: Deportes y actividades al aire libreDocumento55 páginasEspecialidades Scouts: Deportes y actividades al aire libreAnny SfmAún no hay calificaciones

- Creatividad, Master UnIrDocumento22 páginasCreatividad, Master UnIrAnna TorresAún no hay calificaciones

- Test Ordenanza Conserje AyuntamientoDocumento3 páginasTest Ordenanza Conserje Ayuntamientomantecados67% (3)

- Cuidados interculturales en la salud materna e infantilDocumento28 páginasCuidados interculturales en la salud materna e infantilRebeca LoyolaAún no hay calificaciones

- Consumos culturales de adolescentes y jóvenesDocumento29 páginasConsumos culturales de adolescentes y jóvenesgauchofiero99Aún no hay calificaciones

- Disposiciones Complementarias FinalesDocumento2 páginasDisposiciones Complementarias FinalesAdriana NicollAún no hay calificaciones

- Aerodinamica FCD 1Documento6 páginasAerodinamica FCD 1Rolando RivasAún no hay calificaciones

- Plan Analitco MAMOGRAFIA I - EUFEMIADocumento3 páginasPlan Analitco MAMOGRAFIA I - EUFEMIAMonserrate Briones CuencaAún no hay calificaciones

- Tarea 1 Jorge JuarezDocumento8 páginasTarea 1 Jorge Juarezjorge juarezAún no hay calificaciones

- Por Qué Surge El BarrocoDocumento3 páginasPor Qué Surge El BarrocoJose JaspeAún no hay calificaciones

- Psilocibes ThemushroomsDocumento255 páginasPsilocibes Themushroomsfred sanAún no hay calificaciones

- Tasacion Comercial de InmuebleDocumento5 páginasTasacion Comercial de InmuebleMARTINAún no hay calificaciones

- Verbos Regulares e Irregulares en Ingles.Documento3 páginasVerbos Regulares e Irregulares en Ingles.Edam MaldonadoAún no hay calificaciones

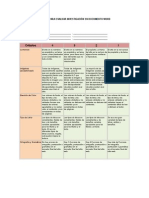

- Rubrica para Evaluar Investigacin en WordDocumento1 páginaRubrica para Evaluar Investigacin en Wordapi-257093331Aún no hay calificaciones

- Unidad Educativa Fiscal "Monseñor Leonidas Proaño": Actividades/ Clases Virtuales 3er. TrimestreDocumento6 páginasUnidad Educativa Fiscal "Monseñor Leonidas Proaño": Actividades/ Clases Virtuales 3er. TrimestreNayeli melani Criollo torresAún no hay calificaciones

- Movimiento Uniforme en Tuberías y La Ecuación de DarcyDocumento5 páginasMovimiento Uniforme en Tuberías y La Ecuación de DarcySERGIO PAUL MASABANDA DIAZAún no hay calificaciones

- Clasificacion Segun La Cantidad de DivisoresDocumento5 páginasClasificacion Segun La Cantidad de DivisoresDavidPazMestanzaAún no hay calificaciones

- Ayudantía N°3.1 - Ing PDFDocumento1 páginaAyudantía N°3.1 - Ing PDFsdfghfgmjhfgdfdsAún no hay calificaciones