Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Ad632 PDF

Cargado por

Bouazizi HechmiDescripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Ad632 PDF

Cargado por

Bouazizi HechmiCopyright:

Formatos disponibles

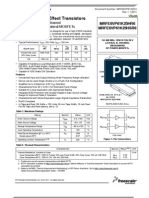

Internally Trimmed

Precision IC Multiplier

AD632

Data Sheet

FEATURES

FUNCTIONAL BLOCK DIAGRAM

Pretrimmed to 0.5% maximum 4-quadrant error

All inputs (X, Y, and Z) differential, high impedance for

[(X1 X2)(Y1 Y2)/10] + Z2 transfer function

Scale-factor adjustable to provide up to 10 gain

Low noise design: 90 mV rms, 10 Hz to 10 kHz

Low cost, monolithic construction

Excellent long-term stability

VS

TRANSFER FUNCTION

X1

V-I

X2

VO = A

(X1 X2) (Y1 Y2)

10

TRANSLINEAR

MULTIPLIER

ELEMENT

Y1

(Z1 Z2)

V-I

Z2

VOS

Y2

Z1

HIGH GAIN

OUTPUT

AMPLIFIER

2.7k

V-I

0.75 ATTEN

OUT

09040-007

APPLICATIONS

High quality analog signal processing

Differential ratio and percentage computations

Algebraic and trigonometric function synthesis

Accurate voltage controlled oscillators and filters

+VS

STABLE

REFERENCE

AND BIAS

25k

Figure 1.

GENERAL DESCRIPTION

The AD632 is an internally trimmed monolithic four-quadrant

multiplier/divider. The AD632B has a maximum multiplying

error of 0.5% without external trims.

rejection. The effectiveness of the variable gain capability is

enhanced by the inherent low noise of the AD632 at 90 V rms.

Excellent supply rejection, low temperature coefficients, and

long-term stability of the on-chip thin film resistors and buried

zener reference preserve accuracy even under adverse conditions.

The simplicity and flexibility of use provide an attractive alternative

approach to the solution of complex control functions.

1.

2.

The AD632 is pin-for-pin compatible with the industry

standard AD532 but with improved specifications and a fully

differential high impedance Z input. The AD632 is capable of

providing gains of up to 10, frequently eliminating the need

for separate instrumentation amplifiers to precondition the

inputs. The AD632 can be effectively employed as a variable

gain differential input amplifier with high common-mode

Rev. D

PRODUCT HIGHLIGHTS

3.

4.

5.

6.

Guaranteed performance over temperature.

The AD632A and AD632B are specified for maximum

multiplying errors of 1.0% and 0.5% of full scale,

respectively, at +25C and are rated for operation from

25C to +85C.

Maximum multiplying errors of 2.0% (AD632S) and

1.0% (AD632T) are guaranteed over the extended

temperature range of 55C to +125C.

High reliability.

The AD632S and AD632T series are available with MILSTD-883 Level B screening.

All devices are available in either the hermetically sealed

TO-100 metal can or ceramic DIP package.

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 19792013 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

AD632

Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Thermal Resistance .......................................................................5

Applications ....................................................................................... 1

Pin Configurations and Function Descriptions ............................6

Functional Block Diagram .............................................................. 1

Typical Performance Characteristics ..............................................7

General Description ......................................................................... 1

Operation As a Multiplier ................................................................8

Product Highlights ........................................................................... 1

Operation As a Divider .....................................................................9

Revision History ............................................................................... 2

Outline Dimensions ....................................................................... 10

Specifications..................................................................................... 3

Ordering Guide .......................................................................... 11

Absolute Maximum Ratings ............................................................ 5

REVISION HISTORY

5/13Rev. C to Rev. D

Changes to Table 1 ............................................................................. 3

Changes to Ordering Guide ...........................................................11

12/11Rev. B to Rev. C

Updated Format .................................................................. Universal

Added Figure 1, Renumbered Sequentially ................................... 1

Deleted Chip Dimensions and Pad Layout Section ...................... 5

Changes to Figure 3 and Figure 4 ................................................... 6

Added Table 3 and Table 4 .............................................................. 6

Changes to the Operations as a Divider Section .......................... 9

Updated Outline Dimensions ....................................................... 10

4/10Rev. A to Rev. B

Changes to Pin Configurations and Product Highlights

Sections .............................................................................................. 1

Changes to Thermal Characteristics Section ................................ 3

Updated Outline Dimensions ......................................................... 6

Changes to Ordering Guide ............................................................ 6

Rev. D | Page 2 of 12

Data Sheet

AD632

SPECIFICATIONS

@ +25C, VS = 15 V, R 2 k, unless otherwise noted. Specifications shown in boldface are tested on all production units at final

electrical test. Results from those tests are used to calculate outgoing quality levels.

Table 1.

Parameter

MULTIPLIER PERFORMANCE

Transfer Function

Min

AD632A

Typ

Max

( X1 X 2 ) (Y1 Y2 )

10 V

Total Error 1 (10 V X, Y +10

V)

TA = Min to Max

Total Error vs. Temperature

Scale Factor Error

(SF = 10,000 V Nominal) 2

Temperature Coefficient of

Scaling Voltage

Supply Rejection (15 V 1 V)

Nonlinearity

X (X = 20 V p-p, Y = 10 V)

Y (Y = 20 V p-p, X = 10 V)

Feedthrough 3

X (Y Nulled, X = 20 V p-p 50 Hz)

Y (X Nulled, Y = 20 V p-p 50 Hz)

Output Offset Voltage

Output Offset Voltage Drift

DYNAMICS

Small Signal BW, (VOUT = 0.1 rms)

1% Amplitude Error

(CLOAD = 1000 pF)

Slew Rate (VOUT 20 p-p)

Settling Time (to 1%, VOUT = 20 V)

NOISE

Noise Spectral Density

SF = 10 V

SF = 3 V 4

Wideband Noise

A = 10 Hz to 5 MHz

P = 10 Hz to 10 kHz

OUTPUT

Output Voltage Swing

Output Impedance (f 1 kHz)

Output Short-Circuit Current

(RL = 0, TA = Min to Max)

Amplifier Open-Loop Gain

(f = 50 Hz)

INPUT AMPLIFIERS (X, Y, and Z) 5

Signal Voltage Range

(Differential or CommonMode Operating Diff.)

Offset Voltage X, Y

Offset Voltage Drift X, Y

Offset Voltage Z

Offset Voltage Drift Z

CMRR

Bias Current

Offset Current

Differential Resistance

+ Z2

Min

AD632B

Typ

Max

( X1 X 2 ) (Y1 Y2 )

10 V

1.0

AD632S

Typ

Max

( X1 X 2 ) (Y1 Y2 )

10 V

0.5

+ Z2

Min

AD632T

Typ

Max

( X1 X 2 ) (Y1 Y2 )

10 V

Units

+ Z2

1.0

0.5

2.0

0.02

1.0

0.01

%

%/C

0.005

%

%/C

1.5

0.022

1.0

0.015

0.25

0.02

0.1

0.01

0.25

0.2

0.1

0.01

0.01

0.01

0.01

0.4

0.2

0.2

0.1

0.3

0.1

0.4

0.2

0.2

0.1

0.3

0.1

%

%

0.3

0.01

5

200

0.15

0.01

2

100

0.3

0.1

15

0.3

0.01

5

0.15

0.01

2

0.3

0.1

15

300

%

%

mV

V/C

30

30

500

1

50

1

50

1

50

1

50

MHz

kHz

20

2

20

2

20

2

20

2

V/s

s

0.8

0.4

0.8

0.4

0.8

0.4

0.8

0.4

V/Hz

V/Hz

1.0

90

1.0

90

1.0

90

1.0

90

mV/rms

V/rms

11

60

+ Z2

Min

11

11

11

0.1

0.1

0.1

0.1

30

70

30

70

30

70

30

70

mA

dB

10

12

10

12

10

12

10

12

5

100

5

200

80

0.8

0.1

10

20

2

50

2

100

90

0.8

0.1

10

10

5

100

5

20

2

150

2

10

mV

V/C

mV

V/C

dM

A

A

M

30

70

2.0

15

60

2.0

Rev. D | Page 3 of 12

80

0.8

0.1

10

30

500

70

2.0

90

0.8

0.1

10

15

300

2.0

AD632

Data Sheet

Parameter

DIVIDER PERFORMANCE

Transfer Function(X1 > X2)

AD632A

Typ

Max

Min

10V

Total Error1

(X = 10 V, 10 V Z +10 V)

(X = 1 V, 1 V Z +1 V)

(0.1 V X 10 V, 10 V Z

10 V)

SQUARER PERFORMANCE

Transfer Function

(Z 2 Z 1 )

( X1 X 2 )

10 V

Total Error (10 V X 10 V)

SQUARE-ROOTER PERFORMANCE

Transfer Function, (Z1 Z2)

10V

10 V

+ Y1

10V

10 V

10 V

Figures given are percent of full-scale, 10 V (that is, 0.01% = 1 mV).

Can be reduced to 3 V using an external resistor between VS and SF.

3

Irreducible component due to nonlinearity: excludes effect of offsets.

4

Using an external resistor adjusted to give a value of SF = 3 V.

5

See the functional block diagram (Figure 1) for definition of sections.

1

2

Rev. D | Page 4 of 12

%

%

%

+ Z2

10 V(Z 2 Z 1 ) + X 2

0.5

15

Units

+ Y1

0.3

22

4

( X1 X 2 )

( X 1 X 2 )2

+ Z2

15

8

(Z 2 Z 1 )

0.35

1.0

1.0

1.0

18

4

10V

10 V(Z 2 Z 1 ) + X 2

15

8

+ Y1

0.6

0.5

18

( X1 X 2 )

( X 1 X 2 )2

+ Z2

10 V(Z 2 Z 1 ) + X 2

15

(Z 2 Z 1 )

AD632T

Typ

Max

Min

0.75

2.0

2.5

0.3

1.0

( X1 X 2 )

( X 1 X 2 )2

+ Z2

10 V(Z 2 Z 1 ) + X 2

(Z 2 Z 1 )

AD632S

Typ

Max

Min

0.35

1.0

1.0

0.6

Total Error (1 V Z 10 V)

POWER SUPPLY SPECIFICATIONS

Supply Voltage

Rated Performance

Operating

Supply Current

Quiescent

+ Y1

0.75

2.0

2.5

( X 1 X 2 )2

AD632B

Typ

Max

Min

8

4

22

V

V

mA

Data Sheet

AD632

ABSOLUTE MAXIMUM RATINGS

THERMAL RESISTANCE

JA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 2. Thermal Resistance

Package Type

10-Lead TO-100

14-Lead SBDIP

JA

150

95

JC

25

25

Unit

C/W

C/W

Rev. D | Page 5 of 12

AD632

Data Sheet

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

+VS

7

1

AD632

2

3

Z1

(Not to Scale)

X2

VS 3

OUT

13 Y1

AD632

12 Y2

TOP VIEW

11 VOS

(Not to Scale)

NC 5

10 Z2

NC 4

X1

5

4

14 +VS

OUT 2

VS

09040-001

Y1

Z1 1

Z2 (GND)

9

10

NC 6

X2

X1 7

NC

NC = NO CONNECT

09040-002

VOS

Y2

Figure 3. Pin Configuration, D-Package, SBDIP

Figure 2. Pin Configuration, H-Package, TO-100

Table 3. Pin Function Descriptions, 10-Pin TO-100

Table 4. Pin Function Descriptions, 14-Lead SBDIP

Pin No.

1

2

3

4

5

6

7

8

9

10

Pin No.

1

2

3

4, 5, 6, 8

Mnemonic

Z1

OUT

VS

NC

7

9

10

11

12

13

14

X1

X2

Z2

VOS

Y2

Y1

+VS

Mnemonic

Y1

+VS

Z1

OUT

VS

X1

X2

Z2

VOS

Y2

Description

Y Multiplicand Noninverting Input.

Positive Supply Voltage.

Summing Node Noninverting Input.

Product.

Negative Supply Voltage.

X Multiplicand Noninverting Input.

X Multiplicand Inverting Input.

Summing Node Inverting Input.

Offset Voltage Adjustment.

Y Multiplicand Inverting Input.

Rev. D | Page 6 of 12

Description

Summing Node Noninverting Input.

Product.

Negative Supply Voltage.

No Connection. Do not connect to

this pin.

X Multiplicand Noninverting Input.

X Multiplicand Noninverting Input.

Summing Node Inverting Input.

Offset Voltage Adjustment.

Y Multiplicand Inverting Input.

Y Multiplicand Noninverting Input.

Positive Supply Voltage.

Data Sheet

AD632

TYPICAL PERFORMANCE CHARACTERISTICS

Typical @ 25C with VS = 15 V.

1000

40

20

VX = 1V DC

VZ = 100mV rms

0dB = 1V rms, RL = 2k

VX = 10V DC

VZ = 1V rms

100

1k

10k

100k

FREQUENCY (Hz)

1M

20

1k

10M

Figure 4. AC Feedthrough vs. Frequency

0

CL = 1000pF

CL = 0pF

CL 1000pF

CF 200pF

CL 1000pF

CF = 0pF

20

30

10k

NORMAL

CONNECTION

09040-005

WITH 10

FEEDBACK

ATTENUATOR

100k

1M

FREQUENCY (Hz)

100k

FREQUENCY (Hz)

1M

10M

Figure 6. Frequency Response vs. Divider Denominator Input Voltage

0dB = 0.1V rms, RL = 2k

10

10k

09040-006

0.1

10

OUTPUT RESPONSE (dB)

VX = 100mV DC

VZ = 10mV rms

VO

)

Vz

OUTPUT (dB

X FEEDTHROUGH

10

09040-004

FEEDTHROUGH (mV p-p)

Y FEEDTHROUGH

100

10M

Figure 5. Frequency Response as a Multiplier

Rev. D | Page 7 of 12

AD632

Data Sheet

OPERATION AS A MULTIPLIER

A much lower scaling voltage can be achieved without any reduction of input signal range using a feedback attenuator, as shown

in Figure 8. In this example, the scale is such that VOUT = XY, so

that the circuit can exhibit a maximum gain of 10. This connection

results in a reduction of bandwidth to about 80 kHz without the

peaking capacitor, CF. In addition, the output offset voltage is

increased by a factor of 10 making external adjustments necessary

in some applications.

X1

+VS

+15V

X2

OUT

VOS

OUTPUT, 12V PK

(X X2) (Y1 Y2)

+ Z2

= 1

10

Z1

OPTIONAL SUMMING

INPUT, Z, 10V PK;

VOS TERMINAL

NOT USED

Z2

Y INPUT

10V FS

12V PK

Y1

Y2

VS

15V

09040-008

X INPUT

10V FS

12V PK

Figure 7. Basic Multiplier Connection

Feedback attenuation also retains the capability for adding a

signal to the output. Signals can be applied to the Z terminal,

where they are amplified by 10, or to the common ground

connection where they are amplified by 1. Input signals can

also be applied to the lower end of the 2.7 k resistor, giving a

gain of +9.

When needed, the user can reduce ac feedthrough to a minimum

(as in a suppressed carrier modulator) by applying an external

trim voltage (30 mV range required) to the X or Y input. Figure 4

shows the typical ac feedthrough with this adjustment mode.

Note that the feedthrough of the Y input is a factor of 10 lower

than that of the X input and is to be used for applications where

null suppression is critical.

The Z2 terminal of the AD632 can be used to sum an additional

signal into the output. In this mode, the output amplifier behaves

as a voltage follower with a 1 MHz small signal bandwidth and

a 20 V/s slew rate. Always reference this terminal to the ground

point of the driven system, particularly if this is remote. Likewise, reference the differential inputs to their respective signal

common potentials to realize the full accuracy of the AD632.

Rev. D | Page 8 of 12

X INPUT

10V FS

12V PK

X1

+VS

+15V

X2

OUT

OUTPUT, 12V PK

= (X1 X2) (Y1 Y2)

(SCALE = 1)

Z1

Z2

Y INPUT

10V FS

12V PK

Y1

VOS

Y2

VS

15V

Figure 8. Connections for Scale Factor of Unity

09040-009

Figure 7 shows the basic connection for multiplication. Note

that the circuit meets all specifications without trimming.

Data Sheet

AD632

OPERATION AS A DIVIDER

Figure 9 shows the connection required for division. Unlike

earlier products, the AD632 provides differential operation on

both the numerator and the denominator, allowing the ratio of

two floating variables to be generated. Further flexibility results

from access to a high impedance summing input to Y1. As with

all dividers based on the use of a multiplier in a feedback loop,

the bandwidth is proportional to the denominator magnitude,

as shown in Figure 6.

X INPUT

(DENOMINATOR)

+10V FS

+12V PK

+15V

2k

TO

200k

OPTIONAL

15V

SUMMING INPUT

10V PK

+VS

+15V

OUTPUT, 12V PK

10 (Z2 Z1)

+ Y1

=

(X1 X2)

X2

+VS

OUT

VOS

Z1

VS

Z2

Z INPUT

(NUMERATOR)

10V FS, 12V PK

Y1

Y2

VS

15V

09040-010

The accuracy of the AD632 B-model is sufficient to maintain a

1% error over a 10 V to 1 V denominator range.

X1

Figure 9. Basic Divider Connection

Rev. D | Page 9 of 12

AD632

Data Sheet

OUTLINE DIMENSIONS

0.005 (0.13) MIN

0.080 (2.03) MAX

8

14

1

PIN 1

0.200 (5.08)

MAX

0.310 (7.87)

0.220 (5.59)

0.100 (2.54)

BSC

0.765 (19.43) MAX

0.200 (5.08)

0.125 (3.18)

0.023 (0.58)

0.014 (0.36)

0.070 (1.78)

0.030 (0.76)

0.320 (8.13)

0.290 (7.37)

0.060 (1.52)

0.015 (0.38)

0.150

(3.81)

MIN

SEATING

PLANE

0.015 (0.38)

0.008 (0.20)

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 10. 14-Lead Side-Brazed Ceramic Dual In-Line Package [SBDIP]

(D-14)

Dimensions shown in inches and (millimeters)

REFERENCE PLANE

0.500 (12.70)

MIN

0.185 (4.70)

0.165 (4.19)

0.160 (4.06)

0.110 (2.79)

0.335 (8.51)

0.305 (7.75)

0.370 (9.40)

0.335 (8.51)

5

0.021 (0.53)

0.016 (0.40)

0.115

(2.92)

BSC

8

4

9

0.045 (1.14)

0.025 (0.65)

3

2

0.040 (1.02) MAX

BASE & SEATING PLANE

10

1

0.034 (0.86)

0.025 (0.64)

0.230 (5.84)

BSC

36 BSC

DIMENSIONS PER JEDEC STANDARDS MO-006-AF

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 11. 10-Pin Metal Header Package [TO-100]

(H-10)

Dimensions shown in inches and (millimeters)

Rev. D | Page 10 of 12

022306-A

0.050 (1.27) MAX

Data Sheet

AD632

ORDERING GUIDE

Model 1

AD632AD

AD632ADZ

AD632AHZ

AD632BD

AD632BDZ

AD632BHZ

AD632SD

AD632SH

AD632SH/883B

AD632TD

AD632TD/883B

AD632TH

AD632TH/883B

1

Temperature Range

25C to +85C

25C to +85C

25C to +85C

25C to +85C

25C to +85C

25C to +85C

55C to +125C

55C to +125C

55C to +125C

55C to +125C

55C to +125C

55C to +125C

55C to +125C

Package Description

14-Lead Side-Brazed Ceramic Dual In-Line Package [SBDIP]

14-Lead Side-Brazed Ceramic Dual In-Line Package [SBDIP]

10-Pin Metal Header Package [TO-100]

14-Lead Side-Brazed Ceramic Dual In-Line Package [SBDIP]

14-Lead Side-Brazed Ceramic Dual In-Line Package [SBDIP]

10-Pin Metal Header Package [TO-100]

14-Lead Side-Brazed Ceramic Dual In-Line Package [SBDIP]

10-Pin Metal Header Package [TO-100]

10-Pin Metal Header Package [TO-100]

14-Lead Side-Brazed Ceramic Dual In-Line Package [SBDIP]

14-Lead Side-Brazed Ceramic Dual In-Line Package [SBDIP]

10-Pin Metal Header Package [TO-100]

10-Pin Metal Header Package [TO-100]

Z = RoHS Compliant Part.

Rev. D | Page 11 of 12

Package Option

D-14

D-14

H-10

D-14

D-14

H-10

D-14

H-10

H-10

D-14

D-14

H-10

H-10

AD632

Data Sheet

NOTES

19792013 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D09040-0-5/13(D)

Rev. D | Page 12 of 12

También podría gustarte

- Ad8421 PDFDocumento28 páginasAd8421 PDFsoft4gsmAún no hay calificaciones

- Low Cost 1.2 G Dual Axis Accelerometer ADXL213: Features General DescriptionDocumento13 páginasLow Cost 1.2 G Dual Axis Accelerometer ADXL213: Features General DescriptionJose Adolfo Monteverde SalazarAún no hay calificaciones

- AD623Documento24 páginasAD623Humberto PachecoAún no hay calificaciones

- Low Cost Analog Multiplier: AD633JN/AD633ANDocumento8 páginasLow Cost Analog Multiplier: AD633JN/AD633ANNarendra BholeAún no hay calificaciones

- Ad 536 ADocumento8 páginasAd 536 AlamikkAún no hay calificaciones

- Features Description: Sbfs017A - December 1995 - Revised December 2004Documento15 páginasFeatures Description: Sbfs017A - December 1995 - Revised December 2004LasithaAún no hay calificaciones

- Ad633 Multiplicador AnalogicoDocumento8 páginasAd633 Multiplicador AnalogicombocoAún no hay calificaciones

- ADXL210Documento11 páginasADXL210JaehyupKimAún no hay calificaciones

- AD623ANDocumento16 páginasAD623ANmeroka2000Aún no hay calificaciones

- Iso122sensor de TensionDocumento15 páginasIso122sensor de TensionRichard ZerpaAún no hay calificaciones

- Adxl103 203Documento16 páginasAdxl103 203herbertmgAún no hay calificaciones

- Precision Instrumentation Amplifier AD524: Features Functional Block DiagramDocumento28 páginasPrecision Instrumentation Amplifier AD524: Features Functional Block Diagrammili111213Aún no hay calificaciones

- Integrated Circuit True RMS-to-DC Converter: C To +125 C Operation (AD536AS)Documento8 páginasIntegrated Circuit True RMS-to-DC Converter: C To +125 C Operation (AD536AS)Decker JamesAún no hay calificaciones

- AD22300, AD22301, AD22302: 3.3V Single and Dual Axis Automotive iMEMS AccelerometersDocumento5 páginasAD22300, AD22301, AD22302: 3.3V Single and Dual Axis Automotive iMEMS AccelerometersHugo D. Alvarez100% (1)

- Low Level, True RMS-to-DC Converter AD636: Features Functional Block DiagramDocumento16 páginasLow Level, True RMS-to-DC Converter AD636: Features Functional Block DiagramcblinceAún no hay calificaciones

- Adxrs610 Yaw Rate GyroDocumento12 páginasAdxrs610 Yaw Rate GyroTarek Car MillaAún no hay calificaciones

- AD8002 Data SheetDocumento21 páginasAD8002 Data SheetMartinCharlyAún no hay calificaciones

- LC MOS Single Supply, 12-Bit 600 KSPS ADC: S Conversion TimeDocumento14 páginasLC MOS Single Supply, 12-Bit 600 KSPS ADC: S Conversion TimeThang PhamAún no hay calificaciones

- Precision Instrumentation Amplifier: V P-P 0.1 HZ To 10 HZDocumento16 páginasPrecision Instrumentation Amplifier: V P-P 0.1 HZ To 10 HZManojChowdaryAún no hay calificaciones

- Iso 122Documento18 páginasIso 122rnjlmv83100% (1)

- Tda 9556Documento16 páginasTda 9556Miloud ChouguiAún no hay calificaciones

- High Performance, Wide Bandwidth Accelerometer ADXL001: FeaturesDocumento16 páginasHigh Performance, Wide Bandwidth Accelerometer ADXL001: FeaturesMago ChinesAún no hay calificaciones

- AD633 Analog MultiplierDocumento16 páginasAD633 Analog MultiplierCostel CostescuAún no hay calificaciones

- ADXL105 ADocumento9 páginasADXL105 AJuan Jose SaAún no hay calificaciones

- Adxl 278Documento12 páginasAdxl 278Dav1t1Aún no hay calificaciones

- AD7533Documento12 páginasAD7533Jose David Medina MartinezAún no hay calificaciones

- Ad 620Documento13 páginasAd 620flavioscrAún no hay calificaciones

- Low Cost, Low Power Instrumentation Amplifier AD620: 62.3 V To 618 V)Documento4 páginasLow Cost, Low Power Instrumentation Amplifier AD620: 62.3 V To 618 V)flavioscrAún no hay calificaciones

- Ad620 PDFDocumento16 páginasAd620 PDFRODRIGO TROCONISAún no hay calificaciones

- TLC 2201Documento69 páginasTLC 2201Laki LazaricAún no hay calificaciones

- +2.7 V To +5.5 V, 350 KSPS, 10-Bit 4-/8-Channel Sampling AdcsDocumento20 páginas+2.7 V To +5.5 V, 350 KSPS, 10-Bit 4-/8-Channel Sampling AdcsAbhishek ChaudharyAún no hay calificaciones

- 750 MHZ, 16 × 16 Analog Crosspoint Switch Adv3226/Adv3227: Features Functional Block DiagramDocumento24 páginas750 MHZ, 16 × 16 Analog Crosspoint Switch Adv3226/Adv3227: Features Functional Block Diagramwcma57Aún no hay calificaciones

- High-Linearity Analog Optocouplers: Technical DataDocumento19 páginasHigh-Linearity Analog Optocouplers: Technical DataBui Minh SinhAún no hay calificaciones

- RF Power Field Effect Transistors: MRFE6VP61K25HR6 MRFE6VP61K25HSR6Documento13 páginasRF Power Field Effect Transistors: MRFE6VP61K25HR6 MRFE6VP61K25HSR6Zoran DjuricAún no hay calificaciones

- AD8001Documento16 páginasAD8001sresciaAún no hay calificaciones

- Low Cost, Low Power Instrumentation Amplifier AD620 Connection Diagram and SpecsDocumento16 páginasLow Cost, Low Power Instrumentation Amplifier AD620 Connection Diagram and Specslogin38Aún no hay calificaciones

- Acelerometro ADXL103-ADXL203Documento12 páginasAcelerometro ADXL103-ADXL203cukey13Aún no hay calificaciones

- Low Noise, Low Gain Drift, G 2000 Instrumentation AmplifierDocumento20 páginasLow Noise, Low Gain Drift, G 2000 Instrumentation AmplifiervabecompAún no hay calificaciones

- Current Differential Relay ManualDocumento4 páginasCurrent Differential Relay Manualppraveenkumar79Aún no hay calificaciones

- Accelerometer DatsheetDocumento12 páginasAccelerometer DatsheetAlmadovar AlfonsoAún no hay calificaciones

- Strain Gauge Measuring Amplifier BA 662: ManualDocumento10 páginasStrain Gauge Measuring Amplifier BA 662: ManualReza RezaAún no hay calificaciones

- Ad 630Documento13 páginasAd 630Antonio PerezAún no hay calificaciones

- ADXL326 AcelerometroDocumento16 páginasADXL326 AcelerometroGerman GodiAún no hay calificaciones

- Medical Ecg Ina326Documento23 páginasMedical Ecg Ina326ronny5525Aún no hay calificaciones

- 3312 Panel Instrument 3771Documento12 páginas3312 Panel Instrument 3771JoséAún no hay calificaciones

- Low Cost, Low Power Instrumentation Amplifier AD620: 62.3 V To 618 V)Documento7 páginasLow Cost, Low Power Instrumentation Amplifier AD620: 62.3 V To 618 V)flavioscrAún no hay calificaciones

- Ad 620Documento16 páginasAd 620Jesus Ismael MendezAún no hay calificaciones

- Service Manual: HD-52G787, HD-52G887, HD-56G787, HD-56G887, HD-61G787, HD-61G887Documento205 páginasService Manual: HD-52G787, HD-52G887, HD-56G787, HD-56G887, HD-61G787, HD-61G887Rick Costa100% (1)

- THS4051, THS4052 70-Mhz High-Speed Amplifiers: DescriptionDocumento25 páginasTHS4051, THS4052 70-Mhz High-Speed Amplifiers: DescriptionSaadAhmedBeihaqiAún no hay calificaciones

- FN 7925Documento14 páginasFN 7925praveen_banthiAún no hay calificaciones

- TSL257S DatasheetDocumento9 páginasTSL257S DatasheetAndresPalaciosAún no hay calificaciones

- 9-0-9 Step Down TransformerDocumento20 páginas9-0-9 Step Down TransformerSarthak JoshiAún no hay calificaciones

- 110 Waveform Generator Projects for the Home ConstructorDe Everand110 Waveform Generator Projects for the Home ConstructorCalificación: 4 de 5 estrellas4/5 (1)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDe EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsAún no hay calificaciones

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Aún no hay calificaciones

- Ifac2012 Working With Time-Delay Systems in MATLAB Suat GumussoyDocumento6 páginasIfac2012 Working With Time-Delay Systems in MATLAB Suat GumussoyBouazizi HechmiAún no hay calificaciones

- Apkarian LMIDocumento129 páginasApkarian LMIBouazizi HechmiAún no hay calificaciones

- A Finite Zero Exclusion PrincipleDocumento2 páginasA Finite Zero Exclusion PrincipleBouazizi HechmiAún no hay calificaciones

- Full Order LPVH Observers For LPV Time-Delay SysteDocumento6 páginasFull Order LPVH Observers For LPV Time-Delay SysteBouazizi HechmiAún no hay calificaciones

- New Extended LMI Characterization For State Feedback Control of Continuous-Time Uncertain Linear SystemsDocumento6 páginasNew Extended LMI Characterization For State Feedback Control of Continuous-Time Uncertain Linear SystemsBouazizi HechmiAún no hay calificaciones

- Jensen's and Wirtinger's Inequalities For Time-Delay SystemsDocumento7 páginasJensen's and Wirtinger's Inequalities For Time-Delay SystemsBouazizi HechmiAún no hay calificaciones

- Induced - Norm Observer-Based Controller Design For Continuous-Time Polytopic LPV SystemsDocumento5 páginasInduced - Norm Observer-Based Controller Design For Continuous-Time Polytopic LPV SystemsBouazizi HechmiAún no hay calificaciones

- Sciencedirect: © 2017, Ifac (International Federation of Automatic Control) Hosting by Elsevier Ltd. All Rights ReservedDocumento6 páginasSciencedirect: © 2017, Ifac (International Federation of Automatic Control) Hosting by Elsevier Ltd. All Rights ReservedBouazizi HechmiAún no hay calificaciones

- 2008 Jensen Integral Inequality Approach To Stability Analysis of Continuous-Time Systems With Time-Varying Delay X.L.ZhuDocumento11 páginas2008 Jensen Integral Inequality Approach To Stability Analysis of Continuous-Time Systems With Time-Varying Delay X.L.ZhuBouazizi HechmiAún no hay calificaciones

- Ad632 PDFDocumento12 páginasAd632 PDFBouazizi HechmiAún no hay calificaciones

- Sciencedirect: © 2017, Ifac (International Federation of Automatic Control) Hosting by Elsevier Ltd. All Rights ReservedDocumento6 páginasSciencedirect: © 2017, Ifac (International Federation of Automatic Control) Hosting by Elsevier Ltd. All Rights ReservedBouazizi HechmiAún no hay calificaciones

- Fault Detection Observer Design For A Polytopic LPV System Using The Relative DegreeDocumento13 páginasFault Detection Observer Design For A Polytopic LPV System Using The Relative DegreeBouazizi HechmiAún no hay calificaciones

- A Course in Robust Control Theory PDFDocumento380 páginasA Course in Robust Control Theory PDFDenis Hinojosa ZeballosAún no hay calificaciones

- A Course in Robust Control Theory PDFDocumento380 páginasA Course in Robust Control Theory PDFDenis Hinojosa ZeballosAún no hay calificaciones

- Ceragon 3200T Installation - GuideDocumento99 páginasCeragon 3200T Installation - GuideFabricio VilelaAún no hay calificaciones

- Camera Accessories - Quick Selection GuideDocumento39 páginasCamera Accessories - Quick Selection GuidecarlosAún no hay calificaciones

- MITSUBISHI - Manual - PLC - Iq-R - SLMP Connect C# MrJ4BDocumento232 páginasMITSUBISHI - Manual - PLC - Iq-R - SLMP Connect C# MrJ4Bca bienAún no hay calificaciones

- (Slides Note) 09 ISFT Acquisition and Preservation VE - MHHDocumento40 páginas(Slides Note) 09 ISFT Acquisition and Preservation VE - MHHsdfd84932Aún no hay calificaciones

- DesignDocumento126 páginasDesignbelayAún no hay calificaciones

- 02-PAS-Fundamentals-The VaultDocumento33 páginas02-PAS-Fundamentals-The VaultOliver QuiambaoAún no hay calificaciones

- Ecodrive FinalDocumento24 páginasEcodrive FinalChris WrightAún no hay calificaciones

- Table ListDocumento4 páginasTable ListRidho Saputro HutomoAún no hay calificaciones

- FAQ 117 DDX9121b Advanced Data AnalysisDocumento6 páginasFAQ 117 DDX9121b Advanced Data AnalysisAlessandro SouzaAún no hay calificaciones

- Maincon Control Software Load Mill Ver17 and Lathe Ver10Documento10 páginasMaincon Control Software Load Mill Ver17 and Lathe Ver10Hau Le TrungAún no hay calificaciones

- Lecture Schedule Subject: Linear Integrated Circuits Subject Code: L503 Name of Staff: Assini.HDocumento3 páginasLecture Schedule Subject: Linear Integrated Circuits Subject Code: L503 Name of Staff: Assini.HAssini HussainAún no hay calificaciones

- SIMOTION Diagnostics V2 0 enDocumento43 páginasSIMOTION Diagnostics V2 0 enabirajesh100% (1)

- Fujitsu Stylistic q584Documento8 páginasFujitsu Stylistic q584conmar5mAún no hay calificaciones

- B1 - Overlay Virtual Networking and SDDCDocumento278 páginasB1 - Overlay Virtual Networking and SDDCdownloadpostaAún no hay calificaciones

- S272 User Manual V2.5Documento49 páginasS272 User Manual V2.5Lauren AdolfAún no hay calificaciones

- Devicenet en PDFDocumento156 páginasDevicenet en PDFgapam_2Aún no hay calificaciones

- Remote Method InvocationDocumento2 páginasRemote Method InvocationArif MohmmadAún no hay calificaciones

- Dhamdhere OS2E Chapter 02 PowerPoint SlidesDocumento73 páginasDhamdhere OS2E Chapter 02 PowerPoint SlidesManjunath MaddyAún no hay calificaciones

- BCT Mini ProjDocumento12 páginasBCT Mini Projprathamshelke53Aún no hay calificaciones

- 55-102 NumpyDocumento48 páginas55-102 NumpyRap ImaginAún no hay calificaciones

- RE 615ANSI DNP-3 Communication Manual 065952Documento44 páginasRE 615ANSI DNP-3 Communication Manual 065952Papun Kumar SwainAún no hay calificaciones

- Brushless motor速通门Documento19 páginasBrushless motor速通门Oscar Antonio Osses VargasAún no hay calificaciones

- Computer Architecture - Notes2Documento101 páginasComputer Architecture - Notes2Sheela SajAún no hay calificaciones

- Automatic Speed Controlling System Using IoTDocumento3 páginasAutomatic Speed Controlling System Using IoTInternational Journal of Innovative Science and Research TechnologyAún no hay calificaciones

- Wave Shaping and Swiching CircuitsDocumento3 páginasWave Shaping and Swiching Circuitskaran007_mAún no hay calificaciones

- Elevating Workflow Efficiency: The New Imagerunner 1643if Ii & 1643I IiDocumento4 páginasElevating Workflow Efficiency: The New Imagerunner 1643if Ii & 1643I Iisanjay4u4allAún no hay calificaciones

- Wipro NTH FAQsDocumento9 páginasWipro NTH FAQssudhuAún no hay calificaciones

- 2Documento16 páginas2tarunAún no hay calificaciones

- LogDocumento13 páginasLogMis DeptAún no hay calificaciones

- The IF ElseDocumento2 páginasThe IF ElsecyberomiAún no hay calificaciones