Documentos de Académico

Documentos de Profesional

Documentos de Cultura

(Journal) Design and Implementation of Zigbee Transmitter On Fpga Using VHDL

Cargado por

FranxCuckooTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

(Journal) Design and Implementation of Zigbee Transmitter On Fpga Using VHDL

Cargado por

FranxCuckooCopyright:

Formatos disponibles

DESIGN AND IMPLEMENTATION OF

ZIGBEE TRANSMITTER ON FPGA USING VHDL

1

PUNIT RAMACHANDRA RAMAJI, 2MANJUNATH G ASUTI

1

M-Tech VLSI Design and Embedded Systems, RITM Bangalore

2

Assistant Professor ECE Dept, RITM Bangalore

Abstract- This paper explores the implementation of a digital transmitter for 2.4 GHz Zigbee IEEE 802.15.4 applications on

a field programmable gate array (FPGA) for an Acknowledgement frame. Zigbee technology was developed for a

Wireless Personal Area Networks (WPAN), aimed at control and military applications with low data rate and low power

consumption. Zigbee is a standard defines the set of communication protocols for low data-rate, short-range wireless

networking. Zigbee based wireless devices operate in 868 MHz, 915 MHz, and 2.4 GHz frequency bands. Digital Zigbee

Transmitter comprises of Cyclic Redundancy Check, Bit-to-Symbol block, Symbol-to-chip block, Offset QPSK Modulator.

The work here is to show how we can design Zigbee transmitter with its specifications by using VHDL code through Xilinx

ISE version 12 was developed to design these blocks.

I. INTRODUCTION

Zigbee is a low data rate, low power, and low cost

wireless networking protocol based on the IEEE

802.15.4, which is a set of new communication

protocols for wireless transmission. Zigbee protocol

defines the media access control (MAC) and physical

(PHY) layers for low rate WPANs. It supports the

frequency bands 868 MHz for European countries,

915 MHz for the United States, and 2.4 GHz for

worldwide.

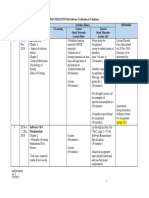

Figure1. The acknowledgment frame

The acknowledge frame used contains 11 octets (i.e.

88 bits) of physical protocol data unit (PPDU). The

binary data from the PPDU packet are inserted into

the cyclic redundancy check block to detect errors

during transmission. The Cyclic Redundancy Check is

the most powerful of the redundancy checking

techniques, the CRC is based on binary division. In

CRC a sequence of redundant bits, called the CRC or

the CRC remainder is appended to the end of a data

stream. The resulting data becomes exactly divisible

by a second, predetermined binary number. At its

destination, the incoming data is divided by the same

number.

Main network topologies used in ZigBee wireless

networking are star and peer-to-peer networks. In the

star topology, every device in the network can

communicate only with the personal area network

coordinator. A Full Function Device takes up a role as

PAN coordinator; the other nodes can be Reduced

Function Device or Function Device. In the peer-topeer topology, each device can communicate directly

with any other device if the devices are close enough

together to establish a successful communication link.

Any Function Device in this topology can play the

role of the personal area network coordinator.

The diagram below will show you the Sequence of

Events that takes place when using CRC. CRCs can

detect all one bits and two bits errors as well as all odd

number of bits in error. Since CRC is a technique for

detecting errors, but not for making corrections when

errors are detected, the whole packet data will be

retransmitted if error occurs. For Zigbee Standard,

CRC involves a division of the transmitted packet data

by a constant called the generator polynomial. The

CRC block contains the SHR, PHR and PHY payload.

In the PHY payload, the FCS mechanism employs a

16-bit CRC in order to detect errors. The FCS is

calculated over the MHR and MFR payload parts of

the frame using the algorithm Every four bits of

PPDU octet are mapped onto one data symbol, which

will take place in bit-to-symbol block. The symbols

Zigbee digital transmitter in 2.4GHz band is designed

using VHDL for acknowledgement frame. MAC

frame structures consist of beacon, data,

acknowledgment, and MAC command frames. The

MAC layer defines two types of nodes: Reduced

Function Devices and Full Function Devices .The

beacon frame is used by a coordinator to transmit

beacons.

The function of beacons is to synchronize the clock of

all the devices within the same network. The data

frame is used to transmit data. Meanwhile, the

acknowledgement frame is used to confirm successful

frame reception. The Zigbee digital transmitter is

designed for acknowledgment frame which is shown

in Figure 1 based on IEEE 802.15.4standard.

Proceedings of 10th IRF International Conference, 01st June-2014, Pune, India, ISBN: 978-93-84209-23-0

148

Design and Implementation of Zigbee Transmitter on FPGA Using VHDL

will be spread into 32-chip PN sequence by utilizing

Direct Sequence Spread Spectrum method in Symbolto-chip block. Then, the chips will be modulated using

OQPSK technique.

frames which is originated from MAC sub-layer is

inserted into the CRC block. Then, every 4 bits are

mapped into one data symbol in the bit-to-symbol

block. The symbol-to-chip block performs the DSSS

where each symbol is mapped into a 32-chip PN

sequence as shown in Table 1. After that, these chips

are processed by OQPSK (Offset Quadrature Phase

Shift Keyed) modulator.

Fig 3: Transmitter Architecture

II. DESIGN METHODOLOGY

The behaviour of the Zigbee digital transmitter can be

modelled using VHDL through Xilinx ISE. The

VHDL module for each transmitter can be combined,

then synthesized, simulated, and implemented on

Spartan3E FPGA.

OQPSK (offset QPSK) is a special version of QPSK

in which the transmitted signal has no amplitude

modulation. This disadvantage of a amplitude

modulation are a result of 180 shifting in the phase.

In OQPSK the incoming signal is divided in the

modulator into two portions I and Q which are then

transmitted shifted by a half symbol duration. The

phase plane of a OQPSK is shown in Figure 2. There

is no phase shift through the zero crossing which

means there are no phase shifts by 180 as in a

standard QPSK.

The input data comprise 22 symbols. Each data

symbol from the bit-to-symbol block is append onto

a 32-chip PN sequence using the DSSS method. The

output data are 704 chips in total with the frequency of

2 MHz . The numbers of chips produced are based

on[88 bits/4] symbols x 32 = 704 chips Based on this

equation, each even chip of output data is registered as

C0, C2 .. C704, and each odd chip is registered as

C1, C3 C703, which is totally 352 chips each for Iphase and Q-phase.

III. RESULTS AND DISCUSSION

Simulation and implementation were performed for

the digital Transmitter. The output waveforms were

compared to verify their functionality. The simulation

waveform shown in below Figure.

Waveform for Transmitter Data Bits

Figure 3: Cyclic Redundancy Check

Table 1: Symbol to chip mapping using DSSS

The proposed digital transceiver for Zigbee

applications is shown in Fig 3. The acknowledgment

Waveform for BIT-TO-SYMBOL Simulation

Proceedings of 10th IRF International Conference, 01st June-2014, Pune, India, ISBN: 978-93-84209-23-0

149

Design and Implementation of Zigbee Transmitter on FPGA Using VHDL

CONCLUSION

This paper shows the VHDL based design of digital

transmitter for 2.4GHz band Zigbee applications. The

behaviour of CRC and Bit-to-symbol were

characterized using VHDL. The functionality of the

proposed transmitter matches its theoretical

expectation. With VHDL, the transmitter design area

could be reduced to a smaller scale.

REFERENCES

[1]

Zigbee Alliance, available at: www.zigbee.org.

[2]

A. Mohammed Mian and Divyabharathi. R, Design and

Simulation of ZIGBEE Transmitter Using Verilog

[3]

RAFIDAH AHMAD*, OTHMAN SIDEK, SHUKRI

KORAKKOTTIL KUNHI MOHD, IMPLEMENTATION

OF A VERILOG-BASED DIGITAL RECEIVER FOR 2.4

GHz ZIGBEE APPLICATIONS ON FPGA

[4]

Somya Goel1, Dr Ranjit Singh2, FIETE, VHDL Based

Design and Implementation of Zigbee Transreceiver on

FPGA

[5]

Wireless Communications: The Future William Webb

2007 John Wiley & Sons, Ltd. ISBN: 0-470-03312-6

[6]

Rafidah Ahmad, Othman Sidek, Wan Md. Hafizi Wan

Hassin, Shukri Korakkottil Kunhi Mohd, and Abdullah

Sanusi Husain, Verilog-Based Design and Implementation

of Digital Transmitter for Zigbee Applications

[7]

Alberto Camilli, Carlos E. Cugnasca, Antonio M. Saraiva,

Andre R. Hirakawa, Pedro L.P. Correa, From wireless

sensors to field mapping: Anatomy of an application for

precision agriculture.

Waveform for SYMBOL-TO-CHIP Simulation

Proceedings of 10th IRF International Conference, 01st June-2014, Pune, India, ISBN: 978-93-84209-23-0

150

También podría gustarte

- MyArcadePlugin Pro DocumentationDocumento65 páginasMyArcadePlugin Pro DocumentationAbdUllahAún no hay calificaciones

- Researchpaper OFDM Modulator For Wireless LAN WLAN StandardDocumento5 páginasResearchpaper OFDM Modulator For Wireless LAN WLAN Standardtsk4b7Aún no hay calificaciones

- Fuji DR IdDocumento112 páginasFuji DR IdMario Ramos0% (1)

- Chris Mills Practical CSS3 Develop and Design 2012 PDFDocumento352 páginasChris Mills Practical CSS3 Develop and Design 2012 PDFFranxCuckooAún no hay calificaciones

- Color Detection Using FPGA Based Smart CameraDocumento19 páginasColor Detection Using FPGA Based Smart Cameratry199Aún no hay calificaciones

- Using Usb Secondary Isp Bootloader PDFDocumento7 páginasUsing Usb Secondary Isp Bootloader PDFMainak SenAún no hay calificaciones

- What's New in CSS3 by Estelle WeylDocumento38 páginasWhat's New in CSS3 by Estelle Weylmartin_rr100% (1)

- RS232 CommunicationsDocumento37 páginasRS232 CommunicationsNoor Kareem100% (1)

- Design and Simulation of ZIGBEE TransmitterDocumento5 páginasDesign and Simulation of ZIGBEE TransmitterMahesh Kumar GAún no hay calificaciones

- Design and Simulation of State-Of-Art Zigbee Transmitter For Iot Wireless DevicesDocumento4 páginasDesign and Simulation of State-Of-Art Zigbee Transmitter For Iot Wireless DevicesEdgar A.BAún no hay calificaciones

- Ahmad 2009Documento4 páginasAhmad 2009Zoro ZoroAún no hay calificaciones

- Building Wireless Sensor Networks With Zigbee: Paper ID #7789Documento18 páginasBuilding Wireless Sensor Networks With Zigbee: Paper ID #7789krishAún no hay calificaciones

- Concatenated Coding in OFDM For Wimax Using USRP N210 and GNU RadioDocumento14 páginasConcatenated Coding in OFDM For Wimax Using USRP N210 and GNU RadioJohn Berg100% (1)

- FPGA Implementation of Convolutional Encoder and Hard Decision Viterbi DecoderDocumento5 páginasFPGA Implementation of Convolutional Encoder and Hard Decision Viterbi DecoderSiva KrishnaAún no hay calificaciones

- Design and Implement of QPSK Modem Based On FPGADocumento3 páginasDesign and Implement of QPSK Modem Based On FPGAAnil PatilAún no hay calificaciones

- Includes Report, Presentation,: SynopsysDocumento2 páginasIncludes Report, Presentation,: SynopsysasitAún no hay calificaciones

- MT - All CHP - Telecom MGMT - Question BankDocumento10 páginasMT - All CHP - Telecom MGMT - Question Bankseshu_baluAún no hay calificaciones

- OFDM in VerilogDocumento6 páginasOFDM in VerilogMarwan AhmedAún no hay calificaciones

- Turbo Encoder and Decoder Chip Design and FPGA Device Analysis For Communication SystemDocumento12 páginasTurbo Encoder and Decoder Chip Design and FPGA Device Analysis For Communication SystemIJRES teamAún no hay calificaciones

- Cots SDRDocumento7 páginasCots SDRsatya1220Aún no hay calificaciones

- Design Approach For VHDL and FPGA Implementation of Automotive Black Box Using CAN ProtocolDocumento5 páginasDesign Approach For VHDL and FPGA Implementation of Automotive Black Box Using CAN ProtocolRahul KarayiAún no hay calificaciones

- Performance Analysis of Wimax 802.16e Physical Layer Using Digital Modulation Techniques and Code RatesDocumento6 páginasPerformance Analysis of Wimax 802.16e Physical Layer Using Digital Modulation Techniques and Code RatesOluwaseunAún no hay calificaciones

- Software-Defined Radio Using XilinxDocumento5 páginasSoftware-Defined Radio Using XilinxNishant SinghAún no hay calificaciones

- Low Power Design of The Physical Layer of NarrowBand IoT LTE TransmitterDocumento7 páginasLow Power Design of The Physical Layer of NarrowBand IoT LTE Transmitteromnia taysirAún no hay calificaciones

- Fpga Implementation of Direct Sequence Spread SpectrumDocumento29 páginasFpga Implementation of Direct Sequence Spread SpectrumThirumal ArunAún no hay calificaciones

- ViterbiDocumento12 páginasViterbiDevanshu AnandAún no hay calificaciones

- Performance Evaluation of Zigbee Protocol Using Opnet Modeler For Mine SafetyDocumento5 páginasPerformance Evaluation of Zigbee Protocol Using Opnet Modeler For Mine SafetyijcsnAún no hay calificaciones

- Wireless Handheld Ordering Terminal Based On Embedded SystemDocumento6 páginasWireless Handheld Ordering Terminal Based On Embedded SystemGaurav PohujaAún no hay calificaciones

- Software Defined Radio Implementation of A DVB S Transceiver PaperDocumento5 páginasSoftware Defined Radio Implementation of A DVB S Transceiver PaperLalchand MangalAún no hay calificaciones

- Paper ID 45 - 45Documento12 páginasPaper ID 45 - 45Usman TariqAún no hay calificaciones

- Volume 1number 2PP 508 513Documento6 páginasVolume 1number 2PP 508 513Anubhav SinghAún no hay calificaciones

- Wireless Communication ZigbeeDocumento11 páginasWireless Communication ZigbeeChirag MistryAún no hay calificaciones

- Wind Band Radar Signal Using RF2051Documento8 páginasWind Band Radar Signal Using RF2051Khushal KharadeAún no hay calificaciones

- Data EncrytipnDocumento5 páginasData EncrytipnRajan MiglaniAún no hay calificaciones

- Communication Protocols Augmentation in VLSI Design ApplicationsDocumento5 páginasCommunication Protocols Augmentation in VLSI Design ApplicationsMoorthy VenkatachalamAún no hay calificaciones

- Design Low Power Physical Layer of NB-IOT LTE Uplink ReceiverDocumento5 páginasDesign Low Power Physical Layer of NB-IOT LTE Uplink Receiversadsadasdsad asdasda100% (1)

- FPGA-based Implementation of Efficient Sample Rate Conversion For Software Defined RadiosDocumento5 páginasFPGA-based Implementation of Efficient Sample Rate Conversion For Software Defined RadiosNitin MathurAún no hay calificaciones

- 263 Exp3 CNSDocumento15 páginas263 Exp3 CNSneha.shroffAún no hay calificaciones

- Design of LDPC Decoder Using FPGA: Review of Flexibility: Asisa Kumar Panigrahi, Ajit Kumar PandaDocumento6 páginasDesign of LDPC Decoder Using FPGA: Review of Flexibility: Asisa Kumar Panigrahi, Ajit Kumar PandaresearchinventyAún no hay calificaciones

- Embedded Lab: Wireless Data Transmission Between Two PIC Microcontrollers Using Low-Cost RF ModulesDocumento11 páginasEmbedded Lab: Wireless Data Transmission Between Two PIC Microcontrollers Using Low-Cost RF ModulesSumon DharaAún no hay calificaciones

- By Andrew Morgan at Labels:: April 02, 2014 LTEDocumento10 páginasBy Andrew Morgan at Labels:: April 02, 2014 LTEAsadKhanAún no hay calificaciones

- An Efficient Cordic Processor For Complex Digital Phase Locked LoopDocumento7 páginasAn Efficient Cordic Processor For Complex Digital Phase Locked LoopInternational Journal of Application or Innovation in Engineering & ManagementAún no hay calificaciones

- Simulation of Bask, BPSK, BFSK Modulators Using VerilogDocumento12 páginasSimulation of Bask, BPSK, BFSK Modulators Using VerilogJames MorenoAún no hay calificaciones

- Bit Error Optimization of Coded Ofdm System Over RDocumento10 páginasBit Error Optimization of Coded Ofdm System Over RzelalemaschaleyAún no hay calificaciones

- Design Low Power Physical Layer of NB-IOT LTE Uplink ReceiverDocumento17 páginasDesign Low Power Physical Layer of NB-IOT LTE Uplink Receiversadsadasdsad asdasdaAún no hay calificaciones

- Using A COTS SDR As A 5G Development Platform: Bob Muro, Pentek IncDocumento13 páginasUsing A COTS SDR As A 5G Development Platform: Bob Muro, Pentek IncAmericanPrideAún no hay calificaciones

- Dept. of Ece, Sreebuddha College of Engineering 1Documento34 páginasDept. of Ece, Sreebuddha College of Engineering 1SARATH MOHANDASAún no hay calificaciones

- 1 Design of Vegetable Greenhouse Monitoring System Based On Zigbee and GPRSDocumento4 páginas1 Design of Vegetable Greenhouse Monitoring System Based On Zigbee and GPRSESP32 CAMAún no hay calificaciones

- 50ICRASE130513Documento4 páginas50ICRASE130513Kanaga VaratharajanAún no hay calificaciones

- MPEG-4 Performance Analysis For A CDMA Network-on-Chip: Manho Kim, Daewook Kim and Gerald E. SobelmanDocumento4 páginasMPEG-4 Performance Analysis For A CDMA Network-on-Chip: Manho Kim, Daewook Kim and Gerald E. SobelmanraghavaAún no hay calificaciones

- 6analysis of Coding Techniques in WiMAXDocumento8 páginas6analysis of Coding Techniques in WiMAXPrabhakarAún no hay calificaciones

- QPSK Modulation and Demodulation Implementation On CEVA XC-321 DSP For IEEE 802.11b Wi-Fi Phone ApplicationDocumento5 páginasQPSK Modulation and Demodulation Implementation On CEVA XC-321 DSP For IEEE 802.11b Wi-Fi Phone ApplicationdeviAún no hay calificaciones

- Design of A Wireless Medical Monitoring System: Computer and Management (CAMAN), 2011 International Conference OnDocumento8 páginasDesign of A Wireless Medical Monitoring System: Computer and Management (CAMAN), 2011 International Conference Onbopparajuswathi_8787Aún no hay calificaciones

- Smart Traffic Control: Divyabharathi.S, Logapriya.V, Karthick.RDocumento6 páginasSmart Traffic Control: Divyabharathi.S, Logapriya.V, Karthick.RLogapriya ViswanathanAún no hay calificaciones

- Implementation of GPRS-Based Positioning System Using PIC MicrocontrollerDocumento4 páginasImplementation of GPRS-Based Positioning System Using PIC MicrocontrollerRAMPRASAD89Aún no hay calificaciones

- Design & Simulation of Zigbee Transceiver System Using MatlabDocumento4 páginasDesign & Simulation of Zigbee Transceiver System Using MatlabseventhsensegroupAún no hay calificaciones

- A Software-Programmable Multiple-Standard Radio PlatformDocumento5 páginasA Software-Programmable Multiple-Standard Radio PlatformdvdreadsAún no hay calificaciones

- Implementation of Adaptive Viterbi DecoderDocumento7 páginasImplementation of Adaptive Viterbi DecoderseventhsensegroupAún no hay calificaciones

- A Smart Zigbee Based Wireless Weather Station Monitoring SystemDocumento6 páginasA Smart Zigbee Based Wireless Weather Station Monitoring SystemHachem ElyousfiAún no hay calificaciones

- Analysis of Simulation Parameters of Pulse Shaping FIR Filter For WCDMADocumento16 páginasAnalysis of Simulation Parameters of Pulse Shaping FIR Filter For WCDMAavnishAún no hay calificaciones

- CQ 2424552457Documento3 páginasCQ 2424552457IJMERAún no hay calificaciones

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkDe EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkAún no hay calificaciones

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDDe EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDAún no hay calificaciones

- Thinkpad T500 and W500 Hardware Maintenance ManualDocumento216 páginasThinkpad T500 and W500 Hardware Maintenance ManualJJ2JAún no hay calificaciones

- Spanish RomanceDocumento8 páginasSpanish RomanceFranxCuckooAún no hay calificaciones

- Tiersen, Yann - La Valse D - 'Amelie (Piano Version) PDFDocumento5 páginasTiersen, Yann - La Valse D - 'Amelie (Piano Version) PDFEliud SCAún no hay calificaciones

- Introduction To Middleware IDocumento30 páginasIntroduction To Middleware Isrini1006Aún no hay calificaciones

- Stene Prize 2017 - Letter To EULAR Member Organisations of PARE - DocxDocumento3 páginasStene Prize 2017 - Letter To EULAR Member Organisations of PARE - DocxFranxCuckooAún no hay calificaciones

- Wireless Sensor28Documento6 páginasWireless Sensor28FranxCuckooAún no hay calificaciones

- Volume (9) Issue (1) 136-153Documento18 páginasVolume (9) Issue (1) 136-153FranxCuckooAún no hay calificaciones

- ISCED Mapping 2014 - CyprusDocumento13 páginasISCED Mapping 2014 - CyprusFranxCuckooAún no hay calificaciones

- Volume (9) Issue (1) 136-153Documento18 páginasVolume (9) Issue (1) 136-153FranxCuckooAún no hay calificaciones

- Volume (9) Issue (1) 136-153Documento18 páginasVolume (9) Issue (1) 136-153FranxCuckooAún no hay calificaciones

- Chapter 6Documento57 páginasChapter 6Rakesh KumarAún no hay calificaciones

- The Neglected Art of Fixed Point ArithmeticDocumento35 páginasThe Neglected Art of Fixed Point ArithmeticvierusAún no hay calificaciones

- Lecture 5 Fixed Point Vs Floating Point Q-Format Number RepresentationDocumento5 páginasLecture 5 Fixed Point Vs Floating Point Q-Format Number RepresentationShanuj GargAún no hay calificaciones

- Chapter 2 MSDocumento79 páginasChapter 2 MSRakesh KumarAún no hay calificaciones

- Capoeira Song Compendium Version 1.0 InternationalDocumento91 páginasCapoeira Song Compendium Version 1.0 InternationalRodrigo Moreno GodoyAún no hay calificaciones

- Chapter 8 MsDocumento83 páginasChapter 8 MsDaniel Baquero Medina MorAún no hay calificaciones

- Receiver DesignDocumento122 páginasReceiver Designadeelanwar1Aún no hay calificaciones

- Chapter 3 MsDocumento108 páginasChapter 3 MsKjfsa TuAún no hay calificaciones

- QFSKDocumento160 páginasQFSKHussain Ageel NaseerAún no hay calificaciones

- EE4512 Analog and Digital Communications EE4513 Analog and Digital Communications LaboratoryDocumento46 páginasEE4512 Analog and Digital Communications EE4513 Analog and Digital Communications LaboratoryalexxxAún no hay calificaciones

- Multiplexing TechniquesChapter 7 PDFDocumento19 páginasMultiplexing TechniquesChapter 7 PDFDioen Biosca RojasAún no hay calificaciones

- Syslog LT400 2023 11 14Documento71 páginasSyslog LT400 2023 11 14finelineelectricalmaintenanceAún no hay calificaciones

- ZM1 Low Amperage Line Sensor: BenefitsDocumento2 páginasZM1 Low Amperage Line Sensor: BenefitsArun JosephAún no hay calificaciones

- Division of Aklan: Specialized Training Portfolio & Skills 10 PTSDocumento3 páginasDivision of Aklan: Specialized Training Portfolio & Skills 10 PTSLYNETTEAún no hay calificaciones

- Valeport miniSVPDocumento1 páginaValeport miniSVPHafiz AsyrafAún no hay calificaciones

- Smart Waste Management System: Software EngineeringDocumento17 páginasSmart Waste Management System: Software EngineeringAbdal LalitAún no hay calificaciones

- How To Create A User Instruction ManualDocumento3 páginasHow To Create A User Instruction ManualJusalyn Marcos DomingoAún no hay calificaciones

- Thesis Hooks PluginDocumento8 páginasThesis Hooks Pluginiapesmiig100% (2)

- Mind Map For PHD ThesisDocumento8 páginasMind Map For PHD ThesisHelpWritingPapersForCollegeSingapore100% (1)

- Exercise 7.3: Rolling Updates and Rollbacks: Nginx VersionsDocumento4 páginasExercise 7.3: Rolling Updates and Rollbacks: Nginx VersionstektitemoAún no hay calificaciones

- Hemisphere Crescent VS110 GPS Compass: Call: EmailDocumento2 páginasHemisphere Crescent VS110 GPS Compass: Call: EmailNguyen Phuoc HoAún no hay calificaciones

- Flash Tutorial Falling StarsDocumento12 páginasFlash Tutorial Falling Starspayeh89Aún no hay calificaciones

- E27307Documento28 páginasE27307Tarcisio FreitasAún no hay calificaciones

- GR 12 - CS - Quick Revision Notes and Important QuestionsDocumento131 páginasGR 12 - CS - Quick Revision Notes and Important Questionsshrinsaliha532Aún no hay calificaciones

- CS 1026 Assignment 4Documento5 páginasCS 1026 Assignment 4Jessica Li0% (3)

- DBMS Unit - 3Documento46 páginasDBMS Unit - 3logunaathanAún no hay calificaciones

- OurApp Using NodejsDocumento19 páginasOurApp Using NodejsPOLURU SUMANTH NAIDU STUDENT - CSEAún no hay calificaciones

- Cybrary Business FlyerDocumento2 páginasCybrary Business Flyerzillions61Aún no hay calificaciones

- TSV3561 Lesson Plan For StudentDocumento9 páginasTSV3561 Lesson Plan For StudentShenWeiAún no hay calificaciones

- Licensing - Brief - PLT - Licensing Windows 365 and Windows 11 Virtual Desktops For Remote AccessDocumento8 páginasLicensing - Brief - PLT - Licensing Windows 365 and Windows 11 Virtual Desktops For Remote AccessDariusG.BermeoAún no hay calificaciones

- PeopleSoft SharePoint Integration With InFlightDocumento18 páginasPeopleSoft SharePoint Integration With InFlightjlabrashAún no hay calificaciones

- Efficient Kotlin: Speed-Up Your Kotlin ProjectDocumento56 páginasEfficient Kotlin: Speed-Up Your Kotlin Projectname coinAún no hay calificaciones

- Major Project ReportDocumento38 páginasMajor Project ReportHritik JaiswalAún no hay calificaciones

- LONRIXDocumento9 páginasLONRIXsanjay prasadAún no hay calificaciones

- CTLG MINI08engDocumento48 páginasCTLG MINI08enggadacz111Aún no hay calificaciones

- Prepared by Destiny Corporation: Reading and Writing Data From Microsoft Excel/Word Using DDEDocumento6 páginasPrepared by Destiny Corporation: Reading and Writing Data From Microsoft Excel/Word Using DDEniravAún no hay calificaciones

- FL300 User ManualDocumento29 páginasFL300 User Manualc4r700% (1)