Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Ap7102 Adsd Syllabi

Cargado por

shankarTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Ap7102 Adsd Syllabi

Cargado por

shankarCopyright:

Formatos disponibles

KONGUNADU COLLEGE OF ENGINEERING AND TECHNOLOGY, THOTTIAM.

AP 7102 ADVANCED DIGITAL LOGIC SYSTEM DESIGN

OBJECTIVES:

To analyze synchronous and asynchronous sequential circuits

To realize and design hazard free circuits

To familiarize the practical issues of sequential circuit design

To gain knowledge about different fault diagnosis and testing methods

To estimate the performance of digital systems

To know about timing analysis of memory and PLD

UNIT I SEQUENTIAL CIRCUIT DESIGN

9

Analysis of Clocked Synchronous Sequential Networks (CSSN) - Modeling of CSSN State Assignment and Reduction Design of CSSN Design of Iterative Circuits

ASM Chart ASM Realization, Design of Arithmetic circuits for Fast adder- Array Multiplier.

UNIT II ASYNCHRONOUS SEQUENTIAL CIRCUIT DESIGN

9

Analysis of Asynchronous Sequential Circuit (ASC) Flow Table Reduction Races in ASC State Assignment Problem and the Transition Table Design of ASC

Static and Dynamic Hazards Essential Hazards Design of Hazard free circuits - Data Synchronizers Designing Vending Machine Controller Mixed Operating Mode

Asynchronous Circuits. Practical issues such as clock skew, synchronous and asynchronous inputs and switch bouncing.

UNIT III FAULT DIAGNOSIS & TESTING

9

Fault diagnosis: Fault Table Method Path Sensitization Method Boolean Difference Method Kohavi Algorithm Tolerance Techniques The Compact Algorithm.

Design for testability: Test Generation Masking Cycle DFT Schemes. Circuit testing fault model, specific and random faults, testing of sequential circuits, Built in Self

Test, Built in Logic Block observer (BILBO), signature analysis.

UNIT IV PERFORMANCE ESTIMATION

9

Estimating digital system reliability, transmission lines, reflections and terminations, system integrity, network issues for digital systems, formal verifications of digital

system: model-checking, binary decision, theorem proving, circuit equivalence.

UNIT V TIMING ANALYSIS

9

ROM timings, Static RAM timing, Synchronous Static RAM and its timing, Dynamic RAM timing, Complex Programmable Logic Devices, Logic Analyzer Basic

Architecture, Internal structure, Data display, Setup and Control, Clocking and Sampling.

TOTAL: 45 PERIODS

REFERENCES:

1. Charles H.Roth Jr Fundamentals of Logic Design, Thomson Learning 2004.

2. Nripendra N Biswas Logic Design Theory Prentice Hall of India, 2001.

3. Parag K.Lala An introduction to Logic Circuit Testing Morgan and claypool publishers, 2009.

4. Stephen D Brown, Fundamentals of digital logic, TMH publication, 2007.

5. Balabanian, Digital Logic Design Principles, Wiley publication, 2007.

6. Stalling, Computer Organization & Architecture, Pearson Education India, 2008.

7. J.F.Wakerly, Digital Design, Pearson Education India, 2012.

8. J.F.Wakerly, Digital Design principles and practices, PHI publications, 2005.

KNCET, TRICHY

9. Charles J. Sipil, Microcomputer Handbook McCrindle- Collins Publications 1977.

UNIT I

SEQUENTIAL CIRCUIT DESIGN

Analysis of Clocked Synchronous Sequential Networks (CSSN) - Modeling of CSSN- State Assignment and Reduction- Design of CSSN- Design of

iterative circuits-ASM chart- ASM Realization, Design of arithmetic Circuits for Fast adder-Array Multiplier.

Session

No.

Topics to be covered

Ref

1.

Analysis of Clocked Synchronous Sequential Networks- Introduction.

2.

Design of a Sequential parity checker, Analysis of Moore and Mealy sequential circuit by signal

tracing and timing charts.

3.

Method of constructing state table and state graphs for Moore and Mealy machines.

4.

General Models for a clocked Mealy and Moore sequential circuits.

5.

Guidelines for state assignments and reduction of state table using state assignment.

6.

Different types of State Assignment- Shared row, Multiple row and One hot state assignment.

7.

Determination of state equivalence and circuit equivalence using an implication table.

8.

Design of iterative circuits, Design of a n-bit comparator.

9.

Algorithmic State Machine (ASM) Charts- Derivation and realization of ASM Chart.

10.

Design of Arithmetic circuits for Fast adder- Carry look ahead adder.

11.

Array Multiplier Structure of an 4 X 4 Multiplier circuit.

Page No

Material Page

No

KNCET, TRICHY

UNIT II

ASYNCHRONOUS SEQUENTIAL CIRCUIT DESIGN

Analysis of Asynchronous Sequential Circuit (ASC) - Flow Table Reduction-Races in ASC- State Assignment Problem and the Transition Table- Design of

ASC-Static and Dynamic Hazards- Essential Hazards- Design of Hazard free circuits- Data Synchronizers- Designing Vending Machine Controller- Mixed

Operating Mode Asynchronous Circuits. Practical issues such as clock skew, synchronous and asynchronous inputs and switch bouncing.

Session

No.

Topics to be covered

Ref

12.

Analysis of Asynchronous Sequential Circuit - Design of Fundamental mode sequential

circuit - Primitive state table, state table reduction and state assignment.

13.

Design of Pulse mode sequential circuit- Primitive state table, state table reduction and state

assignment.

14.

Problems in Asynchronous Sequential Circuits Cycles, Critical race and Non- Critical race.

2,5

15.

Hazards- Static, Dynamic and Essential Hazards.

2,5

16.

Design of Hazard free switching circuits- Static Hazard and Essential Hazard elimination.

2,5

17.

Working principle of Data synchronizer.

18.

Design of Vending machine controller- Description/ Specification, FSM design steps, State

diagram and state table.

19.

Design of mixed operating mode asynchronous circuit.

20.

Practical issues: Clock skew, synchronous and asynchronous inputs and switch bouncing.

Page No

Material Page

No

KNCET, TRICHY

UNIT III

FAULT DIAGNOSIS & TESTING

Fault diagnosis: Fault Table Method- Path Sensitization Method- Boolean Difference Method- Kohavi Algorithm -Tolerance Techniques- The Compact

Algorithm. Design for testability: Test Generation- Masking Cycle - DFT schemes. Circuit testing fault model, specific and random faults, testing of

sequential circuits, Built in self test, Built in Logic Block observer (BILBO), Signature analysis.

Session

No.

Topics to be covered

Ref

21.

Fault Models- Stuck-at fault, Bridging fault, stuck-open fault and Temporary faults.

22.

Fault Diagnosis of Digital systems- Test generation for combinational logic circuits- Fault

Table Method and Path Sensitization method.

23.

Boolean Difference method.

24.

Kohavi and Compact Algorithm.

25.

Tolerance techniques- Static redundancy, Dynamic redundancy

and Hybrid redundancy.

26.

Self- purging redundancy, Sift-out modular redundancy

27.

Fault in PLAs, Test generation and Masking cycle.

28.

Design for Testability (DFT), DFT schemes, Circuit testing fault model: Specific and random

faults.

29.

Testing of sequential circuits and Built In Self Test (BIST).

30.

Built In Logic Block Observer (BILBO) and Signature analysis.

Page No

Material Page

No

KNCET, TRICHY

UNIT IV

PERFORMANCE ESTIMATION

Estimating digital system reliability, transmission lines, reflections and terminations, system integrity, network issues for digital systems, formal verifications

of digital system: model- checking, binary decision diagram, theorem proving, circuit equivalence.

Session

No.

Topics to be covered

Ref

31.

Estimating Digital System Reliability- Failure rates, Reliability and MTBF, System

Reliability.

32.

Transmission lines with infinite and finite length terminated with characteristic impedance,

Logic signal terminations.

33.

Network issues for digital systems: Noise, Time margin, Parasitic inductance and

capacitances.

34.

Digital System Integrity to minimize Noise Margin, Transmission Line effects, Signal Path

Return currents and power distribution.

35.

Design and Verification of Digital Systems: Design flow and RTL Verification.

36.

Binary Decision Diagrams with an example.

37.

Model for Design Verification, Functional Validation.

38.

Formal Verification and Challenges in Symbolic Simulation.

Page No

Material Page

No

KNCET, TRICHY

UNIT V

TIMING ANALYSIS

ROM timings, Static RAM timing, Synchronous Static RAM and its timing. Dynamic RAM timing, Complex Programmable Logic devices, Logic Analyzer

Basic Architecture, Internal Structure, Data display, Setup and Control, Clocking and Sampling.

Session

No.

Topics to be covered

Ref

39.

Read Only Memory (ROM) Timing diagram.

40.

Static RAM Internal Structure and Timing parameters for Read and Write operation of

static RAM.

41.

Synchronous SRAM- Internal Structure and its read and Write operation.

42.

Dynamic RAM Structure, Write and burst read cycle Timing.

43,44

Complex Programmable Logic Devices general architecture, Function block architecture,

Input/output block architecture and Switch Matrix.

45.

Logic Analyzer- Basic Architecture and Internal Structure.

46.

Logic Analyzer- Clocking, Triggering, Acquisition and Capturing Glitches.

47.

Logic Analyzer- Data display, Setup and Control

Page No

Material

Page No

7

7

7

6

6

6

KNCET, TRICHY

También podría gustarte

- Thomas Calculus 11th (Textbook + Solutions)Documento140 páginasThomas Calculus 11th (Textbook + Solutions)Sendhilkumar Alalasundaram76% (33)

- Vlsi Mtech Jntu Kakinada II Sem SyllabusDocumento16 páginasVlsi Mtech Jntu Kakinada II Sem Syllabusrv prasad50% (2)

- On-Chip Communication Architectures: System on Chip InterconnectDe EverandOn-Chip Communication Architectures: System on Chip InterconnectAún no hay calificaciones

- Digital Circuit Testing: A Guide to DFT and Other TechniquesDe EverandDigital Circuit Testing: A Guide to DFT and Other TechniquesAún no hay calificaciones

- Generador El PoyDocumento4 páginasGenerador El PoyPortillo Calix Jorge LuisAún no hay calificaciones

- Ap7102 AdsdDocumento5 páginasAp7102 AdsdshankarAún no hay calificaciones

- De SyllabusDocumento2 páginasDe SyllabusKarthikeyan_Go_9525Aún no hay calificaciones

- Regulations - 2009: Affiliated Institutions Anna University, ChennaiDocumento10 páginasRegulations - 2009: Affiliated Institutions Anna University, Chennaisri_vas00074013Aún no hay calificaciones

- EC6302 - de - SyllabusDocumento2 páginasEC6302 - de - SyllabusNava KrishnanAún no hay calificaciones

- Computer Organization Lab Experiments ListDocumento1 páginaComputer Organization Lab Experiments ListHimanshu MittalAún no hay calificaciones

- Advanced Digital System DesignDocumento1 páginaAdvanced Digital System Designarunecetheboss0% (3)

- Ae IIDocumento27 páginasAe IIAnbu SelvanAún no hay calificaciones

- M E EmbeddedSystemTechnologiesDocumento31 páginasM E EmbeddedSystemTechnologiesRohini BabuAún no hay calificaciones

- Vlsi Design PDFDocumento22 páginasVlsi Design PDFKishore KumarAún no hay calificaciones

- Digital Electronics Combinational and Sequential Circuit DesignDocumento2 páginasDigital Electronics Combinational and Sequential Circuit DesignjeevaAún no hay calificaciones

- R 2008 M.E. Applied Electronics SyllabusDocumento31 páginasR 2008 M.E. Applied Electronics SyllabusisasenthilAún no hay calificaciones

- EC657 Digital System Design and EC661 Digital Signal Processing StructuresDocumento2 páginasEC657 Digital System Design and EC661 Digital Signal Processing StructuresAvinash KumarAún no hay calificaciones

- EC1303 Digital System Design Course OverviewDocumento2 páginasEC1303 Digital System Design Course OverviewMohamed Abdul RahimAún no hay calificaciones

- Course 9Documento2 páginasCourse 9faster123Aún no hay calificaciones

- Revised Syllabus MicroelectronicsDocumento19 páginasRevised Syllabus MicroelectronicsBaluvu JagadishAún no hay calificaciones

- M.tech Vlsi Syllabus: D.A.John & K.Martin, Analog Integrated Circuit Design, Wiley, 1997Documento5 páginasM.tech Vlsi Syllabus: D.A.John & K.Martin, Analog Integrated Circuit Design, Wiley, 1997Garth RodriguezAún no hay calificaciones

- Applied Mathematics For Electronics EngineersDocumento35 páginasApplied Mathematics For Electronics EngineersRamJiDRAún no hay calificaciones

- Switching Theory and Logic DesignDocumento2 páginasSwitching Theory and Logic DesignManjunath BadigerAún no hay calificaciones

- EtrxDocumento16 páginasEtrxapi-236544093Aún no hay calificaciones

- VLSI Design Fundamentals and Digital CircuitsDocumento2 páginasVLSI Design Fundamentals and Digital Circuitsjames RAún no hay calificaciones

- Engineering Mathematics - Iv CODE: 10 MAT 41 IA Marks: 25 Hrs/Week: 04 Exam HRS: 03 Total HRS: 52 Exam Marks:100 Part-A Unit-I: Numerical Methods - 1Documento14 páginasEngineering Mathematics - Iv CODE: 10 MAT 41 IA Marks: 25 Hrs/Week: 04 Exam HRS: 03 Total HRS: 52 Exam Marks:100 Part-A Unit-I: Numerical Methods - 1HmmTell TellAún no hay calificaciones

- VLSI SyllabusDocumento13 páginasVLSI SyllabusNagabhushanam KoduriAún no hay calificaciones

- Regulation - 2009: Affiliated Institutions Anna University, ChennaiDocumento27 páginasRegulation - 2009: Affiliated Institutions Anna University, ChennaiYogeswaran SundarrajAún no hay calificaciones

- VLSI Design Course OverviewDocumento1 páginaVLSI Design Course OverviewRajalingam BossAún no hay calificaciones

- M.tech Vlsi Syllabus: D.A.John & K.Martin, Analog Integrated Circuit Design, Wiley, 1997Documento6 páginasM.tech Vlsi Syllabus: D.A.John & K.Martin, Analog Integrated Circuit Design, Wiley, 1997yupsup9Aún no hay calificaciones

- Vit Ece 5th Year SyllabusDocumento16 páginasVit Ece 5th Year Syllabuspranavateja12399Aún no hay calificaciones

- Vlsi Vlsid Vlsisd Vlsi Me Ece PDFDocumento18 páginasVlsi Vlsid Vlsisd Vlsi Me Ece PDFramanaidu1Aún no hay calificaciones

- (IIT Guwahati) VLSI Design Verification and TestDocumento4 páginas(IIT Guwahati) VLSI Design Verification and Testjitu_4Aún no hay calificaciones

- 401 M.E. Applied ElectronicsDocumento10 páginas401 M.E. Applied Electronicsd_vijay666Aún no hay calificaciones

- Vlsi Mtech 1st - Year - Jntu Kakinada SyllabusDocumento8 páginasVlsi Mtech 1st - Year - Jntu Kakinada Syllabustele203Aún no hay calificaciones

- Common Recruitment Examination June 2013: DeityDocumento10 páginasCommon Recruitment Examination June 2013: DeitydannycbsAún no hay calificaciones

- Es IiDocumento16 páginasEs IiSivasankar YalavarthyAún no hay calificaciones

- VLSI Design SyllabusDocumento2 páginasVLSI Design SyllabusJyoti RanjanAún no hay calificaciones

- Btech New SyllabusDocumento8 páginasBtech New SyllabusDrBhoopal RaoAún no hay calificaciones

- 6Xn1 Digital Integrated CircuitsDocumento2 páginas6Xn1 Digital Integrated CircuitsapbhatkarAún no hay calificaciones

- Vlsi DesignDocumento12 páginasVlsi DesignTanveer AhmedAún no hay calificaciones

- Me SyllabusDocumento3 páginasMe SyllabusPrabhu SubramaniamAún no hay calificaciones

- B 1254789545454e CseDocumento1 páginaB 1254789545454e CseAnonymous a8rdyKOCAún no hay calificaciones

- RGPV Syllabus Cbgs Ec 3 Sem All SubjectsDocumento8 páginasRGPV Syllabus Cbgs Ec 3 Sem All SubjectsAyushAún no hay calificaciones

- Vlsi System DesignDocumento12 páginasVlsi System DesignMahender GoudAún no hay calificaciones

- EmbeddedDocumento9 páginasEmbeddedNanc Joy100% (1)

- Applied Mathematics and Digital Signal ProcessingDocumento5 páginasApplied Mathematics and Digital Signal ProcessingvigneshkumarcAún no hay calificaciones

- syllabusTNPSC Ase Asa SyllabusDocumento9 páginassyllabusTNPSC Ase Asa SyllabusVaikunthan SAún no hay calificaciones

- Postgraduate M E Instrumentation and ControlDocumento8 páginasPostgraduate M E Instrumentation and Controljricardo019763535Aún no hay calificaciones

- Vlsi Mtech Jntu Kakinada SyllabusDocumento11 páginasVlsi Mtech Jntu Kakinada Syllabusaditya414Aún no hay calificaciones

- Syllabus For Applied ElectronicsDocumento28 páginasSyllabus For Applied ElectronicsvinayakbondAún no hay calificaciones

- MTech VLSI Design 1st Sem SyllabusDocumento5 páginasMTech VLSI Design 1st Sem SyllabusPrakash Sinha100% (1)

- Electronic Design Automation: Synthesis, Verification, and TestDe EverandElectronic Design Automation: Synthesis, Verification, and TestAún no hay calificaciones

- Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLDe EverandIntroduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLAún no hay calificaciones

- Networks on Chips: Technology and ToolsDe EverandNetworks on Chips: Technology and ToolsCalificación: 5 de 5 estrellas5/5 (3)

- Performance Evaluation by Simulation and Analysis with Applications to Computer NetworksDe EverandPerformance Evaluation by Simulation and Analysis with Applications to Computer NetworksAún no hay calificaciones

- Multimedia Services in Wireless Internet: Modeling and AnalysisDe EverandMultimedia Services in Wireless Internet: Modeling and AnalysisAún no hay calificaciones

- Parallel Processing for Artificial Intelligence 1De EverandParallel Processing for Artificial Intelligence 1Calificación: 5 de 5 estrellas5/5 (1)

- Practical Design of Digital Circuits: Basic Logic to MicroprocessorsDe EverandPractical Design of Digital Circuits: Basic Logic to MicroprocessorsCalificación: 4.5 de 5 estrellas4.5/5 (2)

- KONGUNADU COLLEGE OF ENGINEERING AND TECHNOLOGY TERMINAL EXAMINATION-I ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUITSDocumento2 páginasKONGUNADU COLLEGE OF ENGINEERING AND TECHNOLOGY TERMINAL EXAMINATION-I ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUITSshankarAún no hay calificaciones

- Ex06 - Answer Key Adaic Te-2Documento8 páginasEx06 - Answer Key Adaic Te-2shankarAún no hay calificaciones

- M.E. Applied Electronics - R2017Documento47 páginasM.E. Applied Electronics - R2017Mr.R.Ragumadhavan ecestaffAún no hay calificaciones

- Ex05 - Question Paper Adaic - ModelDocumento2 páginasEx05 - Question Paper Adaic - ModelshankarAún no hay calificaciones

- Introduction To MATLABDocumento36 páginasIntroduction To MATLABViju JigajinniAún no hay calificaciones

- Design of Efficient Class-E Power Amplifiers For Short-Distance CommunicationsDocumento11 páginasDesign of Efficient Class-E Power Amplifiers For Short-Distance CommunicationsshankarAún no hay calificaciones

- MATLAB BasicsDocumento24 páginasMATLAB BasicsshankarAún no hay calificaciones

- NBA Modified RF&MW LPDocumento4 páginasNBA Modified RF&MW LPshankarAún no hay calificaciones

- KONGUNADU COLLEGE M.E ECE I/I TIME TABLE 2018-19Documento1 páginaKONGUNADU COLLEGE M.E ECE I/I TIME TABLE 2018-19shankarAún no hay calificaciones

- Zero Diagonal Property Symmetry Property Unitary Property Phase Shift PropertyDocumento5 páginasZero Diagonal Property Symmetry Property Unitary Property Phase Shift PropertyshankarAún no hay calificaciones

- Kongunadu College of Engineering and TechnologyDocumento2 páginasKongunadu College of Engineering and TechnologyshankarAún no hay calificaciones

- Adaic TT 2016Documento2 páginasAdaic TT 2016shankarAún no hay calificaciones

- Ec 6502 Principles of Digital Signal Processing - Question Bank - 2018Documento17 páginasEc 6502 Principles of Digital Signal Processing - Question Bank - 2018shankarAún no hay calificaciones

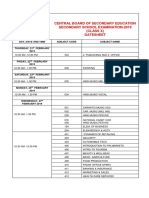

- Central Board of Secondary Education Secondary School Examination-2019 (Class X) DatesheetDocumento4 páginasCentral Board of Secondary Education Secondary School Examination-2019 (Class X) DatesheetPriyanka SharmaAún no hay calificaciones

- Digital Signal Processing Introduction PartDocumento13 páginasDigital Signal Processing Introduction Partshankar100% (1)

- Ada Syllabus 2013Documento1 páginaAda Syllabus 2013shankarAún no hay calificaciones

- Kongunadu College of Engineering and Technology, ThourpattiDocumento1 páginaKongunadu College of Engineering and Technology, ThourpattishankarAún no hay calificaciones

- HTTPDocumento2 páginasHTTPshankarAún no hay calificaciones

- CH 3 - FeedbackDocumento54 páginasCH 3 - FeedbackshankarAún no hay calificaciones

- RF&MW M 1Documento2 páginasRF&MW M 1shankarAún no hay calificaciones

- Unit 1 Ada 2014Documento22 páginasUnit 1 Ada 2014shankarAún no hay calificaciones

- Ec6802 Wireless NetworksDocumento1 páginaEc6802 Wireless NetworksBritto Ebrington AjayAún no hay calificaciones

- Ada Syllabus 2013Documento1 páginaAda Syllabus 2013shankarAún no hay calificaciones

- WN Unit1 and Unit5Documento1 páginaWN Unit1 and Unit5shankar0% (1)

- HTTPDocumento2 páginasHTTPshankarAún no hay calificaciones

- Unit V: Time Varying Fields and Maxwell'S EquationsDocumento12 páginasUnit V: Time Varying Fields and Maxwell'S EquationsshankarAún no hay calificaciones

- MultiplierDocumento16 páginasMultipliershankarAún no hay calificaciones

- AP9212Documento7 páginasAP9212shankarAún no hay calificaciones

- Unit 1 Adsd KncetDocumento46 páginasUnit 1 Adsd KncetshankarAún no hay calificaciones

- Mobile Fading-Rayleigh and Lognormal SuperimposedDocumento4 páginasMobile Fading-Rayleigh and Lognormal Superimposedأحمد عليAún no hay calificaciones

- EPP and TLE Content Matrix PDFDocumento2 páginasEPP and TLE Content Matrix PDFLynn PlacidoAún no hay calificaciones

- Ceramic - Filter - and - Duplexer - Data - Sheet RALTRONDocumento7 páginasCeramic - Filter - and - Duplexer - Data - Sheet RALTRONYung SangAún no hay calificaciones

- Handbook of Nanophase and Nano Structured Materials 4Documento344 páginasHandbook of Nanophase and Nano Structured Materials 4mohayman100% (2)

- RTKDocumento18 páginasRTKSumit KumarAún no hay calificaciones

- Fiery Cws Cofigure Color Work StationDocumento90 páginasFiery Cws Cofigure Color Work StationAli VatanAún no hay calificaciones

- Lab 1 Introduction To Android StudioDocumento19 páginasLab 1 Introduction To Android StudioYong ShunAún no hay calificaciones

- Safety and Overload Couplings Book Margin EditedDocumento49 páginasSafety and Overload Couplings Book Margin EditedluisAún no hay calificaciones

- Siemens MS 43Documento20 páginasSiemens MS 43Rómulo Simón Lizarraga León100% (1)

- MTDC System PDFDocumento17 páginasMTDC System PDFAshok Kumar67% (3)

- Frequency Tripler Using The CA3028: Figure 1: X3 Multiplier Using Differential AmplifierDocumento1 páginaFrequency Tripler Using The CA3028: Figure 1: X3 Multiplier Using Differential AmplifierRadmila LugonjicAún no hay calificaciones

- Signal TheoryDocumento9 páginasSignal Theoryapi-282356011Aún no hay calificaciones

- B-63950en 04 100111Documento678 páginasB-63950en 04 100111Ibon Cid Rivera50% (2)

- S Feature D Escriptio: LT1780/LT1781 Low Power 5V RS232 Dual Driver/Receiver With 15kV ESD ProtectionDocumento13 páginasS Feature D Escriptio: LT1780/LT1781 Low Power 5V RS232 Dual Driver/Receiver With 15kV ESD ProtectionisaiasvaAún no hay calificaciones

- AC GENERATOR PROJECT REPORTDocumento21 páginasAC GENERATOR PROJECT REPORTCHALLENGER'S PHYSICS CLASSESAún no hay calificaciones

- Android Flashing GuideDocumento3 páginasAndroid Flashing GuideLynda NuryatiAún no hay calificaciones

- Sony Hcd-gnz77d Gnz88d Ver-1.3 SCHDocumento6 páginasSony Hcd-gnz77d Gnz88d Ver-1.3 SCHShailesh SanayeAún no hay calificaciones

- Transmisor de PresionDocumento4 páginasTransmisor de PresionGarcia FranciscoAún no hay calificaciones

- 0000518A Circuit Breaker PaperDocumento5 páginas0000518A Circuit Breaker PaperRicardo HerreraAún no hay calificaciones

- Week 8 Assignment SolutionsDocumento4 páginasWeek 8 Assignment Solutionsvidhya dsAún no hay calificaciones

- Specification: Actuator For Smoke DamperDocumento2 páginasSpecification: Actuator For Smoke Dampermartin saadAún no hay calificaciones

- Solutions and interpretations of harmonic oscillator equationsDocumento156 páginasSolutions and interpretations of harmonic oscillator equationsmcloughtAún no hay calificaciones

- 3 77 PDFDocumento68 páginas3 77 PDFviatr0nic100% (1)

- Abdallah Matoug Al-Dushaishi: Electrical EngineerDocumento4 páginasAbdallah Matoug Al-Dushaishi: Electrical Engineerameer457Aún no hay calificaciones

- McAfee device backup process ESM incremental fullDocumento11 páginasMcAfee device backup process ESM incremental fullabbuasherAún no hay calificaciones

- Canadian-Solar Datasheet Inverter 3ph-12-20KW-ROW EN V1.1 May-2020-5Documento2 páginasCanadian-Solar Datasheet Inverter 3ph-12-20KW-ROW EN V1.1 May-2020-5ENG. ALEXAún no hay calificaciones

- Velocity of Longitudinal WaveDocumento12 páginasVelocity of Longitudinal WaverenzoAún no hay calificaciones

- Circuit Construction Kit Ac Virtual Lab HTML Guide - enDocumento4 páginasCircuit Construction Kit Ac Virtual Lab HTML Guide - enkavithaAún no hay calificaciones