Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Genesys Logic, Inc.: Datasheet Revision 1.02 Aug. 21, 2007

Cargado por

CarlosClarosTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Genesys Logic, Inc.: Datasheet Revision 1.02 Aug. 21, 2007

Cargado por

CarlosClarosCopyright:

Formatos disponibles

Genesys Logic, Inc.

GL830

USB 2.0 to SATA

Bridge Controller

Datasheet

Revision 1.02

Aug. 21, 2007

GL830 USB2.0 to SATA Bridge Controller

Copyright:

Copyright 2007 Genesys Logic Incorporated. All rights reserved. No part of the materials may be

reproduced in any form or by any means without prior written consent of Genesys Logic, Inc.

Disclaimer:

ALL MATERIALS ARE PROVIDED "AS IS" WITHOUT EXPRESS OR IMPLIED WARRANTY OF ANY

KIND. NO LICENSE OR RIGHT IS GRANTED UNDER ANY PATENT OR TRADEMARK OF

GENESYS LOGIC INC.. GENESYS LOGIC HEREBY DISCLAIMS ALL WARRANTIES AND

CONDITIONS IN REGARD TO MATERIALS, INCLUDING ALL WARRANTIES, IMPLIED OR

EXPRESS, OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, AND

NON-INFRINGEMENT OF INTELLECTUAL PROPERTY. IN NO EVENT SHALL GENESYS LOGIC

BE LIABLE FOR ANY DAMAGES INCLUDING, WITHOUT LIMITATION, DAMAGES RESULTING

FROM LOSS OF INFORMATION OR PROFITS. PLEASE BE ADVISED THAT THE MATERIALS

MAY CONTAIN ERRORS OR OMMISIONS. GENESYS LOGIC MAY MAKE CHANGES TO THE

MATERIALS OR TO THE PRODUCTS DESCRIBED THEREIN AT ANY TIME WITHOUT NOTICE.

Trademarks:

is a registrated trademark of Genesys Logic, Inc.

All trademarks are the properties of their respective owners.

Office:

Genesys Logic, Inc.

12F, No. 205, Sec. 3, Beishin Rd., Shindian City,

Taipei, Taiwan

Tel: (886-2) 8913-1888

Fax: (886-2) 6629-6168

http://www.genesyslogic.com

2007 Genesys Logic Inc. - All rights reserved.

Page 2

GL830 USB2.0 to SATA Bridge Controller

Revision History

Revision

Date

Description

1.00

06/14/2007

First Formal Release

1.01

7/17/2007

Add 48 and 128pin description

1.02

08/21/2007

Modify LQFP48/64/128 description

2007 Genesys Logic Inc. - All rights reserved.

Page 3

GL830 USB2.0 to SATA Bridge Controller

TABLE OF CONTENTS

CHAPTER 1 GENERAL DESCRIPTION................................................... 8

CHAPTER 2 FEATURES .............................................................................. 9

CHAPTER 3 PIN ASSIGNMENT .............................................................. 10

3.1 PINOUTS.................................................................................................... 10

3.2 PIN LIST.................................................................................................... 13

3.3 PIN DESCRIPTIONS ................................................................................... 15

CHAPTER 4 BLOCK DIAGRAM.............................................................. 22

CHAPTER 5 FUNCTION DESCRIPTION ............................................... 23

5.1 UTM......................................................................................................... 23

5.2 SIE............................................................................................................ 23

5.3 EP0/EP3 FIFO AND BULK BUFFER ........................................................ 23

5.4 OPERATION REGISTER............................................................................. 23

5.5 SPI INTERFACE ........................................................................................ 23

5.6 PHY LAYER ............................................................................................. 23

5.7 LINK LAYER ............................................................................................. 23

5.8 TRANSPORT LAYER .................................................................................. 23

5.9 APPLICATION LAYER ............................................................................... 23

CHAPTER 6 ELECTRICAL CHARACTERISTICS............................... 24

6.1 ABSOLUTE MAXIMUM RATINGS .............................................................. 24

6.2 TEMPERATURE CONDITIONS ................................................................... 24

6.3 DC CHARACTERISTICS ............................................................................ 24

6.3.1 I/O Type digital pins ....................................................................... 24

6.3.2 USB Interface DC Characteristics ................................................ 25

6.3.3 SATA Interface DC Characteristics ............................................. 25

6.3.4 Reference Clock Input Requirement ............................................ 25

6.3.5 Reference Resistor Requirement ................................................... 25

6.4 AC CHARACTERISTICS ............................................................................ 25

6.4.1 USB Interface AC Characteristics ................................................ 25

6.4.2 SATA Interface AC Characteristics ............................................. 25

2007 Genesys Logic Inc. - All rights reserved.

Page 4

GL830 USB2.0 to SATA Bridge Controller

CHAPTER 7 PACKAGE DIMENSION..................................................... 26

CHAPTER 8 ORDERING INFORMATION ............................................ 29

2007 Genesys Logic Inc. - All rights reserved.

Page 5

GL830 USB2.0 to SATA Bridge Controller

LIST OF FIGURES

FIGURE 3.1 - 48 PIN LQFP PINOUT DIAGRAM.................................................................. 10

FIGURE 3.2 - 64 PIN LQFP PINOUT DIAGRAM.................................................................. 11

FIGURE 3.3 - 128 PIN LQFP PINOUT DIAGRAM ............................................................... 12

FIGURE 4.1 - BLOCK DIAGRAM ......................................................................................... 22

FIGURE 7.1 GL830 48 PIN LQFP PACKAGE .................................................................. 26

FIGURE 7.2 - GL830 64 PIN LQFP PACKAGE ................................................................... 27

FIGURE 7.3 - GL830 128 PIN LQFP PACKAGE ................................................................. 28

2007 Genesys Logic Inc. - All rights reserved.

Page 6

GL830 USB2.0 to SATA Bridge Controller

LIST OF TABLES

TABLE 3.1 48 PIN LIST .................................................................................................... 13

TABLE 3.2 64 PIN LIST .................................................................................................... 13

TABLE 3.3 128 PIN LIST .................................................................................................. 14

TABLE 3.4 48 PIN DESCRIPTIONS.................................................................................... 15

TABLE 3.5 64 PIN DESCRIPTIONS.................................................................................... 16

TABLE 3.6 128 PIN DESCRIPTIONS.................................................................................. 18

TABLE 6.1 - MAXIMUM RATINGS ...................................................................................... 24

TABLE 6.2 - TEMPERATURE CONDITIONS ......................................................................... 24

TABLE 6.3 - I/O TYPE DIGITAL PINS .................................................................................. 24

TABLE 6.6 - REFERENCE CLOCK INPUT REQUIREMENT .................................................. 25

TABLE 6.7 - REFERENCE RESISTOR REQUIREMENT ......................................................... 25

TABLE 8.1 - ORDERING INFORMATION ............................................................................. 29

2007 Genesys Logic Inc. - All rights reserved.

Page 7

GL830 USB2.0 to SATA Bridge Controller

CHAPTER 1 GENERAL DESCRIPTION

The GL830 is a highly-compatible, low cost USB 2.0 to SATA bridge controller, which integrates Genesys

Logic own design high speed UTMI (USB 2.0 Transceiver Macrocell Interface) transceiver/receiver and Serial

ATA PHY. As a one-chip solution which complies with Universal Serial Bus specification rev. 2.0 and Serial

ATA specification rev. 2.6. There are totally 4 endpoints in the GL830 controller, Control (0), Bulk In (1), Bulk

Out (2), and Interrupt (3). By complies with the USB Storage Class specification ver.1.0 (Bulk only protocol),

the GL830 can support not only plug and play but also Windows Vista/ XP/ 2000/ ME default driver. The

GL830 uses 25MHz crystal and slew-rate controlled pads to reduce the EMI issue. With 64-pin LQFP

(7mmX7mm) package, the GL830 is the best cost/ performance solution to fit different situations in the USB 2.0

high speed storage class applications such as SATA HDD and ODD.

2007 Genesys Logic Inc. - All rights reserved.

Page 8

GL830 USB2.0 to SATA Bridge Controller

CHAPTER 2 FEATURES

Complies with Universal Serial Bus specification rev. 2.0.

Complies with USB Storage Class specification ver.1.0. (Bulk only protocol)

Operating system supported: Win Vista/ Win XP / 2000 / Me / 98 / 98SE; Mac OS 9.X / X.

Integrated USB 2.0 Transceiver Macrocell Interface (UTMI) transceiver and Serial Interface Engine (SIE).

Support 4 endpoints: Control (0) / Bulk Read (1) / Bulk Write (2) / Interrupt (3).

64 / 512 bytes Data Payload for full / high speed Bulk Endpoint.

Complies with Serial ATA specification rev. 2.6.

Support SATA hot-plug

Support Spread Spectrum Clocking to reduce EMI

Support Partial/Slumber power management

Provide adjustable TX signal amplitude and pre-emphasis level

Provide specified OOB signal detection and transmission

Embedded Turbo 8051.

ROM size: 12k words; RAM size: 1280 bytes. (Bulk Buffer: 512 words, MC RAM: 256 bytes)

Supports Power Down mode and USB suspend indicator.

Supports USB 2.0 TEST mode features.

Supports 4 PIO and 4GPIO for programmable AP.

Supports device power control for power on/off when running suspend mode.

Provides LED indicator for Full Speed and High Speed .

using 25 MHz external clock to provide better EMI.

3.3V power input; 5V tolerance pad.

Supports Wakeup ability.

Embedded Regulator (3.3V to 1.8V).

Embedded Regulator (5V to 3.3V).

Provides SPI interface for Finger Print (only for 64 pin package).

Available in 48/64/128-pin LQFP.

2007 Genesys Logic Inc. - All rights reserved.

Page 9

GL830 USB2.0 to SATA Bridge Controller

CHAPTER 3 PIN ASSIGNMENT

GND

CVDD

X1

X2

VDD

GND

VDD

CVDD

AGND

AVDD

DP

DM

36

35

34

33

32

31

30

29

28

27

26

25

3.1 Pinouts

RTERM

37

24

AGND

PLLVDD

38

23

RREF

PLLVSS

39

22

AVDD

TXVSS

40

21

NC

TXVDD

41

20

GPIO1

TXP

42

19

NC

TXN

43

18

PIO2

RXN

44

17

GPIO2

RXP

45

16

NC

RXVDD

46

15

V5

RXVSS

47

14

VDD

CVDD

48

13

GND

10

11

12

GND

GPIO0

GPIO3

PIO3

HRST_

CVDD

VDD

GND

TEST

PIO0

PIO1

CVDD

LQFP - 48

Figure 3.1 - 48 Pin LQFP Pinout Diagram

2007 Genesys Logic Inc. - All rights reserved.

Page 10

GL830 USB2.0 to SATA Bridge Controller

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

PLLVDD

49

32

NC

PLLVSS

50

31

NC

RXPEXT

51

30

GPIO1

RXNEXT

52

29

NC

TXNEXT

53

28

NC

TXPEXT

54

27

PIO2

TXVSS

55

26

NC

TXVDD

56

25

GPIO2

TXP

57

24

NC

TXN

58

23

V5

RXN

59

22

VDD

RXP

60

21

GND

RXVDD

61

20

CVDD

RXVSS

62

19

NC

CVDD

63

18

NC

GND

64

17

NC

GL830

LQFP - 64

10

11

12

13

14

15

16

Figure 3.2 - 64 Pin LQFP Pinout Diagram

2007 Genesys Logic Inc. - All rights reserved.

Page 11

GL830 USB2.0 to SATA Bridge Controller

NC

NC

NC

NC

NC

NC

NC

PLLVDD

PLLVDD

PLLVSS

RXPEXT

RXNEXT

TXNEXT

TXPEXT

TXVSS

TXVDD

TXP

TXN

RXN

RXP

RXVDD

RXVSS

CVDD

GND

NC

ROM_A8

ROM_A7

ROM_A9

ROM_A6

ROM_A10

ARESET_

SPDSEL

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

GL830

LQFP - 128

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

GPIO4

PHYRDY

DMACK_

GPIO1

IORDY

T_ROM

DIOR_

PIO2

DIOW_

GPIO2

DMARQ

ROM_D5

V5

VDD

VDD

MODE1

GND

CVDD

DD15

ROM_D2

DD0

ROM_D6

DD14

ROM_D1

DD1

ROM_D7

DD13

ROM_D0

DD2

ROM_A0

PIO1

PIO0

Figure 3.3 - 128 Pin LQFP Pinout Diagram

2007 Genesys Logic Inc. - All rights reserved.

Page 12

GL830 USB2.0 to SATA Bridge Controller

3.2 Pin List

Table 3.1 48 Pin List

Pin#

Pin Name

Type Pin#

Pin Name

Type Pin#

Pin Name

Type Pin#

Pin Name

Type

GND

13

GND

25

DM

37

RTERM

GPIO0

14

VDD

26

DP

38

PLLVDD

GPIO3

15

V5

27

AVDD

39

PLLVSS

PIO3

16

NC

28

AGND

40

TXVSS

HRST_

17

GPIO2

29

CVDD

41

TXVDD

CVDD

18

PIO2

30

VDD

42

TXP

VDD

19

NC

31

GND

43

TXN

GND

20

GPIO1

32

VDD

44

RXN

TEST

21

NC

33

X2

45

RXP

10

PIO0

22

AVDD

34

X1

46

RXVDD

11

PIO1

23

RREF

35

CVDD

47

RXVSS

12

CVDD

24

AGND

36

GND

48

CVDD

Pin Name

Type

Table 3.2 64 Pin List

Pin#

Pin Name

Type Pin#

Pin Name

GPIO0

17

NC

33

AVDD

49

PLLVDD

GPIO3

18

NC

34

RREF

50

PLLVSS

PIO3

19

NC

35

AGND

51

RXPEXT

NC

20

CVDD

36

DM

52

RXNEXT

HRST_

21

GND

37

DP

53

TXNEXT

NC

22

VDD

38

AVDD3

54

TXPEXT

NC

23

V5

39

AGND3

55

TXVSS

CVDD

24

NC

40

CVDD

56

TXVDD

VDD

25

GPIO2

41

VDD

57

TXP

10

MODE

26

NC

42

GND

58

TXN

11

GND

27

PIO2

43

VDD

59

RXN

12

TEST

28

NC

44

X2

60

RXP

13

NC

29

NC

45

X1

61

RXVDD

2007 Genesys Logic Inc. - All rights reserved.

Type Pin#

Pin Name

Type Pin#

Page 13

GL830 USB2.0 to SATA Bridge Controller

14

NC

30

GPIO1

46

CVDD

62

RXVSS

15

PIO0

31

NC

47

GND

63

CVDD

16

PIO1

32

NC

48

RTERM

64

GND

Pin Name

Type

Table 3.3 128 Pin List

Pin#

Pin Name

Type Pin#

Pin Name

GPIO0

33

PIO0

65

AINTRQ

97

NC

GPIO3

34

PIO1

66

AVDD

98

NC

PIO4

35

ROM_A0

67

AVDD

99

NC

PIO3

36

DD2

68

RREF

100

NC

ROM_A5

37

ROM_D0

69

AGND

101

NC

DD7

38

DD13

70

AGND

102

NC

ROM_A11

39

ROM_D7

71

DM

103

NC

DD8

40

DD1

72

DP

104

PLLVDD

HRST_

41

ROM_D1

73

AVDD

105

PLLVDD

10

DD6

42

DD14

74

AGND

106

PLLVSS

11

ROM_A4

43

ROM_D6

75

GND

107

RXPEXT

12

DD9

44

DD0

76

GND

108

RXNEXT

13

ROM_A12

45

ROM_D2

77

CVDD

109

TXNEXT

14

DD5

46

DD15

78

DA1

110

TXPEXT

15

ROM_A3

47

CVDD

79

DA0

111

TXVSS

16

CVDD

48

GND

80

NC

112

TXVDD

17

CVDD

49

MODE1

81

DA2

113

TXP

18

VDD

50

VDD

82

ROM_D3

114

TXN

19

MOD0

51

VDD

83

CS0_

115

RXN

20

GND

52

V5

84

ROM_D4

116

RXP

21

DD10

53

ROM_D5

85

CS1_

117

RXVDD

22

ROM_A13

54

DMARQ

86

GND

118

RXVSS

23

TEST

55

GPIO2

87

VDD

119

CVDD

24

TXD

56

DIOW_

88

VDD

120

GND

25

RXD

57

PIO2

89

GND

121

NC

2007 Genesys Logic Inc. - All rights reserved.

Type Pin#

Pin Name

Type Pin#

Page 14

GL830 USB2.0 to SATA Bridge Controller

26

DD4

58

DIOR_

90

GND

122

ROM_A8

27

ROM_A2

59

T_ROM

91

VDD

123

ROM_A7

28

DD11

60

IORDY

92

X2

124

ROM_A9

29

ROM_A14

61

GPIO1

93

X1

125

ROM_A6

30

DD3

62

DMACK_

94

VDD

126

ROM_A10

31

ROM_A1

63

PHYRDY

95

GND

127

ARESET_

32

DD12

64

GPIO4

96

RTERM

128

SPDSEL

3.3 Pin Descriptions

Table 3.4 48 Pin Descriptions

USB Interface

Pin Name

Pin#

Type

Description

RREF

23

Reference resistor

DM

25

HS D-

DP

26

HS D+

AVDD

22,27

USB Analog 3.3V power

AGND

24,28

USB Analog Ground

SATA Interface

Pin Name

Pin#

Type

Description

RTERM

37

Reference resistor

PLLVDD

38

1.8V Power Supplies for internal PLL

PLLVSS

39

Ground for internal PLL

TXVSS

40

Ground for transceiver part

TXVDD

41

1.8V Power Supplies for transceiver part

TXP

42

SATA Differential Transmit TX+

TXN

43

SATA Differential Transmit TX-

RXN

44

SATA Differential Receive RX-

RXP

45

SATA Differential Receive RX+

RXVDD

46

1.8V Power Supplies for receiver part

RXVSS

47

Ground for receiver part

Digital Power and Ground

Pin Name

Pin#

Type

2007 Genesys Logic Inc. - All rights reserved.

Description

Page 15

GL830 USB2.0 to SATA Bridge Controller

CVDD

VDD

GND

V5

6,12,29,

35,48

7,14 30,

32

1,8,13,

31,36

15

1.8V Digital Power

3.3V Digital Power

Digital Ground

5V Power Input

Miscellaneous Interface

Pin Name

Pin#

Type

Description

TEST

X2

33

Crystal Output

X1

34

Crystal Input

HRST_

GPIO0~3

2,20,17,3

PIO0~3

10,11,18,

4

B

(pu)

B

(pd)

NC

16,19,21

I (pd) Test Mode Input

I (pu) Reset Pin

General Purpose I/O #0~#3

Programmable I/O #0~#3

No connection

Table 3.5 64 Pin Descriptions

USB Interface

Pin Name

Pin#

Type

Description

RREF

34

Reference resistor

DM

36

HS D-

DP

37

HS D+

AVDD

33,38

USB Analog 3.3V power

AGND

35,39

USB Analog Ground

SATA Interface

Pin Name

Pin#

Type

Description

RTERM

48

Reference resistor

PLLVDD

49

1.8V Power Supplies for internal PLL

PLLVSS

50

Ground for internal PLL

RXPEXT

51

eSATA Differential Receive RX+

RXNEXT

52

eSATA Differential Receive RX-

2007 Genesys Logic Inc. - All rights reserved.

Page 16

GL830 USB2.0 to SATA Bridge Controller

TXNEXT

53

eSATA Differential Transmit TX-

TXPEXT

54

eSATA Differential Transmit TX+

TXVSS

55

Ground for transceiver part

TXVDD

56

1.8V Power Supplies for transceiver part

TXP

57

SATA Differential Transmit TX+

TXN

58

SATA Differential Transmit TX-

RXN

59

SATA Differential Receive RX-

RXP

60

SATA Differential Receive RX+

RXVDD

61

1.8V Power Supplies for receiver part

RXVSS

62

Ground for receiver part

Digital Power and Ground

Pin Name

CVDD

VDD

GND

V5

Pin#

8,20,40,

46,63

9,22,41,

43

11,21,42,

47,64

23

Type

Description

1.8V Digital Power

3.3V Digital Power

Digital Ground

5V Power Input

Miscellaneous Interface

Pin Name

Pin#

TEST

12

X2

44

Crystal Output

X1

45

Crystal Input

HRST_

I (pu) Reset Pin

MODE

10

I (pd) Mode Select (0=> USB to SATA; 1=> eSATA to SATA)

GPIO0~3

1,30,25,2

PIO0~3

NC

15,16,27,

3

4,6,7,13,

14,17,18,

19,24,26,

28,29,31,

32

Type

Description

I (pd) Test Mode Input

B

(pu)

B

(pd)

General Purpose I/O #0~#3

Programmable I/O #0~#3

No connection

2007 Genesys Logic Inc. - All rights reserved.

Page 17

GL830 USB2.0 to SATA Bridge Controller

Table 3.6 128 Pin Descriptions

USB Interface

Pin Name

Pin#

Type

Description

RREF

68

Reference resistor

DM

71

HS D-

DP

72

HS D+

AVDD

66,67,73

USB Analog 3.3V power

AGND

69,70,74

USB Analog Ground

SATA Interface

Pin Name

Pin#

Type

Description

RTERM

96

Reference resistor

PLLVDD

104,105

1.8V Power Supplies for internal PLL

PLLVSS

106

Ground for internal PLL

RXPEXT

107

eSATA Differential Receive RX+

RXNEXT

108

eSATA Differential Receive RX-

TXNEXT

109

eSATA Differential Transmit TX-

TXPEXT

110

eSATA Differential Transmit TX+

TXVSS

111

Ground for transceiver part

TXVDD

112

1.8V Power Supplies for transceiver part

TXP

113

SATA Differential Transmit TX+

TXN

114

SATA Differential Transmit TX-

RXN

115

SATA Differential Receive RX-

RXP

116

SATA Differential Receive RX+

RXVDD

117

1.8V Power Supplies for receiver part

RXVSS

118

Ground for receiver part

Digital Power and Ground

Pin Name

CVDD

VDD

GND

Pin#

16,17,47,

77,119

18,50,51

87,88,91,

94

20,48,75,

76,86,89,

90,95,

120

Type

Description

1.8V Digital Power

3.3V Digital Power

Digital Ground

2007 Genesys Logic Inc. - All rights reserved.

Page 18

GL830 USB2.0 to SATA Bridge Controller

V5

52

5V Power Input

ATA/ ATAPI Interface (Host mode)

Pin Name

DD0~15

ARESET_

CS1_, CS0_

Pin#

Type

44,40,36,

30,26,14,

10,6,8,12,

21,28,32,

38,42,46

IDE Data Bus

127

I

(pu)

Device Reset

85, 83

I

(pu)

Description

Chip Select #1,#0

DA0~2

79,78,81

I

(pd)

INTRQ

65

IDE interrupt input

DMACK_

62

I

(pu)

IDE Acknowledge

IORDY

60

DIOR_

58

DIOW_

56

DMARQ

54

I

(pu)

I

(pu)

O

IDE Address #2,#1,#0

IDE Ready

IDE read signal

IDE write signal

IDE request

ATA/ ATAPI Interface (Device mode)

Pin Name

Pin#

44,40,36,

30,26,14,

10,6,8,12,

21,28,32,

38,42,46

Type

IDE Data Bus

127

Device Reset

85, 83

Chip Select #1,#0

DA0~2

79,78,81

IDE Address #2,#1,#0

INTRQ

65

I

(pd)

IDE interrupt input

DMACK_

62

IDE Acknowledge

IORDY

60

I

(pu)

DIOR_

58

IDE read signal

DIOW_

56

IDE write signal

DMARQ

54

I

(pd)

DD0~15

ARESET_

CS1_, CS0_

Description

IDE Ready

IDE request

2007 Genesys Logic Inc. - All rights reserved.

Page 19

GL830 USB2.0 to SATA Bridge Controller

Miscellaneous Interface

Pin Name

Pin#

TEST

23

X2

92

Crystal Output

X1

93

Crystal Input

HRST_

MODE0,1

GPIO0~4

PIO0~4

19,49

1,61,55,2,

64

33,34,57,

4,3

TXD

24

RXD

25

SPDSEL

128

PHYRDY

63

T_ROM

59

ROM_A0~14

ROM_D0~7

NC

Notation:

Type

O

I

B

B/I

B/O

P

A

35,31,27,

15,11,5,

125,123,

122,124,

126,7,13,

22,29

37,41,45,

82,84,53,

43,39

80,97,98,

99,100,

101,102,

103

Type

Description

I (pd) Test Mode Input

I (pu) Reset Pin

Mode Select

00=> USB to SATA; 10=> eSATA to SATA;

I

01=> USB to PATA; 11=> SATA to PATA

(pd)

When MODE0,1=11, PIO1=0 is device mode.

When MODE0,1=11, PIO1=1 is host mode.

B

General Purpose I/O #0~#4

(pu)

B

Programmable I/O #0~#4

(pd)

O

8051 UART TXD

(pu)

B

8051 UART RXD

(pu)

I

0 => force in 1.5G; 1 => negotiate interface speed with attached

(pd) device (1.5G or 3G)

O

SATA PHY ready

I (pd) 0 => Internal ROM; 1 => External ROM

B

(pd)

ROM Address #0~#14

ROM Data #0~#7

No connection

Output

Input

Bi-directional

Bi-directional, default input

Bi-directional, default output

Power / Ground

Analog

2007 Genesys Logic Inc. - All rights reserved.

Page 20

GL830 USB2.0 to SATA Bridge Controller

SO

pu

pd

odpu

Automatic output low when suspend

Internal pull up

Internal pull down

Open drain with internal pull up

2007 Genesys Logic Inc. - All rights reserved.

Page 21

GL830 USB2.0 to SATA Bridge Controller

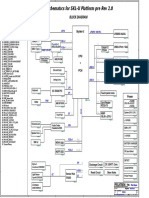

CHAPTER 4 BLOCK DIAGRAM

GPIO

Application Layer

PATA

Transport Layer

SPI

Bulk Buffer

EP0/3 FIFO

Controller

Operation

Register

Link Layer

SIE

8051 Core

PHY Layer

UTM

ROM

eSATA

SATA

RAM

USB

Figure 4.1 - Block Diagram

2007 Genesys Logic Inc. - All rights reserved.

Page 22

GL830 USB2.0 to SATA Bridge Controller

CHAPTER 5 FUNCTION DESCRIPTION

5.1 UTM

The USB 2.0 Transceiver Macrocell, its the analog circuitry that handles the low level USB protocol and

signaling, and shifts the clock domain of the data from the USB 2.0 rate to one that is compatible with the

general logic.

5.2 SIE

The Serial Interface Engine, which contains the USB PID and address recognition logic, and other sequencing

and state machine logic to handle USB packets and transactions.

5.3 EP0/EP3 FIFO and Bulk Buffer

Endpoint 0/3 FIFO: The Control and Interrupt FIFO. It is composed of TX03FIFO and RX03FIFO, with

64-byte FIFO each, and it is used for endpoint 0/3 data transfer.

Bulk Buffer: It is constructed in interleaved architecture and composed by two data buffers which is used to store

data transferred between USB host and IDE device.

5.4 Operation Register

It is a register space to store status information and to control the functions of GL830 by 8051.

5.5 SPI Interface

The Serial Peripheral Interface is a serial, synchronous communication protocol. It is compatible with

Motorolas SPI specifications.

5.6 PHY Layer

It has elastic buffer and supports receiver detection, data serialization and de-serialization.

5.7 Link Layer

The Link layer transmits and receives frames, transmits primitives based on control signals from the Transport

layer, and receives primitives from the Phy layer which are converted to control signals to the Transport layer.

5.8 Transport Layer

The Transport layer constructs Frame Information Structures for transmission and decomposes received Frame

Information Structure

5.9 Application Layer

The Application Layer translates the ATA operation onto internal protocols.

2007 Genesys Logic Inc. - All rights reserved.

Page 23

GL830 USB2.0 to SATA Bridge Controller

CHAPTER 6 ELECTRICAL CHARACTERISTICS

6.1 Absolute Maximum Ratings

Table 6.1 - Maximum Ratings

Symbol

Min.

Typ.

Max.

Unit

Digital I/O pad power supply voltage

3.0

3.3

3.6

Vcore

Digital power supply voltage

1.62

1.8

1.98

VAUSB

Analog power supply voltage for USB PHY

3.0

3.3

3.6

VASATA

Analog power supply voltage for SATA PHY

1.62

1.8

1.98

Static discharge voltage

4000

100

VIO

VESD

TA

Parameter

Ambient Temperature

6.2 Temperature Conditions

Table 6.2 - Temperature Conditions

Item

Value

Storage Temperature

-50oC ~ 150 oC

Operating Temperature

0 oC ~ 70 oC

6.3 DC Characteristics

6.3.1 I/O Type digital pins

Table 6.3 - I/O Type digital pins

Parameter

Min.

Typ.

Max.

Unit

Current sink @ VOL = 0.4V

10.58

14.21

16.87

mA

Current output @ VOH = 2.4V (TTL high)

14.74

27.46

43.0

mA

Falling slew rate at 30 pF loading capacitance

0.56

0.91

1.28

V/ns

Rising slew rate at 30 pF loading capacitance

0.58

0.91

1.72

V/ns

Schmitt trigger low to high threshold point

1.4

1.5

1.6

Schmitt trigger low to high threshold point

1.4

1.5

1.6

Pad internal pull up resister

37.87K

64.7K

108.11K

Ohms

Pad internal pull down resister

29.85K

59.45K

134.26K

Ohms

2007 Genesys Logic Inc. - All rights reserved.

Page 24

GL830 USB2.0 to SATA Bridge Controller

6.3.2 USB Interface DC Characteristics

The GL830 conforms to DC characteristics for Universal Serial Bus specification rev. 2.0. Please refer to this

specification for more information.

6.3.3 SATA Interface DC Characteristics

The GL830 conforms to DC characteristics for Serial ATA specification rev. 2.6. Please refer to this

specification for more information.

6.3.4 Reference Clock Input Requirement

Table 6.6 - Reference Clock Input Requirement

Parameter

Min.

Typ.

Max.

Unit

X1 crystal frequency

25

MHz

X1 cycle time

40

ns

6.3.5 Reference Resistor Requirement

Table 6.7 - Reference Resistor Requirement

Parameter

Min.

Typ.

Max.

Unit

USB Reference Resistor

680

Ohms

SATA Reference Resistor

5.1K

Ohms

6.4 AC Characteristics

6.4.1 USB Interface AC Characteristics

The GL830 conforms to all timing diagrams and specifications for Universal Serial Bus specification rev. 2.0.

Please refer to this specification for more information.

6.4.2 SATA Interface AC Characteristics

The GL830 conforms to all timing diagrams and specifications for Serial ATA specification rev. 2.6. Please

refer to this specification for more information.

2007 Genesys Logic Inc. - All rights reserved.

Page 25

GL830 USB2.0 to SATA Bridge Controller

CHAPTER 7 PACKAGE DIMENSION

Figure 7.1 GL830 48 Pin LQFP Package

2007 Genesys Logic Inc. - All rights reserved.

Page 26

GL830 USB2.0 to SATA Bridge Controller

Figure 7.2 - GL830 64 Pin LQFP Package

2007 Genesys Logic Inc. - All rights reserved.

Page 27

GL830 USB2.0 to SATA Bridge Controller

D

D1

A

A2

96

65

64

97

Green

Package

Internal

No.

GL830

AAAAAAAGAA

YWWXXXXXXXX

Date Code

Code

No.

Lot Code

33

128

4X

32

4X

e

0- 1

aaa C A B D

L1

E2

E1

A1

0.05 S

D2

bbb H A B D

c

ddd M C A B s D s

0-

SEATING

PLANE

ccc C

0- 2

R1

R2

GAGE PLANE

0.25mm

0- 3

NOTES :

1. DIMENSIONS D1 AND E1 DO NOT INCLUDE

MOLD PROTRUSION. ALLOWABLE

PROTRUSION IS 0.25 mm PER SIDE. D1 AND

E1 ARE MAXIMUM PLASTIC BODY SIZE

DIMENSIONS INCLUDING MOLD MISMATCH.

2. DIMENSION b DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL NOT CAUSE THE LEAD

WIDTH TO EXCEED THE MAXIMUM b

DIMENSION BY MORE THAN 0.08mm.

DAMBAR CAN NOT BE LOCATED ON THE

LOWER RADIUS OR THE FOOT.

CONTROL DIMENSIONS ARE IN MILLIMETERS.

MILLIMETER

INCH

SYMBOL

MIN. NOM. MAX. MIN. NOM. MAX.

0.063

1.60

A

0.006

0.05

0.15 0.002

A1

1.35

1.40

1.45 0.053 0.055 0.057

A2

16.00 BASIC

0.630 BASIC

D

16.00 BASIC

0.630 BASIC

E

14.00 BASIC

0.551 BASIC

D1

14.00 BASIC

0.551 BASIC

E1

12.40 BASIC

D2

0.488 BASIC

12.40 BASIC

E2

0.488 BASIC

0.08

0.003

R1

R2

0.08

0.20 0.003

0.008

00

3.5

7

0

3.5

7

0- 1

0

0

0- 2

11

12

13

11

12

13

0- 3

11

12

13

11

12

13

0.09

0.20 0.004

0.008

c

0.45

0.60

0.75 0.018 0.024 0.030

L

L1

1.00 REF

0.039 REF

0.20

0.008

S

0.13

0.16

0.23 0.005 0.006 0.009

b

0.40 BASIC

0.016 BASIC

e

TOLERANCES OF FORM AND POSITION

aaa

0.20

0.008

0.20

0.008

bbb

0.08

0.003

ccc

0.003

ddd

0.07

Figure 7.3 - GL830 128 Pin LQFP Package

2007 Genesys Logic Inc. - All rights reserved.

Page 28

GL830 USB2.0 to SATA Bridge Controller

CHAPTER 8 ORDERING INFORMATION

Table 8.1 - Ordering Information

Part Number

Package

Green

Version

Status

GL830-MNGXX

48-pin LQFP

Green Package

XX

Available

GL830-MSGXX

64-pin LQFP

Green Package

XX

Available

GL830-MXGXX

128-pin LQFP

Green Package

XX

Available

2007 Genesys Logic Inc. - All rights reserved.

Page 29

También podría gustarte

- Network Design Proposal For AirportDocumento16 páginasNetwork Design Proposal For AirportSaiteja Kothapalli67% (12)

- Reviewer CSS 1 8Documento11 páginasReviewer CSS 1 8Leigh Ilustrisimo100% (7)

- Genesys Logic, Inc.: Datasheet Revision 1.02 Aug. 21, 2007Documento29 páginasGenesys Logic, Inc.: Datasheet Revision 1.02 Aug. 21, 2007Raul RondonAún no hay calificaciones

- 3100 3150 MCM User ManualDocumento108 páginas3100 3150 MCM User ManualwagnerpAún no hay calificaciones

- Intel 855GM/855GME Chipset Graphics and Memory Controller Hub (GMCH)Documento213 páginasIntel 855GM/855GME Chipset Graphics and Memory Controller Hub (GMCH)I’M FINE OkAún no hay calificaciones

- Intel 3 Series Express Chipset Family: DatasheetDocumento438 páginasIntel 3 Series Express Chipset Family: DatasheetGabrielAún no hay calificaciones

- m07508207 XXXXXXXX 0 enDocumento424 páginasm07508207 XXXXXXXX 0 enStefan BusoiAún no hay calificaciones

- Intel G35 Express Chipset: DatasheetDocumento351 páginasIntel G35 Express Chipset: DatasheetSrî HárshàAún no hay calificaciones

- 8 Bit Microcontroller: TLCS-870/C SeriesDocumento160 páginas8 Bit Microcontroller: TLCS-870/C SeriesСергей СтаниславскийAún no hay calificaciones

- m07508204 XXXXXXXX 0enDocumento514 páginasm07508204 XXXXXXXX 0enGolliardAún no hay calificaciones

- PMA7105Documento200 páginasPMA7105Alberto MontillaAún no hay calificaciones

- 89 e 58 RD 2Documento81 páginas89 e 58 RD 2Anonymous i62AB9PeigAún no hay calificaciones

- Atom 330 DatasheetDocumento46 páginasAtom 330 DatasheetFederico Estrella RosarioAún no hay calificaciones

- LINX - Configurator User Manual PDFDocumento308 páginasLINX - Configurator User Manual PDFahmad jaberAún no hay calificaciones

- DSP TMS320C2812 DatasheetDocumento177 páginasDSP TMS320C2812 DatasheetJosé Ramón MezaAún no hay calificaciones

- Celeron M DatasheetDocumento69 páginasCeleron M Datasheetbrenosilva1983Aún no hay calificaciones

- E8501 Chipset North BridgeDocumento388 páginasE8501 Chipset North BridgeFranklin JimenezAún no hay calificaciones

- (1Gb Nor Flash) MX66U1G45G, 1.8V, 1Gb, v1.1Documento127 páginas(1Gb Nor Flash) MX66U1G45G, 1.8V, 1Gb, v1.1justy0714Aún no hay calificaciones

- Genesys Logic, Inc.: Datasheet Revision 1.20 Dec. 27, 2002Documento67 páginasGenesys Logic, Inc.: Datasheet Revision 1.20 Dec. 27, 2002Juan Patricio Salamanca ReyesAún no hay calificaciones

- Wago Pfc200maneDocumento460 páginasWago Pfc200maneGaurav BhardwajAún no hay calificaciones

- IA32 Arch Vol ADocumento812 páginasIA32 Arch Vol AKarla VazquezAún no hay calificaciones

- Intel Pentium 4 Processor 6x1 Sequence: DatasheetDocumento108 páginasIntel Pentium 4 Processor 6x1 Sequence: DatasheetjjoaquimmartinsAún no hay calificaciones

- Citect For Windows, Version 5.xx TONS Driver, User Information and DesignDocumento58 páginasCitect For Windows, Version 5.xx TONS Driver, User Information and DesignMohanChandraAún no hay calificaciones

- Intel® 64 and IA-32 Architectures Software Developer's ManualDocumento842 páginasIntel® 64 and IA-32 Architectures Software Developer's ManualJonathan SchubaAún no hay calificaciones

- Atom E3800 Family DatasheetDocumento5050 páginasAtom E3800 Family DatasheetSun minggangAún no hay calificaciones

- Intel Pentium 4 Processor On 90 NM Process: DatasheetDocumento81 páginasIntel Pentium 4 Processor On 90 NM Process: DatasheetDuvan MartinezAún no hay calificaciones

- MSP4301X UsermanualDocumento157 páginasMSP4301X Usermanualsathiya_kala82Aún no hay calificaciones

- Kuka - Usertech 2.3: Kuka Robot Group Kuka System Technology (KST)Documento71 páginasKuka - Usertech 2.3: Kuka Robot Group Kuka System Technology (KST)AnatoliiAún no hay calificaciones

- W83977TFDocumento161 páginasW83977TFJohn HallowsAún no hay calificaciones

- Intel 64 and IA-32 Architectures Software Developers Manual - Volume 2A - Instruction Set Reference A-MDocumento814 páginasIntel 64 and IA-32 Architectures Software Developers Manual - Volume 2A - Instruction Set Reference A-MflovatoAún no hay calificaciones

- Genesys Logic, Inc.: Revision 1.02 Dec. 28, 2006Documento23 páginasGenesys Logic, Inc.: Revision 1.02 Dec. 28, 2006Prasanth KaliAún no hay calificaciones

- cc1310 TRMDocumento1733 páginascc1310 TRMPratimAún no hay calificaciones

- User Manual: Published October 2010Documento61 páginasUser Manual: Published October 2010arbyAún no hay calificaciones

- Data Manual: SM320C6713-EP SM320C6713B-EPDocumento133 páginasData Manual: SM320C6713-EP SM320C6713B-EPdhanaramAún no hay calificaciones

- 64 Ia 32 Architectures Software Developer Instruction Set Reference Manual 325383Documento1493 páginas64 Ia 32 Architectures Software Developer Instruction Set Reference Manual 325383Agustina De NapoliAún no hay calificaciones

- Intel 64 Architecture 2Documento812 páginasIntel 64 Architecture 2seanAún no hay calificaciones

- Intel 845G/845GL/845GV Chipset: DatasheetDocumento193 páginasIntel 845G/845GL/845GV Chipset: DatasheetSatadru BeraAún no hay calificaciones

- AEQ Phoenix Studio Users ManualDocumento128 páginasAEQ Phoenix Studio Users Manualpedreiro1Aún no hay calificaciones

- 7430-3810-04 - B User Manual, DMUX80ZADocumento127 páginas7430-3810-04 - B User Manual, DMUX80ZA李小宇Aún no hay calificaciones

- User Manual 1671799Documento206 páginasUser Manual 1671799EDSON ROCHAAún no hay calificaciones

- Ti 505 BasicDocumento128 páginasTi 505 BasicdrsaylorAún no hay calificaciones

- 318726Documento104 páginas318726evynmsAún no hay calificaciones

- Software Operating Instructions: Quadnet / Duonet OSP - V3.0xDocumento88 páginasSoftware Operating Instructions: Quadnet / Duonet OSP - V3.0xamartins1974Aún no hay calificaciones

- 5210Documento61 páginas5210bocarocaAún no hay calificaciones

- Bosch CC 750Documento58 páginasBosch CC 750wtn2013Aún no hay calificaciones

- p5qc Motherboard Atx PDFDocumento188 páginasp5qc Motherboard Atx PDFOttavio GhisaAún no hay calificaciones

- 253666Documento848 páginas253666damcobbAún no hay calificaciones

- Tms320f2812 Data ManualDocumento151 páginasTms320f2812 Data ManualRogerio Lucas RosaAún no hay calificaciones

- M3A79-T DeluxeDocumento164 páginasM3A79-T Deluxepeeg2ochAún no hay calificaciones

- SDM Vol 2aDocumento710 páginasSDM Vol 2aĐạtAún no hay calificaciones

- 64 Ia 32 Architectures Software Developer Vol 2a ManualDocumento652 páginas64 Ia 32 Architectures Software Developer Vol 2a ManualАлексей ЕршовAún no hay calificaciones

- Amd ManualDocumento921 páginasAmd ManualPrithvi HvAún no hay calificaciones

- 3BSE025998 AlarmDocumento110 páginas3BSE025998 AlarmAmir SayahanAún no hay calificaciones

- 8525 30 G2 User ManualDocumento230 páginas8525 30 G2 User ManualToma HrgAún no hay calificaciones

- DNP3 User Guide Axon Test - 20150728AT38UG0EDocumento61 páginasDNP3 User Guide Axon Test - 20150728AT38UG0Eteo nguyenAún no hay calificaciones

- Asus M3A32-MVP Deluxe Series Manual PDFDocumento176 páginasAsus M3A32-MVP Deluxe Series Manual PDFVali IgnatAún no hay calificaciones

- 200 Series Chipset PCH Datasheet Vol 1 PDFDocumento286 páginas200 Series Chipset PCH Datasheet Vol 1 PDFIglesia RestauracionAún no hay calificaciones

- Winbond LPC I/O W83627THF: Date: August 7, 2003 Revision: 0.8Documento132 páginasWinbond LPC I/O W83627THF: Date: August 7, 2003 Revision: 0.8temp001Aún no hay calificaciones

- Pentium Pro Processor BIOS Writer's Guide: January, 1996Documento73 páginasPentium Pro Processor BIOS Writer's Guide: January, 1996MarcoAún no hay calificaciones

- MGS3750-28F: User's GuideDocumento82 páginasMGS3750-28F: User's GuideLongo LaurisAún no hay calificaciones

- Intel® Atom™ Processor Z6xx Series: DatasheetDocumento47 páginasIntel® Atom™ Processor Z6xx Series: DatasheetLeonard LiuAún no hay calificaciones

- Digital Media Processing: DSP Algorithms Using CDe EverandDigital Media Processing: DSP Algorithms Using CAún no hay calificaciones

- Block Diagram: X453MA Repair GuideDocumento5 páginasBlock Diagram: X453MA Repair GuideCarlosClarosAún no hay calificaciones

- TPCC8131 Datasheet en 20140217Documento9 páginasTPCC8131 Datasheet en 20140217CarlosClarosAún no hay calificaciones

- Dell Vostro 5460 Schematics Version A Quanta Jw8b Jw8c Lapptop SchematicsDocumento56 páginasDell Vostro 5460 Schematics Version A Quanta Jw8b Jw8c Lapptop SchematicsCid Patrick HwfAún no hay calificaciones

- F0af6 Clevo W830T W840TDocumento46 páginasF0af6 Clevo W830T W840TOsvaldo LucianiAún no hay calificaciones

- Hitachi Cdh-Le24fd04 CH 8m35s SvcmnlsDocumento39 páginasHitachi Cdh-Le24fd04 CH 8m35s SvcmnlsCarlosClarosAún no hay calificaciones

- Asus EEEPC 1008ha - Rev 1.3G PDFDocumento1 páginaAsus EEEPC 1008ha - Rev 1.3G PDFCarlosClarosAún no hay calificaciones

- Cifs With RecommendationsDocumento13 páginasCifs With RecommendationsShaon MukherjeeAún no hay calificaciones

- Advantages Disadvantages: 3. Stateful Multilayer Inspection FirewallDocumento2 páginasAdvantages Disadvantages: 3. Stateful Multilayer Inspection FirewallKaren GarzaAún no hay calificaciones

- CCNA 2 (v5.0.3 + v6.0) Chapter 1 Exam Answers 2020 - 100% FullDocumento29 páginasCCNA 2 (v5.0.3 + v6.0) Chapter 1 Exam Answers 2020 - 100% FullwuillianbarretoAún no hay calificaciones

- Day One - Junos For Ios EngineersDocumento55 páginasDay One - Junos For Ios Engineersrockerptit100% (1)

- Ovmsparc Best Practices 2334546Documento30 páginasOvmsparc Best Practices 2334546Tran Minh LongAún no hay calificaciones

- PDFDocumento189 páginasPDFdilshad m shaikh100% (2)

- WCMC Chapter 2 - Mobile Computing - ConciseDocumento20 páginasWCMC Chapter 2 - Mobile Computing - ConciseMehari TemesgenAún no hay calificaciones

- Forensic Science International: Abid Khan Jadoon, Waseem Iqbal, Muhammad Faisal Amjad, Hammad Afzal, Yawar Abbas BangashDocumento15 páginasForensic Science International: Abid Khan Jadoon, Waseem Iqbal, Muhammad Faisal Amjad, Hammad Afzal, Yawar Abbas BangashRaissaAguiarAún no hay calificaciones

- Telehouse Global Data Center SolutionsDocumento15 páginasTelehouse Global Data Center SolutionsTelehouseAmericaAún no hay calificaciones

- Spec Sheet For Edge Gateway 3000 Series (NEW)Documento3 páginasSpec Sheet For Edge Gateway 3000 Series (NEW)Michele BrunelliAún no hay calificaciones

- OracleEBS R12.1.3 QuickRefGuide 2011Documento13 páginasOracleEBS R12.1.3 QuickRefGuide 2011Hossam El-FaxeAún no hay calificaciones

- S. SecurityDocumento2 páginasS. SecurityMuhammad Luthfi ZulfiqarAún no hay calificaciones

- Anviz - VF30 - QuickGuide - New Board - V1.4 - EN PDFDocumento2 páginasAnviz - VF30 - QuickGuide - New Board - V1.4 - EN PDFJeison CubillosAún no hay calificaciones

- Fieldserver Driver - Serial Caterpillar Catm5X Protocol DriverDocumento4 páginasFieldserver Driver - Serial Caterpillar Catm5X Protocol Driversandeep_puri656Aún no hay calificaciones

- E-Tech Q3 Module2Documento16 páginasE-Tech Q3 Module2Ryan Negad50% (2)

- UMTS - WCDMA TechnologyDocumento10 páginasUMTS - WCDMA TechnologysurvivalofthepolyAún no hay calificaciones

- Guide Iridium Skyfile 1 11ENDocumento24 páginasGuide Iridium Skyfile 1 11ENdityoz1288Aún no hay calificaciones

- Is It Possible To Limit How Many Clients Are Able To Connect To An AccessDocumento15 páginasIs It Possible To Limit How Many Clients Are Able To Connect To An Accessatik rahmanAún no hay calificaciones

- Pegatron p3hcj Rev. 2.0 Acer Aspire r7-372tDocumento59 páginasPegatron p3hcj Rev. 2.0 Acer Aspire r7-372tlopezale0393Aún no hay calificaciones

- VAV CablingDocumento2 páginasVAV Cablingsripriya01Aún no hay calificaciones

- 06 DHCP IP ConfigurationDocumento6 páginas06 DHCP IP ConfigurationÁndrian Áde RAún no hay calificaciones

- Sp916gkv6 ManualDocumento78 páginasSp916gkv6 ManualDiego KalikAún no hay calificaciones

- ServicesDocumento10 páginasServicesLukmanKhakimAún no hay calificaciones

- Chapter 02 - Introduction To TechnologyDocumento14 páginasChapter 02 - Introduction To TechnologyAntonyAún no hay calificaciones

- Configuring Any Connect VPN Client ConnectionsDocumento18 páginasConfiguring Any Connect VPN Client ConnectionsJoaquim TchipaAún no hay calificaciones

- 3HH11984AAAATQZZA16 V1 R6.2.04 IHUB QoS GuideDocumento116 páginas3HH11984AAAATQZZA16 V1 R6.2.04 IHUB QoS Guidehadh2311.srovtcAún no hay calificaciones

- AWS Identity and Access Management User GuideDocumento883 páginasAWS Identity and Access Management User Guideshikhaxohebkhan100% (1)

- Datasheet DataMan8700Documento6 páginasDatasheet DataMan8700Erica SöderlundAún no hay calificaciones