Documentos de Académico

Documentos de Profesional

Documentos de Cultura

A Low On-Resistance Triple RESURF SOI LDMOS With Planar and Trench Gate Integration

Cargado por

woshisimoxTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

A Low On-Resistance Triple RESURF SOI LDMOS With Planar and Trench Gate Integration

Cargado por

woshisimoxCopyright:

Formatos disponibles

Chin. Phys.

Vol. 21, No. 6 (2012) 068501

A low on-resistance triple RESURF SOI LDMOS with

planar and trench gate integration

Luo Xiao-Rong()a)b) , Yao Guo-Liang()a) ,

Zhang Zheng-Yuan()b) ,

Jiang Yong-Heng()a) , Zhou Kun( )a) , Wang Pei( )a) , Wang Yuan-Gang()a) ,

Lei Tian-Fei()a) , Zhang Yun-Xuan()a) , and Wei Jie( )a)

a) State Key Laboratory of Electronic Thin Films and Integrated Devices. University of Electronic Science

and Technology of China, Chengdu 610054, China

b) No. 24 Research Institute of China Electronics Technology Group Corporation, Chongqing 400060, China

(Received 23 September 2011; revised manuscript received 17 November 2011)

A low on-resistance (Ron,sp ) integrable silicon-on-insulator (SOI) n-channel lateral double-diused metaloxide

semiconductor (LDMOS) is proposed and its mechanism is investigated by simulation. The LDMOS has two features:

the integration of a planar gate and an extended trench gate (double gates (DGs)); and a buried P-layer in the N-drift

region, which forms a triple reduced surface eld (RESURF) (TR) structure. The triple RESURF not only modulates

the electric eld distribution, but also increases N-drift doping, resulting in a reduced specic on-resistance (Ron,sp )

and an improved breakdown voltage (BV) in the o-state. The DGs form dual conduction channels and, moreover, the

extended trench gate widens the vertical conduction area, both of which further reduce the Ron,sp . The BV and Ron,sp

are 328 V and 8.8 m cm2 , respectively, for a DG TR metaloxidesemiconductor eld-eect transistor (MOSFET)

by simulation. Compared with a conventional SOI LDMOS, a DG TR MOSFET with the same dimensional device

parameters as those of the DG TR MOSFET reduces Ron,sp by 59% and increases BV by 6%. The extended trench gate

synchronously acts as an isolation trench between the high-voltage device and low-voltage circuitry in a high-voltage

integrated circuit, thereby saving the chip area and simplifying the fabrication processes.

Keywords: SOI, electric eld, breakdown voltage, trench gate, specic on-resistance

PACS: 85.30.De, 85.30.Tv, 84.70.p

DOI: 10.1088/1674-1056/21/6/068501

1. Introduction

Lateral double-diused metaloxidesemiconductor (LDMOS) eld eect transistors are widely used

in smart power integrated circuits (ICs) due to their

ease of integration and drive. The on-resistance (Ron )

increases with breakdown voltage (BV) as Ron

BV2.5 in a conventional power LDMOS,[1] resulting in an increase in power loss. The reduced surface eld (RESURF) technique is always employed to

achieve the trade-o between Ron and BV.[26] Trench

gate metaloxidesemiconductor eld-eect transistors (MOSFETs) further reduce the value of Ron

because of the high channel density and the elimination of the junction eld eect transistor (JFET)

eect.[714] Two structures, in which the gate and

the source or the gate and the drain were placed in

one trench, were used to reduce the cell pitch and

Ron,sp .[10,11] Unfortunately, these are good options

only for MOSFETs with BV < 100 V, owing to the

complex fabrication process and weakened eect for

devices with a higher BV. The purpose of this paper

is (i) to realize a high BV, (ii) to minimize the on-state

loss, and (iii) to isolate the low-voltage circuitry from

high-voltage devices in power ICs.

Combining the RESURF technique with the merits of trench gate MOSFETs and LDMOSFETs as

mentioned above, we propose a double gate (DG)

triple RESURF (TR) SOI LDMOS, which integrates

a trench gate and a planar gate. The DGs form dual

conduction channels, thereby reducing the value of

Ron,sp . Furthermore, the buried p-layer (BP) and the

N-drift region form a triple RESURF, thereby increasing the N-drift doping and reshaping the electric eld

distribution. A reduced Ron and an improved BV are

therefore obtained. The extended trench gate realizes

the isolation in a high-voltage IC, with the DG TR

MOSFET serving as its power device.

Project

supported by the National Natural Science Foundation of China (Grant Nos. 61176069 and 609 76060) and the National

Key Laboratory of Analogue Integrated Circuit (Grant No. 9140C090304110C0905).

Corresponding author. E-mail: xrluo@uestc.edu.cn

c 2012 Chinese Physical Society and IOP Publishing Ltd

http://iopscience.iop.org/cpbhttp://cpb.iphy.ac.cn

068501-1

Chin. Phys. B

Vol. 21, No. 6 (2012) 068501

2. Device structure and mechanism

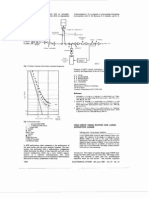

Figure 1 shows a schematic cross section of the

DG TR MOSFET in an HVIC. It has a planar gate

and a trench gate, which is extended to the buried

oxide (BOX). The BP is built into the N-drift region,

forming a triple RESURF and two parallel current

paths. In the layout, the drain region and the trench

gate are in the central and peripheral regions, respectively. For the DG TR MOSFET in the blocking state,

the high potential from the drain is terminated within

the trench gate. A P+ grounded ring encircles the

trench gate, acting as a bypass capacitance to avoid

noise. The extended trench gate thus realizes the isolation between the high-voltage and low-voltage re-

gions. In Fig. 1, Lbp is the length of the BP, D1 is

the distance of the top interface of the BP from the

surface, and tS is the thickness of the SOI layer. Nd

is the doping concentration of the SOI layer, tI is the

thickness of the BOX, and Ld is the length of the drift

region. Figure 1 shows the x and y directions.

In the on-state, the double gates and the BP layer

form two parallel current paths, and the extended

trench gate widens the conduction area; moreover, the

triple RESURF increases the N-drift doping. All of

these reduce the Ron . In the blocking state, the additional PN junctions consisting of the BP and the

N-drift region reshape the electric eld, and the extended trench gate also acts as a gate eld plate, both

of which enhance the BV.

Fig. 1. Schematic cross section of the SOI DG TR LDMOS in an SOI HVIC.

3. Results and discussion

The device structures are investigated by simulation with MEDICI. The models used include CONSRH, AUGER, CONMOB, and FLDMOB, and they

are general models for device simulation. Listed in

Table 1 are the device materials and the same structural parameters for ve types of devices. Figure 2

shows the current owline contours for the DG TR,

trench gate triple RESURF (TG TR), planar gate

triple RESURF (PG TR), and double gate (DG)

MOSFETs without the BP layer, and the conventional

SOI (C-SOI) LDMOS at VGS = 15 V, VDS = 0.5 V

with their own high gure-of-merit (FOM) (FOM =

BV2 /Ron,sp [15] ) value. The dual current paths are

formed above and below the BP layer, respectively,

and the triple RESURF increases the Nd , which both

result in a reduction in the value of Ron,sp . The BP

increases the optimal N d (Nd,o ) from 2.5 1015 cm3

of the DG MOSFET to 8 1015 cm3 of the DG TR

MOSFET. The JEFT eect, caused by the BP, Ndrift and p-body, is nevertheless adverse to the reduc-

tion in Ron for the PG TR and TG TR MOSFETs.

Figure 3 shows their current density distributions at

x = 14 m. The DG TR MOSFET has the highest

average current density and thus the lowest Ron,sp ,

while the C-SOI LDMOS is just the opposite. For

the TG TR, the optimal Nd,o is higher than that for

the PG TR. Furthermore, the extended trench gate

widens the current path, both of which cause a lower

Ron,sp than that of the PG TR.

Table 1. The materials and the same structural parameters for DG TR, TG TR, PG TR, DG, and conventional

SOI MOSFETs (unit: m)

Material

tS

tI

Thickness of BP

Ld

Cell pitch

SOI

18

25

In Fig. 4, the surface eld distributions and the

vertical eld distributions are given with the same

device parameters as those in Fig. 2. The surface

eld plates of the drain/source and planar gate modulate the surface eld. For the DG TR, TG TR, and

068501-2

Chin. Phys. B

Vol. 21, No. 6 (2012) 068501

PG TR devices, the BP layer enhances the vertical

eld strength under the BP layer, thereby enhancing

the eld strength in the buried oxide, as shown in

Figs. 4(b) and 5, respectively. In particular, the extended trench gate acts as a eld plate to enhance

the bulk eld at the source side, especially the lateral eld. These eld-reshaping eects are veried by

comparing the equipotential contours of the dashed

line rectangles in Figs. 5(a), 5(b), and 5(d) with those

of Fig. 5(c), and Fig. 5(e).

Fig. 2. The current owline contours for (a) DG TR; (b) TG TR; (c) PG TR; (d) DG; and (e) C-SOI at their own optimal

condition (i.e. high FOM value). The BP layer thickness is 1 m. VGS = 15 V, VDS = 0.5 V, 106 Am1 /contour.

of Nd , Ron,sp , and BV for ve devices, showing that

the DG TR MOSFET has the highest performance.

Fig. 3. The current densities in the y direction (x =

14 m).

The inuences of Nd on BV and Ron,sp , each as a

function of D1 and Lbp , are shown in Fig. 6. Figure

6(a) shows that the long BP (Lbp > 8 m) eectively

increases the Nd,o and reduces the Ron,sp , maintaining

a high BV. At Lbp = 0, the DG TR is a DG MOSFET,

which has a low Nd,o and high Ron,sp . Figure 6(c)

shows the dependences of the maximum BV (BVmax )

and Ron,sp on Lbp and D1 at their own optimal Nd .

The trade-o between the BV and Ron,sp is obtained

at 18 m< Lbp < 24 m with a 25 m device length.

Figures 6(b) and 6(c) show that D1 has a slight inuence on BV and Ron when 1.3 m < D1 < 2.3 m at

tS = 6 m. Listed in Table 2 are the optimal values

068501-3

Fig. 4. Electric eld distributions of (a) surface eld and

(b) vertical eld in the y direction.

Chin. Phys. B

Vol. 21, No. 6 (2012) 068501

Fig. 5. Equipotential contours at breakdown for (a) DG TR (328 V), (b) TG TR (332 V), (c) PG TR (320 V), (d) DG

(317 V), and (e) C-SOI (308 V), with the same device parameters as those in Fig. 2; the potential dierence between

adjacent equipotential lines is 10 V.

Fig. 6. Dependences of BV and Ron,sp on (a) Nd , each as a function of Lbp (D1 = 1.7 m), (b) on Nd , each as a function of D1

(Lbp = 22 m), (c) on Lbp (D1 = 1.7 m) and D1 (Lbp = 22 m) with their own optimal values of Nd for the DG TR MOSFET.

068501-4

Chin. Phys. B

Vol. 21, No. 6 (2012) 068501

Table 2. BV and Ron,sp for SOI MOSFETs (in the onstate, VGS = 15 V, VDS = 0.5 V).

Device type

Nd,o /1015 cm3 Ron,sp /m cm2 BV/V

DG TR

8.8

328

TG TR

11.8

332

PG TR

4.5

15.5

320

DG

Conventional

SOI LDMOS

2.5

16.7

317

21.6

308

trench, thereby saving the chip area and simplifying

the isolation process in power ICs.

References

[1] Hu C 1979 IEEE Trans. Electron Dev. 26 243

[2] Huang Y S and Baliga B J 1991 Proc. ISPSD 27

[3] Disney D R, Paul A K and Darwish M 2001 Proc. ISPSD

399

The key steps of one of the feasible fabrication

methods for the DTDG SOI MOSFET include implantation followed by Si epitaxy to form the BP layer

and N-drift region; p-well implantation, and annealing the p-well and BP layer; etching the Si trench

and relling polysilicon by in-situ doping; and forming source/drain regions and electrodes.

[4] Guo Y F, Li Z J and Zhang B 2006 Microelectronics Journal 37 861

[5] Hua T T, Guo Y F and Sheu G 2010 Proc. ICSICT 1850

[6] Luo X R, Zhang B and Li Z J 2007 Solid-State Electron

51 493

[7] Disney D, Chan W and Lam R 2008 Proc. ISPSD 24

[8] Udrea F and Amaratunga G A J 1995 IEEE Trans. Electron Dev. 42 1356

[9] Johnny K O S and Wan C 1993 US Patent 5 227 653

[10] Fujishima N, Andre C and Salama T 1997 Proc. IEDM

359

4. Conclusion

A low specic on-resistance integrable SOI nchannel LDMOS is proposed and investigated by simulation. The double gates reduce Ron,sp , and the BP

layer reduces Ron,sp and improves BV. Compared with

conventional SOI LDMOSs, the DG TR MOSFET reduces Ron,sp by 59% and maintains a high BV. The extended trench gate synchronously acts as an isolation

[11] Fujishima N, Sugi A, Andre C and Salama T 2006 US

Patent 7 005 352 B2

[12] Luo X R, Wang Y G, Deng H and Udrea F 2010 Chin.

Phys. B 19 077306

[13] Hu S D, Li Z J, Zhang B and Luo X R 2010 Chin. Phys.

B 19 037303

[14] Luo X R, Fan J and Wang Y G 2011 IEEE Electron Dev.

Lett. 32 185

[15] Ye H and Haldar P 2008 IEEE Trans. Electron Dev. 55

2246

068501-5

También podría gustarte

- Design of High Order Suspended Stripline Bandpass Filter With Miniaturization M. ChenDocumento9 páginasDesign of High Order Suspended Stripline Bandpass Filter With Miniaturization M. ChenArun KumarAún no hay calificaciones

- Manuscript 167 OldDocumento6 páginasManuscript 167 Oldsudipta2580Aún no hay calificaciones

- Dual-Gate Lateral Double-Diffused Metal&ndash Oxide Semiconductor With Ultra-Low Specific On-ResistanceDocumento6 páginasDual-Gate Lateral Double-Diffused Metal&ndash Oxide Semiconductor With Ultra-Low Specific On-ResistanceAnonymous G1iPoNOKAún no hay calificaciones

- H. Liu, D. K. Mohata, A. Nidhi, V. Saripalli, V. Narayanan and S. DattaDocumento2 páginasH. Liu, D. K. Mohata, A. Nidhi, V. Saripalli, V. Narayanan and S. DattaMas MoAún no hay calificaciones

- The Impact of Fringing Field On The Device Performance of A P-Channel Tunnel Field-Effect Transistor With A High-Gate DielectricDocumento6 páginasThe Impact of Fringing Field On The Device Performance of A P-Channel Tunnel Field-Effect Transistor With A High-Gate DielectricdabalejoAún no hay calificaciones

- GIDLDocumento4 páginasGIDLTnSharmaAún no hay calificaciones

- Analytical Modeling of Output Conductanc PDFDocumento7 páginasAnalytical Modeling of Output Conductanc PDFRafael Sanchotene SilvaAún no hay calificaciones

- Microelectronic CircuitDocumento696 páginasMicroelectronic CircuitImtiaz AhmedAún no hay calificaciones

- Microelectronics Journal: Shuguang Han, Baoyong Chi, Zhihua WangDocumento5 páginasMicroelectronics Journal: Shuguang Han, Baoyong Chi, Zhihua WangRAJAMOHANAún no hay calificaciones

- Conclusion:: To DiagnosticsDocumento3 páginasConclusion:: To DiagnosticsDhaval PatelAún no hay calificaciones

- Gate Tunneling Current and Quantum Effects in Deep Scaled MosfetsDocumento5 páginasGate Tunneling Current and Quantum Effects in Deep Scaled Mosfetsashishj1083Aún no hay calificaciones

- Backgate Effect LdmosDocumento7 páginasBackgate Effect LdmosgajananaAún no hay calificaciones

- Compact Microstrip Bandstop Filter for UWB ApplicationDocumento11 páginasCompact Microstrip Bandstop Filter for UWB Application1822601Aún no hay calificaciones

- A Broadband Cmos Multiplier-Based Correlator For Ir-Uwb Transceiver SocDocumento4 páginasA Broadband Cmos Multiplier-Based Correlator For Ir-Uwb Transceiver SocmiracuAún no hay calificaciones

- 343435454Documento5 páginas343435454beefong7680Aún no hay calificaciones

- Bramhane 2016Documento12 páginasBramhane 2016Shashi KantAún no hay calificaciones

- Design of A 2.5Ghz Differential Cmos Lna: Z SC G C L S (L SC LDocumento4 páginasDesign of A 2.5Ghz Differential Cmos Lna: Z SC G C L S (L SC LnaveenmotamarriAún no hay calificaciones

- Design of A 100 V High-Side NCH LDMOS Breakdown EnhanceDocumento4 páginasDesign of A 100 V High-Side NCH LDMOS Breakdown EnhanceRon HuangAún no hay calificaciones

- Review of Modern Field Effect Transistor Technologie1Documento8 páginasReview of Modern Field Effect Transistor Technologie1G ManAún no hay calificaciones

- Aip Adv TfetDocumento10 páginasAip Adv TfetAnik PaulAún no hay calificaciones

- Understanding Power MosfetsDocumento5 páginasUnderstanding Power MosfetsIskander XandrosAún no hay calificaciones

- A Novel Technique To Minimize Standby Leakage Power in Nanoscale CMOS VLSIDocumento4 páginasA Novel Technique To Minimize Standby Leakage Power in Nanoscale CMOS VLSIShiksha SinghAún no hay calificaciones

- Analysis of Interface Switching For NB Doped SrTiO3 Single Crystal Device Using Complex Impedance SpectrosDocumento3 páginasAnalysis of Interface Switching For NB Doped SrTiO3 Single Crystal Device Using Complex Impedance SpectrosEl Mostafa BourimAún no hay calificaciones

- Equivalent Circuit Model of Slotted Ground StructuresDocumento3 páginasEquivalent Circuit Model of Slotted Ground StructureshmalrizzoAún no hay calificaciones

- C-4 Layout of MOS TransistorDocumento82 páginasC-4 Layout of MOS TransistorNelson Lozada DelfinadoAún no hay calificaciones

- Dual Material Gate Technique For Enhanced Transconductance and Breakdown Voltage of Trench Power MOSFETsDocumento17 páginasDual Material Gate Technique For Enhanced Transconductance and Breakdown Voltage of Trench Power MOSFETsMamidala Jagadesh KumarAún no hay calificaciones

- 2019 Nat Photon - Mingbo He - High-Performance Hybrid Silicon and Lithium Niobate Mach-Zehnder Modulators For 100 Gbps and Beyond - SMDocumento9 páginas2019 Nat Photon - Mingbo He - High-Performance Hybrid Silicon and Lithium Niobate Mach-Zehnder Modulators For 100 Gbps and Beyond - SMaliflailasurumiAún no hay calificaciones

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyDe EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyAún no hay calificaciones

- Doping and Doping Less III-V Tunnel Field Effect Transistors (TFET) : Investigation On Reasons For ON Current ImprovementDocumento4 páginasDoping and Doping Less III-V Tunnel Field Effect Transistors (TFET) : Investigation On Reasons For ON Current ImprovementNiranjan ReddyAún no hay calificaciones

- EI2301-IE - Unit 1 - Part A and Part B - With Answers PDFDocumento21 páginasEI2301-IE - Unit 1 - Part A and Part B - With Answers PDFsartpgitAún no hay calificaciones

- Compact Analytical Drain Current Model of Gate-All-Around Nanowire Tunneling FETDocumento5 páginasCompact Analytical Drain Current Model of Gate-All-Around Nanowire Tunneling FETKadava R N Karthik 20PHD7152 (SENSE)Aún no hay calificaciones

- FinFET Inverter Anlaysis PDFDocumento14 páginasFinFET Inverter Anlaysis PDFRakeshAún no hay calificaciones

- Broadband Low Noise Amplifier with Built-in LinearizerDocumento8 páginasBroadband Low Noise Amplifier with Built-in LinearizerRAJAMOHANAún no hay calificaciones

- 8 Chapter-7 & 8 Chapter SolnsDocumento42 páginas8 Chapter-7 & 8 Chapter Solnsapi-3721660Aún no hay calificaciones

- FETDocumento91 páginasFETpawan_32Aún no hay calificaciones

- AN211 FET Teory and PracticeDocumento12 páginasAN211 FET Teory and PracticefabirznAún no hay calificaciones

- Report GF GHJH UghsuhDocumento30 páginasReport GF GHJH UghsuhrayedkhanAún no hay calificaciones

- Leakage Control For Deep-Submicron Circuits: Kaushik Roy, Hamid Mahmoodi-Meimand, and Saibal MukhopadhyayDocumento12 páginasLeakage Control For Deep-Submicron Circuits: Kaushik Roy, Hamid Mahmoodi-Meimand, and Saibal MukhopadhyayDebbrat GhoshAún no hay calificaciones

- Design of New DGS Hairpin Microstrip Bandpass Filter Using Coupling Matrix MethodDocumento5 páginasDesign of New DGS Hairpin Microstrip Bandpass Filter Using Coupling Matrix MethodĐoàn GiangAún no hay calificaciones

- Pid00050 2 CmosDocumento8 páginasPid00050 2 CmosSaurabh ChakravartyAún no hay calificaciones

- Rural News, Jul 2011Documento4 páginasRural News, Jul 2011emediageAún no hay calificaciones

- Effect of Substrate Bias in The Capacitive Coupling of SOI UTBB MOSFETsDocumento4 páginasEffect of Substrate Bias in The Capacitive Coupling of SOI UTBB MOSFETs浜本毅司Aún no hay calificaciones

- Investigation of Channel Doping Concentration and Reverse Boron Penetration On P-Type Pi-Gate Poly-SiDocumento6 páginasInvestigation of Channel Doping Concentration and Reverse Boron Penetration On P-Type Pi-Gate Poly-SimeghrajpurkayasthaAún no hay calificaciones

- Design and Simulation of A Two Stage OPAMPDocumento4 páginasDesign and Simulation of A Two Stage OPAMPAbd TashAún no hay calificaciones

- A Broadband Folded Gilbert Cell CMOS MixerDocumento6 páginasA Broadband Folded Gilbert Cell CMOS MixerMohammedIrshadAhAún no hay calificaciones

- Session 3: Solid State Devices I MOS and Fet (A) : Wednesday, Oct. 18 P.M. To SheratonDocumento2 páginasSession 3: Solid State Devices I MOS and Fet (A) : Wednesday, Oct. 18 P.M. To SheratonManda Praveen KumarAún no hay calificaciones

- RF Switches Using Phase Change Materials: Yonghyun Shim, Gwendolyn Hummel, and Mina Rais-ZadehDocumento4 páginasRF Switches Using Phase Change Materials: Yonghyun Shim, Gwendolyn Hummel, and Mina Rais-ZadehkaurVRAún no hay calificaciones

- Bipolar Charge-Plasma Transistor: A Novel Three Terminal DeviceDocumento6 páginasBipolar Charge-Plasma Transistor: A Novel Three Terminal DevicedabalejoAún no hay calificaciones

- High Voltage Junctionless FET With Improved DC Performance Compared To LDMOSDocumento4 páginasHigh Voltage Junctionless FET With Improved DC Performance Compared To LDMOSIJSTEAún no hay calificaciones

- M MMM M MMM MM MMMM MM MMMM M MM MM M MM MMDocumento19 páginasM MMM M MMM MM MMMM MM MMMM M MM MM M MM MMpiezodocAún no hay calificaciones

- Low Power Design and Simulation of 7T SRAM Cell Using Various Circuit TechniquesDocumento6 páginasLow Power Design and Simulation of 7T SRAM Cell Using Various Circuit TechniquesseventhsensegroupAún no hay calificaciones

- 4.2.5 Sensitivity Analysis: Fig. 4.8 Measurement Setup For The Crosstalk Evaluation. Image Taken Modified FromDocumento8 páginas4.2.5 Sensitivity Analysis: Fig. 4.8 Measurement Setup For The Crosstalk Evaluation. Image Taken Modified FromkarlgAún no hay calificaciones

- High Power VHF Frequency-Hopping FiltersDocumento10 páginasHigh Power VHF Frequency-Hopping FiltersA. VillaAún no hay calificaciones

- Scattering in Nanotransistors: A Numerical Study: Alexei Svizhenko and M. P. AnantramDocumento20 páginasScattering in Nanotransistors: A Numerical Study: Alexei Svizhenko and M. P. AnantramKarunan BathoorAún no hay calificaciones

- Parents, Apr 2011Documento4 páginasParents, Apr 2011emediageAún no hay calificaciones

- A Dual-Polarized Square-Ring Slot Antenna For UWB, Imaging, and Radar ApplicationsDocumento4 páginasA Dual-Polarized Square-Ring Slot Antenna For UWB, Imaging, and Radar ApplicationsSambit Kumar GhoshAún no hay calificaciones

- Analysis of Breakdown Characteristics in Source Field-Plate Algan/Gan HemtsDocumento4 páginasAnalysis of Breakdown Characteristics in Source Field-Plate Algan/Gan HemtsAnonymous jxm0WNS7QaAún no hay calificaciones

- 30.6 A 10Db 44Ghz Loss-Compensated Cmos Distributed AmplifierDocumento3 páginas30.6 A 10Db 44Ghz Loss-Compensated Cmos Distributed AmplifierAli HattabAún no hay calificaciones

- Charge Transport Model of Double Gate Tunnel FETDocumento7 páginasCharge Transport Model of Double Gate Tunnel FETFahad NibirAún no hay calificaciones

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysDe EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysAún no hay calificaciones

- 850 NM VCSEL and PD For Ultra High Speed DataDocumento5 páginas850 NM VCSEL and PD For Ultra High Speed DatawoshisimoxAún no hay calificaciones

- Optical Interconnects For Future Data Center NetworksDocumento179 páginasOptical Interconnects For Future Data Center Networkswoshisimox100% (2)

- 电子设计从零开始Documento374 páginas电子设计从零开始woshisimoxAún no hay calificaciones

- Widely Tunable High Efficiency Pa With Ultra Narrow Instantaneous BandwidthDocumento12 páginasWidely Tunable High Efficiency Pa With Ultra Narrow Instantaneous BandwidthwoshisimoxAún no hay calificaciones

- Eecs 2011 31Documento106 páginasEecs 2011 31woshisimoxAún no hay calificaciones

- Clock Tree Design in Sub-Vt CircuitsDocumento57 páginasClock Tree Design in Sub-Vt CircuitswoshisimoxAún no hay calificaciones

- PA Workshop InstructionDocumento77 páginasPA Workshop InstructionwoshisimoxAún no hay calificaciones

- High Efficiency Cmos Stacked Fet Power Amplifier For Wcdma Applications Using Soi TechnologyDocumento3 páginasHigh Efficiency Cmos Stacked Fet Power Amplifier For Wcdma Applications Using Soi TechnologywoshisimoxAún no hay calificaciones

- BSIM480 ManualDocumento185 páginasBSIM480 ManualwoshisimoxAún no hay calificaciones

- EKVmodelDocumento7 páginasEKVmodelwoshisimoxAún no hay calificaciones

- HiSIM HV 2.1.0 Users ManualDocumento89 páginasHiSIM HV 2.1.0 Users Manualwoshisimox100% (1)

- A General Approach For Multivariate Statistical MOSFET Compact Modeling Preserving CorrelationsDocumento4 páginasA General Approach For Multivariate Statistical MOSFET Compact Modeling Preserving CorrelationswoshisimoxAún no hay calificaciones

- Analog Circuit Sizing Using Adaptive Worst-Case Parameters SetsDocumento5 páginasAnalog Circuit Sizing Using Adaptive Worst-Case Parameters SetswoshisimoxAún no hay calificaciones

- Berkeley DA Noise Analisys Analog RF WPDocumento23 páginasBerkeley DA Noise Analisys Analog RF WPwoshisimoxAún no hay calificaciones

- Analog NoiseDocumento25 páginasAnalog NoiseAshwin BhatAún no hay calificaciones

- A Surface-Potential-Based Compact Model For AlGaNDocumento7 páginasA Surface-Potential-Based Compact Model For AlGaNwoshisimoxAún no hay calificaciones

- Comparative Study of Parasitic Elements On RF Fom in 28 NM FD Soi and Bulk TechnologiesDocumento4 páginasComparative Study of Parasitic Elements On RF Fom in 28 NM FD Soi and Bulk TechnologiesNealAún no hay calificaciones

- Simulation of Single-ElectronDocumento161 páginasSimulation of Single-Electronمزمل اقبالAún no hay calificaciones

- Full Text 01Documento69 páginasFull Text 01Rohit LauvanshiAún no hay calificaciones

- NASA COTS Electronics For SpaceDocumento33 páginasNASA COTS Electronics For SpaceTiago MantayAún no hay calificaciones

- Evolution, Challenge, and Outlook of TSV 3D IC - ICEP April 2011 KeynoteDocumento16 páginasEvolution, Challenge, and Outlook of TSV 3D IC - ICEP April 2011 Keynoteice_speed2006Aún no hay calificaciones

- Midterm Exam 1Documento9 páginasMidterm Exam 1Hemal ShahporiaAún no hay calificaciones

- Vlsi Viva QuestionsDocumento9 páginasVlsi Viva Questionssheethal rokhadeAún no hay calificaciones

- FinfetDocumento71 páginasFinfetaishwarya guttedarAún no hay calificaciones

- Silicon PhotonicsDocumento112 páginasSilicon PhotonicsSabiran GibranAún no hay calificaciones

- A W-Band LNA/Phase Shifter With 5-dB NF and 24-mW Power Consumption in 32-nm CMOS SOIDocumento10 páginasA W-Band LNA/Phase Shifter With 5-dB NF and 24-mW Power Consumption in 32-nm CMOS SOItoto byAún no hay calificaciones

- Introduction To Finfet Hsiao-Chen ChangDocumento124 páginasIntroduction To Finfet Hsiao-Chen Changapi-23860054850% (2)

- Chapter 2 Cmos Fabrication Technology and Design RulesDocumento56 páginasChapter 2 Cmos Fabrication Technology and Design Rulesvanarajesh620% (1)

- Fep - 12 02 03Documento20 páginasFep - 12 02 03lkb9999Aún no hay calificaciones

- Finfet Application Operation PDFDocumento7 páginasFinfet Application Operation PDFSatishEducatioAún no hay calificaciones

- Seminar On FINFET TechnologyDocumento25 páginasSeminar On FINFET TechnologyNamrata Saxena100% (1)

- Simulating Three-Mode Silicon Photonic (De)MultiplexerDocumento15 páginasSimulating Three-Mode Silicon Photonic (De)MultiplexerTran Tuan AnhAún no hay calificaciones

- A Review Paper On Cmos, Soi and Finfet Technology: Einfochips Pvt. Ltd. Ahmedabad, Asic Physical Design EngineerDocumento10 páginasA Review Paper On Cmos, Soi and Finfet Technology: Einfochips Pvt. Ltd. Ahmedabad, Asic Physical Design EngineerRohit JangidAún no hay calificaciones

- Strained Silicon Technology for CMOS ScalingDocumento35 páginasStrained Silicon Technology for CMOS ScalingTanzeem IqbalAún no hay calificaciones

- Double Gate AnalysisDocumento8 páginasDouble Gate AnalysisVishwas GosainAún no hay calificaciones

- CMOS ScalingDocumento19 páginasCMOS ScalingnsrkntAún no hay calificaciones

- 1Documento28 páginas1Ashvinikumar DongreAún no hay calificaciones

- Lecture 1 2013Documento92 páginasLecture 1 2013sohailasghar_tAún no hay calificaciones

- Piyush PPT of ZRAMDocumento16 páginasPiyush PPT of ZRAMPiyush SharmaAún no hay calificaciones

- Ultra-Low-Power 10-Bit 1kS/s SAR-ADC in 28nm FD-SOIDocumento86 páginasUltra-Low-Power 10-Bit 1kS/s SAR-ADC in 28nm FD-SOIVishnuGundaAún no hay calificaciones

- Tcoil SST TX Kossel JSSC 2008Documento16 páginasTcoil SST TX Kossel JSSC 2008顏敬賢Aún no hay calificaciones

- 5gison - Which Impact For Rfsoi Technologies ?: Rfsoi Workshop Shanghai Cédric MalaquinDocumento24 páginas5gison - Which Impact For Rfsoi Technologies ?: Rfsoi Workshop Shanghai Cédric MalaquinHimanshu GondAún no hay calificaciones

- References Leca+Philip Stretchable 50376-2017-Philippe-UnlockedDocumento21 páginasReferences Leca+Philip Stretchable 50376-2017-Philippe-Unlockedck maitiAún no hay calificaciones

- Simulation of SOI PIN Diode for Space Radiation DetectionDocumento12 páginasSimulation of SOI PIN Diode for Space Radiation Detectionzuraixoz7967Aún no hay calificaciones

- Vlsi DesignDocumento215 páginasVlsi Designverilogcourseteam100% (9)

- SOI MosfetDocumento4 páginasSOI MosfetramaswathimAún no hay calificaciones