Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Informe Multietapa

Cargado por

AndresRojasDescripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Informe Multietapa

Cargado por

AndresRojasCopyright:

Formatos disponibles

UNIVERSIDAD PEDAGOGICA Y TECNOLOGICA DE

COLOMBIA

SEDE SECCIONAL SOGAMOSO

ESCUELA DE INGENIERIA ELECTRONICA

LABORATORIO DE ELECTRONICA III

AMPLIFICADORES MULTIETAPA USANDO MODELO

HIBRIDO H

IVAN DAVID ALFONSO DIAZ

e-mail: ivandalf@hotmail.com

GUILLERMO ANDRES ROJAS PIRAZAN

e-mail: daniel.and_rojas10@hotmail.com

Abril 20 de 2012

RESUMEN: En el siguiente laboratorio se

diseara un amplificador multietapa usando el

modelo hibrido H, para unos parmetros

establecidos.

PALABRAS CLAVE: Amplificador, Impedancia,

Parmetros Hbridos, Transconductancia.

1. INTRODUCCIN

Una de las principales aplicaciones de los

transistores es la amplificacin de pequea seal,

por

esto

es

importante

conocer

las

configuraciones de estos. La amplificacin

consiste en generar a la salida del dispositivo una

seal elctrica idntica a la de entrada pero de

mayor amplitud. Los amplificadores pueden ser de

voltaje o de corriente dependiendo de la

configuracin de este.

Cuando se disea un amplificador, no es posible

obtener las caractersticas deseadas (ganancia de

tensin y resistencias de entrada y salida) con una

nica etapa, por lo tanto, ser necesario utilizar

ms de una etapa, resultando un amplificador

multi-etapa en cascada (La salida de una etapa se

conecta a la entrada de la siguiente).

Laboratorio de electrnica III

Pgina 1

2. OBJETIVOS

Disear e implementar un amplificador

multi-etapa con transistores FET y BJT

usando el modelo hibrido H.

Distinguir el funcionamiento tanto en DC

como en AC de los amplificadores FET y

BJT.

Proporcionar las pautas bsicas para el

diseo de amplificador de Audio.

3. MATERIALES Y EQUIPOS

Osciloscopio

Generador de Seales

Protoboard

Resistencias de diferentes valores

Multimetro

Fuentes de alimentacin DC.

Transistores BJT y JFET

Vcc = 24 V

5. PROCEDIMIENTO:

RC = RL = RDC = 56.

Para establecer Qac= 0.5:

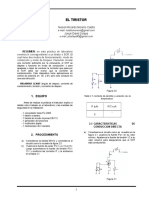

Para el desarrollo de la prctica, se disea un

amplificador multietapa usando el modelo hibrido,

el cual tiene Avt=90, RL=56 y Zi > 100K.

En el diseo del amplificador, se implementara

cuatro etapas, la primera etapa es diseada con

un transistor J-FET para garantizar la impedancia

de entrada con Av=1, la segunda y tercer etapa

son amplificadores en Emisor comn sin

condensador de desacople, ya que tienen

ganancias de voltaje bajas, y la ltima etapa es un

amplificador en colector comn ya que la carga es

pequea. En la figura 1 se puede observar el

diagrama de bloques del amplificador multietapa

completo.

Z L=R ac =RC R L =28

I CQ =

V CC

24

= =285,71mA .

R DC + R ac 84

V CEQ =I CQR ac =8 V

El Beta del par Darlington=132000

I BQ=

I CQ

=2,2 A

V R 1=V B E + I CQRE =17,4 V

I R 1=10I BQ=22 A

R 1=

Figura 1. Diagrama de bloques Amplificador

Multiepata

Inicialmente se disea la cuarta etapa, es

diseada con par Darlington para garantizar una

buena impedancia de entrada, ya que es

considerada para el diseo de la etapa anterior. El

circuito se observa en la figura 2.

V R1

=800 k

I R1

I R 2=I BQ + I R 1=24,2 A

R 2=

V CC V R 1

=273 k

I R2

RB =R1 R 2=203.54 K

z 1=hichfcZ L

Z =Z1 RB =190,37 K

Para el diseo de la tercer etapa se tiene en

cuenta Zin de la etapa siguiente, Av=15, por lo

tanto se disea un amplificador en emisor comn

como el de la figura 3.

Figura 2. Etapa Amplificador en Colector Comn.

Los parmetros hbridos del transistor Darlington

obtenidos experimentalmente son los siguientes:

hfe=102.6K; hie=42K; hre=0,0048; hoe=0,0062

El procedimiento de diseo es el siguiente:

Laboratorio de electrnica III

Pgina 2

V BB =0,7+I CQR E=1.42 V

R c

R 2

Vcc

C 1

Q 2N 3904

R 2=

V CCRB

=2,3 K

V BB

R 1=

V CCR B

=37 K

V CC V BB

C 2

V 3

R 1

R e

R L

Figura 3. Etapa Amplificador en Emisor Comun

Los parmetros hbridos del transistor BJT

obtenidos experimentalmente son los siguientes:

hfe=155; hie=1,2K; hre=0,00016; hoe=0,000032

El procedimiento de diseo es el siguiente:

Av=15; Beta = 150; RL=0,9*Zin=172 K

Se asume RC = 2k

z L =R L R C 1.97 K

Despejando Re de la siguiente ecuacin

hfeZ L

hie+ hfeR E

100

AV =

; RE = 104

Rac =R E +Z L =2.1 K

R DC =RC + R E=2.1 K

Garantizando Qac = 0.5:

I CQ =

V CC

=5.71 mA

Rac + RDC

I

I BQ= CQ =38 A

V CEQ =I CQR ac =11.9V

RB 0.1R E =2.7 K RB =2,2 K

Laboratorio de electrnica III

Pgina 3

z 1=hie+ hfeR E =16,7 K

Z =Z1 RB =1,94 K

Para el diseo del amplificador de la segunda

etapa se procede a medir los parmetros hbridos

experimentalmente en el punto de operacin. Los

parmetros H obtenidos son:

hfe=160; hie=1,1K; hre=0,0003; hoe=0,000052

Beta=180

Teniendo los parmetros H, se disea el

amplificador en configuracin emisor comn, ya

que no se desea una ganancia de voltaje muy

grande, el circuito se observa en la figura 3. El

procedimiento a seguir es el siguiente:

Av=6; Beta = 182; RL=0,9*Zin=1,75 K

Se asume RC = 1,5k

z L =R L R C 806,8

Despejando Re de la siguiente ecuacin

AV =

hfeZ L

hie+ hfeR E

; RE = 150

Rac =R E +Z L =956,8

R DC =RC + R E=1,6 K

Garantizando Qac = 0.5:

I CQ =

V CC

=9,3 mA

Rac + RDC

V CEQ =I CQR ac =9 V

RB 0.1R E =2,7 K RB =2,2 K

V BB =0,7+ I CQR E=2 V

R2=

V CCRB

=2,4 K

V BB

R1=

V CCR B

=27 K

V CC V BB

Z L=R AC RS

Despejando Rs de:

AV =

gm Z L

1+ gm R S

RS =

990

Z L=1,3 K

Z L=R D R L

z 1=hie+ hfeR E =25,1 K

R D=5 K

V =V GS + RS I D =3,9 V

Z =Z1 RB =2 K

Para disear la primera etapa del amplificador, se

implementa un transistor J-FET, el cual tiene como

caractersticas importantes IDss y VGSoff, los

cuales se hallan experimentalmente para obtener

resultados exactos.

Los parmetros obtenidos son:

Tomando

RG >100 K

RG =100 K

R 2=

RG V DD

=615,384 K

V

R 1=

RG V DD

=120 K

V DD V

IDss = 9,1 mA; VGSoff = -3,33V; VDD=24V

El procedimiento de diseo utilizado es el

siguiente:

R L=0,9Z =1,75 K

Se asume

V DSQ =2,5 V

V

I DQ > DSQ =1,72 mA

RL

I DQ=1, 4 mA

Al cambiar los transistores en el amplificador

multietapa ya diseado, este no tiene el mismo

funcionamiento, la misma efectividad, ya que

todos los transistores tienen diferentes parmetros

hbridos para un punto de operacin.

En los anexos, se puede observar la simulacin de

cada etapa y de todo el amplificador multietapa, el

cual tiene una ganancia de voltaje de 90.

Ec. De Shocley

V

I D =I DSS 1 GS

V GSoff

PREGUNTAS

a.

Cmo est conformado el modelo

hibrido H para trabajar a altas

frecuencias? cules son las diferencias

y similitudes con el modelo usado en

estas prcticas?

b.

Consulte acerca del modelo hibrido pi del

transistor y explique cmo funciona.

V GS=2 V

gm=

Ya que

R AC =

2I DSS

V

1 GS =2 mS

V GSoff

V GSoff

Q AC =0,5

V DSQ

=2,36 K

I DQ

Laboratorio de electrnica III

Pgina 4

El modelo hibrido

es importante

cuando el transistor se utilza en alta

frecuencia, en la fig se muestra el modelo

r

para bajas frecuencias.

La corriente de salida circula durante todo el ciclo

de la seal de entrada, en un solo transistor. La

corriente de polarizacin del transistor de salida es

alta y constante durante todo el proceso,

independientemente de si hay o no hay salida de

audio. La distorsin introducida es muy baja, pero

el rendimiento tambin ser bajo, estando siempre

por debajo del 50%.Lo que significa que la otra

mitad de la corriente amplificada ser disipada por

el transistor en forma de calor.

Amplificador clase B

Parmetros del modelo pi

rbb= resistencia de dispersin de base

rbe = resistencia que representa el

efecto de recombinacin de los

portadores minoritarios en la base

rbc = resistencia debida al efecto Early

o modulacin del ancho de base

rce = resistencia entre colector y emisor

salida

gmvbe= corriente de cortocircuito en la

salida, depende de la polarizacin

emisor-base

c.

Realice una tabla donde se especifiquen

las principales caractersticas de cada

una de las etapas utilizadas para la

construccin del amplificador.

Durante un semiciclo la corriente circula y es

amplificada por un transistor, y durante otro

semiciclo circula y es amplificada por otro

transistor, lo cual permite un descanso de un

semiciclo a cada transistor y uno de trabajo y

disipacin de potencia. Adems, no circula

corriente a travs de los transistores de salida

cuando no hay seal de audio.

El problema es que ocurre la llamada "distorsin

por cruce", ya que cuando en el primer semiciclo

la tensin de la seal cae por debajo de los 0.6 V

(tensin aproximada de polarizacin de juntura

base-emisor de un BJT), se despolariza el BJT y

deja de amplificar lo cual tambin ocurre cuando

en el otro semiciclo, la tensin no llega todava a

los 0.6 V. En resumen, en el caso de una senoidal,

tendramos 1.2 V no amplificados, aunque esta no

es la mejor forma de definirlo.

Amplificador de Clase AB

Emisor

comn

sin C

Colector

comn

Z

entrada

Z

salida

media

alta

20 1

alta

alta

Av

Ai

alta

Mismo caso que el amplificador B solo que existe

una pequea corriente que circula por los 2

transistores constantemente, que los polariza

reduciendo enormemente la llamada "distorsion

por cruce". Como en los amplificadores de clase

A, hay una corriente de polarizacin constante,

pero relativamente baja, evitando la distorsin de

cruce (de ah su nombre: AB). En el caso de

amplificadores de sonido son los ms usados

llegando a distorsiones menores del 0.01%

(THD=0.01%)

Los Amplificadores Clase

siguientes caractersticas:

d.

Como se mide la potencia que entrega un

amplificador a la carga.

P=vrmsrms

e.

Que son los amplificadores clase A,

Clase B y clase AB, como funcionan.

Amplificador de Clase A

Laboratorio de electrnica III

Pgina 5

A tienen

las

la seal de salida es un ciclo

completo de la seal de entrada.

Se polariza en el punto medio de

recta de carga. Es decir Q=o.5

El nico transistor amplifica toda la

seal.

Tiene un rendimiento muy bajo

(<25%)

Los Amplificadores Clase

siguientes caractersticas:

tienen

las

Se utilizan dos transistores

Se polariza cada transistor en la

zona de corte.

Cada

transistor

amplifica

un

semiciclo

Tiene mejor rendimiento (hasta

80%).

Los Amplificadores Clase AB tienen las

siguientes caractersticas:

f.

Utiliza dos transistores

Se polariza cada transistor un poco

por encima de la zona de corte.

Cada transistor amplifica un poco

mas de un semiciclo completo.

Tiene menor rendimiento que la

clase B.

Que es un amplificador de audio. Cmo

funciona?

1. CONCLUSIONES

Cuando se desea disear un amplificador

multietapa con varias etapas, es muy importante

tener en cuenta que las fuentes u otros factores

pueden generar ruido que distorsiona la seal

amplificada. Tambin es importante que el

condensador de la salida de la etapa colector

comn sea mayor a 10uF para aislar el nivel DC

de la seal amplificada.

Es importante medir los parmetros hbridos del

transistor a utilizar para un punto de operacin, ya

que el diseo cambia para transistores diferentes.

9. BIBLIOGRAFIA

BOYLESTAD, Robert L. Electrnica: Teora de

Circuitos. Editorial Prentice Hall, 1995.

GUTIERRES, Humberto. Electrnica Anloga:

Teora y laboratorios. Vol. 2.

Laboratorio de electrnica III

Pgina 6

MALVINO, Albert Paul. Principios de electrnica.

Editorial McGraw-Hill, 1991.

Laboratorio de electrnica III

Pgina 7

100mV

50mV

0V

-50mV

-100mV

0s

V(VIN)

1ms

V(R9:2)

2ms

3ms

4ms

5ms

6ms

7ms

8ms

9ms

10ms

Time

Anexo 1: Tabla de datos obtenidos experimentalmente en los circuitos limitadores, sujetadores y

multiplicadores de voltaje:

limitador

voltaje

Vrmsciclo(V)

vpicopico(V)

Vmedio(

V)

Sujetador

voltaje

fig. 6

fig. 6.2

4,08

4,07

7,52

10,2

3

-1,26

fig. 11

Fig. 13

fig. 7

2.49

4.8

2.88

fig. 9

3.32

7.76

110m

Vpico-pico

-14,97

15.07

Vout=43.

Multiplicador

68V

Limitador

fig. 16

Vmi

n

0,90

6

-0,9

vmi

Vpico-pico

n

6.32

2.64

También podría gustarte

- Informe MultietapaDocumento11 páginasInforme MultietapaINGEPEREZ224Aún no hay calificaciones

- Amplificador Con BJT en Emisor ComúnDocumento6 páginasAmplificador Con BJT en Emisor ComúnDaniel OliveraAún no hay calificaciones

- El Transistor Como AmplificadorDocumento4 páginasEl Transistor Como AmplificadorMARTIN RODOLFO LIZOLA GOMEZAún no hay calificaciones

- Laboratorio de FiltrosDocumento17 páginasLaboratorio de FiltrosLuis Mendoza100% (1)

- Limitadores y MultiplicadoresDocumento6 páginasLimitadores y MultiplicadoresMarjo RiveAún no hay calificaciones

- Corrección de la prueba del segundo parcial de Máquinas Eléctricas IIDocumento3 páginasCorrección de la prueba del segundo parcial de Máquinas Eléctricas IIErick Alexander Silva ReyesAún no hay calificaciones

- Experiencia N°1 - EE458Documento3 páginasExperiencia N°1 - EE458diegoAún no hay calificaciones

- SCR funcionamientoDocumento3 páginasSCR funcionamientoNelsito MorenoAún no hay calificaciones

- Informe Multietapa Muy Bueno PDFDocumento11 páginasInforme Multietapa Muy Bueno PDFEduardo Mayorga EspejoAún no hay calificaciones

- Experiencia 7. Amplificador Realimentado (En Cascada)Documento6 páginasExperiencia 7. Amplificador Realimentado (En Cascada)Steven ZacariasAún no hay calificaciones

- Guia de Laboratorio 2-3 Amp. en Cascada y DarlingtonDocumento3 páginasGuia de Laboratorio 2-3 Amp. en Cascada y DarlingtonJeffersonLeonRapAún no hay calificaciones

- Experimento 29Documento3 páginasExperimento 29samuelAún no hay calificaciones

- Práctica Nº5 - Informe (Amplificador Jfet)Documento8 páginasPráctica Nº5 - Informe (Amplificador Jfet)vhirgho13Aún no hay calificaciones

- PRÁCTICA 11 Amplificadores Con JFETDocumento15 páginasPRÁCTICA 11 Amplificadores Con JFETkevinAún no hay calificaciones

- Previo 6 Respuesta de Frecuencia de Circuitos en CADocumento8 páginasPrevio 6 Respuesta de Frecuencia de Circuitos en CAHiuston Cueto CcoriAún no hay calificaciones

- Amplificadores de TensiónDocumento13 páginasAmplificadores de TensiónJose Manuel Mendez Flores100% (1)

- 12 - Autotransformadores PDFDocumento19 páginas12 - Autotransformadores PDFJuan Carlos Choque Martínez100% (1)

- Distribución de Tensión en Cadenas de AisladoresDocumento3 páginasDistribución de Tensión en Cadenas de AisladoresmartinmejiasolanoAún no hay calificaciones

- Transformadores de potencia en subestacionesDocumento13 páginasTransformadores de potencia en subestacionesAnuar LaraAún no hay calificaciones

- Elecproblemas 1 QDocumento83 páginasElecproblemas 1 QAitor De La PintaAún no hay calificaciones

- Reporte de Filtro Pasa BajasDocumento8 páginasReporte de Filtro Pasa BajasBeto RoAún no hay calificaciones

- Practica2 TermistorDocumento44 páginasPractica2 TermistorVerónica Marisol Barros BurneoAún no hay calificaciones

- Informe Nº5 Amplificadores de PotenciaDocumento10 páginasInforme Nº5 Amplificadores de PotenciaMariUsy Virgini'aAún no hay calificaciones

- Troceador Clase ADocumento4 páginasTroceador Clase AJuan Chaug SánchezAún no hay calificaciones

- Nuevas soluciones de calidad de energía para aplicaciones industrialesDocumento1 páginaNuevas soluciones de calidad de energía para aplicaciones industrialesHector Morales BadilloAún no hay calificaciones

- Informe Del Oscilador ColpittsDocumento4 páginasInforme Del Oscilador ColpittsJefferson RoseroAún no hay calificaciones

- Lab 2Documento6 páginasLab 2Cristian Aste PintoAún no hay calificaciones

- Informe Final 5 Circuitos Electronicos 2 PDFDocumento11 páginasInforme Final 5 Circuitos Electronicos 2 PDFEVERAún no hay calificaciones

- Dobladores de VoltajeDocumento3 páginasDobladores de VoltajeBichito LoveAún no hay calificaciones

- El Amplificador Darlington Con BJTDocumento2 páginasEl Amplificador Darlington Con BJTLeirsson PeñalvaAún no hay calificaciones

- Control Por Ángulo de DisparoDocumento3 páginasControl Por Ángulo de DisparoRafael PerezAún no hay calificaciones

- Inversores de onda cuadrada problemasDocumento1 páginaInversores de onda cuadrada problemasCarlos Ernesto Zevallos RuízAún no hay calificaciones

- Epi Laboratorio Citro B Huaman Chacca Alex 8Documento8 páginasEpi Laboratorio Citro B Huaman Chacca Alex 8Steep HacheAún no hay calificaciones

- Caractersiticas de Los BJTDocumento5 páginasCaractersiticas de Los BJTJulian Andres EcheverryAún no hay calificaciones

- Primer Parcial Electrónica 3Documento2 páginasPrimer Parcial Electrónica 3Erik BermudezAún no hay calificaciones

- Limite de OperacionDocumento8 páginasLimite de OperacionCalixto TorresAún no hay calificaciones

- Conexion Cascode Amplificadores Darlington y Darlington Compuesto PDFDocumento16 páginasConexion Cascode Amplificadores Darlington y Darlington Compuesto PDFjohanAún no hay calificaciones

- Formato IEEEDocumento3 páginasFormato IEEErogerAún no hay calificaciones

- Laboratorio1 56Documento4 páginasLaboratorio1 56JassielAún no hay calificaciones

- Contadores digitales: divisores de frecuencia y circuitos integradosDocumento17 páginasContadores digitales: divisores de frecuencia y circuitos integradosmadura123Aún no hay calificaciones

- Ps2320 Problemas Resueltos Bode NyquistDocumento4 páginasPs2320 Problemas Resueltos Bode NyquistJuan Rossel HUAún no hay calificaciones

- Interruptor Estatico de Corriente AlternaDocumento5 páginasInterruptor Estatico de Corriente AlternaTRUJILLO ZULUETA RENATO ANGELOAún no hay calificaciones

- Informe Polarización Por División de VoltajeDocumento8 páginasInforme Polarización Por División de VoltajeEdwin Andres Villamil DiazAún no hay calificaciones

- ConclusionesDocumento9 páginasConclusionesJesus Custodio PisfilAún no hay calificaciones

- Receptor FMDocumento17 páginasReceptor FMteacirtro_777779991100% (1)

- Lab Nº5 - Diseño de Polarización BJT - V12014-IDocumento4 páginasLab Nº5 - Diseño de Polarización BJT - V12014-IJordi EscalanteAún no hay calificaciones

- Amplificadores BJT en CascadaDocumento6 páginasAmplificadores BJT en CascadaJose SegoviaAún no hay calificaciones

- Lab 5 Configuraciones Del Transistor BJTDocumento3 páginasLab 5 Configuraciones Del Transistor BJTanarchy71100% (1)

- Curva Característica del Diodo SemiconductorDocumento3 páginasCurva Característica del Diodo SemiconductorTomoyoKisekoAún no hay calificaciones

- Consulta Transformador Nucleo AcorazadoDocumento3 páginasConsulta Transformador Nucleo AcorazadoGalo HaroAún no hay calificaciones

- Diagrama de Bloques y Principios de FuncionamientoDocumento1 páginaDiagrama de Bloques y Principios de FuncionamientoGustavo AmericoAún no hay calificaciones

- Ecuaciones Diferenciales Amplificador AudioDocumento12 páginasEcuaciones Diferenciales Amplificador AudioAlexis Ang100% (1)

- Práctica 6Documento14 páginasPráctica 6Calvin CantuAún no hay calificaciones

- Folleto Parte IIDocumento118 páginasFolleto Parte IISamuel RodriguezAún no hay calificaciones

- Conclusiones Etn - 503Documento4 páginasConclusiones Etn - 503Aldo Alarcon ContrerasAún no hay calificaciones

- Motor ImpulsionDocumento13 páginasMotor ImpulsionLuis ChacónAún no hay calificaciones

- G.a.3 Aplicaciones en AC Con DiodosDocumento17 páginasG.a.3 Aplicaciones en AC Con DiodosHarry ZaldañaAún no hay calificaciones

- Solucionario 4ta Práctica Calificada EE210 N Ciclo 2020-2Documento5 páginasSolucionario 4ta Práctica Calificada EE210 N Ciclo 2020-2Diego Salazar UrbinaAún no hay calificaciones

- Amplificador multietapa híbrido HDocumento8 páginasAmplificador multietapa híbrido HAndrés AvilaAún no hay calificaciones

- Informe MultietapaDocumento11 páginasInforme MultietapaVanneza CifuentesAún no hay calificaciones

- EXT rQm4BdWO6CjD3bZbeHZMDocumento5 páginasEXT rQm4BdWO6CjD3bZbeHZMAndresRojasAún no hay calificaciones

- Mo 2Documento31 páginasMo 2AndresRojasAún no hay calificaciones

- Válvulas de SeguridadDocumento18 páginasVálvulas de SeguridadjmiguelroAún no hay calificaciones

- Matlab 2Documento33 páginasMatlab 2Zereth Sahar Zav SalcidoAún no hay calificaciones

- 004 Montaje e Instalacion Tableros ElectricosDocumento8 páginas004 Montaje e Instalacion Tableros ElectricosJohn OMAún no hay calificaciones

- Calidad SenaDocumento1 páginaCalidad SenajadechysAún no hay calificaciones

- Automatismos Logica Cableada PDFDocumento21 páginasAutomatismos Logica Cableada PDFalvarolol20085459100% (1)

- Cable Optico Fiber Lan Ar Indoor - Outdoor - ExpDocumento3 páginasCable Optico Fiber Lan Ar Indoor - Outdoor - ExpAndresRojasAún no hay calificaciones

- Subestaciones eléctricas: diseño e innovaciónDocumento100 páginasSubestaciones eléctricas: diseño e innovaciónJose Deniz100% (1)

- Bibliografia de Electricidad y ElectronicaaDocumento2 páginasBibliografia de Electricidad y ElectronicaaRubenBosque67% (3)

- 004 Montaje e Instalacion Tableros ElectricosDocumento8 páginas004 Montaje e Instalacion Tableros ElectricosJohn OMAún no hay calificaciones

- GremioDocumento11 páginasGremioAndresRojasAún no hay calificaciones

- PREVALIDADORESDocumento1 páginaPREVALIDADORESAndresRojasAún no hay calificaciones

- 004 Montaje e Instalacion Tableros ElectricosDocumento8 páginas004 Montaje e Instalacion Tableros ElectricosJohn OMAún no hay calificaciones

- Elementos eléctricos automatismos industrialesDocumento13 páginasElementos eléctricos automatismos industrialesIvan ZukuAún no hay calificaciones

- 004 Montaje e Instalacion Tableros ElectricosDocumento8 páginas004 Montaje e Instalacion Tableros ElectricosJohn OMAún no hay calificaciones

- PROCABLES Resistencia y Reactancia en CA Instalacion Trifasica 600vDocumento16 páginasPROCABLES Resistencia y Reactancia en CA Instalacion Trifasica 600vMauricio Gonzalez CaycedoAún no hay calificaciones

- Cables industriales certificadosDocumento2 páginasCables industriales certificadosAndresRojasAún no hay calificaciones

- 6003978a Esla Pressure Cal Brochure WDocumento32 páginas6003978a Esla Pressure Cal Brochure Wjuncar25Aún no hay calificaciones

- Guia Pat - SRTDocumento27 páginasGuia Pat - SRTingeblancoAún no hay calificaciones

- Puesta A TierraDocumento5 páginasPuesta A TierraYuler Eugenio MamaniAún no hay calificaciones

- 1Documento301 páginas1AndresRojasAún no hay calificaciones

- Puesta A TierraDocumento5 páginasPuesta A TierraYuler Eugenio MamaniAún no hay calificaciones

- Guia Pat - SRTDocumento27 páginasGuia Pat - SRTingeblancoAún no hay calificaciones

- 1244-Texto Del Artículo-2668-1-10-20161212Documento8 páginas1244-Texto Del Artículo-2668-1-10-20161212AndresRojasAún no hay calificaciones

- PROCABLES Resistencia y Reactancia en CA Instalacion Trifasica 600vDocumento16 páginasPROCABLES Resistencia y Reactancia en CA Instalacion Trifasica 600vMauricio Gonzalez CaycedoAún no hay calificaciones

- Rie 07114Documento11 páginasRie 07114AndresRojasAún no hay calificaciones

- Certificados de Calidad 2018Documento3 páginasCertificados de Calidad 2018AndresRojasAún no hay calificaciones

- 1 Indice Dossier Final Cluster 51Documento10 páginas1 Indice Dossier Final Cluster 51AndresRojasAún no hay calificaciones

- Protocolo de Pruebas Producto Terminado: NORMA NTC 2131, NTC 3274, IEC 265-1, IEC 694 Pruebas de RutinaDocumento2 páginasProtocolo de Pruebas Producto Terminado: NORMA NTC 2131, NTC 3274, IEC 265-1, IEC 694 Pruebas de RutinaAndresRojasAún no hay calificaciones

- Que es informática, computación y sus componentesDocumento2 páginasQue es informática, computación y sus componenteserick fuentesAún no hay calificaciones

- Practica Mecatronica: Tableros de MediciónDocumento4 páginasPractica Mecatronica: Tableros de MediciónYoltzin Hdez CAún no hay calificaciones

- Trabsistores Practica 3Documento5 páginasTrabsistores Practica 3Pablo DanielAún no hay calificaciones

- APU-2. Edificio PlazaDocumento181 páginasAPU-2. Edificio PlazaEdwin Angel Pardo QuezadaAún no hay calificaciones

- Definicion de Memoria DigitalDocumento8 páginasDefinicion de Memoria DigitalChristian Aron Iglesias Chingal100% (1)

- Manual de Operacion y Mantenimiento de Rodillo Vibratorio Ca362d PDDocumento126 páginasManual de Operacion y Mantenimiento de Rodillo Vibratorio Ca362d PDSan Juam ContratistasAún no hay calificaciones

- Panel Fotografico BeatoDocumento9 páginasPanel Fotografico BeatoRayLeonardSmithCastañedaCastroAún no hay calificaciones

- FORD Tarjetas de RescateDocumento204 páginasFORD Tarjetas de RescateMiguel Moreno MaciasAún no hay calificaciones

- La Obsolescencia ProgramadaDocumento3 páginasLa Obsolescencia ProgramadaYimitsy Morgan MillerAún no hay calificaciones

- Tracer 9GT-B5U-28197-S0Documento880 páginasTracer 9GT-B5U-28197-S0نهمياسباريرا100% (1)

- Practica 7 DispoDocumento9 páginasPractica 7 DispoOscar MontesAún no hay calificaciones

- Mecanismo de Selector de ObjetosDocumento5 páginasMecanismo de Selector de ObjetosMaicol AvendañoAún no hay calificaciones

- SUBDRENAJE (Autoguardado)Documento14 páginasSUBDRENAJE (Autoguardado)Ronaldo LeyvaAún no hay calificaciones

- Traduccion Manual PARTE 1Documento10 páginasTraduccion Manual PARTE 1Jairo Ivan JIMENEZ RODRIGUEZAún no hay calificaciones

- Propiedades y características de diodos semiconductorDocumento3 páginasPropiedades y características de diodos semiconductorMauricio LlanoAún no hay calificaciones

- Impresoras Matriciales PDFDocumento13 páginasImpresoras Matriciales PDFEdgarForeroAún no hay calificaciones

- Pablo Ramos - Vanessa VargasDocumento21 páginasPablo Ramos - Vanessa VargasPablo RamosAún no hay calificaciones

- Laboratorio N 10 SecuencialDocumento6 páginasLaboratorio N 10 SecuencialAlberto EnriqueAún no hay calificaciones

- Practica Caracterización de La ICT en Un Proyecto Técnico SoluciónDocumento18 páginasPractica Caracterización de La ICT en Un Proyecto Técnico SoluciónRamón Ramírez LuzAún no hay calificaciones

- Despiece TZR 75Documento44 páginasDespiece TZR 75Pablo Perez-Fuentes RamosAún no hay calificaciones

- Practica 1Documento11 páginasPractica 1ValeriaAún no hay calificaciones

- Tarea-fisica3-B Condensadores 5,4-Oriana-100442934Documento5 páginasTarea-fisica3-B Condensadores 5,4-Oriana-100442934Pamela Maceo RosarioAún no hay calificaciones

- 19pfl3403 55 Pss LsppaDocumento3 páginas19pfl3403 55 Pss LsppaJose Miguel ArciaAún no hay calificaciones

- Manual de instrucciones digestor de bagazo R-TE-0501 a R-TE-0504Documento7 páginasManual de instrucciones digestor de bagazo R-TE-0501 a R-TE-0504Walter Antonio Llenque TrellesAún no hay calificaciones

- Interpretación de manuales y folletos de mecánicaDocumento53 páginasInterpretación de manuales y folletos de mecánicaEdwin Luis Shoke CunuranaAún no hay calificaciones

- Motor DCDocumento9 páginasMotor DCLuis Arturo Pola NiñosAún no hay calificaciones

- Formato de presentación de trabajos académicos en mecánica automotrizDocumento34 páginasFormato de presentación de trabajos académicos en mecánica automotrizelias huertaAún no hay calificaciones

- INSTRUCCIONES DE USO Y MANTENIMIENTO MOTORREDUCTORESesDocumento24 páginasINSTRUCCIONES DE USO Y MANTENIMIENTO MOTORREDUCTORESesAparicio NiveckAún no hay calificaciones

- M27C512 EPROM de bajo consumo con programación automáticaDocumento4 páginasM27C512 EPROM de bajo consumo con programación automáticaRoy Garcia PalaciosAún no hay calificaciones

- Suminco Limpiadores Instrucciones InstalaciónDocumento9 páginasSuminco Limpiadores Instrucciones InstalaciónJuan GuillermoAún no hay calificaciones