Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Tema 8 Transp Mem Cam Ram

Cargado por

ppjeans0 calificaciones0% encontró este documento útil (0 votos)

68 vistas6 páginasTRANSPARENCIAS MEMORIAS CAM Y RAM

Derechos de autor

© © All Rights Reserved

Formatos disponibles

PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoTRANSPARENCIAS MEMORIAS CAM Y RAM

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

68 vistas6 páginasTema 8 Transp Mem Cam Ram

Cargado por

ppjeansTRANSPARENCIAS MEMORIAS CAM Y RAM

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Está en la página 1de 6

Memorias RAM y CAM

MEMORIAS RAM Y CAM

RAM = Memorias de acceso aleatorio.

CAM = Memorias de acceso por contenidos.

Memorias de acceso secuencial (FIFO, LIFO).

11.2. ORGANIZACIN DE LAS MEMORIAS SRAM

Las memorias RAM estticas constan de un ncleo de almacenamiento formado por un nmero muy grande de

biestables R-S y un conjunto de circuitos perifricos de direccionamiento y control de las operaciones de las operaciones

de lectura/escritura.

El elemento bsico, la celda R-S, almacena un bit

y el conjunto de celdas (bits) se organizan en

trminos de bytes o palabras, que son grupos de n

bits (8, 13,32, ... ) que se tratan globalmente. Cada

direccin corresponde a una palabra. As, con k

bits podremos direccionar K=2k palabras y la

forma ms inmediata de acceder a cada una de

estas palabras es usando un decodificador de k a

K, tal como se ilustra en la figura.

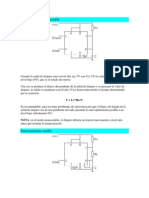

Estructura matricial

Dimensiones horizontal y

vertical del circuito sean

comparables. Esto se

consigue al repartir los bits

de la direccin (Aa, A, ...

,Ak-) en dos grupos, uno

para direccionar las filas

de una matriz (Al, AI+ , ...

,Ak-) Y el otro para

direccionar las columnas

(Aa, A, ... ,AI_)

Pgina 1/6

Memorias RAM y CAM

Cronograma de un ciclo de lectura

Cronograma de un ciclo de escritura

Pgina 2/6

Memorias RAM y CAM

Celdas RAM estticas (SRAM) en tecnologa Bipolar.

Su caracterstica principal es el tiempo de acceso que es muy corto, por ello se emplean principalmente en el diseo de

memorias cach.

Se realiza con transistores multiemisor,

que equivalen a transistores colocados en

paralelo el colector y la base y con la

entrada por emisor. De esta manera, al

conectar un 0 en cualquiera de los dos

emisores, el transistor correspondiente

conducir y por lo tanto la VCE=0V y la

tensin colector masa ser de 0V.

Por convenio se interpreta que se

almacena un 1 cuando Q1 est

conduciendo (Q2 al corte) y un 0

cuando Q1 al corte (Q2 conduciendo).

La salida se obtiene de un amplificador

diferencial, de forma que cuando aparece

un nivel de tensin en la lnea BL

( BL 0V ) habr una cada de tensin

en R3(1) y no la habr en la R3(0),

provocando ello un nivel 1 de salida. Al

revs, cuando aparece un nivel de tensin

en la lnea BL 3,5V (BL=0V) habr

una cada de tensin en R3(0) y no la

habr en la R3(1), provocando ello un

nivel 0 de salida.

Seleccin de celda: La seleccin de celda se producir introduciendo un nivel alto (1) en WL, provocando ello que los

emisores Ei estn los dos a 1 y dejando el estado del transistor en manos de los emisores Ei, o sea en manos

de las entradas de escritura de 1 (BL) o de escritura de 0 BL .

En caso de que WL=0V, los dos emisores Ei estarn a 0V, provocando ello que el biestable permanezca en el

estado anterior. Esto es, si anteriormente Q1 conduca, su VCE=0V por lo que la tensin en B2 era 0V y por lo

tanto Q2 estaba cortado. En estas circunstancias no importa lo que metamos en BL y BL porque nunca

conseguiremos hacer cortarse al transistor que estaba conduciendo, ni conducir al que estaba cortado,

permaneciendo la celda en su estado anterior.

Lectura: Tras seleccionar la celda con WL, solo el emisor del transistor que conduce (Q1 por ejemplo) proporciona

corriente a una de las lneas de datos produciendo un impulso de salida del amplificador de lectura.

Escritura: Se empieza seleccionando la celda mediante WL e introduciendo el dato que queremos meter (nivel lgico 0)

por BL (1) o por BL (0). Por ejemplo supongamos que se quiere introducir un 1, para ello activaremos WL (3V)

e introduciremos un 1 (3V) por BL y un 0 por BL. Un 0 en BL provoca que Q1 conduzca, su VCE=0V y por lo

tanto la VEB2=0V, lo cual provoca que Q2 se corte y su VCE=3V (1). De esta manera la VEB1=3V y provocar

que Q1 conduzca y por lo tanto su VCE=0V, manteniendo con ello el nivel introducido al principio y provocando

su almacenamiento.

Pgina 3/6

Memorias RAM y CAM

Celdas RAM estticas (SRAM) en tecnologa MOS.

La idea bsica es la misma que en el caso bipolar paro a partir de transistores MOS.

Igual que en el caso anterior se dispone de la patilla

de seleccin de celda WL y de las lneas de datos

BL y BL .

Partimos de dos inversores acoplados (Q1-Q3 y Q2Q4) y se aaden otros dos (Q5 y Q6) para habilitar

la lectura y escritura.

Suponer que se almacena un 1 cunado Q1 est

conduciendo y Q2 esta cortado.

Seleccin de celda: La seleccin de celda se

producir introduciendo un nivel alto (1) en

WL, provocando ello que los transistores Q5

y Q6 conduzcan y que por lo tanto se pueda

leer o escribir en la celda.

Lectura: Tras seleccionar la celda con WL, har

que Q5 y Q6 conduzcan y por lo tanto los

valores de los puntos A y B aparezcan en

las lneas BL y BL respectivamente.

Escritura: Se empieza seleccionando la celda mediante WL e introduciendo el dato que queremos meter (nivel lgico 1)

por BL (1) o por BL (0). Por ejemplo supongamos que se quiere introducir un 0, para ello activaremos WL e

introduciremos un 1 por BL y un 0 por BL. Un 0 en BL provoca que la puerta de Q1 se polarice a 0V y por lo

tanto dicho Q1 se corte y la VDS=VDD. Dicha tensin se aplica a la puerta de Q2 y por lo tanto VGS2=VDD. Esto

provoca que Q2 conduzca y por lo tanto su VDS=0V, reforzando y memorizando el nivel inicialmente introducido

de 0V.

Uso del amplificador diferencial en celdas SRAM

Celda SRAM de 4 transistores con carga resistiva

Pgina 4/6

Memorias RAM y CAM

Celdas RAM dinmicas (DRAM) en tecnologa MOS.

En los casos en los que se desea alto nivel de integracin y bajo consumo aunque se penalice con velocidades de

trabajo menores, se recurre a las celdas dinmicas. Bsicamente el diseo consiste en reducir el nmero de transistores

que componen la celda, consiguiendo las caractersticas citadas, obteniendo diferentes configuraciones a cada cual ms

sencilla, hasta llegar el mximo de simplicidad consistente en construir una celda con nico transistor.

Si se compara con la celda esttica se aprecia que se

han eliminado dos transistores y que el elemento

almacenador de informacin son los condensadores C1

y C2. Estos condensadores no se implementan

especficamente en la celda, sino que son las

capacidades parsitas de los propios transistores las

que sirven como elementos almacenadores.

Para evitar la prdida de carga de estos condensadores

se introduce un sistema de refresco a travs de los

transistores Q11 y Q12 que hace que la informacin de

salida se vuelva a meter en la entrada.

El paso posterior fue pasar de cuatro a tres transistores.

Se consigue en base a eliminar la redundancia de

almacenamiento, ya que hasta este momento se

almacenada

la

informacin

deseada

y

su

complementaria.

Como

ahora

la

clula

de

almacenamiento es la capacidad parsita del transistor

MOS, no es necesaria dicha redundancia y por lo tanto

se puede eliminar la mitad de la celda.

La ltima reduccin del tamao de celda en la RAM

dinmica consiste en utilizar un nico transistor y su

capacidad parsita como elemento almacenador.

Su funcionamiento es sencillo, basta un transistor que

permita la entrada y salida de carga al condensador.

Durante el ciclo de escritura se habilita la celda WL y se

introduce el nivel en la entrada BL, al conducir Q1 dicha

carga se introduce en C1 y queda almacenada.

Para su lectura, simplemente se habilita la celda WL,

provocando que Q1 conduzca y que por lo tanto el valor

de C1 aparezca en BL.

Pgina 5/6

Memorias RAM y CAM

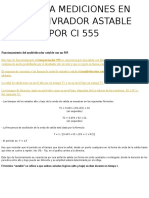

CIRCUITOS DE MEMORIA ASOCIATIVA (CAM)

Celda CAM bsica en CMOS.

Su constitucin bsica consiste en utilizar una celda SRAM de 6 transistores y 4 transistores ms para realizar las

funciones de comparacin del estado de alta o bajadle bit almacenado en los otros seis con el bit correspondiente al

registro patrn.

Pgina 6/6

También podría gustarte

- Adc y DacDocumento9 páginasAdc y DacDarkwolfen GreyhoundAún no hay calificaciones

- Resumen de Las Familias LogicasDocumento18 páginasResumen de Las Familias LogicasjoelAún no hay calificaciones

- Trabajo de Investigación 3 ELA2Documento7 páginasTrabajo de Investigación 3 ELA2Juan David Rodriguez BeltranAún no hay calificaciones

- Practica Temporizador 555Documento15 páginasPractica Temporizador 555Jesús BañosAún no hay calificaciones

- Control Del TLC5940Documento4 páginasControl Del TLC5940bernejorgeAún no hay calificaciones

- Memoria EstaticaDocumento14 páginasMemoria EstaticaPAPOFULEAún no hay calificaciones

- CMOS circuitos familiaDocumento9 páginasCMOS circuitos familiaPaul R. ZamudioAún no hay calificaciones

- Memoria EEPROM Serie 24LC256Documento17 páginasMemoria EEPROM Serie 24LC256Nico DomínguezAún no hay calificaciones

- Polarizacion Del Transistor BJTDocumento29 páginasPolarizacion Del Transistor BJTElias Wilder Solano HuaroccAún no hay calificaciones

- Familias TTL y CmosDocumento14 páginasFamilias TTL y CmosDiana OlivaresAún no hay calificaciones

- Convertidor Adc 0805Documento3 páginasConvertidor Adc 0805vmromerorAún no hay calificaciones

- Cálculo de Un Preamplificador en Emisor ComúnDocumento10 páginasCálculo de Un Preamplificador en Emisor Comúnjljo100% (2)

- Memorias FisicasDocumento8 páginasMemorias FisicasFacundo Esteban PalermoAún no hay calificaciones

- Convertidor AnalogoDocumento3 páginasConvertidor AnalogoJohan Gomez GAún no hay calificaciones

- Las Formas de Onda de Un Astable Con El 555Documento8 páginasLas Formas de Onda de Un Astable Con El 555Mario Eduardo Ponce GomezAún no hay calificaciones

- Polarizacion Del Transistor BJTDocumento29 páginasPolarizacion Del Transistor BJTLarry Christian Tumialán BorjaAún no hay calificaciones

- El Transistor Sin PolarizaciónDocumento12 páginasEl Transistor Sin PolarizaciónYESID GERARDO MONCADA RUBIOAún no hay calificaciones

- Resumen Unidad 5 - Juan Manuel GonzalezDocumento6 páginasResumen Unidad 5 - Juan Manuel Gonzalezcpyin88Aún no hay calificaciones

- Transistores MOSDocumento13 páginasTransistores MOStoniskaiAún no hay calificaciones

- Disipación de PotenciaDocumento11 páginasDisipación de PotenciaBrian AvalosAún no hay calificaciones

- Informe PreamplificadorDocumento26 páginasInforme PreamplificadorNico SuAún no hay calificaciones

- Circuitos TTL y CmosDocumento5 páginasCircuitos TTL y CmosAlondra TaveraAún no hay calificaciones

- Familias Logicas TTL y CMOSDocumento8 páginasFamilias Logicas TTL y CMOSDaniel DzulAún no hay calificaciones

- Cargador Automático de BateríasDocumento5 páginasCargador Automático de BateríasRoJaS2109Aún no hay calificaciones

- Amplificador cuasicomplementario en contrafase: análisis y optimizaciónDocumento24 páginasAmplificador cuasicomplementario en contrafase: análisis y optimizaciónGastonRodrigoPotenzaAún no hay calificaciones

- Consulta 2Documento7 páginasConsulta 2Fernando Guilcaso RieraAún no hay calificaciones

- ADC0804Documento5 páginasADC0804Juan Sebastian AcevedoAún no hay calificaciones

- 17 - Relojes o Multivibradores AstablesDocumento16 páginas17 - Relojes o Multivibradores AstablesMatías Felipe Contardo100% (1)

- Termometro DigitalDocumento6 páginasTermometro DigitalHamlet Deathbat GatesAún no hay calificaciones

- Laboratorio 02 Final - CompletoDocumento15 páginasLaboratorio 02 Final - CompletoCarlos Ernesto Flores AlbinoAún no hay calificaciones

- Oscilador Astable Con Transistores BJTDocumento21 páginasOscilador Astable Con Transistores BJTSanty Marchulo VenegasAún no hay calificaciones

- Convertidor Digital AnalógicoDocumento9 páginasConvertidor Digital AnalógicoWaked Mohamed100% (1)

- Análisis del LM3524 para conversión DC/DCDocumento7 páginasAnálisis del LM3524 para conversión DC/DCDiego ArmandoAún no hay calificaciones

- Previo 1 Sist. DigitalesDocumento13 páginasPrevio 1 Sist. DigitalesValeria Andrea Nina ArrescurenagaAún no hay calificaciones

- Familias Lógicas BipolaresDocumento8 páginasFamilias Lógicas BipolarestoniskaiAún no hay calificaciones

- Trabajo (Sistema Secuencial)Documento35 páginasTrabajo (Sistema Secuencial)zulyAún no hay calificaciones

- Transistor BJTDocumento35 páginasTransistor BJTFrancisco HernandezAún no hay calificaciones

- Sistema de Alimentacion y RespaldoDocumento22 páginasSistema de Alimentacion y RespaldoIsaac Tellez100% (1)

- Circuito RC Aplicado Al 555Documento11 páginasCircuito RC Aplicado Al 555Pablo HernandezAún no hay calificaciones

- Circuito de Protección Integral de Amplificadores y ParlantesDocumento7 páginasCircuito de Protección Integral de Amplificadores y ParlantesEsther RomeroAún no hay calificaciones

- Tarea de Mayela Inv ObettDocumento12 páginasTarea de Mayela Inv ObettIndira RamirezAún no hay calificaciones

- 8Documento14 páginas8Percy Flores MoralesAún no hay calificaciones

- DisEtnII 2 Conversor ADC y DAC PDFDocumento6 páginasDisEtnII 2 Conversor ADC y DAC PDFclaudioruAún no hay calificaciones

- ds1307 - RTC en EspañolDocumento11 páginasds1307 - RTC en EspañolWilson Reina PulidoAún no hay calificaciones

- Familia DTLDocumento3 páginasFamilia DTLHenry LazoAún no hay calificaciones

- Multivibrador Astable Con Un 555Documento7 páginasMultivibrador Astable Con Un 555Meza Puchoc JeanAún no hay calificaciones

- Etapas de PotenciaDocumento13 páginasEtapas de PotenciaAlvaro HerreraAún no hay calificaciones

- Convertidor DaDocumento3 páginasConvertidor DaJose Cortes BenavidesAún no hay calificaciones

- Info Previo 01digi IIDocumento12 páginasInfo Previo 01digi IIFelipe CarreñoAún no hay calificaciones

- Practica 8 Lab. Elect. IIDocumento8 páginasPractica 8 Lab. Elect. IILuis Ernesto PalmarAún no hay calificaciones

- Laboratorio de circuitos ADC y DAC de 3 bitsDocumento12 páginasLaboratorio de circuitos ADC y DAC de 3 bitsosmarAún no hay calificaciones

- Tarea 2.4 Conocer y Analizar La Operación de Los Convertidores de Resistencias Ponderadas y R-2RDocumento10 páginasTarea 2.4 Conocer y Analizar La Operación de Los Convertidores de Resistencias Ponderadas y R-2RFernando RiosAún no hay calificaciones

- Amplificador Diferencial - Edgar Uriel Hernández MartínezDocumento7 páginasAmplificador Diferencial - Edgar Uriel Hernández MartínezEdgar Uriel Hernández MartínezAún no hay calificaciones

- Funcionamiento Del Convertidor Analógico Digital ADC0809Documento5 páginasFuncionamiento Del Convertidor Analógico Digital ADC0809Jorge CaballeroAún no hay calificaciones

- Circuito Astable de Onda SimétricaDocumento6 páginasCircuito Astable de Onda SimétricaFernando AstrozaAún no hay calificaciones

- Armónicas en Sistemas Eléctricos IndustrialesDe EverandArmónicas en Sistemas Eléctricos IndustrialesCalificación: 4.5 de 5 estrellas4.5/5 (12)

- 100 Circuitos de Shields para MotoresDe Everand100 Circuitos de Shields para MotoresCalificación: 4.5 de 5 estrellas4.5/5 (4)

- Quiz-GESTION DE EMPRESAS INFORMATICASDocumento3 páginasQuiz-GESTION DE EMPRESAS INFORMATICASppjeansAún no hay calificaciones

- Base de Datos AutomóvilesDocumento3 páginasBase de Datos AutomóvilesJorge Rollán DiezAún no hay calificaciones

- Tema 3 Autoevaluación (Soluciones)Documento12 páginasTema 3 Autoevaluación (Soluciones)ppjeansAún no hay calificaciones

- Unidad 1 - Auto-EvaluaciónDocumento10 páginasUnidad 1 - Auto-EvaluaciónppjeansAún no hay calificaciones

- Migración de BBDD Access A Base y MySQLDocumento51 páginasMigración de BBDD Access A Base y MySQLMarcelo Uribe CastroAún no hay calificaciones

- Unidad 1 - Auto-Evaluación PDFDocumento10 páginasUnidad 1 - Auto-Evaluación PDFppjeansAún no hay calificaciones

- Migración de BBDD Access A Base y MySQLDocumento51 páginasMigración de BBDD Access A Base y MySQLMarcelo Uribe CastroAún no hay calificaciones

- Pautas 8757593 PDFDocumento1 páginaPautas 8757593 PDFppjeansAún no hay calificaciones

- Notas de La Versión 6.0.8Documento17 páginasNotas de La Versión 6.0.8ppjeansAún no hay calificaciones

- Cupones C Ene2017penbalcDocumento3 páginasCupones C Ene2017penbalcppjeansAún no hay calificaciones

- 2010 ExamDocumento2 páginas2010 ExamSandraMireyaAún no hay calificaciones

- Auto Tema 1Documento2 páginasAuto Tema 1borjita_delan88Aún no hay calificaciones

- Notas de La Versión 7.0.2Documento10 páginasNotas de La Versión 7.0.2ppjeansAún no hay calificaciones

- Notas de La Versión 6.0.8Documento17 páginasNotas de La Versión 6.0.8ppjeansAún no hay calificaciones

- Pautas 8757593Documento1 páginaPautas 8757593ppjeansAún no hay calificaciones

- GusanoDocumento1 páginaGusanodeyanira17Aún no hay calificaciones

- Plan de clases Ingeniería InformáticaDocumento3 páginasPlan de clases Ingeniería InformáticaMireya Claramonte GarciaAún no hay calificaciones

- Guia de Estudio 1 PDFDocumento7 páginasGuia de Estudio 1 PDFppjeansAún no hay calificaciones

- Tabla Formulas EstadisticaDocumento3 páginasTabla Formulas EstadisticappjeansAún no hay calificaciones

- Mario Net AsDocumento7 páginasMario Net AsppjeansAún no hay calificaciones

- TrazalacasaDocumento1 páginaTrazalacasaJoves PerruquersAún no hay calificaciones

- Apuntes Bachillerato Fisica ElectromagnetismoDocumento9 páginasApuntes Bachillerato Fisica ElectromagnetismoSara SánchezAún no hay calificaciones

- APUNTES MAQUINAS ELECTRICAS - U 3 v1.1Documento54 páginasAPUNTES MAQUINAS ELECTRICAS - U 3 v1.1TGreatJhonnIE TTos100% (1)

- Sincronización Chevrolet Cruze 1.8LDocumento20 páginasSincronización Chevrolet Cruze 1.8LHector Flores de Jesus91% (11)

- Manual de Usuario DVR AVTECH MDR751ZB v20110203Documento59 páginasManual de Usuario DVR AVTECH MDR751ZB v20110203cencom100% (1)

- Teoria 5 - DielectricosDocumento48 páginasTeoria 5 - DielectricossalvornahuelAún no hay calificaciones

- MariaDB VentajasDocumento2 páginasMariaDB VentajasJon LinkAún no hay calificaciones

- Parraga Kevin Preparatorio#1Documento4 páginasParraga Kevin Preparatorio#1Juan David RamírezAún no hay calificaciones

- Motores CA: Asíncronos y SíncronosDocumento87 páginasMotores CA: Asíncronos y SíncronosNinoska MaciasAún no hay calificaciones

- Inversor 3000w IGBT PWM onda senoidalDocumento9 páginasInversor 3000w IGBT PWM onda senoidalJuan ArayaAún no hay calificaciones

- Ayudantia Fisica 120 USMDocumento7 páginasAyudantia Fisica 120 USMPancho BascuñanAún no hay calificaciones

- Mar de Dirac PDFDocumento2 páginasMar de Dirac PDFNoe Hernandez TorrejonAún no hay calificaciones

- METALOGRAFIADocumento5 páginasMETALOGRAFIAGabii DominguezAún no hay calificaciones

- Manual de Uso BonusNet Ed.1.0Documento56 páginasManual de Uso BonusNet Ed.1.0vsilva_200967% (3)

- Fundamentos de Los Generadores Electricos en CDDocumento11 páginasFundamentos de Los Generadores Electricos en CDLuis Angel Ortega MárquezAún no hay calificaciones

- Proyecto Final-Redes Emergentes-Perla Jennifer Mendoza MartinezDocumento69 páginasProyecto Final-Redes Emergentes-Perla Jennifer Mendoza MartinezPerla Jennifer Mendoza MartinezAún no hay calificaciones

- Componentes de Control de FrenosDocumento20 páginasComponentes de Control de FrenosJose Vicente Yago MoraAún no hay calificaciones

- Modulación DBL 40Documento9 páginasModulación DBL 40GustavoAún no hay calificaciones

- ElectricidadDocumento9 páginasElectricidadJosue QuintanaAún no hay calificaciones

- Cambiar El Fondo e Icono de Una Memoria USBDocumento4 páginasCambiar El Fondo e Icono de Una Memoria USBPako PadillaAún no hay calificaciones

- Accionamientos Con Motor EléctricoDocumento38 páginasAccionamientos Con Motor EléctricoEric AndrésAún no hay calificaciones

- Resistencia de diodos semiconductorDocumento12 páginasResistencia de diodos semiconductorNehemias RiveraAún no hay calificaciones

- ModuloI AjusteespacialDocumento10 páginasModuloI AjusteespacialJorge DíazAún no hay calificaciones

- PLC Fatek EspDocumento25 páginasPLC Fatek EspEddy SanchezAún no hay calificaciones

- Comportamiento Circuitos RLCDocumento29 páginasComportamiento Circuitos RLCmiguel gtzAún no hay calificaciones

- Examen Electrónica DigitalDocumento19 páginasExamen Electrónica DigitalNiria Camacho MendozaAún no hay calificaciones

- Unidades Protocolo de Fotocurado PDFDocumento10 páginasUnidades Protocolo de Fotocurado PDFMaria EuanAún no hay calificaciones

- Generaciones de Los S.O. (Sistemas OperativosDocumento9 páginasGeneraciones de Los S.O. (Sistemas OperativosCristian GabrielAún no hay calificaciones

- Investigación Sistema Solares Fotovoltaicos y Térmicos-2.3 y 2.4 - Azucena Rasgado LorenzoDocumento20 páginasInvestigación Sistema Solares Fotovoltaicos y Térmicos-2.3 y 2.4 - Azucena Rasgado Lorenzol20770126Aún no hay calificaciones

- Calculo de Barras Colectoras en Una Subestacion ElectricaDocumento15 páginasCalculo de Barras Colectoras en Una Subestacion ElectricaSantiago Carrasco100% (1)

- Pensum Electricidad y Electronica Automotriz PDFDocumento1 páginaPensum Electricidad y Electronica Automotriz PDFAriel Toño Vaquera ZeballosAún no hay calificaciones

- Lab 01 - Motor ElectricoDocumento13 páginasLab 01 - Motor ElectricoSantiago Santa CruzAún no hay calificaciones