Documentos de Académico

Documentos de Profesional

Documentos de Cultura

130MC Iab

Cargado por

SD Nicolas HTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

130MC Iab

Cargado por

SD Nicolas HCopyright:

Formatos disponibles

S.E.P. S.E.I.T. D.G.I.T.

CENTRO NACIONAL DE INVESTIGACIN

Y DESARROLLO TECNOLGICO

cenidet

DESARROLLO E IMPLEMENTACIN DE UN

BANCO DE PRUEBAS PARA CARACTERIZAR

DISPOSITIVOS DE ALTA POTENCIA

T E S I S

PARA OBTENER EL GRADO DE

MAESTRO EN CIENCIAS EN

INGENIERA ELECTRNICA

P R E S E N T A:

ING. IVN ALCAL BAROJAS

DIRECTORES DE TESIS

DR. ABRAHAM CLAUDIO SNCHEZ

DRA. MARA COTOROGEA PFEIFER

CUERNAVACA, MOR. MARZO 2003

S.E.P. S.E.I.T. D.G.I.T.

CENTRO NACIONAL DE INVESTIGACIN

Y DESARROLLO TECNOLGICO

cenidet

DESARROLLO E IMPLEMENTACIN DE UN

BANCO DE PRUEBAS PARA CARACTERIZAR

DISPOSITIVOS DE ALTA POTENCIA

T E S I S

PARA OBTENER EL GRADO DE

MAESTRO EN CIENCIAS EN

INGENIERA ELECTRNICA

P R E S E N T A:

ING. IVN ALCAL BAROJAS

DIRECTORES DE TESIS

DR. ABRAHAM CLAUDIO SNCHEZ

DRA. MARA COTOROGEA PFEIFER

CUERNAVACA, MOR. MARZO, 2003

CONTENIDO

Simbologa iii

Nomenclatura v

Captulo 1 Planteamiento del problema y justificacin

1.1 Dispositivos Semiconductores de Potencia Controlados (DSEP)

1.1.1 Caractersticas de los dispositivos semiconductores de

potencia

1.1.2 Comparacin entre los diferentes dispositivos

1.2 El tiristor de apagado por compuerta (GTO)

1.2.1 Estructura y funcionamiento

1.2.2 Caractersticas

1.2.3 Mejoras realizadas

1.3 El transistor bipolar de compuerta aislada (IGBT)

1.3.1 Estructura y funcionamiento

1.3.2 Caractersticas

1.3.3 Tecnologas de fabricacin del IGBT

1.4 Modos de conmutacin

1.5 Justificacin

1.6 Objetivos

Captulo 2 Metodologa abordada

2.1 Caracterizacin experimental

2.1.1 Diseo general del circuito de pruebas

2.1.1.1 Mtodo de prueba

2.1.1.2 Modo de funcionamiento

2.1.1.3 Tipo de control

2.1.2 Diseo propuesto para los circuitos de prueba

2.2 Caracterizacin mediante simulacin

2.3 tipos de fuentes

2.3.1 Flyback

2.3.2 Push-pull

2.3.3 Medio puente

2.3.4 Puente completo

2.3.5 Fuente de alta potencia

2.4 Conclusiones

i

2

3

4

6

6

8

9

11

13

13

14

16

17

18

20

20

20

21

22

23

24

25

26

27

28

29

30

33

Captulo 3 Fuente de alto voltaje

3.1 Caractersticas de fuentes de alto voltaje

3.2 Diseo de la fuente de CD

3.2.1 Diseo de la etapa inversora

3.2.2 Diseo del transformador

3.2.3 Diseo de la etapa de rectificacin y filtrado

3.3 Modelo matemtico de la fuente de CD

3.3.1 Funcionamiento

3.3.2 Anlisis estacionario

3.4 Anlisis en simulacin y validacin experimental

3.5 Anlisis transitorio durante el cargado del condensador

3.6 Conclusiones

Captulo 4 Banco de pruebas

4.1 Caractersticas generales

4.2 Almacenamiento de energa

4.3 Circuito de prueba

4.3.1 Conmutacin dura

4.3.1.1 Circuito de potencia

4.3.1.2 Principio de funcionamiento

5.3.1.3 Consideraciones de diseo

4.3.2 Corto circuito tipo I

4.3.2.1 Circuito de potencia

4.3.2.2 Principio de funcionamiento

4.3.2.3 Consideraciones de diseo

4.4 Conclusiones

Captulo 5 Pruebas y Resultados

5.1 Pruebas en conmutacin dura

5.1.1 Consideraciones en simulacin

5.1.2 Consideraciones en pruebas experimentales

5.1.3 Variacin del voltaje de alimentacin V0

5.1.4 Variacin de la corriente de carga IC

5. 2 Pruebas en corto circuito

5.3 Conclusiones

36

36

36

41

43

43

43

45

46

51

52

54

55

55

56

56

57

60

61

61

62

64

64

66

66

68

69

69

78

80

Capitulo 6 Conclusiones y trabajos futuros 81

Bibliografa 85

Anexo I Anlisis en Mathcad 87

Anexo II Hojas de datos 93

ii

SIMBOLOGA

Eficiencia

( Regulacin

(1, (2 Factor de amplificacin de corriente

i Variacin de corriente

t Variacin del tiempo

Ac rea efectiva del ncleo

Ap Producto de reas

At rea de superficie

Aw(B) Tamao del alambre

Bm Densidad de flujo

C1,2,... Capacitor

CL Capacitor de filtrado

Cp Capacitancia parsita

Ct Capacitor de oscilacin

D Ciclo de trabajo

D1,2 Diodo

D1R,2R,... Diodos del rectificador

DE Diodo de emisor

di/dt Pendiente de corriente

dv/dt Pendiente de voltaje

E Energa

f Frecuencia

fosc Frecuencia de oscilacin

IA Corriente de nodo

iCap Corriente en capacitor

IC Corriente de carga

iD Corriente a la salida del rectificador

ID1,D2,... Corriente en el diodo

IG, IGQ Corriente de compuerta

Iin Corriente de entrada

IK Corriente de ctodo

iL Corriente en la carga o de salida

INS Corriente en el secundario del transformador

Io Corriente de salida

ip Corriente en el primario del transformador

Iprom Corriente promedio en el transistor

Ipt Corriente pico del transistor

IQ1,Q2,Q3 Corriente en el transistor

ireg Corriente en los IGBTs del regulador

is Corriente en el secundario del transformador

J Densidad de corriente

iii

J3, J2, J1 Uniones del dispositivo

Ke Coeficiente elctrico

Kf Coeficiente de la forma de onda

Kg Geometra del ncleo

Ku Factor de utilizacin de ventana

Lcarga Inductancia de carga

Lp Inductancia del devanado primario

Lpar Inductancia parsita

Ls Inductancia del devanado secundario

MLT Largo promedio del devado

n Relacin de transformacin

Np Nmero de vueltas en el devanado primario

Ns Nmero de vueltas en el devanado secundario

Nr Nmero de vueltas en el devanado de restablecimiento

Po Potencia de salida

Pp Prdidas en el cobre primario

Ps Prdidas en el cobre secundario

Pt Potencia aparente

Q1,2,3,4 Transistor o interruptor

QE Interruptor de emisor

QG Interruptor de compuerta

R2,... Resistencia

RG(on) Resistencia de compuerta en el encendido

RG (off) Resistencia de compuerta en el apagado

Rind Resistencia de la inductancia

RL Resistencia de carga

Rp Resistencia del devanado primario

Rpar Resistencia parsita

Rs Resistencia del devanado secundario

Rt Resistencia de oscilacin

T Periodo

t Tiempo

T1, T2 Tirirstor

td Tiempo de retardo

tf Tempo de bajada

toff Tiempo de apagado

ton Tiempo de encendido

tr Tiempo de subida

Tr1, Tr2 Transistores

ts Tiempo de propagacin o almacenamiento

tt Tiempo de la cola de apagado

V0 Voltaje de alimentacin

V1 Voltaje en el primario del transformador

V2 Voltaje en el secundario del transformador

VAK Voltaje nodo-ctodo

vCE Voltaje colector-emisor

iv

VCE(sat) Voltaje colector-emisor de saturacin

Vd Voltaje de cada del diodo

Vin Voltaje de la fuente de alimentacin o de entrada

vL Voltaje de salida o en la carga

VLcarga Voltaje en la inductancia de carga

Vo Voltaje de salida

Voc Voltaje en circuito abierto

Vp Voltaje en el primario del transformador

VS Voltaje en el secundario del trasnformador

VTR Voltaje en el transformador

Wtef Peso del ncleo

NOMENCLATURA

AUX Auxiliar

BJT Transistor bipolar

BM Behavioral modelig

CA Corriente alterna

CD Corriente directa

DAGTO Tiristor de apagado por compuerta asistido por un diodo

DSEP Dispositivos semiconductores de potencia controlados

DUT Dispositivo bajo prueba

ETO Tiristor apagado por emisor

FS Field-Stop

GTO Tiristor de apagado por compuerta

IGBT Transistor bipolar de compuerta aislada

IGCT Tiristor con compuerta conmutada integrada

JFET Transistor de efecto de campo unin

MCT Tiristor controlado por MOS

MOS Metal xido semiconductor

MOSFET Transistor de efecto de campo metal xido semiconductor

MTO Tiristor de apagado por MOS

MVA Mega volts amperes

NPT Non Punch-Through

PSpice Programa de simulacin de circuitos elctricos y electrnicos

PT Punch-Through

PWM Modulador de ancho de pulso

SIT Transistor de induccin esttico

SOA rea de operacin segura

SPT Soft-Punch-Through

ZCS Conmutacin a corriente cero

ZVS Conmutacin a voltaje cero

v

vi

Captulo 1

Planteamiento del problema y justificacin

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

En este captulo se presentan en forma general los problemas a los que se enfrenta el

diseador de circuitos al seleccionar el dispositivo adecuado para la aplicacin deseada. Las

diversas aplicaciones implican requerimientos energticos particulares que demandan

ciertas caractersticas a los dispositivos. As, uno de los problemas a los que se enfrenta el

diseador, es poder seleccionar el dispositivo semiconductor de potencia que presente las

caractersticas mas adecuadas a la aplicacin, por lo cual es importante conocer bien las

caractersticas con las que cuentan los dispositivos. Este estudio inicia con una introduccin

sobre la electrnica de potencia en general.

La electrnica de potencia es una rama de la ingeniera elctrica que combina la

energa elctrica, la electrnica y el control. El control se encarga del rgimen permanente y

de las caractersticas dinmicas de los sistemas de lazo cerrado. La energa elctrica tiene

que ver con el equipo de potencia esttico y rotativo o giratorio, para la generacin,

transmisin y distribucin de la misma. La electrnica se ocupa de los dispositivos y

circuitos semiconductores requeridos en el procesamiento de seales para cumplir con los

objetivos de control deseados. La electrnica de potencia se puede definir como la

aplicacin de la electrnica de estado slido para el control y la conversin de la energa

elctrica. Algunas de sus aplicaciones son: control de calor, control de la intensidad

luminosa, controles de motor, reguladores CA y CD, calentamiento por induccin,

compensadores de VAR estticos, filtros activos y muchos ms.

El elemento base de un sistema electrnico de potencia es el dispositivo que se

utiliza para realizar la funcin de interrupcin. Hoy en da la electrnica de potencia

aprovecha los avances de la tecnologa como son: fabricacin de circuitos integrados y

dispositivos semiconductores de potencia, que trabajan bajo la supervisin de un control

electrnico. La tendencia es producir mdulos inteligentes, donde el control, la proteccin y

la etapa de potencia sean integrados en un mismo encapsulado.

1.1 Dispositivos Semiconductores de Potencia Controlados (DSEP)

La motivacin de usar dispositivos de conmutacin en un convertidor es la de

incrementar la eficiencia de la conversin, ya que dichos dispositivos se operan solo en los

estados de encendido o apagado. Un dispositivo semiconductor de potencial ideal

presentara las siguientes caractersticas:

facilidad de comando

resistencia de encendido nula

tiempos de conmutacin nulos

densidad de corriente ilimitada

tensin de bloqueo ilimitada

corriente de fuga nula

Tal dispositivo no tendra prdidas de conmutacin, de conduccin, ni de control,

por lo tanto la eficiencia del convertidor tendera a ser del 100%. Sin embargo, los

componentes reales presentan prdidas que reducen la eficiencia de los convertidores y, por

2

Planteamiento del problema y justificacin

lo tanto, se hace necesario conocer las caractersticas de estos dispositivos para lograr su

ptima utilizacin en las diferentes condiciones de operacin [1].

1.1.1 Caractersticas de los dispositivos semiconductores de potencia

Considerando un interruptor ideal, las caractersticas requeridas de los dispositivos

semiconductores de potencia controlados se pueden resumir de la siguiente manera:

alta capacidad de bloqueo, baja corriente de fuga bajas prdidas por bloqueo

manejar alta densidad de corriente bajas prdidas por conduccin

tiempos cortos de conmutacin bajas prdidas por conmutacin

facilidad de control (control por tensin)

no necesita circuitos adicionales como snubbers insensibilidad al di/dt y dv/dt

robustez en corto circuito y estabilidad trmica

inteligencia y confiabilidad

bajos costos

Es obvio que un solo dispositivo no puede satisfacer con todos los requerimientos

de igual manera, por lo que se han desarrollado semiconductores de potencia, cuya

caracterstica se adaptan a los diferentes tipos de aplicacin.

Los requerimientos de los componentes que actan como interruptores en

convertidores electrnicos se confrontan con las leyes fsicas que impiden su realizacin en

un solo componente, por lo que se hace necesario una optimizacin del semiconductor con

respecto a su aplicacin. Sin embargo, todos los dispositivos de potencia tienen una

propiedad en comn que los distingue de los dems componentes electrnicos: disponen en

su estructura de una capa gruesa y con un dopado muy bajo para poder soportar las altas

tensiones de bloqueo. Adicionalmente, todos los semiconductores de potencia tienen una

estructura vertical, que permite un mejor aprovechamiento de la superficie y una mejor

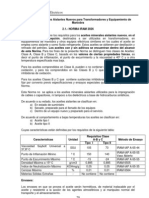

distribucin de la corriente. En la Figura 1.1 se presenta la estructura de los dispositivos de

potencia ms relevantes. Resaltan sus propiedades comunes y sus diferencias. Las

estructuras fundamentales de dispositivos de potencia son: la estructura diodo, la estructura

tiristor, la estructura transistor y la estructura MOS.

Hoy en da, al diseador de convertidores se le ofrece una amplia gama de

componentes modernos a diferentes niveles de tensin, de corriente, as como de frecuencia

de operacin. Los dispositivos ms utilizados son: el MOSFET (Metal Oxide

Semiconductor Field Effect Transistor) (tecnologa unipolar, frecuencias altas, potencias

bajas), el IGBT (Insulated Gate Bipolar Transistor) (tecnologa hbrida, frecuencias y

potencias medianas) y el GTO (tecnologa bipolar, frecuencias bajas, potencias altas).

3

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

Figura 1.1Estructura de los dispositivos de potencia ms relevantes.

1.1.2 Comparacin entre los diferentes dispositivos

Segn el mecanismo de transporte de corriente, los dispositivos de potencia se

clasifican en componentes unipolares (MOSFET, SIT) y componentes bipolares (diodo,

tiristor, GTO y transistor bipolar).

Los dispositivos bipolares realmente presentan el grupo ms amplio en la

electrnica de potencia. Su buen comportamiento en conduccin se debe a la inyeccin de

portadores en la zona n- a causa de una o dos uniones pn polarizadas directamente. En el

transporte de corriente participan tanto electrones como huecos. Por otro lado, las buenas

caractersticas en conduccin contradicen los requerimientos de una rpida conmutacin

debido a la inyeccin de portadores minoritarios (cargas almacenadas).

En los dispositivos unipolares, en cambio, participan nicamente portadores

mayoritarios en el transporte de corriente y no se modula la conductividad de la zona n-,

por lo que su resistencia est determinada solamente por su conductividad intrnseca. De

esta manera no se pueden combinar altas tensiones de bloqueo con alta capacidad de

corriente. Las ventajas de los MOSFETs consisten en un buen comportamiento dinmico

(no hay cargas almacenadas por ser dispositivos unipolares) y en su control simple y

prcticamente sin prdidas (control de campo estructura MOS) que presenta una estabilidad

trmica del dispositivo. El MOSFET aprovecha la tecnologa de alta integracin de la

microelectrnica (MOSFET de baja potencia).

Entre los nuevos semiconductores de potencia que han salido al mercado, algunos

combinan las ventajas de las dos tecnologas, bipolar y unipolar, en un solo componente

hbrido, como es el caso del IGBT.

La Figura 1.2 muestra una comparacin de los diferentes dispositivos de potencia

controlados con respecto a la potencia y la frecuencia de conmutacin. En la Figura 1.2

podemos destacar al GTO por su elevada capacidad de conmutacin, el cual es un tiristor

auto desactivado por compuerta. Este dispositivo resulta muy atractivo para la conmutacin

4

Planteamiento del problema y justificacin

forzada de convertidores y est disponible hasta 4000V y 3000A, para frecuencias de

conmutacin hasta 1kHz. El MCT (tiristor controlado por MOS) se puede activar mediante

un pequeo pulso de voltaje negativo sobre la compuerta MOS (respecto a su nodo), y

desactivar mediante un pulso pequeo de voltaje positivo. Es similar a un GTO, excepto en

que la ganancia de desactivacin es muy alta. Los MCT estn disponibles hasta 1000V,

100A y para frecuencias de hasta 20kHz. Los transistores bipolares de alta potencia son

comunes en los convertidores de energa a frecuencias menores de 10 kHz y su aplicacin

es eficaz en potencias hasta 1200V/ 400A.

Los MOSFET de potencia se utilizan en convertidores de potencia de alta velocidad

y estn disponibles en una especificacin de poca potencia en un rango de 1000V/ 50A y

hasta frecuencias de conmutacin de decenas de kilohertz. Los IGBT son transistores de

potencia controlados por voltaje. Por naturaleza son ms rpidos que los BJT, pero an no

tan rpidos como los MOSFET. Los IGBT son adecuados para altos voltajes, altas

corrientes y frecuencias de hasta 20kHz en conmutacin dura. Los IGBT estn disponibles

como mdulos hasta 4500V/1000A. El SIT (transistor de induccin esttico) es un

dispositivo de alta potencia y de alta frecuencia. Las especificaciones de uso de corriente de

los SIT puede ser hasta 1200V, 300A y la velocidad de interrupcin puede ser tan alta

como 100 kHz [2].

En los ltimos aos, algunos trabajos han sido orientados a mejorar las

caractersticas de apagado de los dispositivos GTO, esto basado en la condicin de

ganancia unitaria durante el apagado. Dentro de estos trabajos de investigacin podemos

destacar al MTO (Higt Power Bipolar MOS Thyristor), el IGTC (Integrated Gate-

Conmutated Thyristor), el ETO (Emitter Turn-off Thyristor) y el DAGTO (Diode Assisted

Gate Turn-off Thyristor) [3], [4], [5] y [6].

Figura 1.2Aplicaciones de los dispositivos de potencia controlados

5

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

1.2 El tiristor de apagado por compuerta (GTO)

Convertidores de alta potencia han sido altamente usados en aplicaciones de

traccin, control y administracin de la energa, sistemas de almacenamiento magntico de

la energa y convertidores industriales. Hasta la fecha, los GTOs son los dispositivos

semiconductores controlados por compuerta mas ampliamente usados a altos voltajes (VBR

c 3300 V) y altas potencias (S c 0.5 MVA) en convertidores aplicados a traccin e

inversores industriales. Algunos fabricantes ofrecen en el mercado GTOs para potencias de

conmutacin por arriba de los 36 MVA (6000V, 6000A).

1.2.1 Estructura y funcionamiento

La estructura del GTO es esencialmente similar al tiristor convencional. Como se

muestra en la Figura 1.3a, esta consiste de 4 capas de silicio (pnpn), tres uniones y tres

terminales (nodo, ctodo y compuerta). El funcionamiento del GTO y el tiristor son

bsicamente iguales. La diferencia en operacin entre los dos es que una seal de

compuerta negativa puede apagar al GTO, mientras la corriente de nodo del tiristor tiene

que ser reducida a cero externamente para que cese la conduccin. Para crear esta

diferencia se realizaron modificaciones en el diseo que sacrifican la calidad de algunas

caractersticas del GTO tales como reducir la capacidad de bloqueo inverso e incrementan

las perdidas en conduccin. Debido a que su funcionamiento es casi igual al del tiristor,

excepto por el apagado, describiremos principalmente la operacin del apagado.

Cuando un GTO esta en el estado de encendido, la regin de la base central es

ocupada con huecos suministrados del nodo y electrones suministrados del ctodo. Si un

voltaje inverso es aplicado al hacer la compuerta negativa con respecto al ctodo, parte de

los huecos en la capa de la base p son extrados a travs de la compuerta, suprimiendo la

inyeccin de electrones del ctodo. En respuesta a esta supresin, ms corriente de hueco es

extrada a travs de la compuerta, fomentando la supresin de inyeccin de electrones. En

el curco de este proceso, la unin emisor-ctodo (J3) es puesta completamente en un estado

de polarizacin inversa, el GTO es apagado. La Figura 1.3 ilustra la operacin de apagado,

usando un modelo de dos transistores [7].

a) b)

Figura 1.3Modelo del GTO: a) Estructura del GTO, b) Circuito equivalente

6

Planteamiento del problema y justificacin

Suponiendo que un GTO es dividido en el transistor npn Tr1 en el lado del ctodo y

transistor pnp Tr2 en lado del nodo y estn conectados como se muestra en la Figura 1.3b.

En esta Figura, el factor de amplificacin de corriente del transistor Tr1 es llamado (1 y la

del transistor Tr2 y (2. Si una corriente inversa IGQ fluye a travs de la compuerta, la

corriente de base IB en el transistor Tr1 es reducida cuando IGQ es incrementado. Esta

relacin puede ser expresada por la siguiente ecuacin:

IB

=

(2

*

IA

-

IGQ (1.1)

En la otra mano, la corriente de electrones IRB, la cual desaparece debido a la

recombinacin en la capa de la base Tr1, puede expresarse como sigue:

IRB = (1 - (1) * IK

(1.2)

La relacin entre la corriente de nodo (IA) y la corriente de ctodo (IK) del GTO es

expresada por la siguiente ecuacin:

IA

=

IK

+

IGQ (1.3)

En el apagado del GTO, IB debe ser tan pequea como IRB. La magnitud de corriente

inversa IGQ que satisface esta condicin puede ser calculada por la siguiente ecuacin:

IGQ = ((1 + (2 1) * IA / (1

(1.4)

A) Proceso de encendido

En general el proceso transitorio de encendido del GTO es muy similar al de los

tiristores convencionales conocidos y se muestra en la Figura 1.4. Este proceso presenta

tres intervalos:

El tiempo de retardo (td), el cual es el tiempo transcurrido del comienzo del pulso

de la corriente de compuerta hasta que la corriente de nodo alcanza 10% del valor

final de IA.

El tiempo de subida (tr), el cul es el tiempo entre el 10% y el 90% de IA.

El tiempo de propagacin (ts), el cual est definido a partir del 10% de la tensin Vs

y representa el tiempo durante el cual la corriente se propaga lateralmente hasta la

terminal del ctodo.

B) Proceso de apagado

Este tambin es dividido en tres intervalos:

El tiempo de almacenamiento (ts), durante el cual el exceso de portadores de la base

p es extrado va la corriente de compuerta y todas las uniones (J1,J2 y J3) son

polarizadas. En el periodo final de almacenamiento, la corriente de nodo cae a un

valor de 90% IA y la regin de carga espacial empieza a crecer alrededor de J2.

7

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

El tiempo de bajada (tf) es el tiempo transcurrido del 90% al 10% de IA. Durante

este tiempo el voltaje sobreincrementa el dispositivo y los portadores minoritarios

son desalojados de la base n a la p. Al final de este periodo la unin J3 empieza a

bloquear.

El tercer periodo es una cola (tt) durante la cual la corriente a travs del dispositivo

va del 10% a cerca de cero.

1.2.2 Caractersticas

El GTO tiene varias ventajas, las cuales son [8], [9], [10] , [11]:

A) altas densidades de corriente en conduccin

B) altos voltajes de bloqueo

C) alta capacidad de resistencia a fuertes dv/dt en estado de bloqueo

D) posibilidad de integrar un diodo inverso

Figura 1.4Curvas de encendido y apagado del GTO.

Superior: corriente de nodo y voltaje nodo-ctodo, inferior: corriente de compuerta [7].

8

Planteamiento del problema y justificacin

Como desventajas se pueden resumir las siguientes:

A) Durante el transitorio de apagado, la estructura de 4 capas p-n-p-n (Figura 1.3)

causa una distribucin de corriente no homognea limitando el apagado a dv/dt

entre 500-1000V/us, lo cual requiere de circuitos de ayuda a la conmutacin

(snubbers) grandes y costosos.

B) Durante el transitorio de encendido, la estructura a 4 capas causa un problema

de crecimiento de corriente no controlada, lo que requiere de un circuito

limitador di/dt.

C) Ya que el GTO es un dispositivo controlado por corriente, su impulsor de

compuerta es complejo y disipa cientos de watts en una aplicacin tpica. El

complicado impulsor del GTO tiene como consecuencias un tiempo de

almacenamiento largo y una ganancia de apagado entre 3-5.

1.2.3 Mejoras realizadas

Actualmente, se han realizado varias mejoras a este dispositivo, haciendo un

esfuerzo por mejorar sus caractersticas dinmicas, ya que hasta el momento no han podido

ser desplazados en aplicaciones de conversin de muy alta potencia. Las mejoras realizadas

se describen a continuacin y se muestran en la Figura 1.5.

a) IGCT

El IGCT (tiristor con compuerta conmutada integrada) usa una fuente de voltaje y

un interruptor de compuerta para disminuir drsticamente la inductancia parsita del lazo de

compuerta, alcanzando as una corriente alta de conmutacin [4], [5].

La diferencia fundamental entre un GTO convencional y el nuevo IGCT es que

tiene una muy baja inductancia en la compuerta integrada y la nueva estructura de nodo

trasparente (unin pn con baja eficiencia de emisor a travs de una capa emisor muy

delgada y de dopado bajo). Lo anterior tiene como consecuencia bajas prdidas en la

tecnologa tiristor y la necesidad de menos snubbers. Para alcanzar las caractersticas

deseadas se obtuvieron los siguientes desarrollos:

Mejorar las caractersticas de conmutacin del GTO para obtener una operacin sin

amortiguamiento de dv/dt para altas densidades de corriente.

Reducir las prdidas en los estados de encendido y apagado para minimizar el

grosor del silicio

Reducir los requerimientos del impulsor de compuerta especialmente durante la

conduccin.

Desarrollar diodos antiparalelo para reducir los snubber en el apagado para altos

di/dt

Integrar el interruptor principal GTO y el diodo en un empaque semiconductor,

especialmente en baja potencia.

9

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

Figura 1.5 Circuitos equivalentes de los dispositivos derivados del GTO: a) IGCT b) MTO

c) ETO d) DAGTO

b) MTO

El MTO (tiristor apagado por MOS) usa solo un interruptor de compuerta QG.

Durante el apagado, el interruptor de compuerta es encendido, desviando la

corriente a travs del diodo compuerta-ctodo del GTO y realizando un apagado con

ganancia unitaria [3], [12].

El MTO es un dispositivo de conmutacin basado en el GTO. El GTO requiere una

realizacin compleja de circuitos de potencia que implican diseos cuidadosos de circuitos

impulsores y snubbers. Las mejoras realizadas al MTO son las siguientes:

Mayor velocidad de conmutacin y menores prdidas que el GTO.

Capacidad de corriente de algunos cientos de amperes, fuente de algunos miles de

amperes, capacidad de bloqueo de 6 KV.

Voltaje de saturacin en estado estable 4 V, la eficiencia en operacin de

convertidores de potencia es mejor que la eficiencia empleando IGBTs.

Tiempo de retardo similar al GTO, el tiempo de almacenamiento en el apagado es

mas bajo que el GTO. El tiempo de cada de la corriente en el apagado es de 5 s.

El comportamiento de conmutacin en el encendido es limitado por el di/dt. En el

apagado en conmutacin dura las prdidas son similares al GTO.

La utilizacin de menos snubbers en el apagado del dispositivo es limitado por la

corriente critica, por que la velocidad de subida de la corriente en el impulsor en el

apagado no es suficientemente rpida para mantener la ganancia unitaria en la

operacin de apagado.

c) ETO

El ETO (tiristor apagado por emisor) es otro tipo de tecnologa basada en

dispositivos semiconductores superiores de alta potencia, en este caso en la tecnologa

desarrollada del GTO y del MOSFET de potencia. El tiristor de pagado por emisor es un

10

Planteamiento del problema y justificacin

dispositivo semiconductor hbrido que apaga al GTO por debajo de las condiciones de

ganancia unitaria. El ETO combina las ventajas del GTO y del IGBT: del GTO rangos de

corrientes y voltajes grandes y voltajes pequeos de saturacin, del IGBT control por

voltaje, gran velocidad de conmutacin y un ancho RBSOA (rea de operacin segura

polarizada inversamente) [13].

El ETO hace uso de dos interruptores para realizar una conmutacin de corriente

alta en el apagado. Durante el apagado, el interruptor de emisor QE es apagado mientras que

la compuerta del interruptor QG es encendida. Un voltaje tan alto como el voltaje de ruptura

de QE puede ser aplicado en el lazo de la compuerta de la inductancia parsita, realizando

una conmutacin de corriente rpida. Durante el transitorio de encendido, QE es encendido

y QG es apagado [14], [15].

Un gran pulso de corriente es inyectado en la compuerta del GTO para reducir el

tiempo de retardo de encendido y mejorar el rango di/dt de encendido.

El proceso de apagado es controlado por voltaje y el impulsor de compuerta del

ETO es muy compacto y disipa menos potencia.

d) DAGTO

El DAGTO (tiristor de apagado por compuerta asistido por un diodo) es una nueva

configuracin que ayuda al GTO a alcanzar una ganancia unitaria al apagado y la capacidad

de necesitar menos snubbers al apagado utilizando diodos discretos conectados en serie. El

DAGTO incrementa significativamente el voltaje de apagado el cual puede ser usado para

la conmutacin de la corriente [11].

El DAGTO puede realizar conmutaciones de corrientes muy grandes en el apagado

por el uso del diodo DE. La ganancia de apagado unitaria se logra rpidamente y puede ser

mantenida hasta el final del proceso transitorio de apagado.

1.3 El transistor bipolar de compuerta aislada (IGBT)

Tal como se muestra en la Figura 1.7, el IGBT combina en un solo dispositivo la

tecnologa bipolar (el componente utilizado es el transistor bipolar pnp) y la tecnologa

unipolar (el componente empleado es el MOSFET de canal n). El objetivo de los

fabricantes era obtener un dispositivo que aprovechara las ventajas de cada uno de los

componentes mencionados: alta capacidad de corriente, cada de tensin directa (voltaje

colector-emisor de saturacin) muy baja debido a la modulacin de la zona n

-

que

proporciona la tecnologa bipolar y bajas prdidas por conmutacin as como la facilidad de

comando gracias a la compuerta aislada que ofrece la tecnologa MOSFET, tratando de

mantener las mejores caractersticas dinmicas [1], [9].

Los transistores IGBT han ganado un firme lugar en el diseo de equipos

electrnicos de potencia y han desplazado a los transistores bipolares en aplicaciones de

mediana potencia. Los sistemas en los cuales los IGBT son empleados tienen las

11

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

caractersticas de alta densidad de potencia, alta eficiencia y buenas caractersticas

dinmicas de conmutacin. Algunas de las principales reas de aplicacin de este

interruptor son:

fuentes conmutadas de potencias mayores a 1kW

accionamiento de motores

fuentes de alimentacin ininterrumpibles

balastros electrnicos

calentamiento por induccin

vehculos elctricos

Las ventajas esenciales de los transistores IGBT son: una rea de operacin segura

(SOA por sus siglas en ingls) casi cuadrada y comandado en tensin. Los inconvenientes

principales residen en la dependencia de la temperatura y la cola de corriente al apagado.

La tecnologa del IGBT no cesa de progresar, permitiendo la fabricacin de

dispositivos a potencias cada vez ms altas. La frecuencia de conmutacin del IGBT est

limitada hasta aproximadamente 20kHz debido a su inherente cola de apagado y puede ser

aumentada hasta 100khz o ms, utilizando topologas de convertidores que permiten

conmutacin suave (a voltaje cero o ZVS y a corriente cero o ZCS). Aunque se han hecho

muchos intentos de componentes hbridos todava no se vislumbra el sucesor del IGBT por

lo que contina siendo el dispositivo semiconductor de potencia ptimo en aplicaciones en

mediana potencia.

a) b)

Figura 1.6 Modelo del IGBT: a) Estructura interna del IGBT, b) Diagrama equivalente

12

Planteamiento del problema y justificacin

1.3.1 Estructura y funcionamiento

El transistor IGBT se desarroll a finales de los 80 a partir del transistor MOSFET

de estructura vertical, al cual se le agreg una unin pn del lado del drenaje. Esta unin

suplementaria realiza una estructura transistor pnp y permite beneficiarse en la conduccin

por portadores minoritarios (transporte bipolar). La Figura 1.6a muestra la estructura

interna de este dispositivo y la Figura 1.6b el circuito equivalente de la estructura del

transistor IGBT. Se puede observar que por la sucesin de 3 uniones pn la estructura del

IGBT contiene un tiristor parsito (formado por T1 y T2) cuyo encendido (mediante la

tensin que se origina por la corriente que circula por Rp) es indeseable (efecto lach-up) ya

que se llevara a la prdida del control por la compuerta. Los nuevos diseos de IGBT han

logrado eliminar este efecto (a partir de la segunda generacin).

El estado de conduccin es obtenido de manera similar al de un MOSFET de canal

n por la polarizacin positiva de la compuerta. La corriente del MOSFET alimenta la base

del transistor bipolar pnp y permite la inyeccin de cargas minoritarias en la zona n

-

a

travs de la unin pn polarizada en directa. En consecuencia, la cada de tensin en

conduccin esta constituida por tres componentes: la del canal MOS, una parte resistiva de

la base n

-

cuyo valor es modulado por alta inyeccin de cargas y por la cada de potencial

de la unin p

+

n

-

suplementaria. La resistencia en conduccin de un IGBT es de valor

pequeo, comparativamente a la de un MOS equivalente y favorece el paralelado gracias a

su coeficiente de temperatura positivo.

1.3.2 Caractersticas

El objetivo de los fabricantes al disear el IGBT era obtener un dispositivo que

aprovechara las ventajas del transistor bipolar y del MOSFET : alta capacidad de corriente,

cada de tensin directa (voltaje colector-emisor de saturacin) muy baja debida a la

modulacin de la zona n

-

que proporciona la tecnologa bipolar y bajas prdidas por

conmutacin, as como la facilidad de comando gracias a la compuerta aislada que ofrece la

tecnologa MOSFET, tratando de mantener las mejores caractersticas dinmicas. Las

ventajas esenciales de los transistores IGBT son: un rea de operacin segura (SOA por sus

siglas en ingles) casi cuadrada y comandado en tensin [16], [17].

El IGBT combina en un solo dispositivo la tecnologa bipolar (el componente

utilizado es el transistor bipolar pnp) y la tecnologa MOS (el componente utilizado es el

MOSFET de canal n). Este dispositivo aprovecha las caractersticas de ambas tecnologas,

las cuales son: alta capacidad de corriente, voltaje de saturacin bajo, bajas perdidas por

conmutacin, control por tensin. En la Figura 1.6a se muestra la estructura del IGBT.

Ventajas:

a) densidad de corriente mayor que un MOSFET

b) alta eficiencia

c) caractersticas dinmicas superiores a un BJT

d) rea de operacin segura

13

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

e) comando en tensin

Desventajas:

a) comportamiento dependiente de la temperatura

b) cola de corriente en el apagado (prdidas por conmutacin mayores a un

MOSFET)

c) prdidas en conduccin superiores a un GTO

1.3.3 Tecnologas de fabricacin del IGBT

El IGBT se fabrica actualmente en dos tecnologas bsicas, conocidas como la

tecnologa PT y la tecnologa NPT.

El IGBT ms comn es de tipo PT (Punch-Through). En esta tecnologa de

fabricacin, el dispositivo es construido en un substrato grueso tipo p

+

(300 m). El ancho

de la capa n

-

(base del BJT) construida mediante crecimiento epitaxial es relativamente

pequea. En la Figura 1.7 se puede apreciar que aparte se tiene una capa delgada n

+

entre la

base y el emisor llamada buffer que limita la expansin de la regin de carga de espacio en

estado de bloqueo (efecto Punch-Through). El IGBT de tipo PT alcanza bajas prdidas por

conduccin (resistencia baja) a travs de un coeficiente de emisor alto del BJT interno y

bajas prdidas por conmutacin por medio de un tiempo de vida de los portadores muy

reducido. Esto resulta en un transitorio de corriente en el apagado en forma de cola de gran

amplitud que decrece rpidamente y depende en gran medida de la temperatura.

Existe tambin comercialmente el IGBT de tecnologa NPT (Non Punch-Through)

que es una estructura desarrollada originalmente por la compaa Siemens. Estos

dispositivos son construidos en un substrato homogneo de tipo n

-

de aproximadamente

220 m de ancho. El emisor se realiza a travs de implantacin de una capa p

+

muy delgada

y de dopado bajo (emisor transparente) en la parte posterior del substrato (Figura 1.9). Por

lo tanto, en el IGBT homogneo se realiza la modulacin de la resistencia de base a travs

de un bajo coeficiente de emisor en combinacin con un tiempo de vida de portadores muy

alto. Aparte se tienen bajas prdidas por conmutacin a travs de la recombinacin de

superficie en el emisor transparente. Estas caractersticas conllevan a un transitorio de

corriente en el apagado en forma de cola de una amplitud reducida pero que decae

lentamente y es casi invariable con la temperatura.

La tecnologa NPT es ms robusta y la ms apropiada para dispositivos de alta

tensin de bloqueo, mientras que la tecnologa PT tiene ventajas en aplicaciones con

conmutacin suave. Sin embargo, ambas tecnologas tienen tambin desventajas, que se

han tratado de superar uniendo en una nueva estructura las ventajas del PT y NPT-IGBT

con el fin de reducir por un lado las prdidas por conduccin (reduciendo el VCE) y por otro

lado las prdidas en conmutacin (reduciendo la cola de apagado). Esta estructura, que ha

sido presentada apenas recientemente, se llama Soft-Punch-Through (SPT-IGBT) o tambin

Field-Stop (FS-IGBT) dependiendo del fabricante. La estructura SPT es muy similar a la

NPT, solo con la diferencia de que se logr reducir aun mas su grosor (reduccin de la capa

14

Planteamiento del problema y justificacin

n

-

) a travs de la implementacin de la zona buffer n

+

tpica para la tecnologa PT. Dadas

las distintas estructuras de estas tecnologas, los IGBT de tipo PT, NPT y SPT tienen

tambin caractersticas elctricas diferentes. La Figura 1.7 muestra las estructuras

tradicionales PT y NPT, as como la nueva estructura SPT.

La tecnologa SPT permite la construccin de convertidores con un mayor rango de

potencia, fijando el estndar de voltaje en 1200 V. Estos dispositivos vienen empaquetados

en mdulos y sus caractersticas son: mayor robustez, permite la conexin en paralelo de

los mdulos, transiciones suaves en la conmutacin del dispositivo, bajo incremento de la

resistencia del modulo ante variaciones de temperatura y requerimientos de impulsores

igual que la tecnologa NPT.

ltimamente, se han aplicado para todas las tecnologas una nueva estructura de

compuerta llamada trench-gate a diferencia de la estructura convencional de compuerta

plana. Esta estructura permite reducir las prdidas en conduccin, puesto que el canal del

MOSFET se forma en direccin vertical a la superficie del chip y requiere menos rea

activa. De esta manera se aumenta la densidad de las celdas. Resumiendo, los beneficios

obtenidos con la estructura trench-gate incluyen una disminucin de la resistencia del canal

MOS y la eliminacin de la regin JFET.

Por otro lado, las aplicaciones en las cuales los IGBT han sido tpicamente

empleados son de baja y mediana potencia. Sin embargo, debido a las recientes

aportaciones tecnolgicas, actualmente existen IGBTs de alta potencia que compiten a los

GTOs, los cuales han sido tpicamente usados en aplicaciones de alta potencia. Por lo

anterior es que en este trabajo de tesis se ha propuesto el desarrollo de un banco de pruebas

para caracterizar dispositivos de alta potencia.

Figura 1.7Estructura del IGBT tipo PT, NPT y SPT

15

Punch Through (PT) Non - Punch Through (PT) Soft Punch Through (SPT)

Estructura

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

1.4 Modos de conmutacin

Los diferentes modos de conmutacin a los que se puede someter un dispositivo

semiconductor de potencia controlado y los cuales se pueden presentar en una aplicacin se

resumen de la siguiente manera:

Conmutacin dura

Presencia simultnea de corriente y voltaje en el lapso de tiempo que dura la fase

de conmutacin. Se puede presentar tanto en el encendido como en el apagado del

dispositivo.

Conmutacin suave natural

Ocurre cuando el voltaje o la corriente es cero al encender o al apagar el

dispositivo y por lo tanto se clasifica en:

ZVS (conmutacin a voltaje cero) La condicin para este tipo de conmutacin

se obtiene cuando el voltaje cae hasta cero y tiempo despus evoluciona la

corriente con una pendiente determinada. La conmutacin natural ZVS solo se

presenta en la fase de encendido.

ZCS (conmutacin a corriente cero) La condicin para esta conmutacin se

obtiene cuando la corriente decrece hasta cero y tiempo despus se aplica el

voltaje de bloqueo. La conmutacin natural ZCS solo se presenta en la fase de

apagado.

Corto circuito

Este tipo de conmutacin no es deseable en un convertidor, se tienen dos tipos de

cortocircuito:

Tipo I Se tiene presente un corto en la carga mientras el dispositivo es

encendido.

Tipo II Se tiene el dispositivo en estado de conduccin (manejando una cierta

cantidad de corriente) cuando se presenta un corto en la carga.

En la Figura 1.10 se muestra una comparacin entre los diferentes modos de

conmutacin que puede presentar un interruptor controlado en una aplicacin.

En la Figura 1.11 muestra el rea de operacin segura de un componente y la

trayectoria en cada uno de los diferentes modos de conmutacin de un dispositivo

semiconductor.

16

Planteamiento del problema y justificacin

1.5 Justificacin

El estudio de los dispositivos semiconductores de alta potencia tiene varias

aportaciones originales para solucionar la problemtica abordada y la necesidad de

investigar sobre ellos tiene dos importantes aspectos.

Analizar a fondo el funcionamiento del dispositivo para poder conocer las

implicaciones al usar dispositivos de alta potencia y su proceso de conmutacin para

aprovechar al mximo sus caractersticas en las diferentes aplicaciones de alta

potencia.

Obtener informacin del GTO que nos permita entender hacia donde estn siendo

orientadas las mejoras que se han realizado en estos dispositivos.

Suministrar informacin del comportamiento de los DSEPs de alta potencia a

fabricantes y diseadores.

Figura 1.8Diferentes tipos de conmutacin existentes en un convertidor

17

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

Figura 1.9rea de operacin segura y la trayectoria I = f (V) para cada tipo de conmutacin

1.6 Objetivos

a) Objetivo general

Disear e implementar un banco de pruebas que permita estudiar

experimentalmente el comportamiento de los dispositivos de alta potencia en diferentes

condiciones de conmutacin dura

b) Objetivos particulares

El principal objetivo de esta tesis es disear un banco de pruebas para caracterizar

dispositivos de alta potencia, por lo que se propone lo siguiente para lograrlo:

Simulacin de los circuitos propuestos con el programa PSpice para validar los

procedimientos del diseo.

Construccin del banco de pruebas (que incluye los impulsores de compuerta, los

sistemas de control y la fuente de CD)

Realizacin de algunas pruebas para comprobar el buen funcionamiento del banco

de pruebas.

18

Captulo 2

Metodologa abordada

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

En este captulo se presentan las caractersticas con las cuales deben contar las

fuentes de alto voltaje de CD y diversos tipos de fuentes de alto voltaje en CD con el fin de

presentar las ventajas y desventajas que ofrece cada una de ellas, as como el mtodo para

realizar la caracterizacin de dispositivos semiconductores en forma experimental. Se

presentan tambin los requerimientos mnimos necesarios para obtener buenos resultados

mediante simulacin.

2.1 Caracterizacin experimental

Para realizar la caracterizacin experimental, es necesario disear circuitos de

prueba con una topologa sencilla, poco costosa y con una buena reproduccin de las

condiciones reales que un dispositivo presenta en una aplicacin determinada. Las

caractersticas requeridas para los circuitos de prueba son las siguientes [1]:

nmero limitado de elementos de potencia y de las fuentes

calidad en la reproduccin de las condiciones de operacin en la aplicacin del

convertidor

independencia entre los diferentes parmetros que deben de estar controlados

En la caracterizacin experimental, el trabajo consiste en realizar las mediciones de

corrientes y voltajes en el dispositivo bajo diferentes condiciones de operacin

(conmutacin dura, conmutacin suave, avalancha, etc.) con la posibilidad de realizar

variacin de los parmetros mas importantes del circuito (temperatura, tensin de

alimentacin, corriente de conduccin, inductancia parsita, etc.)

2.1.1 Diseo general del circuito de pruebas

En el diseo del banco de pruebas se toman en cuenta aspectos importantes como:

mtodo de pruebas

modo de funcionamiento

tipo de control

La seleccin depender de la calidad de reproduccin de las condiciones que

presente una aplicacin convertidor dada de tal manera que se tenga independencia en el

control de los diferentes parmetros, una limitacin del nmero de elementos del circuito y

de la potencia instalada de la fuente de alimentacin. A continuacin se describen estos

aspectos.

2.1.1.1 Mtodo de prueba

El comportamiento de un dispositivo semiconductor de potencia (DSEP) puede ser

observado en dos situaciones diferentes, ya sea directamente en la aplicacin del

convertidor mediante la realizacin de circuitos especiales.

a) Circuitos de aplicacin a convertidores

20

Metodologa abordada

Cuando se evala directamente el desempeo del componente en un convertidor, se

presentan las interacciones entre el convertidor y la carga sobre el dispositivo. La

evaluacin bajo estas condiciones presenta las caractersticas siguientes:

Son las condiciones reales: elctricas, trmicas y mecnicas (entorno real del

componente).

La potencia instalada es elevada (funcin de la aplicacin).

Los parmetros accesibles son funcin del convertidor y la naturaleza de la carga.

Globalmente, se obtiene el caso real, pero muy dependiente de la aplicacin,

tenindose poca flexibilidad y grandes dificultades para obtener y sobreponer los

resultados.

b) Circuitos especiales

Cuando se disean circuitos especiales de prueba para el estudio y la caracterizacin

de DSEP, esto permite un mejor control de las condiciones de prueba y una buena

reproduccin de las condiciones tpicas de conmutacin. En el caso de la conmutacin dura

(PWM, modulacin de ancho de pulso) los circuitos especiales de prueba han sido

ampliamente usados.

Globalmente se tiene una mayor flexibilidad en la variacin de los parmetros

externos del circuito, pero no es la aplicacin real del componente a evaluar. Algunas de las

ventajas que ofrece el usar circuitos especiales de prueba son:

Hay poca demanda de potencia, lo que permite realizar pruebas a elevadas

corrientes, sin riesgo de destruccin del dispositivo.

El dispositivo no es demandado trmicamente, ya que se considera la

temperatura de unin igual a la de encapsulado.

No hay interdependencia entre parmetros, lo que facilita el estudio del

comportamiento.

Pero tambin tiene algunas desventajas, entre las cuales son:

El aspecto trmico es abordado solo en estado estable

Se requiere de un equipo de medicin de gran memoria y alta velocidad de

adquisicin

2.1.1.2 Modo de funcionamiento

Circuitos de prueba han sido realizados con el fin de analizar el fenmeno de

conmutacin de un interruptor. Este puede ser un convertidor particular que ofrece las

condiciones correspondientes al componente a estudiar. Para lograr esto se le aaden

componentes auxiliares tales como condensadores, inductores, fuentes e interruptores, los

cuales permiten definir la condicin de prueba. Un objetivo es la limitacin del nmero de

elementos y la energa instalada. La estructura adoptada podr funcionar ya sea de forma

repetitiva o en modo impulsional.

21

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

a) Modo repetitivo

Cuando el modo de funcionamiento es en modo repetitivo, el control es a frecuencia

fija con un ciclo de trabajo reducido con el fin de limitar el incremento de temperatura del

componente.

Este modo de funcionamiento tiene la ventaja de ser una evaluacin muy cercana a

la realidad respecto al cableado y los aspectos trmicos, pero no es adecuado para analizar

la conmutacin propia del componente. La repeticin de ciclos permite establecer mtodos

de medicin por acumulacin y efectuar correcciones de ruido sncronos. Sin embargo esta

estrategia presenta los siguientes problemas:

Potencia instalada igual a las prdidas del componente, lo que requiere un sistema

de enfriamiento y cableado necesariamente grandes.

Interdependencia de parmetros: frecuencia, ciclo de trabajo, temperatura, etc.

b) Modo impulsional

El funcionamiento en modo impulsional es una estrategia de pruebas donde se trata

de una experimentacin en valores reales de corriente, tensin y temperatura. Adems, el

componente es sometido una sola vez a las condiciones de conmutacin lo que, como ya se

mencion, permite una limitacin en nmero de componentes y de la potencia instalada de

la fuente y por otro lado mayor compactacin de los componentes, a fin de reducir el

cableado.

2.1.1.3 Tipo de control

Para el control de la operacin de los dispositivos auxiliares, as como el disparo del

dispositivo bajo prueba, existen dos posibilidades: automtico o de tiempo preestablecido.

a) Control automtico

En este esquema de comando, el encendido y apagado de los dispositivos auxiliares

y bajo prueba se realizan automticamente a valores determinados de voltaje o corriente.

Este sistema de control permite condiciones de conmutacin que pueden ser ajustadas

independientemente de la carga. Es un sistema de control directo.

b) Tiempo preestablecido

En este tipo de comando se establecen los tiempos de encendido y de apagado de los

dispositivos. Este es un sistema de control en lazo abierto, donde los parmetros son solo

indirectamente incontrolados.

22

Metodologa abordada

2.1.2 Diseo propuesto para los circuitos de prueba

Los circuitos de prueba empleados en cada uno de los modos posibles de

conmutacin presentan las siguientes caractersticas:

modo de funcionamiento impulsional (one shot), que permite limitar la energa

solicitada a la red, lo que facilita hacer pruebas en casos extremos.

uso de un control de tiempo preestablecido capaz de asegurar por un lado su funcin

en los diferentes modos de conmutacin y por otro lado ser configurado para un tipo

de control dado en funcin de los parmetros propios del interruptor bajo prueba.

minimizacin del nmero de elementos auxiliares, de manera que los resultados

obtenidos slo se consideran que son debidos al efecto del dispositivo bajo prueba

(DUT) y no a elementos externos interdependientes que modifiquen el

comportamiento del dispositivo; esto se realiza con el fin de controlar mejor las

condiciones impuestas al dispositivo semiconductor en una aplicacin real.

El principio de diseo se plantea en la Figura 2.1, la cual considera las siguientes

partes:

el circuito bajo prueba, el cul es encargado de reproducir las condiciones de la

aplicacin

circuito auxiliar integrado por componentes pasivos e interruptores auxiliares que

debe permitir un ajuste independiente de los parmetros de las condiciones de

prueba.

En relacin a los circuitos de prueba para dispositivos de alta potencia se deben

tomar en consideracin algunos otros aspectos como son:

circuitos limitador de di/dt para controlar el crecimiento de la corriente entre el

circuito de potencia y el bus de CD (banco de condensadores)

circuitos sujetadores de voltaje para evitar sobretiros de voltaje

circuito de control para la carga y descarga de condensadores

carga y descarga del banco de condensadores de manera remota

Figura 2.1Principio de diseo de circuitos especiales de prueba

23

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

2.2 Caracterizacin mediante simulacin

La simulacin de circuitos electrnicos de potencia previa al diseo de prototipos se

ha convertido en una herramienta indispensable, puesto que el simulador (software)

proporciona la confiabilidad del correcto funcionamiento. Pero para poder simular

adecuadamente un circuito elctrico o electrnico en general, es necesario que se cumplan

los siguientes requerimientos [21]:

disponibilidad de un simulador de circuitos adecuado

disponibilidad de los modelos para todos los componentes del diseo

disponibilidad de los parmetros para todos los modelos de todos los componentes

a) Disponibilidad de un simulador adecuado

Se refiere a un simulador de redes elctricas o electrnicas que contenga modelos de

dispositivos electrnicos. Hoy en da existen muchos simuladores de circuitos elctricos y/o

electrnicos pero una gran parte de ellos son utilizados en las instituciones donde se

desarrollaron, es decir, no se encuentran disponibles a cualquier usuario. PSpice, que es una

derivacin de SPICE para la simulacin de circuitos electrnicos integrados, est siendo

utilizado a nivel internacional para realizar simulaciones de circuitos electrnicos de

potencia. PSpice tiene la ventaja de ofrecer una versin demo gratuita del paquete con

suficiente capacidad para analizar diseos de circuitos de potencia que no requieren de

tantos elementos como los circuitos integrados.

b) Disponibilidad de modelos para todos los componentes del diseo

Se refiere a que el simulador contenga los modelos de todos los dispositivos

utilizados en el diseo a simular. Aqu la desventaja de PSpice es que teniendo su origen en

la simulacin de circuitos integrados de baja potencia (microelectrnica) no contiene

modelos adecuados para dispositivos de potencia, con excepcin del IGBT, cuyo modelo

est disponible a partir de la versin 7.0.

De manera general los modelos se pueden clasificar segn la tcnica de desarrollo

en:

modelo de caja negra

modelo de circuito equivalente

modelo fsico

Por otra parte segn el modo de implementacin en el simulador, los modelos se

pueden clasificar en:

macromodelo de tipo BM (behavioral modeling)

macromodelo estructural

macromodelo en cdigo fuente

24

Metodologa abordada

c) Disponibilidad de los parmetros para los modelos de todos los componentes

utilizados

Se refiere a que el diseador disponga de los parmetros de los modelos para cada

componente del diseo. Hoy en da los simuladores suelen incluir extensas libreras de

modelos parmetrizados (modelos con parmetros de componentes reales) de diferentes

fabricantes, y con frecuencia los mismos fabricantes proporcionan estos modelos para sus

dispositivos en diferentes simuladores. Los parmetros de los modelos en el simulador son

los mismos para cada modelo; lo que hace diferente al dispositivo de otro fabricante o de

otras caracterstica es el valor numrico que contiene cada modelo en su respectivo

parmetro. En cambio, el nmero y clase de parmetros de un modelo dependen no slo del

dispositivo a simular, sino en gran medida del tipo de modelo utilizado para dicho

dispositivo.

Para realizar la caracterizacin mediante simulacin es necesario reproducir las

condiciones reales de funcionamiento de los circuitos de prueba, incluyendo los elementos

parsitos en el simulador. El trabajo consiste en realizar los clculos en simulacin de los

circuitos de prueba durante las conmutaciones bajo las mismas condiciones que en el caso

experimental.

2.3 Tipos de fuentes

Las fuentes de poder, que se utilizan en forma extensa en aplicaciones industriales, a

menudo requieren cumplir todas o la mayor parte de las especificaciones siguientes [2]:

1. Aislamiento entre fuente y carga

2. Una alta densidad de potencia a fin de reducir el tamao y el peso

3. Direccin controlada del flujo de la potencia

4. Alta eficiencia de conversin

5. Formas de onda de entrada y de salida con baja distorsin armnica total

6. Factor de potencia controlado si la alimentacin a la fuente es un voltaje de CA

Los reguladores en modo de conmutacin sin transformador no pueden dar el

aislamiento necesario y la potencia de salida es baja. La practica comn es utilizar

conversiones en dos pasos, CD-CA y CA-CD. En caso de entrada de CA, se trata de

conversiones en tres pasos, CA-CD, CD-CA y CA-CD. El aislamiento se consigue

mediante un transformador entre los pasos. La conversin CD-CA se puede llevar a cabo

mediante un inversor PWM o resonante.

Para la etapa del inversor (o del convertidor CD-CA) de la operacin PWM, existen

cuatro configuraciones comunes: flyback, push-pull o en contrafase, medio puente y puente

completo. La salida del inversor, que vara mediante una tcnica PWM, es convertida a un

voltaje de CD mediante un rectificador de diodos. A continuacin se describe el

funcionamiento de algunas fuentes de CD de alto voltaje [18].

25

Voc = Vin 1 +

N p |

Nr |.

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

2.3.1 Flyback

La topologa del circuito para el convertidor flyback se muestra en la Figura 2.2.

Cuando el transistor Q1 se activa, el voltaje de alimentacin aparece a travs del primario

del transformador y se induce un voltaje correspondiente en el secundario. Cuando Q1 esta

apagado, se induce un voltaje de polaridad opuesta en el primario por el secundario, debido

a la accin de transformacin. El voltaje mnimo del circuito abierto del transistor es Voc =

Vin. Si Iin es la corriente promedio de entrada con componente ondulatoria despreciable y el

ciclo de trabajo es D = 50%, la corriente pico del transistor es Ipt = Iin/D = 2Iin. La corriente

de entrada es pulsatoria y discontinua. Sin la presencia del diodo D2, fluir una corriente de

CD a travs del transformador. Cuando Q1 esta apagado, el diodo D2 y el condensador C

restablecen el ncleo del transformador. C se descarga a travs de R, cuando D2 est

apagado y en cada ciclo se pierde energa. Este circuito es muy sencillo y est restringido a

aplicaciones por debajo de 500 W. Se trata de un convertidor directo que requiere de un

lazo de retroalimentacin de control de voltaje.

El ncleo del transformador tambin se puede restablecer instalando un embobinado

de restablecimiento como se muestra en la Figura 2.3a , donde la energa almacenada en el

ncleo del transformador es devuelta a la alimentacin aumentando la eficiencia. El voltaje

en circuito abierto del transistor de la Figura 2.3a es

|

(2.1)

donde Np y Nr son el nmero de vueltas en los bobinados primario y de restablecimiento,

respectivamente. La relacin de vueltas de restablecimiento est relacionada con el ciclo de

trabajo segn la frmula (2.1). Para un ciclo de trabajo D = 0.8, Np / Nr = 0.8 / (1 - 0.8) = 4

y el voltaje en circuito abierto se convierte en Voc = Vin (1 + 4) = 5Vin. El voltaje en circuito

abierto del transistor es mucho ms alto que el voltaje de alimentacin. En la Figura 2.3b se

muestran los voltajes y corrientes tanto a la entrada, como a la salida

Figura 2.2Convertidor flyback

26

Metodologa abordada

a) b)

Figura 2.3Convertidor flyback: a) convertidor con bobinado de restablecimiento, b) formas de

onda de voltajes y corrientes

2.1.2 Push-pull

En la topologa del convertidor push-pull el voltaje pico de colector del transistor de

conmutacin es limitado a dos veces el voltaje de entrada. Esto es debido a la simetra del

tap central del transformador con igual numero de vueltas en el devanado primario. El

suministro de voltaje nunca es almacenado en el transformador, por lo cual mas potencia

puede ser manejada obteniendo una mas grande eficiencia y con mejor regulacin que otros

convertidores. El esquema del circuito bsico del convertidor push-pull es mostrado en la

Figura 2.4a, as como sus formas de onda de las corrientes y voltajes en la Figura 2.4b. Los

transistores de conmutacin Q1 y Q2 conducen alternadamente cada medio ciclo en un

ciclo de trabajo determinado por la entrada de la fuente de voltaje Vin, la relacin de

transformacin y el voltaje de salida deseado. As, el ciclo de trabajo mximo alcanzable es

ligeramente menor que el 50 % para el tiempo de apagado del transistor de conmutacin.

Cuando Q1 se activa, Vin aparece a travs de una mitad del primario. Cuando Q2 se

activa, Vin es aplicado a travs de la otra mitad del transformador. El voltaje del bobinado

primario oscila desde -VS. La corriente promedio a travs del transformador debera en

forma ideal ser cero. El voltaje promedio de salida es

Vo = V2 =

Ns

N p

V1 = a V1 = a Vin (2.2)

Los transistores Q1 y Q2 operan con un ciclo de trabajo del 50 %. El voltaje

en circuito abierto es Voc = 2Vin, la corriente promedio de un transistor Iprom = Iin/2 y la

corriente pico del transistor Ipt = Iin. Dado que el voltaje en circuito abierto del transistor es

dos veces el voltaje de suministro, esta configuracin es adecuada para aplicaciones en bajo

voltaje.

27

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

a) b)

Figura 2.4Convertidor push-pull: a) circuito del convertidor, b) formas de onda de voltajes y

corrientes

2.1.3 Medio puente

La topologa medio puente es usada principalmente en convertidores fuera de lnea

donde los transistores de conmutacin no son sometidos al doble de la entrada de la fuente

de voltaje como en los convertidores de conmutacin forward o push-pull. La Figura 2.5a

muestra el esquema del circuito del convertidor medio puente y la Figura 2.5b muestra las

corrientes y voltajes del convertidor. Como se muestra, el extremo del transformador sin

punto es conectado a la terminal comn de los dos condensadores idnticos de filtrado C1 y

C2, va un condensador de bloqueo de CD Cb. El condensador de bloqueo puede ser

omitido en algunas aplicaciones. Un voltaje de cada en el primario resulta debido al

cargado de los condensadores por la corriente que fluye en el transformador. El voltaje de

la fuente de entrada Vs es dividido entre los dos condensadores de filtrado. As, la terminal

comn de los condensadores de filtrado tiene un voltaje promedio de Vin/2. El propsito

del condensador de bloqueo de CD cb es evitar los problemas de desbalance de flujo

causados por el voltaje en la terminal comn ya que no es exactamente la mitad del voltaje

de la fuente de entrada. El extremo del transformador con punto es conectado a la terminal

comn de los transistores de conmutacin configurados en una configuracin totem-pole.

Los transistores de conmutacin Q1 y Q2 conducen alternadamente cada medio ciclo del

ciclo de conmutacin. As, los dos transistores de conmutacin conectan el extremo del

transformador sin punto a Vin y tierra, mientras el extremo con punto del transformador es

mantenido en Vin/2.

28

Metodologa abordada

a) b)

Figura 2.5Convertidor medio puente: a) circuito del convertidor, b) formas de onda de voltajes y

corrientes

Cuando Q2 est activo, Vin/2 aparece a travs del primario del transformador.

Cuando Q1 est activo, aparece un voltaje inverso de valor Vin/2 a travs del primario del

transformador. El voltaje primario oscila desde Vin/2 hasta Vin/2. El voltaje en circuito

abierto del transistor es Voc = Vin y la corriente pico del transistor es Ipt = 2Iin. La corriente

promedio del transistor es Iprom = Iin. En aplicaciones de alto voltaje, el circuito medio

puente es preferible al circuito push-pull. Sin embargo, para aplicaciones en bajo voltaje, es

preferible el circuito push-pull debido a las bajas corrientes de transistor.

El voltaje promedio de salida es

Vo = V2 =

Ns

N p

V1 = a V1 = 0.5 a Vin

(2.3)

2.1.4 Puente completo

La topologa puente completo es usada principalmente en convertidores fuera de

lnea donde sus transistores de conmutacin no son sometidos al doble de la entrada de la

fuente de voltaje Vin. La Figura 2.6a muestra el esquema del circuito del convertidor puente

completo y en la figura 2.6b se muestran los voltajes y corrientes de este circuito. Como se

muestra, los transistores de conmutacin son configurados una topologa puente completo o

H. Los pares de transistores de conmutacin de Q1-Q4 y Q2-Q3 son conmutados

alternadamente cada medio ciclo del periodo de conmutacin. Cuando el par de transistores

Q1-Q4 son encendidos, el extremo punteado del devanado primario es conectado a la

fuente de voltaje de entrada Vin, mientras el extremo sin punto del devanado primario es

conectado a un potencial cercano a tierra. As, todos los extremos punteados de los

29

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

devanados secundarios son ahora positivos con respecto al extremo sin punto. El voltaje en

el devanado secundario es una versin escalada del voltaje en el devanado primario.

Cuando el par de transistores Q2-Q3 son encendidos, el extremo sin punto del devanado

primario es ahora Vin, mientras el extremo punteado es cercano al potencial de tierra.

El voltaje promedio de salida es

Vo = V2 =

Ns

N p

V1 = a V1 = a Vin (2.4)

El voltaje en circuito abierto del transistor es Voc = Vin y la corriente pico del

transistor es Ipt = Iin. La corriente promedio del transistor es slo Iprom = Iin/2. De todas las

configuraciones, este circuito opera con los menores esfuerzos de voltaje y de corriente en

los transistores y es muy popular para aplicaciones de alta potencia por arriba de 750 W.

Una desventaja es el uso de 4 interruptores, lo cual eleva su costo.

2.1.5 Fuente de alta potencia

A continuacin se describe el funcionamiento de una fuente de alta potencia, la cual

se encontr en la literatura [19], ya que de acuerdo a las caractersticas que presenta como

son su alta potencia y principalmente su elevado voltaje de salida es interesante para el

desarrollo de este trabajo, uno de los puntos mas importantes para la fuente a utilizar en el

banco de pruebas.

a) b)

Figura 2.6Convertidor puente completo: a) circuito del convertidor, b) formas de onda de

voltajes y corrientes

30

Metodologa abordada

Esta fuente de CD de alta potencia, 400 kW y 50 kV en modo conmutado fue

diseada para su uso en cargas dinmicas [19]. Esta usa 4 etapas de 100 kW, convertidores

de CD-CD tipo fuente de corriente con entradas en paralelo y salidas en serie. El

convertidor de CD-CD opera a 20 kHz en un regulador de voltaje parcial y a 10 kHz en el

inversor, transformador y las partes de salida del rectificador en el circuito. IGBTs son

usados como interruptores de potencia. Tcnicas especiales son usadas para proteger la

fuente y cargas contra arcos y cortos severos. Tiene una eficiencia del 93%, un voltaje de

rizo en la salida del 1 % y una rpida respuesta dinmica y solo ocupa 1/3 del tamao de

una fuente de potencia convencional. Es regulable de 0 a 50 kV y de 0 a 400 kW.

El convertidor de CD-CD seleccionado es una versin modificada del PWM, el tipo

de fuente de corriente con un regulador separado y una seccin inversora. Esta usa una

forma de onda rectangular, la cual minimiza la necesidad de filtrado en la salida. La fuente

consiste de un rectificador en la entrada, seguida de un filtro como se muestra en la Figura

2.7. Cada convertidor CD-CD consiste de un regulador de voltaje, inductor, inversor,

transformador, rectificador y filtro. Esta empaquetado en dos partes: el modo

regulador/inversor y el mdulo rectificador/transformador.

El regulador de voltaje opera con una forma de onda cuadrada fija como se muestra

en la Figura 2.8. El transformador/rectificador contiene el transformador, rectificador y un

filtro de salida. Cada convertidor produce una salida de voltaje de 12.5 kV. Todos los

IGBTs en el regulador, as como los del inversor, tienen snubbers de la red consistentes de

un diodo, un resistor y un condensador en paralelo con ellos. Cada uno de los IGBTs Q1-

Q4 del inversor conducen por aproximadamente la mitad del tiempo a una frecuencia de 10

kHz. Los pares formados por Q1 y Q2 y por Q3 y Q4 conducen juntos. Ocurre un traslape

de 2 s cada ciclo cuando los 4 conmutan simultneamente. Este tiempo de traslape ayuda

en la trasferencia entre los pares de IGBTs y la polaridad de salida. El suministro de la red

de amortiguamiento formado por C17, CR17 y R9 limita el voltaje a travs del bus de CD

del inversor.

El transformador, rectificador y la interconexin de alambres son montados dentro

de un tanque poco tensionado y son inmersos en un fluido dielctrico de silicn para el

aislamiento elctrico y el enfriamiento. Los filtros de entrada a la red incluyen un filtro

inductor principal de 500H, el filtro de amortiguamiento de la red de 0.5 & en serie con

8000 F, y la combinacin en paralelo de condensadores de 200 F en la entrada de los 4

convertidores.

El transformador/rectificador contiene el transformador, rectificador y un filtro de

salida. El transformador tiene varios requerimientos especiales de diseo:

(1) Voltaje de entrada con forma de onda cuadrada de 520 VPK a 10 kHz, con una

relacin de vueltas de 24, una salida continua de 100 KW, un aislamiento

entre la salida y tierra de 50 kV de CD.

(2) Baja inductancia parsita con prdidas de potencia aceptables en el inversor y

encontrar el rizo de voltaje en la salida especificada, sin exceder l limite del

condensador de filtrado.

31

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

(3) Control de las prdidas del conductor y el ncleo en CA a 10 kHz con un nivel

aceptable.

(4) Devanado de alambre terciario para el control derivado a una seal de

retroalimentacin de voltaje para la salida del convertidor de CD-CD.

Figura 2.7. Esquema simplificado del circuito de potencia de la fuente de 400 KW [9]

El apilamiento de 4 rectificadores es usado en cada tanque transformador /

rectificador. Estos son conectados en una configuracin puente completo. Cada apilamiento

consiste de 24 diodos en serie, con apareamiento y proteccin a travs de cada diodo. Los

diodos son de recuperacin rpida, en un rango de 85 A, 1000 V y 1.6 C de carga en

recuperacin inversa. El circuito de filtrado de CD en la salida del rectificador de puente

completo consiste de un condensador de filtrado principal C1 y la red de amortiguamiento

compuesta del circuito serie formado por R2 y C2-C4. El valor de la capacitancia de

filtrado es determinado primeramente por el tiempo necesario para la transferencia del

inversor entre las polaridades de la corriente combinadas con el rizo de voltaje requeridos.

Referente al control, el reloj de las 4 fases es usado para sincronizar las compuertas

del convertidor CD-CD. Cada convertidor CD-CD tiene su circuiteria propia para generar

la variacin del tren de pulsos del ciclo de trabajo en las compuertas de los IGBTs del

regulador y la onda cuadrada en las compuertas del inversor de IGBT. El comando del ciclo

de trabajo en la compuerta del regulador de los IGBTs llega del convertidor de CD-CD

individual de la salida de voltaje del lazo de retroalimentacin. Esta seal de

retroalimentacin es derivada de un devanado del bobinado del transformador de salida

(VTR) y la corriente de salida (IO). Esta tcnica evita tener que medir en voltajes altos. La

corriente en los IGBTs del regulador (ireg) tambin son usadas en la circuiteria de

retroalimentacin para suministrar un lazo de control local en modo corriente. Este lazo

32

Metodologa abordada

compensa rpidas sobrecargas. El punto fijo de voltaje para cada convertidor CD-CD llega

de la fuente de potencia completa en el control del lazo de voltaje, la cul usa

retroalimentacin seudo-derivativa con limitaciones locales [9]. La retroalimentacin de la

fuente de potencia en conjunto viene con un divisor de voltaje 10000 a 1. Un generador de

rampa suministra una porcin del control del rizo de voltaje durante la recuperacin de una

reduccin.

Figura 2.8Formas de onda idealizadas de voltaje y corriente de la fuente de potencia:

a) potencia media, b) potencia completa [9]

2.4 Conclusiones

Se presentaron los puntos principales a considerar para el diseo de circuitos de

prueba los cuales son: mtodo de pruebas, modo de funcionamiento y el tipo de control, de

entre los cuales de acuerdo a los requerimientos de los dispositivos se ve que los circuitos

especiales de prueba, as como el tipo de funcionamiento en modo impulsional y con un

tiempo preestablecido son las condiciones en las cuales se puede estudiar el

funcionamiento del dispositivo con un menor costo y menores componentes y exigencias a

la lnea de distribucin.

33

Desarrollo e Implementacin de un Banco de Pruebas para Caracterizar Dispositivos de Alta Potencia

Otro punto importante es el tener un simulador el cual debe tener los modelos de

todo componente lo mas cercano a ellos para tener resultados mucho mas cercanos a lo

realizado experimentalmente.