Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Notas de VHDL

Cargado por

JLB_Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Notas de VHDL

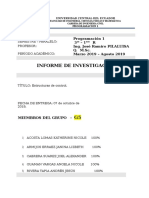

Cargado por

JLB_Copyright:

Formatos disponibles

ndice de contenido

Introduccin...............................................................................................................................................2

Estado actual de la lgica programable.................................................................................................2

Lenguaje de descripcin.............................................................................................................................2

Introduccin...........................................................................................................................................2

Herramientas necesarias para el desarrollo con VHDL........................................................................2

Consideraciones antes de continuar con VHDL....................................................................................2

Unidades bsicas de diseo...................................................................................................................

!signacin concurrente........................................................................................................................."

!signacin condicional.........................................................................................................................#

!signacin seleccionada.......................................................................................................................$

%roceso..................................................................................................................................................&

Estilos de programacin.............................................................................................................................'

(lujo de datos........................................................................................................................................'

(uncional...............................................................................................................................................'

Estructural...........................................................................................................................................)#

*+uinas de estados ,initos.....................................................................................................................)$

Desarrollo de una aplicacin....................................................................................................................)$

-ibliogra,.a..............................................................................................................................................)$

)

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

Introduccin

Estado actual de la lgica programable

El error ms..

Lenguaje de descripcin

Introduccin

El error ms gra0e +ue cometemos es intentar programar en VHDL como si 1ste ,uera un lenguaje

de programacin de computadoras de alto ni0el. Los lenguajes de programacin de alto ni0el son

secuenciales por naturale2a3 VHDL no. VHDL se in0ent para describir 4ard5are 6 de 4ec4o es un

lenguaje concurrente 7todo al mismo tiempo8. Los dos propsitos principales de un lenguaje de

descripcin de 4ard5are son9 primero: +ue puede ser usado para modelar circuitos 6 sistemas digitales3

segundo: teniendo el modelo: permite la subsecuente prueba 6 simulacin del sistema.

El acto de conectar un montn de l.neas 6 blo+ues: pronto se 0uel0e tedioso: con VHDL: tenemos

4erramientas para modelar circuitos digitales de una manera ms inteligente. Esta metodolog.a de

diseo nos permitir dedicar ms tiempo en el diseo de nuestros circuitos 6 menos tiempo en

construirlos.

! continuacin listamos algunas reglas +ue nos sern de utilidad: cuando trabajamos con VHDL9

Cuando trabajamos con VHDL: no estamos programando: estamos diseando 4ard5are. ;i el

cdigo en VHDL se parece al cdigo en un lenguaje de alto ni0el: entonces es un mal cdigo en

VHDL.

Los circuitos digitales ms complejos pueden ser e<presados en t1rminos de construcciones

digitales bsicas.

Herramientas necesarias para el desarrollo con VHDL

La implementacin e<itosa de sistemas con VHDL comien2a por la escritura del cdigo:

compilacin: simulacin 6 s.ntesis. Los ,abricantes de C%LD 6 (%=! proporcionan un conjunto de

4erramientas 4ard5are 6 so,t5are +ue podemos usar para lle0ar a cabo los mencionados pasos.

Consideraciones antes de continuar con VHDL

VHDL no es sensible a las maysculas 7>ienen el mismo signi,icado9 and 6 !nD8.

2

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

VHDL no es sensible a los espacios en blanco 7El mismo signi,icado9 ?@A!3 6 ? @A !38.

Los comentarios comien2an con9 BCCD 7dos guiones8: usar los comentarios apropiados ,acilita el

entendimiento de la descripcin.

La mejor idea es usar parntesis libremente para asegurar el entendimiento del cdigo.

Cada instruccin en VHDL termina con B;D 7punto 6 coma8.

>omar en cuenta lo siguiente para e0itar errores en las instrucciones if: case 6 loop9

Cada BifD tiene su correspondiente BthenD.

Cada BifD debe terminar con Bend ifD.

;i es necesario usar Belse ifD: la 0ersin en VHDL es BelsifD.

Cada BcaseD debe terminar con Bend caseD.

Cada BloopD debe terminar con Bend loopD.

%ara los identificadores 7nombres de 0ariables: constantes: seales: puertos: etc1tera89

Los identi,icadores se deben e<plicar por s. mismos.

%ueden ser tan largos como se desee.

%ueden contener una combinacin de letras: nEmeros 6 guin bajo.

Deben comen2ar con un carcter al,ab1tico.

Fo pueden ,inali2ar con guin bajo: ni tener dos guiones consecuti0os.

Fo se pueden usar las palabras reser0adas7process: label: a,ter: etc1tera8 como identi,icadores.

Unidades bsicas de diseo

Las descripciones de circuitos en VHDL estn basadas en el concepto de Bcaja negraD. En t1rminos

de VHDL: la caja negra est descrita por la declaracin de una entidad: la cul identi,ica con claridad

las entradas 6 salidas generales del sistema.

entity nombre de la entidad is Ggeneric 7opcional: para declarar 0ariables locales83H

port 7nombre de la seal9 modo tipo3

nombre de la seal9 modo tipo3

9

nombre de la seal9 modo tipo83

end nombre de la entidad3

*odo 7especi,ica la direccin de la seal8

in Indica +ue la seal es de entrada.

out Indica +ue la seal es de salida. ;u

0alor puede slo ser le.do por otras

entidades.

bu,,er %ermite 4acer realimentaciones

internas dentro de la entidad. ;e

comporta como salida.

inout ;eal bidireccional.

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

>ipo

bit %uede tener el 0alor de I 6 ).

bit/0ector Conjunto de bits para cada

0ariable de entrada o salida.

integer %uede tener un rango de

0alores enteros.

boolean %uede tener >JUE 6 (!L;E.

real

%uede tener un rango de

0alores reales.

c4aracter Cual+uier carcter.

time %ara indicar el tiempo.

std/logic/0ector K

std/logic K

K>ipos contenidos en la librer.a iee: en el pa+uete std_logic_1164. Una 0e2 +ue estas librer.as 4an

sido incluidas: tendremos acceso a una 0ariedad de 0entajas como9 0arios tipos de datos: ,unciones de

con0ersin: ,unciones matemticas: etc1tera.

Las seales pueden ser e<presadas como indi0iduales o un conjunto de ellas. %or ejemplo: las

seales en un BbusD pueden ser e<presadas como un 0ector 7std/ligic/0ector8: 1stas pueden ser

e<presadas considerando dos tipos de orden por medio de las palabras reser0adas BTOD 6

BDOWNTOD. ;i +ueremos +ue el bit ms signi,icati0o del conjunto sea el primer bit de la i2+uierda

usamos la palabra9 BDOWNTOD. Es decir9

DOWNTO A -

$

-

#

-

"

-

L

-

-

2

-

)

-

I

TO A -

I

-

)

-

2

-

-

L

-

"

-

#

-

$

La ar+uitectura describe lo +ue el circuito 4ace. En otras palabras: en VHDL describe la

implementacin interna de la entidad asociada a ella.

architecture nombre de la arquitectura of nombre de la entidad is

declaraciones

componentes

seales

constantes

,uncin

procedimiento

tipos

egin

sentencias

end nombre de la arquitectura;

Una ar+uitectura puede ser modelada de di,erentes maneras. Entendiendo las di,erentes t1cnicas de

modelado 6 cmo usarlas: representa el paso ms importante para aprender VHDL. Una ar+uitectura

puede ser escrita mediante tres t1cnicas de modelado: mas la combinacin de cual+uiera de las tres9

L

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

!odelos

(lujo de datos

(uncional

Estructural

4.brido

Dentro de los tipos de objetos ms usados tenemos las seales7signal8: para representar un alambre3

0ariables7"ariale8: usadas para almacenar in,ormacin local 6 las constantes 7constant8: +ue son

como una 0ariable: pero cu6o 0alor no puede ser cambiado.

Las seales se declaran al inicio de la ar+uitectura: antes de la palabra BeginD.

Las 0ariables se declaran dentro de la estructura BprocessD: antes de la palabra BeginD.

El paradigma de la descripcin en VHDL se ,undamenta en el paralelismo 6 la concurrencia con la

descripcin te<tual de los circuitos. El cora2n de la descripcin en VHDL es la sentencia concurrente.

E<isten cuatro tipos de sentencias concurrentes9

). !signacin concurrente de seal.

2. !signacin condicional de seal.

. !signacin seleccionada de seal.

L. %roceso.

Asignacin concurrente

La ,orma general de la asignacin concurrente se muestra a continuacin9

@destinoM @A @e<presinM3

En el siguiente ejemplo se muestran dos ,ormas de implementar la ,uncin en VHDL9

"

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

En los ejemplos notamos +ue la declaracin intermedia de las seales es similar a las declaraciones

del puerto en la entidad: e<cepto +ue no se especi,ica el modo 7in: out: inout8. Las seales intermedias

deben ser declaradas en el cuerpo de la ar+uitectura por+ue no tienen enlace al mundo e<terno 6 por eso

no aparecen en la declaracin de entidad. !un+ue el uso de seales intermedias no es obligatorio: su

uso trae consigo algunos bene,icios. %rimero: el uso de seales intermedias es la norma para muc4os

modelos VHDL. Con,orme los circuitos se 4acen ms complejos: e<isten ocasiones en +ue el uso de

seales intermedias se 4ace necesario. ;egundo: el uso de 1stas seales nos permite modelar circuitos

digitales de una manera ms ,cil 6: adems: no implica +ue el 4ard5are generado sea ms complicado.

Las descripciones simples de circuitos tienen la 0entaja de ser ms ,cilmente entendidos 6

sinteti2ados. %ero lo ms importante: es +ue un modelo simple en VHDL no tiene relacin con

la longitud del cdigo.

Asignacin condicional

La sinta<is de la asignacin condicional se muestra a continuacin9

@targetM @A @e<pressionM 54en @conditionM else

@e<pressionM 54en @conditionM else

@e<pressionM3

La mejor ,orma de entender 1sta asignacin es a tra01s de un ejemplo. Consideremos la descripcin

en VHDL de la misma ,uncin del ejemplo anterior9

Esta descripcin no implica una mejora sobre la anterior: en ella e<iste una ,uncin 7target8 6 0arias

e<presiones 6 condiciones. ;i ninguna de las primeras condiciones se cumple: la Eltima es la +ue se

asigna a la ,uncin 7target8.

Es un ejemplo ilustrati0o de +ue podemos usar la asignacin concurrente o condicional para

describir un circuito: sin embargo: e<isten usos ms inteligentes de la asignacin condicional3 por

ejemplo en la descripcin de un multiple<or9

En el ejemplo: ambas descripciones utili2an la asignacin condicional: sin embargo: la di,erencia

#

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

est en usar seales agrupadas 7ilustracin de la i2+uierda8 o seales indi0iduales 7ilustracin de la

derec4a8.

!lgunas notas respecto al ejemplo9

En general: se usan comillas dobles para 0alores asociados con mEltiples seales 7ilustracin

i2+uierda8 6 comillas sencillas para 0alores asociados con seales indi0iduales.

%odemos acceder a seales indi0iduales aun+ue 4a6an sido declaradas como grupo de seales

7std/logic/0ector8: mediante una sinta<is especial 7por ejemplo9 #$%&1'8.

La solucin utili2a el operador relacional BAD: sin embargo: como se ilustra en la ,igura: e<isten

seis tipos en VHDL.

Asignacin seleccionada

El tercer tipo de asignacin de una seal es la asignacin seleccionada: cu6a sinta<is se muestra a

continuacin9

5it4 @c4oose/e<pressionM select

target @A @e<pressionM 54en @c4oicesM:

@e<pressionM 54en @c4oicesM3

Como en la asignacin condicional: 1ste tipo de asignacin tambi1n tiene slo un operador de

asignacin.

Fue0amente describamos la ,uncin de los ejemplos anteriores: pero a4ora usando este tipo de

asignacin9

Fotemos el uso de la sentencia

54en ot4ers al , i nal de l a

descripcin.

Consideremos nue0amente la descripcin

del multiple<or: para darnos cuenta del uso

ms i nt el i gent e de l a as i gnaci n

seleccionada9

El Enico re+uisito para el uso de la

sentencia 54en ot4ers es +ue se ubi+ue al

,inal de la sentencia select.

$

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

Ntro ejemplo: muestra el uso del operador BOD como carcter de seleccin en la seccin de opciones9

!4ora describamos la ,uncin de los

ejemplos anteriores: pero usando este tipo de

asignacin9

Proceso

E<isten di,erentes 6 0ariadas maneras de solucionar el mismo problema: entonces slo +ueda al

diseador escribir su diseo de la manera ms entendible 6 dejar a la 4erramienta de s.ntesis ordenar

los detalles.

La sentencia process es una 4erramienta +ue nos permite ejecutar un cierto nEmero de instrucciones

de manera secuencial: sin embargo: no debemos ol0idar +ue la sentencia 7process8: en s. misma: es

concurrente.

&

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

Estilos de programacin

En la prctica: los circuitos ms complejos: descritos en VHDL: usan una me2cla de los tres

primeros estilos. El m1todo estructural es esencialmente un m1todo +ue combina un conjunto de

modelos VHDL e<istentes: es por esto +ue: en lugar de ser un m1todo de diseo: es ms una ,acilidad

para interconectar mdulos e<istentes.

Fluo de datos

En las ar+uitecturas de ,lujo de datos se encuentran las sentencias concurrentes descritas

anteriormente 7asignacin concurrente: condicional 6 seleccionada8. %or lo tanto: los ejemplos descritos

anteriormente pertenecen a las ar+uitecturas diseadas con estilo de ,lujo de datos. En estos ejemplos:

podemos prcticamente Bobser0arD el ,lujo de los datos por el circuito. Este tipo de modelado ,unciona

bien para circuitos pe+ueos 6 relati0amente simples. %ero: para circuitos ms complejos: es mejor

cambiar a los modelos ,uncionales.

Funcional

El cora2n de este estilo de programacin es la sentencia process. El principal punto a recordar es

+ue el cuerpo del proceso se compone de sentencias secuenciales. Es importante resalta +ue la

ejecucin de una sentencia en el estilo

,uncional es controlada por las seales +ue

aparecen en Bsensi0it6/ListD. %or el

contrario: las sentencias +ue aparecen en el

modelo de ,lujo de datos: son reCe0aluadas

cada 0e2 +ue las seales de entrada

cambian. Esto es una di,erencia ,uncional:

no slo una di,erencia de apariencia.

La sentencia process deber.a ser considerada como una manera +ue el diseador tiene a su

disposicin para ejecutar una serie de sentencias secuenciales: sin ol0idar +ue la sentencia process es en

s. una sentencia concurrente.

Ejemplo9 Describir un comparador mostrado en la ,igura: usando el

modelo ,uncional.

'

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

;entencias secuenciales9 La ejecucin de una sentencia secuencial se inicia cuando ocurre un

cambio en la lista sensiti0a. Debemos recordar +ue la sentencia process es concurrente:

debemos tomar 0entaja de esta ,acilidad: para simpli,icar nuestras descripciones de circuitos.

E<isten tres tipos de sentencias secuenciales9

;entencia de asignacin de una seal B @A B

;entencia Bi,D: se utili2a para pro0ocar una bi,urcacin en el

,lujo de ejecucin de las sentencias secuenciales. Es el

e+ui0alente secuencial de la asignacin condicional de una

seal. ;u ,orma general es9

!lgunas notas acerca de la sinta<is9

Los par1ntesis son opcionales: sin embargo: deber.an incluirse para aumentar el

entendimiento del cdigo VHDL.

La sentencia BelseD ,inal no se asocia con un Bt4enD ,inal: si ninguna de las

sentencias anteriores son ciertas: el else ,inal se ejecuta. Psto garanti2a +ue al menos

una de las secuencias es ejecutada.

La sentencia else es opcional: sin embargo: no incluirla representa la posibilidad de

+ue ninguna de las secuencias sea ejecutada.

Ejemplo9 escribir el cdigo

VHDL: usando la sentencia i,:

+ue descr i ba l a , unci n9

(7!:-:C8 A !-QCQR-C.

)I

Una solucin

Una mejor solucin

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

La sentencia process puede ir precedida con una eti+ueta opcional. Una eti+ueta deber.a

siempre incluirse para identi,icar el proceso como una ,orma de auto descripcin. Un uso

ms inteligente de la sentencia i, se presenta en el siguiente ejemplo9

Ejemplo9 Escribir el cdigo VHDL

+ue describe el *US de la ,igura.

En este ejemplo se puede borrar la sentencia elsi, ,inal 6 colocar la asignacin ,inal en la

sentencia else. ;in embargo 1sto no se considera una buena prctica en VHDL 6 debe ser

e0itada.

Un ejemplo ms9 Escribir el cdigo

VHDL para describir el ,uncionamiento

del *US de la ,igura.

))

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

En la sentencia case: slo se ejecuta un conjunto de

sentencias secuenciales por cada ejecucin de la

sentencia case. Es el e+ui0alente secuencial de la

sentencia de 5it4. ;in embargo: la sentencia case es una

sentencia secuencial +ue se encuentra en el cuerpo de

process mientras +ue 5it4 es una ,orma de asignacin

de una seal concurrente.

Ejemplo: Escribir el cdigo para implementar: (7!:-:C8 A !-QCQR-C. %rimero: procedemos a

completar la ,uncin con los t1rminos

,altantes9(7!:-:C8A!-QCQR-C7!R!Q8A

!-QCQR!-CR!Q-C.

En VHDL podemos usar la ,acilidad de Bno

importaD: sin embargo: se debe e0itar a toda

costa: por+ue algunas 4erramientas de s.ntesis

6 algunos simuladores no pueden manejarla

bien. ;lo mencionaremos cmo se 4ar.a en el

ejemplo de abajo9

Ejemplo9 Vol0amos a escribir el cdigo +ue implemente el

multiple<or de la ,igura9

Lo interesante de la solucin

mostrada en el cdigo de la

derec4a: es +ue la sentencia

case est embebida dentro de

la sentencia i,: dic4o de otra manera: est BanidadaD. Esta

,acilidad es lo +ue 4ace al modelo ,uncional ms poderoso

+ue el de ,lujo de datos.

)2

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

!lgunas recomendaciones antes de concluir con el modelo ,uncional9

;i no entendemos las entradas 6 salidas de VHDL al ni0el bajo: el circuito no se

sinteti2ar apropiadamente.

*antenga sus modelos VHDL lo ms simple posibles: particularmente en la sentencia

process.

En VHDL: la mejor manera es mantener las sentencias process centradas alrededor de

una ,uncin sencilla 6 tener 0arias sentencias process +ue se comuni+uen con cada una.

!lgunas notas acerca de los operadores +ue nos sern de utilidad. Los operadores in VHDL se

agrupan en di,erentes tipos: segEn muestra la tabla9

!lgunos de ellos re+uieren de consideraciones especiales: por ejemplo: los operadores de

despla2amiento re+uieren de las librer.as

ieee.numeric_std o ieee.numeric_bit.

Ejemplos de estos operadores: se

muestran en la tabla9

La di,erencia entre los despla2amientos

lgicos 6 aritm1ticos: es +ue en los

aritm1ticos: el bit de signo nunca cambia 6

el bit +ue se alimenta al ,inal puede ser di,erente.

En la tabla de la derec4a: se muestran otros

operadores9

)

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

Otra recomendacin es que no se debe emplear mucho esfuerzo en memorizar la sintaxis de VH!"

mejor se recomienda que siempre que est#s describiendo un modelo" ten$as a la mano un %acorden&.

esarrollar un 'erdadero entendimiento de VH!" es lo que te con'ertir( en un buen diseador de

hard)are. !a habilidad para memorizar la sintaxis de VH! nos proporciona %almost nothin$&.

*ircuitos secuenciales

Hasta a4ora todo el estudio 6 los ejemplos de VHDL 4an sido elaborados describiendo circuitos

combinacionales: sin embargo: cuando usamos elementos de almacenamiento en el diseo digital: es

necesario describir los circuitos secuenciales. Es posible 6 en algunos casos deseable usar el modelo de

flujo de datos para describir elementos de memoria en VHDL: pero es ms ,cil usar el modelo

funcional.

El estudio de los elementos de memoria comien2a con los ,lipC,lops tipo D: disparados por ,lancos.

%odemos notar +ue la ,uncin rising/edge7CLT8 tambi1n puede ser reempla2ada por la popular

sentencia9 CLTQ e0ent and CLTAQ)Q3

El m1todo usado para asegurar algun estado del ,lipC,lop en caso de +ue la condicin listada en la

sentencia i, no se cumpla: es usando else. Un B5arningD generado por los sinteti2adores de VHDL es la

noti,icacin de +ue se 4a generado un latch. La causa del problema es +ue no se 4a proporcionado

e<pl.citamente un estado de salida para todas las posibles condiciones de entrada. Esto se arregla

colocando otra entrada +ue est1 en sincron.a con la seal de reloj.

La entrada B;D permite la operacin del ,lipC,lop en el pulso de subida del reloj del sistema. En el

pulso de subida del reloj: la entrada B;D toma precedencia sobre la entrada BDD por+ue se re0isa

primero el estado de la entrada B;D en lugar de e<aminar la entrada BDD. La entrada BDD se trans,iere a

la salida slo en el pulso de subida del reloj 6 slo si la entrada B;D est en ni0el bajo.

)L

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

!+u. el diagrama lgico 6 el cdigo VHDL9

Con ,ines de comparacin entre una entrada

as.ncrona 6 una s.ncrona: describiremos la misma

estructura: pero con una entrada BJD 7reset8: +ue es

independiente del reloj. La prioridad se determina

poniendo BJD como la primera condicin en la

sentencia i,. !simismo: se utili2ar la ,uncin

,alling/edge78: para 4acer +ue el ,lipC,lip se acti0e

con un pulso de bajada.

Las ,ormas generales a estas soluciones son

consideradas como los patrones para las entradas

s.ncronas 6 as.ncronas en 0arias re,erencias de VHDL.

Ntro ejemplo consiste en describir la ,uncin de un ,lipC,lop tipo >: sin embargo a4ora

consideraremos la entrada B;D como una seal as.ncrona +ue es acti0a en ni0el bajo: para establecer la

salida del ,lipC,lop tipo >.

)"

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

!as seales que son declaradas como salidas no pueden aparecer en el lado derecho del operador

de asi$nacin. %ara sol0entar este problema: 4acemos uso de las seales intermedias: las cuales pueden

ser usadas como entradas o salidas. Ntra solucin para e0itar este problema es 4aciendo uso de la

especi,icacin de Bbu,,erD: pero nunca debemos usar 1sto en VHDL. El buen uso de VHDL es cuando

recurrimos a las seales intermedias.

Los ,lipC,lops tipo BDD son los elementos de almacenamiento pre,eridos en VHDL. ;i no 4a6 alguna

ra2n espec.,ica para utili2ar otro tipo de ,lipC,lop +ue no sea del tipo BDD: no deber+amos hacerlo.

En VHDL: como en otros lenguajes: 4a6 maneras espec.,icas de 4acer cosas 6 estas cosas deben ser

siempre reali2adas de estas maneras.

Estructural

...

)#

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

Mquinas de estados finitos

Las *+uinas de Estados (initos7(;*8 son abstracciones matemticas utili2adas para resol0er

problemas de automati2acin electrnica: disear protocolos de comunicacin: anlisis 6 otras

aplicaciones de ingenier.a.

La 0ersatilidad del comportamiento en VHDL e0ita la necesidad de 4acer largos diseos en papel.

En la ,igura podemos apreciar el modelo (;* usado en VHDL3 Bparallel InputsD se utili2an para

representar las entradas +ue actEan sobre

cada elemento de almacenamiento

7enables: presets: clears: etc1tera8: B;tate

transitionD inclu6en entradas e<ternas +ue

controlan las transiciones de estado:

B%resent ;tateD son utili2adas por el

BCombinatorial %rocessD para decodi,icar

el siguiente estado BFe<t ;tateD 6 la

salida BE<ternal NutputsD.

E<isten di,erentes m1todos para describir una (;*: sin embargo los ms usados son el dependiente

e independiente %;UF; 7%resent ;tateUFe<t ;tate8. El modelo representado en la ,igura es el

dependiente: es ms claro 6 nos permitir entender ,cilmente el modelo independiente.

Ejemplo9 Usando un estilo de codi,icacin

dependiente: describir el diagrama de estados mostrado

en la ,igura.

Es recomendable dibujar el diagrama de blo+ues.

)$

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

!lgunas notas respecto al ejemplo anterior9

;e 4a declarado un tipo especial 7t6pe8 llamado Bstate/t6peD para representar los estados de la

(;*. Esta 0ariable 4a sido creada 6 no ,orma parte de los tipos nati0os de VHDL.

El elemento de almacenamiento est asociado solamente con la seal B%;D 6 no est

especi,icado para cada combinacin posible de las entradas.

E<isten dos procesos9 El proceso s.ncrono +ue maneja las seales de BJesetD 6 la asignacin de

un nue0o estado al llegar la seal de reloj: el proceso combinacional maneja las salidas no

utili2adas por el proceso s.ncrono.

Debido a +ue los dos procesos operan de manera concurrente: puede considerarse +ue operan de

manera concatenada: un cambio en el circuito combinacional: a,ecta al circuito secuencial 6 as.

sucesi0amente.

Este es el ,ormato estndar para el estilo de cdigo dependiente %;UF;.

La salida de la m+uina de *oore depende slo del estado presente. La 0ariable BV)D est

dentro de la sentencia 54en 6 ,uera del i,. Esto se debe a +ue las salidas de la m+uina

solamente son ,uncin de los estados: no de las entradas e<ternas.

La salida BV)D es establecida a un 0alor: como primer paso del proceso combinacional. Esto

pre0iene seales de V) inesperadas.

!as 'ariables de estados son representadas internamente , no necesita ser precisa porque no son

proporcionadas como una salida.

En algunos diseos: las 0ariables de estado se

proporcionan como salida como indica el diagrama 6 el

cdigo adjunto.

Este cdigo slo di,iere del anterior en la declaracin

de la entidad donde se inclu6e la 0ariable BWD para la

asignacin del estado: adems de la seleccin de seal

BWD basada en la condicin de la 0ariable de estado.

%odemos notar +ue e<isten tres asignaciones

concurrente9 los dos procesos 6 la asignacin por

asignacin en la parte ,inal del cdigo.

)&

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

Ntro ejemplo9

El diagrama muestra +ue es una m+uina tipo *eal6 con

una salida e<terna 6 entrada e<terna. Como tiene tres

estados: la solucin re+uiere al menos dos 0ariables de

estado.

Ntro ejemplo9

-en$amos en mente que un in$eniero

raramente se basa en recetas de

cocina. .ara las /01" el in$eniero es

el creador , probador del dia$rama

de estados.

)'

Apuntes de VHDL

(JLB)

///////////////////////////////////////////////////////////////////////////////////

Desarrollo de una aplicacin

Biliograf!a

*a<ine2: D. =.: X !lcal Yara: Y. 72II$8. VH!2 el arte de pro$ramar sistemas di$itales. *1<ico9 CN*%!Z[! EDI>NJI!L CNF>IFEF>!L.

\4at is %rogrammable Logic] 7s. ,.8. Jecuperado )) de mar2o de 2I): a partir de 4ttp9UU555.<ilin<.comUcompan6UaboutUprogrammable.4tml

2I

También podría gustarte

- Configurar Arduino Nano (Clone)Documento8 páginasConfigurar Arduino Nano (Clone)JLB_Aún no hay calificaciones

- Unidad 1 Sistemas y Unidades de Información DocumentalesDocumento4 páginasUnidad 1 Sistemas y Unidades de Información DocumentalesJLB_Aún no hay calificaciones

- Unidad 1 Sistemas y Unidades de Información DocumentalesDocumento4 páginasUnidad 1 Sistemas y Unidades de Información DocumentalesJLB_Aún no hay calificaciones

- Unidad 1 Sistemas y Unidades de Información DocumentalesDocumento4 páginasUnidad 1 Sistemas y Unidades de Información DocumentalesJLB_Aún no hay calificaciones

- Unidad 1 Sistemas y Unidades de Información DocumentalesDocumento4 páginasUnidad 1 Sistemas y Unidades de Información DocumentalesJLB_Aún no hay calificaciones

- Unidad 2 Técnicas Bibliográficas y Normas de Redacción Documental (Actividad 2)Documento6 páginasUnidad 2 Técnicas Bibliográficas y Normas de Redacción Documental (Actividad 2)JLB_Aún no hay calificaciones

- Guia NT11 SDocumento17 páginasGuia NT11 Sgrover2010Aún no hay calificaciones

- Modelado de alcantarillados con SewerGEMS v8i SS5Documento2 páginasModelado de alcantarillados con SewerGEMS v8i SS5José Antonio Aliaga AzañaAún no hay calificaciones

- Apunte Manipulacion y Preservacion de DatosDocumento38 páginasApunte Manipulacion y Preservacion de DatosalegonconAún no hay calificaciones

- Clase Listas DoblesDocumento2 páginasClase Listas DoblesEstebanRodriguezAún no hay calificaciones

- Etapas de La SimulacionDocumento4 páginasEtapas de La SimulacionTere GutiérrezAún no hay calificaciones

- Algoritmo Del EscánerDocumento1 páginaAlgoritmo Del EscánerRocko AshfordAún no hay calificaciones

- Cap 01 - Fundamentos de La Programación GisDocumento31 páginasCap 01 - Fundamentos de La Programación GissantiagoAún no hay calificaciones

- Guia Teorica ArreglosDocumento22 páginasGuia Teorica ArreglosEfrain Josue Boatswain MedinaAún no hay calificaciones

- Programa - Computacion Aplicada A La Geologia-TorielliDocumento7 páginasPrograma - Computacion Aplicada A La Geologia-TorielliMichael RonaldAún no hay calificaciones

- Tutorial Clasificacion No Supervisada 3.0estableDocumento5 páginasTutorial Clasificacion No Supervisada 3.0establemartinezdiegoeAún no hay calificaciones

- Open MPDocumento25 páginasOpen MPJuan Íñigo MonjasAún no hay calificaciones

- Lo Primero Sería Abrir El Kali Linux y Entrar en El SeToolKit IDocumento13 páginasLo Primero Sería Abrir El Kali Linux y Entrar en El SeToolKit IMartin Quiroz SalazarAún no hay calificaciones

- Red Hopfield (Editado)Documento18 páginasRed Hopfield (Editado)sonia marcela duqueAún no hay calificaciones

- Linea Del TiempoDocumento1 páginaLinea Del TiempoEileen MarinAún no hay calificaciones

- Estructuras de control en programaciónDocumento13 páginasEstructuras de control en programaciónAngee Jeon ♡Aún no hay calificaciones

- C 4153045Documento1015 páginasC 4153045Pierre PandurAún no hay calificaciones

- Metodo CasoDocumento7 páginasMetodo CasoSaul RgvAún no hay calificaciones

- Problemas de ReemplazoDocumento12 páginasProblemas de ReemplazoValentirri EDAún no hay calificaciones

- Cambiar Sistema Operativo en TabletDocumento6 páginasCambiar Sistema Operativo en TabletMigan Electronica50% (2)

- Lista de Chequeo Desempeño MantenimientoDocumento3 páginasLista de Chequeo Desempeño Mantenimientoingalejo1Aún no hay calificaciones

- 1.2 El Procesador y Sus Registros InternosDocumento18 páginas1.2 El Procesador y Sus Registros InternosFrank Diaz100% (1)

- Metodología de La Programación Orientada A Objetos Con C++Documento49 páginasMetodología de La Programación Orientada A Objetos Con C++GranSnake100% (4)

- Delphi OOP-Cap 01Documento32 páginasDelphi OOP-Cap 01Adolfo PachónAún no hay calificaciones

- Conversión de Tipos en Java. (Casting)Documento3 páginasConversión de Tipos en Java. (Casting)Esteban Mariano GutierrezAún no hay calificaciones

- 2 RecursividadDocumento15 páginas2 Recursividadeloisa15Aún no hay calificaciones

- Taller Capitulo 4Documento3 páginasTaller Capitulo 4klorenacastiblancoc3964100% (5)

- Clasificación de Las FallasDocumento2 páginasClasificación de Las FallasPrincipios ProgramacionAún no hay calificaciones

- Tema 1Documento65 páginasTema 1Jose Manuel Rosales RuizAún no hay calificaciones

- Diseño de páginas webDocumento2 páginasDiseño de páginas webMelquisedec De JesusAún no hay calificaciones

- Protocolo MDBDocumento6 páginasProtocolo MDBJoshua Vinicio Lascano50% (2)