Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Detector de Código BCD Simulado en Quartus 13.0

Cargado por

Kevin Arteaga0 calificaciones0% encontró este documento útil (0 votos)

225 vistas13 páginasEl sistema digital determina si el número ingresado corresponde un BCD. En caso de no serlo activa la señal error.

Título original

Detector de código BCD simulado en Quartus 13.0

Derechos de autor

© © All Rights Reserved

Formatos disponibles

PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoEl sistema digital determina si el número ingresado corresponde un BCD. En caso de no serlo activa la señal error.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

225 vistas13 páginasDetector de Código BCD Simulado en Quartus 13.0

Cargado por

Kevin ArteagaEl sistema digital determina si el número ingresado corresponde un BCD. En caso de no serlo activa la señal error.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Está en la página 1de 13

ESCUELA SUPERIOR POLITCNICA DEL LITORAL

FACULTAD DE INGENIERA EN ELECTRICIDAD Y COMPUTACION

LABORATORIO DE SISTEMAS DIGITALES

Proyecto de primer parcial

DETECTOR BCD

Presentado por:

KEVIN ARTEAGA YELA

XAVIER AGUAYO MURILLO

Profesor a cargo:

ING. RONALD PONGUILLO

Guayaquil Ecuador

2014

2

CONTENIDO

1. ESPECIFICACIN ......................................................................................................... 3

DETECTOR DE CODIGO BCD ................................................................................. 3

2. DIAGRAMA DE BLOQUES ............................................................................................ 4

3. DIAGRAMA ASM ........................................................................................................... 5

4. DIAGRAMA DE TIEMPO ............................................................................................... 6

Salida BCD activada .................................................................................................. 6

Salida ERROR activada ............................................................................................ 7

5. DIAGRAMA ESQUEMATICO ......................................................................................... 7

6. DESCRIPCION VHDL.................................................................................................... 9

7. REPORTE SOBRE APROVECHAMIENTO ................................................................. 11

8. CONCLUSIONES ........................................................................................................ 12

9. RECOMENDACIONES ................................................................................................ 12

10. BIBLIOGRAFA ........................................................................................................ 13

3

1. ESPECIFICACIN

DETECTOR DE CODIGO BCD

Disear y construir un circuito DETECTOR DE CODIGO BCD. El circuito tiene una

entrada serial de DATOS, la entrada START y la entrada MOSTRAR representadas

por botoneras y dos salidas (BCD y ERROR) indicadas con dos diodos LED.

Adicionalmente se agregaron dos entradas: la entrada INGRESAR y la entrada

STOP.

Al presionar y soltar la botonera START, el circuito habilitar la entrada de DATOS

siempre que presionemos la entrada INGRESAR, asumiendo que el primer bit que

se ingresa es el LSB. Despus de haber ingresado los datos presionaremos el

botn STOP para detener el ingreso de datos.

Si el cdigo ingresado corresponde a un cdigo BCD, el circuito regresa al estado

inicial generando la seal de salida BCD.

Pero, si el cdigo ingresado no corresponde a un cdigo BCD, el circuito genera la

seal de salida ERROR y luego regresa al estado inicial.

Los diodos LED que indican las salidas BCD y ERROR permanecen prendidos hasta

que se activa la entrada START para empezar el ingreso de un nuevo dato.

Si la seal BCD ha sido activada y se presiona el botn MOSTRAR entonces el

numero BCD ingresado es mostrado en un display de siete segmentos.

4

2. DIAGRAMA DE BLOQUES

En esta seccin mostraremos un esquema general de nuestro sistema digital

DETECTOR BCD, indicando las entradas, salidas y una breve descripcin de la

funcin de cada una. El diagrama de bloques est formado por los siguientes

componentes.

Controlador

Almacenador de datos

Detector BCD

Display

El controlador dirige las acciones del usuario y de la maquina de estados, las

entradas y salidas se muestran en la figura 1. Las entradas del controlador se

encuentran en la parte izquierda del bloque y las salidas a la derecha.

El almacenador de datos guarda los cuatro bits (0 - 1) que el usuario ingrese, el

ingreso de cada bit es habilitado por la entrada en_guarda. La salida del bloque

almacenador de datos es un nmero de cuatro bits.

El detector BCD comprueba si el dato mostrado es un nmero BCD y su salida

SiEsBCD se conecta al controlador para que el tome la decisin de mostrarle al

usuario si es BCD o ERROR.

El bloque Display tiene la funcin de mostrar el nmero BCD.

Figura 1.- Diagrama de bloques del sistema digital detector BCD

3. DIAGRAMA ASM

Figura2.- Diagrama ASM del sistema DETECTOR BCD

El diagrama ASM mostrado en la figura 2 es el diagrama de flujo del bloque

controlador mostrado en la figura 1. Existen 7 estados, etiquetados como Ta, Tb, Tc,

Td, Te, Tf, Tg, Th. El primer estado Ta encera el registro y el contador de cuatro bits.

Una vez que se presiona START pasamos al siguiente estado Tb; si dejamos de

presionar avanzamos al estado Tc.

En el estado Tc, si presionamos STOP nos vamos al siguiente estado Td; sino s,

presionamos ingresar habilitamos en contador (EnC) y el registro (EnR1) para cargar

un bit. Y as se cargaran bits y aumentara el contador hasta que el usuario presione

STOP.

6

Cuando estamos en el estado Td, analizamos si el dato ingresado es un nmero

BCD. Entonces, primero preguntamos si el nmero se ingreso ms de cuatro veces

(4) y si esto es verdadero vamos al estado Te y mostramos ERROR. Si es falso,

preguntamos si el nmero es mayor que nueve (Data>9), si es verdadero

nuevamente nos vamos al estado Te y mostramos ERROR; pero, si es falso nos

dirigimos al estado Tf y activamos la salida BCD, que indica que el nmero

ingresado es BCD.

En el estado de ERROR y en el estado BCD, pasa salir de este estado y regresar al

estado inicial hay que presionar y soltar el botn START.

4. DIAGRAMA DE TIEMPO

Salida BCD activada

Figura 3.- Diagrama de tiempo mostrando la salida error

Las seales internas contador y registro mostrados en la figura 3 nos ayudaran a

saber el nmero de veces que ingreso el dato y el dato de cuatro bits cargado. Una

vez ingresado el dato, el sistema analiza el dato siempre y cuando el usuario

presione STOP. El usuario ingreso exactamente cuatro bits y el nmero cargado es

tres en binario 0011. El controlador muestra la salida BCD que indica que el

nmero es un BCD. Data_out es la salida de 7 bits del decodificador de 7

segmentos.

La figura 4 muestra la salida de ERROR activada. Vemos que despus de presionar

el botn stop, el nmero cargado es 11 en binario 1011. El nmero 11 no

representa un nmero BCD, y por lo tanto muestra la salida ERROR.

7

Salida ERROR activada

Figura 4.- Diagrama de tiempo mostrando la salida BCD

5. DIAGRAMA ESQUEMATICO

La figura muestra el diagrama esquemtico con todas las interconexiones y sus

respectivos nombres. Los componentes utilizados son los siguientes

Controlador

Divisor de Frecuencia

Antirebote

Decodificador de 7 segmentos

Comparadores

Display de 7 segmentos

Puertas lgicas

Descripcin de las terminales ms importantes

EnC.- Habilita al Contador para que cuente el nmero de bit ingresado

EnR1.- Habilita el registro para que se cargue un bit y realice el desplazamiento

DATO.- Bit a ingresar para formar el nmero BCD

BCD.- Salida de un bit que indica si el nmero ingresado es BCD.

ERROR.- Salida de un bit que indica si el nmero ingresado es no es BCD.

DATA[3..0].- Seal interna utilizada para mostrar el valor cargado en el registro de

desplazamiento.

COUNT[3..0].- Seal interna utilizada para mostrar el nmero de datos bits ingresado

por el usuario.

DiferDe4.- Seal que indica si ingreso ms de cuatro bits o menos de cuatro bits

DataMay9.- Seal que indica si el numero ingresado en mayor que nueve

8

6. DESCRIPCION VHDL

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity DetectorCodigoBCD is

port( clock, resetn: in std_logic;

start, DATOS, mostrar, ingresar, stop: in std_logic;

activ_disp: out std_logic;

error,bcd: out std_logic;

data_out: out std_logic_vector(0 to 6));

end detectorCodigoBCD;

architecture comportamiento of DetectorCodigoBCD is

--*****COMPONENTES*****--

component ANTIREBOTE

port(PB_N, CLOCK_100Hz : IN STD_LOGIC;

PB_SIN_REBOTE : OUT STD_LOGIC);

END component;

component clock_div

port

(CLOCK_50MHz :IN STD_LOGIC;

CLOCK_1MHz :OUT STD_LOGIC;

CLOCK_100KHz :OUT STD_LOGIC;

CLOCK_10KHz :OUT STD_LOGIC;

CLOCK_1KHz :OUT STD_LOGIC;

CLOCK_100Hz :OUT STD_LOGIC;

CLOCK_10Hz :OUT STD_LOGIC;

CLOCK_1Hz :OUT STD_LOGIC);

end component;

component contador_up

port(clock,resetn,enable: in std_logic; --enable: entrada de habilitacion

Q : out std_logic_vector(3 downto 0));

end component;

component reg_iz_der

port(R,Resetn,Clock, enable: in std_logic;

Q: out std_logic_vector(3 downto 0));

end component;

component DEC_DR_N

port( BCD : in std_logic_vector(3 downto 0);

10

SEG7 : out std_logic_vector(0 to 6));

end component;

type estado is (Ta, Tb, Tc, Td, Te, Tf, Tg, Th);

signal y: estado;

signal Vcc, EnR1, EnC, DiferDe4,dataMay9, prende: std_logic;

signal data,count, nueve, cuatro: std_logic_vector(3 downto 0);

signal start1, datos1, mostrar1, ingresar1, stop1: std_logic; -- salidas de

antirebotes

signal clk1, clk2, clk3, clk4, clk5, clk6, clk7: std_logic; -- salida de reloj

CLOCk_div

--*****CONTROLADOR*****--

begin

mss_transiciones: process(resetn, clk7, ingresar, mostrar)

begin

if resetn='0' then y<=Ta;

elsif (clk1'event and clk1='1') then

case y is

when Ta => if start='0' then y<=Ta; else y<=Tb; end if;

when Tb => if start='1' then y<=Tb; else y<=Tc; end if;

when Tc => if stop='0' then y<=Tc; else y<=Td; end if;

when Td => if diferDe4='1' then y<=Te; elsif dataMay9='1' then

y<=Te; else y<=Tf ; end if;

when Te => if start='0' then y<=Te; else y<=Tg; end if;

when Tg => if start='1' then y<=Tg; else y<=Ta; end if;

when Tf => if start='0' then y<=Tf; else y<=Th; end if;

when Th => if start='1' then y<=Th; else y<=Ta; end if;

end case;

end if;

end process;

mss_salidas: process(y, stop, ingresar, start, mostrar)

begin

EnR1<='0'; EnC<='0'; Error<='0'; BCD<='0'; prende<='0';

case y is

when Ta =>

when Tb =>

when Tc => if stop='0' and ingresar='1' then EnR1<='1'; EnC<='1';

else EnR1<='0'; EnC<='0'; end if;

when Td =>

when Te => Error<='1';

when Tg =>

when Tf => BCD<='1'; if start='0' and mostrar='1' then prende<='1';

end if;

when Th =>

end case;

end process;

11

--*****PROCESADOR DE DATOS*****--

Vcc<='1';

nueve<="1001";

Cuatro<="0100";

RELOJ: clock_div port map (clock, clk1, clk2, clk3, clk4, clk5, clk6, clk7);

reg_id: reg_iz_der port map(Datos, resetn, clk6, EnR1, data);

contador: contador_up port map(clk6, resetn, EnC, count);

decoder: dec_DR_N port map (data, data_out);

DataMay9<='1' when (Data > Nueve) else '0';

DiferDe4<='1' when ((Count > cuatro) or (Count < cuatro)) else '0';

activ_disp<='1' when (prende = Vcc) else '0';

end comportamiento;

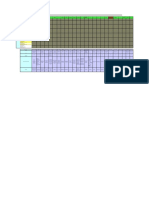

7. REPORTE SOBRE APROVECHAMIENTO

Figura 5.- Captura de pantalla del reporte de compilacin

La figura 5 muestra un reporte general del aprovechamiento de la tarjeta DE0NANO

EP4CE22. Se utilizaron 17 pines de los 154 existentes. Memoria total ocupada en

bits: 5248 (menos del 1%)

12

8. CONCLUSIONES

En resumen, el proyecto DETECTOR BCD se realiz utilizando una

herramienta importante para simular sistemas digitales. Esta herramienta es

Quartus 13.0, por medio de la cual pudimos describir nuestro proyecto de

forma ESTRUCTURAL; en pocas palabras, se escribi todo el proyecto en

lneas de cdigo.

Pudimos darnos cuenta de la dificultad de realizar el proyecto realizando

descripcin estructural, comparado con la construccin de bloques utilizando

el diagrama esquemtico. La dificultad de la descripcin estructural reside en

la interconexin de las terminales de cada componente con otros, lo que no

sucede en la construccin de bloques.

Finalmente, pudimos terminar con xito este proyecto, realizando su anlisis,

la programacin y la implementacin del mismo. Para la implementacin

fsica, se utiliz la tarjeta De0 NANO EP4CE22F17. Cabe destacar que

afianzamos los conocimientos aprendidos en las clases tericas de Sistemas

digitales I y II.

9. RECOMENDACIONES

Fijar el bus de datos nos ayudar a que no existan desconexiones o falsos

contactos; adems, es importante utilizar el cable adecuado para la conexin

de pines del cable de bus de datos con el protoboard. As que si preferimos

utilizar cables rgidos, tomar en cuenta que estos puedes romperse y

producir grandes retrasos a la hora de encontrar el fallo.

Cabe destacar la importancia de conocer las especificaciones de

funcionamiento de los elementos electrnicos a utilizar en nuestro proyecto.

Tales como diodos, pulsadores, resistencia y sus cdigos de colores,

switches y sobre todo el display de 7 segmentos.

Al utilizar la tarjeta DE0 NANO debemos ser cuidadosos con la misma, las

cargas estticas presentes en nuestro cuerpo pueden averiar o daar los

chips y circuitos integrados. Estos dispositivos son sensibles a las cargas

estticas.

13

10. BIBLIOGRAFA

Sistemas digitales, A. Lloris y A. Prieto y L. Parrilla, McGraw Hill,

Madrid 2003.

Fundamentos de sistemas digitales, (7 edicin), Floyd T. L., Prentice

Hall, Madrid 2003.

Principios de Diseo Digital, D.D. Gajski, Prentice Internacional INC.,

1997.

Diseo Digital. Principios y Prcticas, J. F. Wakerly, Prentice

Internacional INC., 2001.

Fundamentos fsicos y tecnolgicos de la informtica, P. Gmez, V.

Nieto, A. lvarez y R. Martnez, Pearson Prentice Hall, Madrid 2006.

También podría gustarte

- CachéDocumento4 páginasCachéAlma PartidaAún no hay calificaciones

- 2019-09-19-195321-94 Diseño de Maquinas ASMDocumento87 páginas2019-09-19-195321-94 Diseño de Maquinas ASMLeonardo CastilloAún no hay calificaciones

- Metodo de EulerDocumento4 páginasMetodo de EulerRolando ChangoAún no hay calificaciones

- Cueva - Las Estructuras Precapitalistas, Antesala Del Subdesarrollo - Cap 1 PDFDocumento22 páginasCueva - Las Estructuras Precapitalistas, Antesala Del Subdesarrollo - Cap 1 PDFRicardo Sandoval ArtemioAún no hay calificaciones

- Sistema de Automatizacion S7 200Documento478 páginasSistema de Automatizacion S7 200Jhonny Zambrano SaavedraAún no hay calificaciones

- Reloj DigitalDocumento6 páginasReloj DigitalJosé Alberto GarcíaAún no hay calificaciones

- Simulador de 8085Documento63 páginasSimulador de 8085Juan Antonio100% (1)

- Margen de FaseDocumento5 páginasMargen de FaseJheyson Chuquispuma MagallanesAún no hay calificaciones

- Equipo 2 PWM PDFDocumento8 páginasEquipo 2 PWM PDFJavier AguilarAún no hay calificaciones

- Teoría de Control II - Problemas y soluciones de simplificación de diagramas de bloques y obtención de modelos en el espacio de estadosDocumento7 páginasTeoría de Control II - Problemas y soluciones de simplificación de diagramas de bloques y obtención de modelos en el espacio de estadosMauri VasquezAún no hay calificaciones

- Unidad Vi. Aritmética Digital. Operaciones y CircuitosDocumento2 páginasUnidad Vi. Aritmética Digital. Operaciones y CircuitosGeiner C. MatosAún no hay calificaciones

- Clase 6 Unidad 2 Modelo de Espacio de EstadoDocumento4 páginasClase 6 Unidad 2 Modelo de Espacio de EstadoMilton VariosAún no hay calificaciones

- Humanidades VDocumento8 páginasHumanidades VUlises Palma MartinezAún no hay calificaciones

- Control OptimoDocumento11 páginasControl OptimoRonyVargasAún no hay calificaciones

- UNIDAD 8 - Sistema de Transmisión de InformaciónDocumento24 páginasUNIDAD 8 - Sistema de Transmisión de Informaciónmuchutti100% (1)

- Circuitos IntegradosDocumento17 páginasCircuitos IntegradosGeraldine K. Valencia MenaAún no hay calificaciones

- Integración Con El Sistema OperativoDocumento11 páginasIntegración Con El Sistema OperativoJesusAún no hay calificaciones

- Ensayo Sobre Logica SecuenciaDocumento21 páginasEnsayo Sobre Logica SecuenciaLuis Enrique Huh PucAún no hay calificaciones

- Informe PenduloDocumento11 páginasInforme PenduloTelmo GuamanAún no hay calificaciones

- Transistor en corte y saturaciónDocumento3 páginasTransistor en corte y saturaciónHéctor Suarez VillalobosAún no hay calificaciones

- Compuertas LogicasDocumento27 páginasCompuertas Logicaszzzxxx666Aún no hay calificaciones

- Contador de Carrera Libre de 4 BitsDocumento2 páginasContador de Carrera Libre de 4 Bitsnert45Aún no hay calificaciones

- Práctica Timers CountersDocumento12 páginasPráctica Timers CountersZab VazquezAún no hay calificaciones

- AnÁlisis y DiseÑo de Circuitos SecuencialesDocumento32 páginasAnÁlisis y DiseÑo de Circuitos SecuencialesOscar Salazar0% (1)

- Comunicacion Matlab-ArduinoDocumento4 páginasComunicacion Matlab-ArduinoRichard ArturoAún no hay calificaciones

- LabVIEW para programación de FPGA Spartan-3EDocumento4 páginasLabVIEW para programación de FPGA Spartan-3EVictoria YánezAún no hay calificaciones

- Operaciones Con BitsDocumento10 páginasOperaciones Con BitspatriciomelendesAún no hay calificaciones

- Impedancia de Circuitos RC y RLDocumento7 páginasImpedancia de Circuitos RC y RLElnatan Torres GonzalezAún no hay calificaciones

- Máquinas de estado finito (FSM) y su modelado con VHDLDocumento77 páginasMáquinas de estado finito (FSM) y su modelado con VHDLDiegoGuzmanAún no hay calificaciones

- 1.2. Clasificacion de SeñalesDocumento27 páginas1.2. Clasificacion de SeñalesLeonardo GarciaAún no hay calificaciones

- Programacion Estructurada PDFDocumento47 páginasProgramacion Estructurada PDFMiguel Dextre100% (1)

- Circuito Muest ReoDocumento3 páginasCircuito Muest ReodaygonAún no hay calificaciones

- Obtener FOH para variables de estado Matlab 2016Documento3 páginasObtener FOH para variables de estado Matlab 2016JAIRO ALEJANDRO CHICAIZA SANGURIMAAún no hay calificaciones

- La Importancia de La Ingenieria para El Futuro de MexicoDocumento5 páginasLa Importancia de La Ingenieria para El Futuro de MexicoArturo Muñoz0% (1)

- Aplicaciones de Circuitos DigitalesDocumento19 páginasAplicaciones de Circuitos DigitalesHernanValencia0% (1)

- Innforme Practica VHDL ALUDocumento13 páginasInnforme Practica VHDL ALUNatalia_meneses8Aún no hay calificaciones

- Procesos ErgódicosDocumento3 páginasProcesos ErgódicosEmily Tobar100% (2)

- El Humanismo Frente A La GlobalizaciónDocumento10 páginasEl Humanismo Frente A La GlobalizaciónNormanAún no hay calificaciones

- Ensayo de Sistemas DigitalesDocumento7 páginasEnsayo de Sistemas DigitalesIgnacio Moreno0% (1)

- Biestable DDocumento2 páginasBiestable DfcojcgAún no hay calificaciones

- Practica 5 (Amplificador Emisor Comun)Documento20 páginasPractica 5 (Amplificador Emisor Comun)Marcos PalaciosAún no hay calificaciones

- Puente H Transistores y MosfetDocumento15 páginasPuente H Transistores y Mosfetblargimded100% (1)

- Sobrecarga de Operadores - ProgramacionDocumento43 páginasSobrecarga de Operadores - Programacionvitevo56Aún no hay calificaciones

- Capacitores e InductoresDocumento58 páginasCapacitores e InductoresBrisman Ricardo Palacin VargasAún no hay calificaciones

- Practica 4de ErasmoDocumento8 páginasPractica 4de ErasmoSamantha GaliciaAún no hay calificaciones

- Manual de prácticas de Física de SemiconductoresDocumento38 páginasManual de prácticas de Física de SemiconductoresricardodeleonbarrazaAún no hay calificaciones

- Laboratorio n4 de Sumador Multiplexor y DemultiplexorDocumento11 páginasLaboratorio n4 de Sumador Multiplexor y DemultiplexorSantos Zosimo Ocas GoicocheaAún no hay calificaciones

- Tutorial para Instalar WincuplDocumento8 páginasTutorial para Instalar WincuplAlfonsoAún no hay calificaciones

- Practica 1 - Unidad 1 Arquitectura de ComputadorasDocumento23 páginasPractica 1 - Unidad 1 Arquitectura de Computadorasjuan pabloAún no hay calificaciones

- Sincronizacion y Multiplexaje.pDocumento11 páginasSincronizacion y Multiplexaje.pLaura Itzel MoralesAún no hay calificaciones

- Fundamentos de sistemas digitalesDocumento21 páginasFundamentos de sistemas digitalesJesus Francisco Diaz AlvaradoAún no hay calificaciones

- Reguladores de Voltaje Integrados y Op AmpDocumento26 páginasReguladores de Voltaje Integrados y Op AmpManuel Jesus Nuñez DAún no hay calificaciones

- Pasos para Conversion Con InterrupcionDocumento6 páginasPasos para Conversion Con Interrupcionfede_sobAún no hay calificaciones

- Construcción de un flip-flop RS con transistores 2N2222Documento9 páginasConstrucción de un flip-flop RS con transistores 2N2222Oscar Alvarez BarrosoAún no hay calificaciones

- Trabajo de VHDLDocumento7 páginasTrabajo de VHDLAlfonso Agama Chico0% (1)

- Barrido de 4 displays 7 segmentos mediante multiplicación de números binarios ingresados por puertosDocumento7 páginasBarrido de 4 displays 7 segmentos mediante multiplicación de números binarios ingresados por puertosFaustoPolancoAriasAún no hay calificaciones

- Sumadora DigitalDocumento18 páginasSumadora Digitaltongers23Aún no hay calificaciones

- Tarea5. Contador 0-99Documento8 páginasTarea5. Contador 0-99Roberto Carlos Barragán Campos100% (1)

- Decodificadores TrabajoDocumento12 páginasDecodificadores TrabajoO7EROAún no hay calificaciones

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- Inter-Beam InterferenceDocumento6 páginasInter-Beam InterferenceKevin ArteagaAún no hay calificaciones

- PROYECTO EmprendimientoDocumento51 páginasPROYECTO EmprendimientoKevin ArteagaAún no hay calificaciones

- Práctica 1Documento12 páginasPráctica 1Kevin ArteagaAún no hay calificaciones

- Algebra LinealDocumento4 páginasAlgebra LinealKevin ArteagaAún no hay calificaciones

- Iniciacion Soldadura Con Estano PDFDocumento10 páginasIniciacion Soldadura Con Estano PDFdiditempuAún no hay calificaciones

- Servicio Movil AvanzadoDocumento1 páginaServicio Movil AvanzadoKevin ArteagaAún no hay calificaciones

- Práctica 10Documento12 páginasPráctica 10Kevin ArteagaAún no hay calificaciones

- Transgenerador Magnético - AbstractoDocumento1 páginaTransgenerador Magnético - AbstractoKevin ArteagaAún no hay calificaciones

- 8 Consejos para Que No Te Sientas FatigadoDocumento3 páginas8 Consejos para Que No Te Sientas FatigadoKevin ArteagaAún no hay calificaciones

- Calificación Del Estudiantado para El Servicio Bibliotecario de La ESPOL - Proyecto de Estadística (1er Parcial) .Documento77 páginasCalificación Del Estudiantado para El Servicio Bibliotecario de La ESPOL - Proyecto de Estadística (1er Parcial) .Kevin Arteaga100% (1)

- Sistemas Numéricos y Códigos. Sistemas Digitales IDocumento42 páginasSistemas Numéricos y Códigos. Sistemas Digitales IKevin ArteagaAún no hay calificaciones

- Diodo y Diodo ZenerDocumento8 páginasDiodo y Diodo ZenerKevin ArteagaAún no hay calificaciones

- Reglas de LaboratorioDocumento2 páginasReglas de LaboratorioKevin ArteagaAún no hay calificaciones

- Diodo y Diodo ZenerDocumento8 páginasDiodo y Diodo ZenerKevin ArteagaAún no hay calificaciones

- Análisis y Detección de Objetos de Primer Plano en Secuencias de VideoDocumento76 páginasAnálisis y Detección de Objetos de Primer Plano en Secuencias de VideoKevin ArteagaAún no hay calificaciones

- ELECTRIZACIONDocumento10 páginasELECTRIZACIONKevin ArteagaAún no hay calificaciones

- Aplicaciones Médicas de La BionanotecnologíaDocumento3 páginasAplicaciones Médicas de La BionanotecnologíaKevin ArteagaAún no hay calificaciones

- 25 Duelo en Padres Que Han Perdido HijosDocumento43 páginas25 Duelo en Padres Que Han Perdido HijospqnenukaAún no hay calificaciones

- Acercamiento A Los Modelos de La EADocumento17 páginasAcercamiento A Los Modelos de La EAJosé Luis Roque PAún no hay calificaciones

- Orígenes y evolución del español a través de las etimologías latinasDocumento2 páginasOrígenes y evolución del español a través de las etimologías latinasPaola GonzálezAún no hay calificaciones

- DisponibilidadDocumento6 páginasDisponibilidadVan HohenheimAún no hay calificaciones

- Ejercicios Eteres y Ac. CarboxilicoDocumento3 páginasEjercicios Eteres y Ac. CarboxilicoKarola PreciosisimaAún no hay calificaciones

- El Coloquio Con Juan Ramón Jiménez de Lezama LimaDocumento23 páginasEl Coloquio Con Juan Ramón Jiménez de Lezama LimaIrán VázquezAún no hay calificaciones

- Libros de La Biblia - SandoyaDocumento1 páginaLibros de La Biblia - SandoyaAaromIsaíOchoaBernabéAún no hay calificaciones

- Diseño de Canal RicaurteDocumento14 páginasDiseño de Canal RicaurteLorena K HernándezAún no hay calificaciones

- Lectura Marco Teorico Metodologico Variables OperacionalizacionDocumento12 páginasLectura Marco Teorico Metodologico Variables OperacionalizacionJesús Dionisio Huarcaya JesúsAún no hay calificaciones

- Matematica Financiera Dubraska PerezDocumento2 páginasMatematica Financiera Dubraska Perezelpro25Aún no hay calificaciones

- El Gran Chasco Los Guiaba Dios Aun Estando EquivocadosDocumento29 páginasEl Gran Chasco Los Guiaba Dios Aun Estando EquivocadosElizabeth CamposAún no hay calificaciones

- Sesión 4 - Competencia ComunicativaDocumento20 páginasSesión 4 - Competencia Comunicativa¡Oolong en CalzonesAún no hay calificaciones

- INVESTIGACION DE ACCIDENTE DE TRABAJO (Trabajo de Campo) AlturasDocumento25 páginasINVESTIGACION DE ACCIDENTE DE TRABAJO (Trabajo de Campo) AlturasAna Maria HernandezAún no hay calificaciones

- Investigación de La Desviación de Resultados MicrobiológicosDocumento39 páginasInvestigación de La Desviación de Resultados MicrobiológicosSolutam MoraleAún no hay calificaciones

- Alicia Misrahi - Los Poderes de VenusDocumento375 páginasAlicia Misrahi - Los Poderes de VenusMirtha Euridice Rodriguez UrbinaAún no hay calificaciones

- Dia 2 EscribirDocumento4 páginasDia 2 EscribirCarla ValdiviaAún no hay calificaciones

- Casos PracticoDocumento2 páginasCasos PracticoCindy Milagro Zelaya Gutiérrez0% (1)

- NeumococoDocumento10 páginasNeumococoJhon Darwin Sánchez VásquezAún no hay calificaciones

- QUIJANO, ANIBAL - Colonialidad Del Poder, Eurocentrismo y América LatinaDocumento31 páginasQUIJANO, ANIBAL - Colonialidad Del Poder, Eurocentrismo y América LatinaNadia NavarroAún no hay calificaciones

- Matriz Rura de InduccionDocumento1 páginaMatriz Rura de InduccionlinaAún no hay calificaciones

- Guia Nivel Avanzado Trabajo PrácticoDocumento7 páginasGuia Nivel Avanzado Trabajo PrácticoROCIO LEONAún no hay calificaciones

- Tutela a novillero por restricción de agremiaciónDocumento3 páginasTutela a novillero por restricción de agremiaciónAna CoronelAún no hay calificaciones

- Comun - 3ºDocumento4 páginasComun - 3ºDenisse PortilloAún no hay calificaciones

- 9-Intoxicacion Por CausticosDocumento57 páginas9-Intoxicacion Por CausticosJuan Martin Perez GrilloAún no hay calificaciones

- Libro - 2do Parcial LEOYE II PDFDocumento32 páginasLibro - 2do Parcial LEOYE II PDFaguila suarezAún no hay calificaciones

- Delito Imperfecto o TentativaDocumento7 páginasDelito Imperfecto o TentativaCinthia LastraAún no hay calificaciones

- Dones EspiritualesDocumento5 páginasDones EspiritualesArmas San Juan Christopher EduardoAún no hay calificaciones

- PigCHAMP Articulos - NodrizasDocumento3 páginasPigCHAMP Articulos - NodrizasPigCHAMP_Pro_EuropaAún no hay calificaciones

- Estilo de Vida IgjDocumento4 páginasEstilo de Vida Igjgenesis acostaAún no hay calificaciones

- Modelo Del Cerebro TriunoDocumento9 páginasModelo Del Cerebro TriunoRicardo RanalliAún no hay calificaciones