Documentos de Académico

Documentos de Profesional

Documentos de Cultura

VLSI Engineer Seeking Circuit Design Roles

Cargado por

Sai Raghu0 calificaciones0% encontró este documento útil (0 votos)

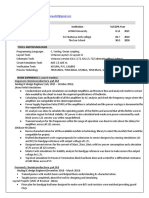

79 vistas2 páginasYerrpothu Gnana Sai Raghu is seeking a position as a VLSI engineer. He has an M.Tech in VLSI system design from NIT Warangal with a CGPA of 8.31/10. He has a B.Tech in Electronics and Communication Engineering from Gudlavalleru Engineering college with a CGPA of 8.23/10. He has experience working with the EDA memory compiler IP team at Intel, developing and testing back-end collaterals and an automated RTL2GDS flow. He has experience with various analog and digital circuit design projects using Cadence and other EDA tools.

Descripción original:

its my resume

Título original

Resume Ygsairaghu NitWarangal

Derechos de autor

© © All Rights Reserved

Formatos disponibles

PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoYerrpothu Gnana Sai Raghu is seeking a position as a VLSI engineer. He has an M.Tech in VLSI system design from NIT Warangal with a CGPA of 8.31/10. He has a B.Tech in Electronics and Communication Engineering from Gudlavalleru Engineering college with a CGPA of 8.23/10. He has experience working with the EDA memory compiler IP team at Intel, developing and testing back-end collaterals and an automated RTL2GDS flow. He has experience with various analog and digital circuit design projects using Cadence and other EDA tools.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

79 vistas2 páginasVLSI Engineer Seeking Circuit Design Roles

Cargado por

Sai RaghuYerrpothu Gnana Sai Raghu is seeking a position as a VLSI engineer. He has an M.Tech in VLSI system design from NIT Warangal with a CGPA of 8.31/10. He has a B.Tech in Electronics and Communication Engineering from Gudlavalleru Engineering college with a CGPA of 8.23/10. He has experience working with the EDA memory compiler IP team at Intel, developing and testing back-end collaterals and an automated RTL2GDS flow. He has experience with various analog and digital circuit design projects using Cadence and other EDA tools.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Está en la página 1de 2

YERRAPOTHU GNANA SAI RAGHU

D.No:16/47,S.N.PURAM,GUDIVADA,KRISHNA DST,ANDHRA PRADESH

Pin Code: 521301, Mail ID: ygsairaghu@gmail.comCell No: +919886276852

Seeking for challenging opportunity as a Vlsi Engineer in the areas of Circuit Design, EDA

Software Development.

NIT Warangal, Andhra Pradesh ,India(2012 - 2014)

M.Tech VLSI system design CGPA:8.31/10(up to 2

nd

year.1

st

sem)

Gudlavalleru Engineering college, JNTUK, A.P , India(2008 - 2012)

Electronics and CommunicationEngineering CGPA:8.23/10

Internship INTEL, Bangalore, India

Working with the EDA memory compiler IP teamdeveloping and testing back end collaterals

generated by the tools.

Developed Automated RTL2GDS Flow for the IP validation.

Tool used are DC and ICC.

Device Modeling Mixed signal designing

Analog IC design Low power circuit designing

Digital IC design RF IC design

VLSI-DSP Architectures Physical design automation

Micro chip Fabrication

Techniques(MCFT)

Testing and Testability

CMOS Flash ADC

High speed low power FoldingADC with two types of comparators are used.

Specifications: 8 bit, Maximum frequency =1.8Ghz,Pmax=590mW.

Tool: Cadence Virtuoso, 180nmTechnology

CMOS Pipeline ADC

The converter is optimized for low-voltage low-power applications by applying an

optimum stage-scaling algorithm at the architectural level and an op-amp and comparator

sharing technique at the circuit level.

Specifications: 10bit, 12MS/s with SNR 68db and DNL .67LSB

Tool: Cadence Virtuoso, 180nm Technology

Low voltage Low power comparator

By using positive feedback technique and by making quiescent current zero power

Consumption is reduced

Specifications: Sampling frequency=1.4Ghz, Resolvingcapability=.1uv, Supply

voltage range: (0.8 to 1.2) v, Pmax=5.8mW.

Tool: Cadence Virtuoso, 180nm Technology

Fully compensated OP-AMP with biasing technique independent of temperature

Specifications: Gain =100db, UGB =10MHz, Phase Margin =87

Tool: Cadence Virtuoso, 180nm Technology

Objective

Education

Graduate

Courses

Academic

Projects

Experience

Design of high gain comparator

Specifications: Sampling frequency=100Mhz,Resolving capability=0.1mv

Tool: Tanner 2m

Implementation of Recursive Least square algorithm for adaptive filter

TheRecursive least squares (RLS) adaptive filter is analgorithmwhich

recursively finds the filter coefficients that minimize a weightedlinear least

squarescost functionrelating to the input signals.

AUTONOMOUS ROVING ROBOT FOR GREENHOUSE CONTROLLING

Because of the different materials in the greenhouse the temperature and light

distribution is not uniform. In order to maintain the temperature and light

uniformly this robot is used.This consists of temperature & light monitoring and

controlling. This unit is installed on a Robot which moves throughthe

greenhouseon a predefined track.

Programming Languages: C, PERL , TCL

Application Software: Tanner, cadence (virtuoso), Design Compiler, IC compiler,

Xilinx

HDL: Verilog, VHDL.

Got Intel Goodie drawer level-II award 4 times during internship.

Secured GATE rank of 559

One among the University Toppers in B.Tech.

Winner of the Merit Cash Award in B. Tech. for subsequent years 2008-2010.

Member of the elite IEEE in B.Tech.

Software

Skills

Academic

Achievements

También podría gustarte

- 233170581-Resume-Ygsairaghu-NitWarangalDocumento2 páginas233170581-Resume-Ygsairaghu-NitWarangalanshuman27.svnitAún no hay calificaciones

- Arjun Singh Senior Software EngineerDocumento3 páginasArjun Singh Senior Software EngineerErArjun Singh SisodiyaAún no hay calificaciones

- 16900121194Documento4 páginas16900121194suvamsarma67Aún no hay calificaciones

- Anum Ahmed Pirkani UkDocumento5 páginasAnum Ahmed Pirkani UkAnum AhmedAún no hay calificaciones

- Using FPGA For Remotely Controlling The Industrial Devices Against Environmental Hazards and Streetlight Illumination 2Documento4 páginasUsing FPGA For Remotely Controlling The Industrial Devices Against Environmental Hazards and Streetlight Illumination 2International Journal of Innovative Science and Research TechnologyAún no hay calificaciones

- ART20172334Documento4 páginasART20172334alfaristelecomAún no hay calificaciones

- List of Electronics Equipment For: Specifications For Items To Be PurchasedDocumento8 páginasList of Electronics Equipment For: Specifications For Items To Be PurchasedKrishan Gopal ShankhdharAún no hay calificaciones

- LIDAR Lite Laser DatasheetDocumento2 páginasLIDAR Lite Laser DatasheetCruz Manuel PerezAún no hay calificaciones

- LIDAR Lite Data SheetDocumento2 páginasLIDAR Lite Data SheetDragomirescu AlinaAún no hay calificaciones

- IOT Based Colour Skittle Sorting MachineDocumento22 páginasIOT Based Colour Skittle Sorting MachineAbhishek MohiteAún no hay calificaciones

- Major Project Stage-1Documento23 páginasMajor Project Stage-1Priya GadirajuAún no hay calificaciones

- IEEE VLSI Projects for StudentsDocumento5 páginasIEEE VLSI Projects for StudentsNamrathaAún no hay calificaciones

- Basit Mahmood: ObjectiveDocumento2 páginasBasit Mahmood: ObjectivebasitAún no hay calificaciones

- Sradha M (RESUME) - QualcommDocumento1 páginaSradha M (RESUME) - Qualcommskrxbbr7nhAún no hay calificaciones

- Ec6511 DSP Lab ManualDocumento156 páginasEc6511 DSP Lab Manualramadossapece100% (5)

- Advanced Solar Array SimulatorDocumento10 páginasAdvanced Solar Array SimulatorDeepthi RamadasAún no hay calificaciones

- Design and Analysis of Two-Stage OP-AMP in 180nm and 45nm TechnologyDocumento5 páginasDesign and Analysis of Two-Stage OP-AMP in 180nm and 45nm TechnologyNam Luu Nguyen NhatAún no hay calificaciones

- Mounika's Resume - Analog IC Design EngineerDocumento3 páginasMounika's Resume - Analog IC Design Engineermounika morampudiAún no hay calificaciones

- M.Tech VLSI & ES seeking position in organizationDocumento3 páginasM.Tech VLSI & ES seeking position in organizationNitin MathurAún no hay calificaciones

- Low-Cost Hybrid Multimeter for Testing and TroubleshootingDocumento5 páginasLow-Cost Hybrid Multimeter for Testing and TroubleshootingLin DanAún no hay calificaciones

- HA030686 Iss9 Nanodac Data SheetDocumento8 páginasHA030686 Iss9 Nanodac Data SheetRavi Kant GuptaAún no hay calificaciones

- Rajarathinam ResumeDocumento5 páginasRajarathinam ResumeManickavel SmsAún no hay calificaciones

- Session 3 Amplifiers and OscillatorsDocumento29 páginasSession 3 Amplifiers and Oscillators吴川斌Aún no hay calificaciones

- Project ReportDocumento66 páginasProject ReportKashikaJunejaAún no hay calificaciones

- Wireless Remote Controlled Linear Actuator LampDocumento5 páginasWireless Remote Controlled Linear Actuator LampIJRASETPublicationsAún no hay calificaciones

- Juttuka Bhaskara Rao 2022 Resume (3) - 1Documento6 páginasJuttuka Bhaskara Rao 2022 Resume (3) - 1Kunal KulkarniAún no hay calificaciones

- Infrared Receiver + NEC Coding Remote Control MaterialsDocumento6 páginasInfrared Receiver + NEC Coding Remote Control MaterialsAdam MikitzelAún no hay calificaciones

- Touch Screen and Zigbee Based Library Automation UsingDocumento37 páginasTouch Screen and Zigbee Based Library Automation UsingKushala KushiAún no hay calificaciones

- E Lab Access Using Wireless Sensor TechnologyDocumento5 páginasE Lab Access Using Wireless Sensor TechnologyEditor IJRITCCAún no hay calificaciones

- Dhanraj.p M.tech (VLSI) 2011Documento4 páginasDhanraj.p M.tech (VLSI) 2011Venkate GowdaAún no hay calificaciones

- Highlight HPC168 Passenger Counter HardwareDocumento10 páginasHighlight HPC168 Passenger Counter HardwareItsJiOAún no hay calificaciones

- Mani ResumeDocumento4 páginasMani ResumeDurairajan AasaithambaiAún no hay calificaciones

- Babu 2014Documento5 páginasBabu 2014PRINKLEAún no hay calificaciones

- Digital Pulse ProcessingDocumento5 páginasDigital Pulse ProcessingNishant SinghAún no hay calificaciones

- Wireless Sensor Network of 3 - Bit ADCDocumento6 páginasWireless Sensor Network of 3 - Bit ADCAnonymous izrFWiQAún no hay calificaciones

- Home Automation Using LabviewDocumento4 páginasHome Automation Using LabviewIJSTEAún no hay calificaciones

- Low-Cost FPGA Based Antenna Pattern Measurement SystemDocumento4 páginasLow-Cost FPGA Based Antenna Pattern Measurement SystemErkut YumrukayaAún no hay calificaciones

- Analog To Digital ConverterDocumento14 páginasAnalog To Digital Converterparth bhardwajAún no hay calificaciones

- Automatic Toll CollectionDocumento27 páginasAutomatic Toll CollectionRakibul HassanAún no hay calificaciones

- Embedded SW Engineer - Anitha YalaDocumento6 páginasEmbedded SW Engineer - Anitha YalaAnitha YalaAún no hay calificaciones

- TDM Pulse Code Modulation Transmitter and Receiver Trainer ST2103 and ST2104 LearningDocumento98 páginasTDM Pulse Code Modulation Transmitter and Receiver Trainer ST2103 and ST2104 Learningcharan_sgAún no hay calificaciones

- FFT Spectrum Analyzer Using Goertzel FilterDocumento6 páginasFFT Spectrum Analyzer Using Goertzel Filterdell911100% (1)

- Response of Cantilever Beam Under Free VibrationDocumento11 páginasResponse of Cantilever Beam Under Free VibrationPriyadarshini KrishnaswamyAún no hay calificaciones

- 90,96 SiiDocumento23 páginas90,96 SiizoamtoAún no hay calificaciones

- ECE Professional Anupriya MishraDocumento2 páginasECE Professional Anupriya MishraDivya srivastavaAún no hay calificaciones

- Intelligent Braking System Project ReportDocumento21 páginasIntelligent Braking System Project ReportMurugan MAún no hay calificaciones

- Flash ADC MidsemDocumento9 páginasFlash ADC MidsemBikashKumarMoharanaAún no hay calificaciones

- 813820112016-Mini ProjectDocumento5 páginas813820112016-Mini ProjectYokes WaranAún no hay calificaciones

- Model 2130 RBM Pro Machinery Analyzer: ConsultantDocumento4 páginasModel 2130 RBM Pro Machinery Analyzer: ConsultantdeepakaniAún no hay calificaciones

- Single Phase Differential Transformer Protection Using ArduinoDocumento4 páginasSingle Phase Differential Transformer Protection Using ArduinoHana AliAún no hay calificaciones

- Vanteddu Sai Kiran Reddy: Mtech Microelectronics at Iiit-AllahabadDocumento1 páginaVanteddu Sai Kiran Reddy: Mtech Microelectronics at Iiit-AllahabadSai Kiran Reddy VantedduAún no hay calificaciones

- A Review: High Speed Low Power Flash ADC: Rahul D. Marotkar, Dr. Manoj S. NagmodeDocumento4 páginasA Review: High Speed Low Power Flash ADC: Rahul D. Marotkar, Dr. Manoj S. NagmodeSunil PandeyAún no hay calificaciones

- Report SampleDocumento13 páginasReport SampleAbuzar KhanAún no hay calificaciones

- SR 92Documento18 páginasSR 92Harshith Gowda RAún no hay calificaciones

- Fast Multi Channel AnalyzerDocumento7 páginasFast Multi Channel AnalyzerDiana AndreiAún no hay calificaciones

- Final ReviewDocumento21 páginasFinal ReviewjyoshnaAún no hay calificaciones

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsDe EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsAún no hay calificaciones

- K S R T CDocumento2 páginasK S R T CSai RaghuAún no hay calificaciones

- Satheesh Kumar Muvvala: Date of Birth: 05 Aug 1991Documento5 páginasSatheesh Kumar Muvvala: Date of Birth: 05 Aug 1991Sai RaghuAún no hay calificaciones

- Steps To Success Manage Your Boss How To Build A Great Working Relationship CoverDocumento3 páginasSteps To Success Manage Your Boss How To Build A Great Working Relationship CoverSai RaghuAún no hay calificaciones

- Ranjan ResumeDocumento3 páginasRanjan ResumeSai RaghuAún no hay calificaciones

- COE 202: Digital Logic Design Memory and Programmable Logic DevicesDocumento25 páginasCOE 202: Digital Logic Design Memory and Programmable Logic DevicesSai RaghuAún no hay calificaciones

- Thesis 1Documento48 páginasThesis 1Sai RaghuAún no hay calificaciones

- Work Report On Project: Project title:RTL2GDS Automation For Hard IP'sDocumento3 páginasWork Report On Project: Project title:RTL2GDS Automation For Hard IP'sSai RaghuAún no hay calificaciones

- Rls MatlabDocumento3 páginasRls MatlabSai RaghuAún no hay calificaciones

- Need For High Speed I/O 01Documento6 páginasNeed For High Speed I/O 01Sai RaghuAún no hay calificaciones

- RF Energy HarvestingDocumento26 páginasRF Energy HarvestingSai Raghu100% (1)

- Ec8095-Vlsi Design-607796847-Ec 8095 NotesDocumento163 páginasEc8095-Vlsi Design-607796847-Ec 8095 Noteshmpudur1968Aún no hay calificaciones

- EI2203 EDC 2marksDocumento14 páginasEI2203 EDC 2marksBhanu KodaliAún no hay calificaciones

- Semiconductor KIA78R000F/PI KIA78R050F/PI: Technical DataDocumento11 páginasSemiconductor KIA78R000F/PI KIA78R050F/PI: Technical DataDarshana NissankaAún no hay calificaciones

- Ts-590s Service ManualDocumento162 páginasTs-590s Service ManualOK1PAAún no hay calificaciones

- ELL 100 Introduction To Electrical Engineering: L 8: N T S M P TDocumento71 páginasELL 100 Introduction To Electrical Engineering: L 8: N T S M P TSanchithya AriyawanshaAún no hay calificaciones

- Experiment 2 - Universal GatesDocumento6 páginasExperiment 2 - Universal GatesPrr PrrAún no hay calificaciones

- Mel G632 224Documento2 páginasMel G632 224Krishna KishoreAún no hay calificaciones

- EE471 Group#11 Lab#1Documento17 páginasEE471 Group#11 Lab#1Trần Ngọc HảiAún no hay calificaciones

- Datasheet IC 7473Documento6 páginasDatasheet IC 7473arif vereroAún no hay calificaciones

- RMS To DC Converters MT 081Documento4 páginasRMS To DC Converters MT 081Lyubomir Rumenov NedyalkovAún no hay calificaciones

- Decode 5 To 32Documento7 páginasDecode 5 To 32Doan Thanh ThienAún no hay calificaciones

- RF Microwave and Millimeter Wave IC Selection Guide 2017Documento56 páginasRF Microwave and Millimeter Wave IC Selection Guide 2017nboninaAún no hay calificaciones

- SEMIKRON DataSheet SKHI 21A R L5012520Documento1 páginaSEMIKRON DataSheet SKHI 21A R L5012520danielle1922 danAún no hay calificaciones

- 74HC4094Documento11 páginas74HC4094Gustavo BarcasnegrasAún no hay calificaciones

- WIX1003 Lab Report 12Documento17 páginasWIX1003 Lab Report 12shu minAún no hay calificaciones

- ECEN 2632 Chapter 3Documento5 páginasECEN 2632 Chapter 3tyutyuAún no hay calificaciones

- Ecen Lab 8 ReportDocumento6 páginasEcen Lab 8 Reportapi-241454978Aún no hay calificaciones

- Burt 2006Documento8 páginasBurt 2006Zhenyu YangAún no hay calificaciones

- AIM:-To Study The Adder & Subtractor Using 741. A PparatusDocumento65 páginasAIM:-To Study The Adder & Subtractor Using 741. A Pparatusvarunbunny199100% (2)

- 74HCT32Documento4 páginas74HCT32Horst MumpitzAún no hay calificaciones

- Mik 3842 Ad 1Documento10 páginasMik 3842 Ad 1Jovica PopovicAún no hay calificaciones

- Mesh AnalysisDocumento61 páginasMesh AnalysisKasani Tirumala tejaAún no hay calificaciones

- Basic Electronics For Beginners - Analogue Electronics and Microcontrollers ProjectsDocumento389 páginasBasic Electronics For Beginners - Analogue Electronics and Microcontrollers Projectsdavid flores83% (6)

- CCE 202: Circuit Analysis II Fall 2019-2020: American University of Science & Technology Faculty of EngineeringDocumento14 páginasCCE 202: Circuit Analysis II Fall 2019-2020: American University of Science & Technology Faculty of Engineeringmohamed yassinAún no hay calificaciones

- An HF 50-W Linear AmplifierDocumento8 páginasAn HF 50-W Linear AmplifierEdward Yanez100% (1)

- 1 Synchronization and Frequency Estimation Errors: 1.1 Doppler EffectsDocumento15 páginas1 Synchronization and Frequency Estimation Errors: 1.1 Doppler EffectsRajib MukherjeeAún no hay calificaciones

- Concept MapDocumento18 páginasConcept MapSriramAún no hay calificaciones

- Non-Isolated Buck Offline LED Driver Description FeaturesDocumento2 páginasNon-Isolated Buck Offline LED Driver Description FeaturesAlberto100% (1)

- Series & Parallel Resistance ExperimentsDocumento2 páginasSeries & Parallel Resistance ExperimentsNisa ElAún no hay calificaciones

- HW 1Documento9 páginasHW 1Kyto_oAún no hay calificaciones