Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Unidad 2 Completa

Cargado por

Courtney Hicks0 calificaciones0% encontró este documento útil (0 votos)

18 vistas20 páginasDerechos de autor

© © All Rights Reserved

Formatos disponibles

DOCX, PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOCX, PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

18 vistas20 páginasUnidad 2 Completa

Cargado por

Courtney HicksCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOCX, PDF, TXT o lea en línea desde Scribd

Está en la página 1de 20

Mauricio ya estn todos los temas aqu de la unidad 2 solo hay que acodarlos

Y a erick le falto meter algunas imgenes

UNIDAD II UNIDAD DE PROCESAMIENTO CENTRAL (CPU)

TEMA: UNIDAD DE PROCESAMIENTO CENTRAL (CPU)

Es el componente principal del ordenador y otros dispositivos programables, que interpreta las

instrucciones contenidas en los programas y procesa los datos. Las CPU proporcionan la

caracterstica fundamental del ordenador digital (la programabilidad) y son uno de los

componentes necesarios encontrados en los ordenadores de cualquier tiempo, junto con la

memoria principal y los dispositivos de entrada/salida. Se conoce como microprocesador el CPU

que es manufacturado con circuitos integrados.

UNIDAD ARITMTICA Y LGICA (ALU)

Realiza operaciones aritmticas (suma, resta, multiplica y divide), determina cuando un nmero

es positivo, negativo o cero; as mismo ejecuta y realiza operaciones lgicas (comparaciones,

conjunciones, disyunciones y negaciones)

CONTROL DE FLUJO

Control de flujo permite que los adaptadores para generar ni responde a las tramas, control de

flujo que ayudan a regular trfico de red. Control de flujo se configura en Opciones de rendimiento

Propiedades cuando Intel PROSet para el Administrador de dispositivos de Windows se instala.

Un interlocutor de enlace puede sobrecargarse si las tramas entrantes llegan ms rpido que el

dispositivo puede procesar. Las tramas se descartarn hasta que la condicin de sobrecarga

pasadas. El mecanismo de control de flujo soluciona este problema y elimina el riesgo de perder

tramas.

Si se produce una situacin de sobrecarga, el dispositivo genera una trama de control de flujo.

Esto obliga al interlocutor de transmisin de enlace para dejar de transmitir antes de intentar

volver a transmitir.

CONTROL MICRO PROGRAMADO

Los microprogramas fueron organizados como una secuencia de microinstrucciones y

almacenados en una memoria del control especial. El algoritmo para la unidad de control

microprogramada es usualmente especificado por la descripcin de un diagrama de flujo.1 La

ventaja principal de la unidad de control microprogramada es la simplicidad de su estructura.

Las salidas del controlador son organizadas en microinstrucciones y pueden ser reemplazadas

fcilmente.2

MICRO PROCESADORES DE UNA COMPUTADORA

Es un conjunto de circuitos sumamente complejos, integrados por componentes electrnicos

microscpicos encapsulados en un pequeo chip. Se encarga de la coordinacin y direccin de

todas las operaciones que se llevan a cabo entre los diversos dispositivos de la computadora; tales

como la memoria RAM, las unidades de disco duro, la ejecucin de instruccionesde los programas,

el control hacia los puertos de comunicacin, las operaciones matemticas, etc. Se le puede

denominar indistintamente entre procesador y microprocesador, actualmente se est llegando al

lmite de la miniaturizacin de los componentes internos y se tiene la visin de que tendrn que

desarrollar nuevos procesadores basados en la computacin cuntica (uso de qubits en lugar de

los bits de la computacin clsica).

Un microprocesador controla todas las funciones de la CPU, o la

Unidad Central de Procesamiento, de una computadora u otro

dispositivo digital. El microprocesador funciona como un cerebro

artificial. Toda la funcin de la CPU se controla por un solo circuito

integrado. El microprocesador est programado para dar y recibir

instrucciones de otros componentes del dispositivo. El sistema

puede controlar todo, desde pequeos dispositivos como

calculadoras y telfonos mviles, a grandes automviles.

CARACTERSTICAS

Los microprocesadores trabajan a base de lgica digital. Los tres componentes que forman las

caractersticas principales del microprocesador son una serie de instrucciones digitales, un cierto

ancho de banda y la velocidad de un reloj que mide el nmero de instrucciones que un

microprocesador puede ejecutar. El microprocesador recibe una serie de instrucciones digitales de

mquina. El ALU (por sus siglas en ingls, Unidad Aritmtica Lgica) del procesador realiza una

serie de clculos basados en las instrucciones que recibi. Adicionalmente, la unidad mueve

informacin de una memoria a otra, y tiene la capacidad de pasar de una serie de instrucciones a

otra.

El microprocesador funciona a travs de dos memorias. La Memoria de Solo Lectura, o ROM (siglas

en ingls), es un programa con una serie de instrucciones fijas y es programada por una serie de

bytes fijos. La otra memoria es la RAM, o Memoria de Acceso Aleatorio (siglas en ingls). El

nmero de bytes en esta memoria es variable y tienen un corto tiempo de duracin. Si la

electricidad se apaga, la RAM se limpia. La ROM tiene un pequeo programa interno llamado BIOS

(siglas en ingls de Sistema Bsico de Entrada Salida). El BIOS prueba el hardware de la mquina

cuando se inicia. Luego, busca otro programa en la ROM llamado sector de inicio. El sector de

inicio ejecuta series de instrucciones que ayudan a utilizar la computadora efectivamente.

CONSIDERACIONES

Las computadoras no son meramente procesadores de informacin. Los microprocesadores

deberan ser capaces de ejecutar instrucciones en formatos de informacin, audio y video.

Deberan soportar un rango de efectos multimedia les. Un microprocesador de 32-bit es esencial

para soportar un software multimedia. Con la ventaja de Internet, los microprocesadores deberan

tener la capacidad de soportar memoria virtual y fsica. Deberan poder trabajar con DSP (siglas en

ingls de Procesadores de Seal Digital) para manejar formatos de reproduccin, audio y video.

Los microprocesadores rpidos no requieren un DSP.

POTENCIAL

En esta era digital, existen muy pocos aparatos que no contengan un

microprocesador. Los avances en medicina, el pronstico del tiempo, los

automviles, las comunicaciones, el diseo y los experimentos cientficos

fueron los resultados del desarrollo de los aparatos tecnolgicos con

microprocesadores. La automatizacin de trabajos manuales difciles es

posible debido al microprocesador. La lgica digital de los

microprocesadores ha llevado a una gran eficiencia y velocidad en todos

los aspectos de la vida. El potencial de su uso es por lo tanto inmenso. Los

microprocesadores aseguran maquinarias de mano ms livianas, as como

sistemas de imgenes y comunicacin que han mejorado y mejorarn los

estilos de vida a escala global

PROCESAMIENTO PARALELO

El procesamiento paralelo es un mtodo para aumentar la velocidad de computacin

ejecutando instrucciones de programa secuenciales de forma simultnea en mltiples

procesadores de computadora. Con la realizacin de mltiples pasos de programa al mismo

tiempo, se disminuye el tiempo total requerido para la ejecucin del programa. Aunque el

procesamiento en paralelo se ha utilizado durante muchos aos en computadoras centrales y de

alta gama, ha encontrado lugar hace poco el escritorio comn y porttil a travs de mltiples

unidades de procesamiento central (CPU, por sus siglas en ingls).

Se presenta informacin general relativa a las diferentes arquitecturas modernas de computadores

que manejan mltiples procesadores, sus ventajas y desventajas.

El procesamiento paralelo ofrece una gran ventaja en cuanto a costos. Sin embargo, su principal

beneficio, la escalabilidad (crecer hacia arquitecturas de mayor capacidad), puede ser difcil de

alcanzar an. Esto se debe a que conforme se aaden procesadores, las disputas por los recursos

compartidos se intesifican.

Algunos diseos diferentes de procesamiento paralelo enfrentan este problema fundamental:

Multiprocesamiento simtrico

Procesamiento masivamente paralelo

Procesamiento paralelo escalable

Cada diseo tiene sus propias ventajas y desventajas.

1. MULTIPROCESAMIENTO SIMETRICO

El Multiprocesamiento simtrico (symmetric multiprocessing / SMP) tiene un diseo simple pero

aun as efectivo. En SMP, mltiples procesadores comparten la memoria RAM y el bus del sistema.

Este diseo es tambin conocido como estrechamente acoplado (tightly coupled), o compartiendo

todo (shared everything).

Debido a que SMP comparte globalmente la memoria RAM, tiene solamente un espacio de

memoria, lo que simplifica tanto el sistema fsico como la programacin de aplicaciones. Este

espacio de memoria nico permite que un Sistema Operativo con Multiconexin (multithreaded

operating system) distribuya las tareas entre varios procesadores, o permite que una aplicacin

obtenga la memoria que necesita para una simulacin compleja. La memoria globalmente

compartida tambin vuelve fcil la sincronizacin de los datos.

SMP es uno de los diseos de procesamiento paralelo ms maduro. Apareci en los

supercomputadores Cray X-MP y en sistemas similares hace dcada y media (en 1983).

Sin embargo, esta memoria global contribuye el problema ms grande de SMP: conforme se

aaden procesadores, el trfico en el bus de memoria se satura. Al aadir memoria cach a cada

procesador se puede reducir algo del trfico en el bus, pero el bus generalmente se convierte en

un cuello de botella al manejarse alrededor de ocho o ms procesadores. SMP es considerada una

tecnologa no escalable.

2. PROCESAMIENTO MASIVAMENTE PARALELO

El Procesamiento masivamente paralelo (Massively parallel processing / MPP) es otro diseo de

procesamiento paralelo. Para evitar los cuellos de botella en el bus de memoria, MPP no utiliza

memoria compartida. En su lugar, distribuye la memoria RAM entre los procesadores de modo que

se semeja a una red (cada procesador con su memoria distribuida asociada es similar a un

computador dentro de una red de procesamiento distribuido). Debido a la distribucin dispersa de

los recursos RAM, esta arquitectura es tambin conocida como dispersamente acoplada (loosely

coupled), o compartiendo nada (shared nothing).

Para tener acceso a la memoria fuera de su propia RAM, los procesadores utilizan un esquema

de paso de mensajes anlogo a los paquetes de datos en redes. Este sistema reduce el trfico del

bus, debido a que cada seccin de memoria observa nicamente aquellos accesos que le estn

destinados, en lugar de observar todos los accesos, como ocurre en un sistema SMP. nicamente

cuando un procesador no dispone de la memoria RAM suficiente, utiliza la memoria RAM sobrante

de los otros procesadores. Esto permite sistemas MPP de gran tamao con cientos y an miles de

procesadores. MPP es un a una tecnologa escalable.

El RS/6000 Scalable Powerparallel System de IBM (SP2) es un ejemplo de sistema MPP, que

presenta una ligera variante respecto al esquema genrico anteriormente planteado. Los

procesadores del RS/6000 se agrupan en nodos de 8 procesadores, los que utilizan una nica

memoria compartida (tecnologa SMP). A su vez estos nodos se agrupan entre s utilizando

memoria distribuida para cada nodo (tecnologa MPP). De este modo se consigue un diseo ms

econmico y con mayor capacidad de crecimiento.

La parte negativa de MPP es que la programacin se vuelve difcil, debido a que la memoria se

rompe en pequeos espacios separados. Sin la existencia de un espacio de memoria globalmente

compartido, correr (y escribir) una aplicacin que requiere una gran cantidad de RAM (comparada

con la memoria local), puede ser difcil. La sincronizacin de datos entre tareas ampliamente

distribuidas tambin se vuelve difcil, particularmente si un mensaje debe pasar por muchas fases

hasta alcanzar la memoria del procesador destino.

Escribir una aplicacin MPP tambin requiere estar al tanto de la organizacin de la memoria

manejada por el programa. Donde sea necesario, se requieren insertar comandos de paso de

mensajes dentro del cdigo del programa. Adems de complicar el diseo del programa, tales

comandos pueden crear dependencias de hardware en las aplicaciones. Sin embargo, la mayor

parte de vendedores de computadores han salvaguardado la portabilidad de las aplicaciones

adoptando, sea un mecanismo de dominio pblico para paso de mensajes conocido como Mquina

virtual paralela (parallel virtual machine / PVM), o un estndar en fase de desarrollo

llamado Interfaz de Paso de Mensajes (Message Passing Interface / MPI), para implementar el

mecanismo de paso de mensajes.

3. PROCESAMIENTO PARALELO ESCALABLE

Cmo superar las dificultades de SMP y MPP? La ltima arquitectura paralela, el Procesamiento

paralelo escalable (Scalable parallel processing / SPP), es un hbrido de SMP y MPP, que utiliza

una memoria jerrquica de dos niveles para alcanzar la escalabilidad. La primera capa de memoria

consiste de un nodo que es esencialmente un sistema SMP completo, con mltiples procesadores

y su memoria globalmente compartida.

Se construyen sistemas SPP grandes interconectando dos o mas nodos a travs de la segunda

capa de memoria, de modo que esta capa aparece lgicamente, ante los nodos, como una

memoria global compartida.

La memoria de dos niveles reduce el trfico de bus debido a que solamente ocurren

actualizaciones para mantener coherencia de memoria. Por tanto, SPP ofrece facilidad de

programacin del modelo SMP, a la vez que provee una escalabilidad similar a la de un diseo

MPP.

ARQUITECTURA DUAL

Core Duo de Intel es la primera CPU de doble ncleo. Es toda una nueva arquitectura de Microsoft,

con dos ncleos en un solo dado, el cual, sencillamente, le da dos fichas en un solo paquete.

Funcionando a velocidades ms bajas que la antigua lnea Pentium, Core Duo conserva el poder

sustancial vs trinquete de velocidad de reloj, mientras que lo que se ofrece, en el momento, rcord

de rendimiento.

Ahora hay Core 2 Duo. En muchos sentidos Core 2 es el mismo que el Ncleo: Las fichas se

construyen utilizando el mismo proceso de produccin y ajuste de la misma como tomas chips

Core Duo. Dejando a un lado Core 2 Extreme (una versin de lujo de la Core 2 Duo), no ver

muchos cambios en las especificaciones: Ambos chips tienen la misma velocidad de bus frontal de

667 MHz, pero Core 2 Duo est disponible en velocidades de reloj algo ms rpido (la pc con que

escribo esto, se dispone de chips de 2.67GHz). El bus frontal comunicacin entre la CPU y

memoria RAM (y otros componentes), y es un conocido cuello de botella de rendimiento para

ordenadores. El Core 2 tambin tiene el mismo cach L2 que tiene el ncleo. Sin embargo, hay

cambios en la arquitectura de silicio que le dan a los Core 2 ms sofisticadas capacidades de

procesamiento. Ambos chips existen en versiones de escritorio y porttiles.

Por qu todo este asunto? Rendimiento, pura y simple. En mis pruebas, Core 2 Duo Core Duo de

ordenadores superan a los equipos de tareas en todos los mbitos, desde la prestacin de grficos

y vdeo para correccin ortogrfica de documentos. Mejora la velocidad vara mucho, pero en

promedio es alrededor de un 30 por ciento. Eso es importante en una industria que prospera en

minscula, mejoras. Mejor an, no hay una diferencia apreciable en la duracin de la batera en

ordenadores porttiles, como el consumo de energa tanto para los chips (en la misma velocidad

de reloj) es prcticamente el mismo.

Ahora vamos a considerar la fijacin de precios. Inicialmente, los chips Core 2 son ms caros que

los Core, pero que ha cambiado, como Core es prcticamente desaparecido desde el escritorio de

mercado ahora. Sorprendentemente, ahora puedes obtener una 2.13GHz CPU Core 2 por menos

del precio de un 1.66GHz Core CPU.

Sin embargo, esperamos ver algunos sistemas todava en el mercado que utiliza el ncleo de CPU,

sobre todo en ordenadores porttiles. Rendimiento sigue siendo muy buena con el sistema central,

por lo que no se siente como usted est recibiendo los productos de segunda clase, si usted

compra un porttil Core Duo, pero recuerde que est comprando un chip de Intel que ya no est

activa la venta, y los precios de los Core 2 sistemas no son realmente diferentes de lo que eran

para Cores. Si se trata de mi dinero, me mantenga fuera de un sistema de Core 2 a menos que

usted tiene en gran medida de un ncleo.

FUNDAMENTOS DE OPERACIN

La funcin bsica que realiza un computador es la ejecucin de un programa. Un programa

consiste en un conjunto de instrucciones y datos almacenados en la unidad de memoria. La CPU es

la encargada de ejecutar las instrucciones especificadas en el programa.

La secuencia de operaciones realizadas en la ejecucin de una instruccin constituye lo que se

denomina ciclo de instruccin. Lo ms cmodo es considerar que el procesamiento del ciclo de

instruccin consta de dos fases:

a) Fase de bsqueda

b) Fase de ejecucin

La operacin fundamental de la

mayora de los CPU, es ejecutar una

secuencia de instrucciones

almacenadas llamadas "programa".

El programa es representado por

una serie de nmeros que se

mantentienen en una cierta clase

de memoria de computador. Hay

cuatro pasos que casi todos los CPU

de arquitectura de von Neumann

usan en su operacin: fetch,

decode, execute,y writeback, (leer,

decodificar, ejecutar, y escribir).

Despus de los pasos de lectura y

decodificacin, es llevado a cabo el paso de la ejecucin de la instruccin. Durante este paso,

varias unidades del CPU son conectadas de tal manera que ellas pueden realizar la operacin

deseada. El paso final, la escritura (writeback), simplemente "escribe" los resultados del paso de

ejecucin a una cierta forma de memoria. Muy a menudo, los resultados son escritos a algn

registro interno del CPU para acceso rpido por subsecuentes instrucciones.

Microprocesadores

El microprocesador o simplemente procesador, es el circuito integrado central y ms complejo de

un sistema informtico; a modo de ilustracin, se le suele asociar por analoga como el "cerebro"

de un sistema informtico. El procesador puede definirse, como un circuito integrado constituido

por millones de componentes electrnicos agrupados en un paquete. Constituye la unidad central

de procesamiento (CPU) de un PC catalogado como microcomputador. Desde el punto de vista

funcional es, bsicamente, el encargado de realizar toda operacin aritmtico-lgica, de control y

de comunicacin con el resto de los componentes integrados que conforman un PC, siguiendo el

modelo base de Von Neumann. Tambin es el principal encargado de ejecutar los programas, sean

de usuario o de sistema; slo ejecuta instrucciones programadas a muy bajo nivel, realizando

operaciones elementales, bsicamente, las aritmticas y lgicas, tales como sumar, restar,

multiplicar, dividir, las lgicas binarias .

DIRECCIONAMIENTO Y CICLO DE EJECUCIN

Ciclo de Instruccin (Ciclo de Ejecucin de

Instruccin)

Anteriormente se explic la secuencia de acciones

que se siguen para ejecutar una instruccin en una

computadora basada en la arquitectura de Von

Neumann. En esta clase se abordar con mayor

detalle el ciclo de ejecucin de instruccin, pero

antes, para este propsito, se considerar que ste

ciclo est compuesto por los tres subciclos

siguientes:

Subciclo de Fetch: Se lee en memoria la siguiente instruccin a ejecutar y se la pasa al CPU.

Subciclo de Ejecutar: Se interpreta el cdigo de la instruccin (opcode) y se ejecuta la

operacin indicada.

Subciclo de Interrupcin: Si las interrupciones estn permitidas y habilitadas, entonces, al

ocurrir una interrupcin, se graba el estado del proceso que est siendo ejecutado y se procede a

dar servicio (procesar) la interrupcin.

Los dos primeros subciclos, subciclo de fetch y subciclo de ejecucin, incorporan todas acciones

de la secuencia de ejecucin de instrucciones que hasta ahora se han explicado. El tercer subciclo,

el subciclo de interrupcin, es introducido por vez primera; ste permite el procesamiento de

interrupciones.

Una interrupcin es una seal que se enva al CPU para indicarle la ocurrencia de un evento.

Subsecuentemente, el procesador interrumpe la ejecucin de la instruccin u operacin que

est realizando y procede a servir (dar servicio o procesar) el programa o rutina correspondiente

al evento inherente a la interrupcin recibida. Usualmente, tras procesar una interrupcin, el

procesador contina con el procesamiento de la tarea que realizaba, en el punto en el que se

qued antes de servir la interrupcin. Una interrupcin, dependiendo de su tipo y naturaleza,

puede requerir atencin inmediata, esperar a que el CPU le d servicio, o, simplemente, ser

ignorada. Existen dos tipos de interrupciones:

Interrupcin de hardware. Este tipo de interrupciones son producidas por otros

dispositivos, dispositivos perifricos, o componentes de hardware de la computadora. Estas

interrupciones causan que el procesador grabe el estado de ejecucin actual y que inicie la

ejecucin de una rutina manejadora de la interrupcin (interrupt handler). La unidad de control

en la computadora que recibe la interrupcin es quien determina en dnde se encuentra la rutina

de manejo correspondiente e instruye que se inicie el procesamiento de la misma.

Interrupciones de software (conocidas tambin como excepciones o trampas). Estas

interrupciones son generadas dentro de un programa y son usadas para indicar al CPU que hacer

una vez que recibe la interrupcin. Usualmente, las interrupciones de software son

implementadas como instrucciones dentro del conjunto de instrucciones de una computadora.

Estas interrupciones causan un cambio de contexto (context switch), lo cual significa que se graba

el estado de ejecucin de la operacin en curso y se procede a ejecutar una rutina manejadora

similar a la de una instruccin de hardware.

NOTA: Las PCs dan soporte a 256 tipos de interrupciones de software y 15 interrupciones de

hardware.

Fetch Indirecto o Ciclo Indirecto

Ya se ha visto que la ejecucin de una instruccin puede requerir invocar uno o ms datos u

operandos que se encuentran en la memoria. Cada uno de estos datos deber ser extrado de la

memoria mediante un fetch. Sin embargo, es frecuente que la instruccin a ejecutar especifique

direccionamiento indirecto para extraer un operando, lo cual implicar el uso de un acceso a

memoria adicional.

Se puede ver al fetch de direccionamiento indirecto como un subciclo ms en el ciclo de

instruccin:

Durante una operacin normal, el procesador

busca secuencialmente y ejecuta una instruccin

tras otra, hasta que se procesa una instruccin

(HALT) de paro. La bsqueda y ejecucin de una

instruccin constituye el ciclo de instruccin, que

representa a su vez una o ms operaciones de

acceso a memoria o a dispositivos de E/S. Cada

acceso a memoria requiere un ciclo mquina.

Hay, por ejemplo, siete tipos diferentes de ciclo

mquina en el 8085.

bsqueda de Cd. p.

lectura de MEMORIA

escritura a MEMORIA

lectura de E/S

escritura a E/S

respuesta a interrupcin

bus inactivo.

REGISTROS INTERNOS

Los registros del procesador se emplean para controlar instrucciones en ejecucin, manejar

direccionamiento de memoria y proporcionar capacidad aritmtica. Los registros son

direccionables por medio de un nombre. Los bits por convencin, se numeran de derecha a

izquierda, como en:

... 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Los registros internos del procesador se pueden clasificar en 6 tipos diferentes

1 Registros de segmento

2-Registros de propsito general

3-Registros de apuntadores

4-Registros de banderas

5-Registros de Pila

Registros de segmento

Un registro de segmento tiene 16 bits de longitud y facilita un rea de memoria para

direccionamiento conocida como el segmento actual.

Registro CS. El DOS almacena la direccin inicial del segmento de cdigo de un programa en el

registro CS. Esta direccin de segmento, mas un valor de desplazamiento en el registro apuntador

de instruccin (IP), indica la direccin de una instruccin que es buscada para su ejecucin.

Registro DS. La direccin inicial de un segmento de datos de programa es almacenada en el

registro DS. En trminos sencillos, esta direccin, mas un valor de desplazamiento en una

instruccin, genera una referencia a la localidad de un byte especifico en el segmento de datos.

Registro SS. El registro SS permite la colocacin en memoria de una pila, para almacenamiento

temporal de direcciones y datos. El DOS almacena la direccin de inicio del segmento de pila de un

programa en le registro SS. Esta direccin de segmento, mas un valor de desplazamiento en el

registro del apuntador de pila (SP), indica la palabra actual en la pila que esta siendo direccionada.

Registros ES. Alguna operaciones con cadenas de caracteres (datos de caracteres) utilizan el

registro extra de segmento para manejar el direccionamiento de memoria. En este contexto, el

registro ES esta asociado con el registro DI (ndice). Un programa que requiere el uso del registro

ES puede inicializarlo con una direccin de segmento apropiada.

Registros FS y GS. Son registros extra de segmento en los procesadores 80386 y posteriores.

Registros de propsito general.

Los registros de propsito general AX, BX, CX y DX son los caballos de batalla del sistema. Son

nicos en el sentido de que se puede direccionarlos como una palabra o como una parte de un

byte. El ultimo byte de la izquierda es la parte "alta", y el ultimo byte de la derecha es la parte

"baja". Por ejemplo, el registro CX consta de una parte CH (alta) y una parte Cl (baja), y usted

puede referirse a cualquier parte por su nombre.

Registro AX. El registro AX, el acumulador principal, es utilizado para operaciones que implican

entrada/salida y la mayor parte de la aritmtica. Por ejemplo, las instrucciones para multiplicar ,

dividir y traducir suponen el uso del AX. Tambin, algunas operaciones generan cdigo mas

eficiente si se refieren al AX en lugar de a los otros registros.

Registro BX. El BX es conocido como el registro base ya que es el nico registro de propsito

general que puede ser ndice para direccionamiento indexado. Tambin es comn emplear el BX

para clculos.

Registro DX. El DX es conocido como l registro de datos. Alguna operaciones de entrada/salida

requieren uso, y las operaciones de multiplicacin y divisin con cifras grandes suponen al DX y al

AX trabajando juntos.

Regresar Arriba

Registro de Apuntador de Instrucciones.

El registro apuntador de instrucciones (IP) de 16 bits contiene el desplazamiento de direccin de la

siguiente instruccin que se ejecuta. El IP esta asociado con el registro CS en el sentido de que el IP

indica la instruccin actual dentro del segmento de cdigo que se esta ejecutando actualmente.

Los procesadores 80386 y posteriores tienen un IP ampliado de 32 bits, llamado EIP.

En el ejemplo siguiente, el registro CS contiene 25A4[0]H y el IP contiene 412H. Para encontrar la

siguiente instruccin que ser ejecutada, el procesador combina las direcciones en el CS y el IP:

Segmento de direccin en el registro CS: 25A40H Desplazamiento de direccin en el registro IP: +

412H Direccin de la siguiente instruccin: 25E52H

Registros Apuntadores.

Los registros SP (apuntador de la pila) Y BP (apuntador de base) estn asociados con el registro SS

y permiten al sistema accesar datos en el segmento de la pila.

Registro SP. El apuntador de la pila de 16 bits esta asociado con el registro SS y proporciona un

valor de desplazamiento que se refiere a la palabra actual que esta siendo procesada en la pila. Los

procesadores 80386 y posteriores tienen un apuntador de pila de 32 bits, el registro ESP. El

sistema maneja de forma automtica estos registros.

En el ejemplo siguiente, el registro SS contiene la direccin de segmento 27B3[0]H y el SP el

desplazamiento 312H. Para encontrar la palabra actual que esta siendo procesada en la pila, la

computadora combina las direcciones en el SS y el SP:

Registro BP. El BP de 16 bits facilita la referencia de parmetros, los cuales son datos y direcciones

transmitidos va pila. Los procesadores 80386 y posteriores tienen un BP ampliado de 32 bits

llamado el registro EBP.

Registros Indice.

Los registros SI y DI estn disponibles para direccionamiento indexado y para sumas y restas.

Registro SI. El registro ndice fuente de 16 bits es requerido por algunas operaciones con cadenas

(de caracteres). En este contexto, el SI esta asociado con el registro DS. Los procesadores 80386 y

posteriores permiten el uso de un registro ampliado de 32 bits, el ESI.

Registro DI. El registro ndice destino tambin es requerido por algunas operaciones con cadenas

de caracteres. En este contexto, el DI esta asociado con el registro ES. Los procesadores 80386 y

posteriores permiten el uso de un registro ampliado de 32 bits, el EDI.

Registro de Banderas.

De los 16 bits del registro de banderas, nueve son comunes a toda la familia de procesadores

8086, y sirven para indicar el estado actual de la maquina y el resultado del procesamiento.

Muchas instrucciones que piden comparaciones y aritmtica cambian el estado de las banderas,

algunas cuyas instrucciones pueden realizar pruebas para determinar la accin subsecuente. En

resumen, los bits de las banderas comunes son como sigue:

OF (Overflow, desbordamiento). Indica desbordamiento de un bit

de orden alto (mas a la izquierda) despus de una operacin aritmtica.

DF (direccin). Designa la direccin hacia la izquierda o hacia la derecha para mover o comparar

cadenas de caracteres.

IF (interrupcin). Indica que una interrupcin externa, como la entrada desde el teclado, sea

procesada o ignorada.

TF (trampa). Permite la operacin del procesador en modo de un paso. Los programas

depuradores, como el DEBUG, activan esta bandera de manera que usted pueda avanzar en la

ejecucin de una sola instruccin a un tiempo, para examinar el efecto de esa instruccin sobre los

registros de memoria.

SF (signo). Contiene el signo resultante de una operacin aritmtica (0 = positivo y 1 = negativo).

ZF (cero). Indica el resultado de una operacin aritmtica o de comparacin (0 = resultado

diferente de cero y 1 = resultado igual a cero).

AF (acarreo auxiliar). Contiene un acarreo externo del bit 3 en un dato de 8 bits para aritmtica

especializada.

PF (paridad). Indica paridad par o impar de una operacin en datos de 8 bits de bajo orden (mas a

la derecha).

CF (acarreo). Contiene el acarreo de orden mas alto (mas a la izquierda) despus de una operacin

aritmtica; tambin lleva el contenido del ultimo bit en una operacin de corrimiento o de

rotacin. Las banderas estn en el registro de banderas en las siguientes posiciones:

Las banderas mas importantes para la programacin en ensamblador son O, S, Z y C, para

operaciones de comparacin y aritmticas, y D para operaciones de cadenas de caracteres. Los

procesadores 80286 y posteriores tienen algunas banderas usadas para propsitos internos, en

especial las que afectan al modo protegido. Los procesadores 80286 y posteriores tienen un

registro extendido de banderas conocido como Eflags.

Registros de PILA

La pila es un rea de memoria importante y por ello tiene, en vez de uno, dos registros que se usan

como desplazamiento (offset) para apuntar a su contenido. Se usan como complemento al registro

y son:

-SP- Stack Pointer: Se traduce como puntero de pila y es el que se reserva el procesador para uso

propio en instrucciones de manipulado de pila. Por lo general , el programador no debe alterar su

contenido.

-BP- Base pointer: Se usa como registro auxiliar. El programador puede usarlo para su provecho.

Claro que estos nombres y tipos de registros son estndar, ya que cada fabricante puede utilizar

otros registro que reemplacen a estos o los auxilien, aun as, los fabricantes que usan otros

registro tienen la misma funcin que los anteriormente mencionados

Ejemplo

Registros de uso general del 8086/8088:

Tienen 16 bits cada uno y son ocho:

AX = Registro acumulador, dividido en AH y AL (8 bits cada uno). Usndolo se produce (en general)

una instruccin que ocupa un byte menos que si se utilizaran otros registros de uso general. Su

parte ms baja, AL, tambin tiene esta propiedad. El ltimo registro mencionado es el equivalente

al acumulador de los procesadores anteriores (8080 y 8085). Adems hay instrucciones como DAA;

DAS; AAA; AAS; AAM; AAD; LAHF; SAHF; CBW; IN y OUT que trabajan con AX o con uno de sus dos

bytes (AH o AL). Tambin se utiliza este registro (junto con DX a veces) en multiplicaciones y

divisiones.

BX = Registro base, dividido en BH y BL. Es el registro base de propsito similar (se usa para

direccionamiento indirecto) y es una versin ms potente del par de registros HL de los

procesadores anteriores.

CX = Registro contador, dividido en CH y CL. Se utiliza como contador en bucles (instruccin LOOP),

en operaciones con cadenas (usando el prefijo REP) y en desplazamientos y rotaciones (usando el

registro CL en los dos ltimos casos).

DX = Registro de datos, dividido en DH y DL. Se utiliza junto con el registro AX en multiplicaciones y

divisiones, en la instruccin CWD y en IN y OUT para direccionamiento indirecto de puertos (el

registro DX indica el nmero de puerto de entrada/salida).

SP = Puntero de pila (no se puede subdividir). Aunque es un registro de uso general, debe utilizarse

slo como puntero de pila, la cual sirve para almacenar las direcciones de retorno de subrutinas y

los datos temporarios (mediante las instrucciones PUSH y POP). Al introducir (push) un valor en la

pila a este registro se le resta dos, mientras que al extraer (pop) un valor de la pila este a registro

se le suma dos.

BP = Puntero base (no se puede subdividir). Generalmente se utiliza para realizar direccionamiento

indirecto dentro de la pila.

SI = Puntero ndice (no se puede subdividir). Sirve como puntero fuente para las operaciones con

cadenas. Tambin sirve para realizar direccionamiento indirecto.

DI = Puntero destino (no se puede subdividir). Sirve como puntero destino para las operaciones

con cadenas. Tambin sirve para realizar direccionamiento indirecto.

Cualquiera de estos registros puede

utilizarse como fuente o destino en

operaciones aritmticas y lgicas

Indicadores (flags)

Hay nueve indicadores de un bit en este

registro de 16 bits. Los cuatro bits ms

significativos estn indefinidos, mientras

que hay tres bits con valores

determinados: los bits 5 y 3 siempre valen

cero y el bit 1 siempre vale uno (esto

tambin ocurra en los procesadores

anteriores).

CF (Carry Flag, bit 0): Si vale 1, indica que

hubo "arrastre" (en caso de suma) hacia, o

"prstamo" (en caso de resta) desde el bit de orden ms significativo del resultado. Este indicador

es usado por instrucciones que suman o restan nmeros que ocupan varios bytes. Las

instrucciones de rotacin pueden aislar un bit de la memoria o de un registro ponindolo en el CF.

PF (Parity Flag, bit 2): Si vale uno, el resultado tiene paridad par, es decir, un nmero par de bits a

1. Este indicador se puede utilizar para detectar errores en transmisiones.

AF (Auxiliary carry Flag, bit 4): Si vale 1, indica que hubo "arrastre" o "prstamo" del nibble (cuatro

bits) menos significativo al nibble ms significativo. Este indicador se usa con las instrucciones de

ajuste decimal.

ZF (Zero Flag, bit 6): Si este indicador vale 1, el resultado de la operacin es cero.

SF (Sign Flag, bit 7): Refleja el bit ms significativo del resultado. Como los nmeros negativos se

representan en la notacin de complemento a dos, este bit representa el signo: 0 si es positivo, 1

si es negativo.

También podría gustarte

- Cap1 ICI445Documento17 páginasCap1 ICI445Yeudy Eliezer FelizAún no hay calificaciones

- Tendencias en La Arquitectura de Las Computadoras 777Documento9 páginasTendencias en La Arquitectura de Las Computadoras 777Courtney HicksAún no hay calificaciones

- Diagrama de Video ConferenciaDocumento2 páginasDiagrama de Video ConferenciaCourtney HicksAún no hay calificaciones

- Ejercicios de ClaseDocumento5 páginasEjercicios de ClaseCourtney HicksAún no hay calificaciones

- Busqueda de 3 Tipos de Discos HDDDocumento3 páginasBusqueda de 3 Tipos de Discos HDDCourtney HicksAún no hay calificaciones

- Unidad 6 Soporte TecnicoDocumento17 páginasUnidad 6 Soporte TecnicoCourtney HicksAún no hay calificaciones

- Tipo de DatosDocumento4 páginasTipo de DatosCourtney HicksAún no hay calificaciones

- Practicas 1er ParcialDocumento9 páginasPracticas 1er ParcialCourtney HicksAún no hay calificaciones

- Unidad 5 CompletaDocumento10 páginasUnidad 5 CompletaCourtney HicksAún no hay calificaciones

- Suma Visual StudioDocumento2 páginasSuma Visual StudioCourtney HicksAún no hay calificaciones

- Unidad 4 CompletaDocumento11 páginasUnidad 4 CompletaCourtney HicksAún no hay calificaciones

- Diagram AsDocumento2 páginasDiagram AsCourtney HicksAún no hay calificaciones

- PolinomioDocumento3 páginasPolinomioCourtney HicksAún no hay calificaciones

- Unidad 6 Soporte TecnicoDocumento17 páginasUnidad 6 Soporte TecnicoCourtney HicksAún no hay calificaciones

- Unidad 4Documento4 páginasUnidad 4Courtney HicksAún no hay calificaciones

- Practicas Visual StudioDocumento2 páginasPracticas Visual StudioCourtney HicksAún no hay calificaciones

- Unidad 2 CompletaDocumento20 páginasUnidad 2 CompletaCourtney HicksAún no hay calificaciones

- GuiaDocumento2 páginasGuiaCourtney HicksAún no hay calificaciones

- Trabajo Completo - ArquitecturaDocumento13 páginasTrabajo Completo - ArquitecturaCourtney HicksAún no hay calificaciones

- Tipos de Diagramas UmlDocumento11 páginasTipos de Diagramas UmlCourtney HicksAún no hay calificaciones

- GuiaDocumento3 páginasGuiaCourtney HicksAún no hay calificaciones

- Unidad 2 ArquitecturaDocumento10 páginasUnidad 2 ArquitecturaCourtney HicksAún no hay calificaciones

- Que Es UmlDocumento4 páginasQue Es UmlCourtney HicksAún no hay calificaciones

- Binario Mayor y MenorDocumento3 páginasBinario Mayor y MenorCourtney HicksAún no hay calificaciones

- 6 Diagramas de FlujoDocumento4 páginas6 Diagramas de FlujoCourtney HicksAún no hay calificaciones

- Trabajo Completo - ArquitecturaDocumento13 páginasTrabajo Completo - ArquitecturaCourtney HicksAún no hay calificaciones

- Trabajo Completo - ArquitecturaDocumento13 páginasTrabajo Completo - ArquitecturaCourtney HicksAún no hay calificaciones

- La observación científica: claves para entender un método pedagógicoDocumento10 páginasLa observación científica: claves para entender un método pedagógicoAlejandra ReyesAún no hay calificaciones

- Cuestionario Instrumento de MediciónDocumento5 páginasCuestionario Instrumento de MediciónSamirAG0% (1)

- Adalberto Diploma UNI Diplomado Gestion Por Procesos y Six SigmaDocumento14 páginasAdalberto Diploma UNI Diplomado Gestion Por Procesos y Six SigmaAdalberto TorresAún no hay calificaciones

- Optoelectronica PDFDocumento12 páginasOptoelectronica PDFPiñon Skot de SfAún no hay calificaciones

- Práctica #7 Cinetica EnzimaticaDocumento4 páginasPráctica #7 Cinetica EnzimaticaWendy Huaraca ChávezAún no hay calificaciones

- Norma Iso 9000-2015 Fundamentos y VocabularioDocumento34 páginasNorma Iso 9000-2015 Fundamentos y VocabularioLuis Carlos Mota Zapata100% (1)

- VIOLENCIa - DemunaDocumento17 páginasVIOLENCIa - DemunaVictor Raul C AAún no hay calificaciones

- DNGB Ev3 ProviDocumento3 páginasDNGB Ev3 ProviDevany GarzaAún no hay calificaciones

- Tomo4 PDFDocumento140 páginasTomo4 PDFOrtiga MayorAún no hay calificaciones

- Fermentacion Del AgaveDocumento2 páginasFermentacion Del AgaveLeidy TovarAún no hay calificaciones

- Preelaboracion y Conservacion de Carnes Aves y CazaDocumento2 páginasPreelaboracion y Conservacion de Carnes Aves y CazaDario Alejandro García GarcíaAún no hay calificaciones

- Simbolos Personalizados y SoportesDocumento18 páginasSimbolos Personalizados y Soporteskakoso74Aún no hay calificaciones

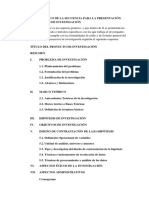

- Protocolo de InvestigacionDocumento9 páginasProtocolo de InvestigacionDavid LopezAún no hay calificaciones

- Síndrome cerebeloso: características, causas y manifestaciones clínicasDocumento9 páginasSíndrome cerebeloso: características, causas y manifestaciones clínicasEmmanuel Padilla JordanAún no hay calificaciones

- SALARIO Emocional TrabajoDocumento5 páginasSALARIO Emocional TrabajoAlejandro SuarezAún no hay calificaciones

- Gritos del corazón y la soledadDocumento13 páginasGritos del corazón y la soledadKevin JesusAún no hay calificaciones

- Fisiología Humana y NeurologíaDocumento14 páginasFisiología Humana y NeurologíaGuillermo Gerardo Gaxiola CerecerAún no hay calificaciones

- Elitismo en MonterreyDocumento1 páginaElitismo en MonterreyGilberto AbelardoAún no hay calificaciones

- Catálogo de partes MasesaDocumento72 páginasCatálogo de partes MasesaSegundo ZapataAún no hay calificaciones

- Habilidades sociales esencialesDocumento18 páginasHabilidades sociales esencialesmariacillerAún no hay calificaciones

- Aplicar El Programa Hot Potatoes para Mejorar La Comprensión Lectora en El Área de Inglés en Los Educandos Del Tercer Grado de Educación SecundariaDocumento20 páginasAplicar El Programa Hot Potatoes para Mejorar La Comprensión Lectora en El Área de Inglés en Los Educandos Del Tercer Grado de Educación SecundariaJulio CordovaAún no hay calificaciones

- GUIA EcopsosDocumento8 páginasGUIA EcopsosDescanso LeonAún no hay calificaciones

- Ética UBA 2012: Introducción a los problemas éticosDocumento6 páginasÉtica UBA 2012: Introducción a los problemas éticosOmar GramajoAún no hay calificaciones

- GanganDocumento1 páginaGanganANA RAMONA ANA RAMONA MORENO/GRATEROAún no hay calificaciones

- XII Bienal Nacional de Arquitectura Mexicana 2012BDocumento27 páginasXII Bienal Nacional de Arquitectura Mexicana 2012BDaniel Adrian Ruiz SibajaAún no hay calificaciones

- Primero Medio Biología, Actividad Semana 23-3Documento3 páginasPrimero Medio Biología, Actividad Semana 23-3María Jose Higuera HigueraAún no hay calificaciones

- PREDICCION DE LA PERMEABILIDAD DPSTDocumento15 páginasPREDICCION DE LA PERMEABILIDAD DPSTDiego Suárez GutiérrezAún no hay calificaciones

- Construya Un Amplificador de 180w Con Tda7294Documento10 páginasConstruya Un Amplificador de 180w Con Tda7294Henry Garcia100% (1)

- Actuar de La Población de La Ciudad de Arequipa Frente Al Problema Prevaleciente de La Contaminación Ambiental y Su Conocimiento Del Impacto A La SaludDocumento4 páginasActuar de La Población de La Ciudad de Arequipa Frente Al Problema Prevaleciente de La Contaminación Ambiental y Su Conocimiento Del Impacto A La SaludALHELI MASIEL ONOFRE CHAMBILLAAún no hay calificaciones

- NOCTURNAL Total La Distancia DetallesDocumento5 páginasNOCTURNAL Total La Distancia DetallesDiarios camAún no hay calificaciones