Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Física de Operación de Los MOSFETs de Potencia

Cargado por

George Hernández0 calificaciones0% encontró este documento útil (0 votos)

105 vistas3 páginas[1] Cada celda elemental de un MOSFET de potencia varía de unos pocos micrómetros a varias decenas de micrómetros de ancho. [2] La región N- permite al dispositivo soportar altos voltajes al habilitar la conducción entre el drenador y el surtidor. El documento describe la estructura y operación básica de un MOSFET de potencia de doble difusión, incluida la formación del canal de inversión controlado por voltaje y la resistencia de conducción.

Descripción original:

Derechos de autor

© © All Rights Reserved

Formatos disponibles

PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documento[1] Cada celda elemental de un MOSFET de potencia varía de unos pocos micrómetros a varias decenas de micrómetros de ancho. [2] La región N- permite al dispositivo soportar altos voltajes al habilitar la conducción entre el drenador y el surtidor. El documento describe la estructura y operación básica de un MOSFET de potencia de doble difusión, incluida la formación del canal de inversión controlado por voltaje y la resistencia de conducción.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

105 vistas3 páginasFísica de Operación de Los MOSFETs de Potencia

Cargado por

George Hernández[1] Cada celda elemental de un MOSFET de potencia varía de unos pocos micrómetros a varias decenas de micrómetros de ancho. [2] La región N- permite al dispositivo soportar altos voltajes al habilitar la conducción entre el drenador y el surtidor. El documento describe la estructura y operación básica de un MOSFET de potencia de doble difusión, incluida la formación del canal de inversión controlado por voltaje y la resistencia de conducción.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Está en la página 1de 3

[1] Cada celda elemental de un MOSFET de potencia varia de unos pocos micrmetros a varias decenas de micrmetros de ancho

[2] La regin N- es la que habilita al dispositivo para soportar altos voltajes

APUNTES DE INVESTIGACIONES DE

TEORIA DE DISPOSITIVOS

Fsica de Operacin de los MOSFET de Potencia de Doble

Difusin (DMOS)

JORGE HERNANDEZ

INGENIERO ELECTRONICO

UNIVERSIDAD DISTRITAL FJC

BOGOTA (COLOMBIA) 2014

INTRODUCCION. QUE ES UN MOSFET DE POTENCIA

Un MOSFET de potencia, como su nombre lo indica, es un tipo de transistor de efecto de campo MOS (Metal

Oxide Semiconductor) diseado especficamente para manejar niveles de potencia significativos. Al contrario

de un BJT (transistor bipolar), que es un dispositivo bipolar controlado por corriente, el MOSFET es un

dispositivo unipolar controlado por voltaje. Esto ltimo significa que en un MOSFET la conduccin de

corriente se debe a un solo tipo de portadores mayoritarios (electrones o huecos) y que se requiere una muy

baja corriente de entrada para controlar una gran potencia de salida.

El MOSFET de potencia es un producto de la evolucin de la tecnologa CMOS, originalmente desarrollada

para la fabricacin de circuitos integrados. Desde su introduccin al mercado a comienzos de la dcada de

1980, los MOSFET de potencia han ido evolucionando en su estructura funcional hasta alcanzar su madurez

definitiva con el proceso de doble difusin (DMOS), tambin llamado difusin vertical (VDMOS). En la

actualidad, prcticamente todos los MOSFET de potencia estn basados en tecnologa DMOS o alguna de sus

variantes, como la TMOS de Motorola. En este artculo nos referiremos exclusivamente a esta tecnologa.

Figura 00

Comparado con otros dispositivos semiconductores de potencia, como los BJTs, los IGBTs y los tiristores, los

MOSFETs de potencia modernos ofrecen varias ventajas, siendo las ms notables su alta velocidad de

conmutacin, su buena eficiencia a bajos voltajes, su alta impedancia de entrada, su coeficiente de temperatura

positivo, su trasconductancia constante, su alta inmunidad a las variaciones de voltaje ( ) dt dv y su bajo costo.

Su principal desventaja es la relativa sensibilidad a las descargas electrostticas.

El MOSFET de potencia es el interruptor de bajo voltaje (por debajo de 200V) ms utilizado en el mundo. Se

utiliza extensivamente en fuentes de alimentacin, convertidores DC-DC y controladores de motores.

.

ESTRUCTURA DE UN MOSFET DE POTENCIA

En la figura 00a se muestra la estructura bsica de la seccin transversal de un MOSFET de potencia de doble

difusin (DMOS), ms exactamente de una de las miles de celdas elementales que lo constituyen. Al contrario

de un MOSFET de baja seal, donde la compuerta (G), el surtidor (S) y el drenador (D) estn localizados en la

[1] Cada celda elemental de un MOSFET de potencia varia de unos pocos micrmetros a varias decenas de micrmetros de ancho

[2] La regin N- es la que habilita al dispositivo para soportar altos voltajes

misma superficie de la pastilla y el canal tiene una disposicin lateral, en un MOSFET de potencia el surtidor

(S) y el drenador (D) estn en lados opuestos y el canal tiene una disposicin vertical. La idea bsica de esta

estructura es controlar eficientemente el flujo de portadores mayoritarios de corriente entre el surtidor (S) y el

drenador (D) mediante la formacin de una capa de inversin virtual (el canal) que conecta ambos contactos.

El canal es controlado o modulado por una seal de voltaje apropiada aplicada entre la compuerta (G) y el

surtidor (S).

Figura 00

Un MOSFET de potencia consta bsicamente de un sustrato de silicio N+ (fuertemente dopado) sobre el cual

crece una capa epitaxial de deriva N- (levemente dopada) y se hacen dos difusiones sucesivas para crear una

zona de base P+ y una zona de deriva N+. A continuacin se hace crecer una delgada capa de xido metlico

(SiO2) que encierra una formacin de silicio policristalino (polisilicio) fuertemente dopada con fsforo. Desde

esta ltima so obtiene el contacto de la compuerta (G). Los contactos del drenador (D) y el surtidor o fuente (S)

se obtienen de metalizaciones que conectan, respectivamente, con la regin N+ del sustrato) y la regin P+ de

la zona doblemente difundida. Esta ltima, denominada tambin region de cuerpo o masa, forma con la regin

N+ de la misma un diodo o unin P-N. La capa de polisilicio emparedada entre las capas de xido metlico

constituye lo que se denomina una estructura MOS (Metal-Oxido-Semiconductor), la cual acta esencialmente

como un condensador.

Desde el punto de vista elctrico, las caractersticas de la unin P-N entre la regin de base P+ y la regin de

deriva N+ asociada al surtidor determina las capacidades de bloqueo de voltaje directo del dispositivo, mientras

que las caractersticas de la regin de deriva N- asociada al drenador determinan las capacidades de bloqueo de

voltaje inverso del mismo. Como resultado se obtiene un dispositivo con una muy baja

) ( on DS

R (resistencia de

conduccin entre drenador y surtidor) y un muy alto

DSS BR

V

) (

( voltaje de ruptura o de bloqueo inverso entre

drenador y surtidor)

..

OPERACIN BASICA (I). CORRIENTE DE DRENADOR (

D

I )

En condiciones de reposo, cuando la compuerta (G) y el surtidor (S) estn al mismo potencial ( 0

GS

V ), no se

establece canal alguno en la regin de base P+ y por tanto no circula una

D

I (corriente de drenador a fuente).

Para que esto ltimo suceda, debe establecerse un camino conductor entre las regiones N+ y N- a travs de la

regin de difusin de base P+

Cuando se aplica al terminal de compuerta un

GS

V de magnitud y polaridad apropiada, la compuerta de

polisilicio induce una capa de inversin en la parte superior de la regin P+, como se muestra en la figura 00.

Esta capa de inversin (canal) conecta la regin N+ del surtidor a la regin N- del drenador y posibilita que

comience a fluir una corriente

D

I a partir de un cierto valor de

GS

V llamado voltaje de umbral (

) ( th GS

V ). La

corriente

D

I est dada aproximadamente por :

o

DS FS DS th GS GS o D

V g V V V C

L

Z

I ] [

) (

[1] (para valores peqieos de

DS

V ) y

o ] [

2

1

] [

2

) (

2

) ( th GS GS FS th GS GS o D

V V g V V C

L

Z

I [2] (para valores grandes de

DS

V )

siendo:

o

DS

V = Voltaje aplicado entre drenador y fuente

[1] Cada celda elemental de un MOSFET de potencia varia de unos pocos micrmetros a varias decenas de micrmetros de ancho

[2] La regin N- es la que habilita al dispositivo para soportar altos voltajes

o

GS

V = Volta aplicado entre compuerta y fuente

o

) ( th GS

V = Voltaje de umbral entre compuerta y fuente

o

FS

g = Transconductancia o ganancia del dispositivo (

GS D

V I )

o = Movilidad de los portadores mayoritarios

o

o

C = Capacitancia por unidad de area del xido de la compuerta

o Z = Ancho del canal

o L = Longitud del canal

Tpicamente, el voltaje de umbralo de la compuerta (

) ( th GS

V ) se especifica para una

D

I de 1.0 mA.

..

OPERACIN BASICA (II). RESISTENCIA DE CONDUCCION (

) ( on DS

R )

A medida que se incrementa el

GS

V por encima de

) ( th GS

V , la resistencia del canal disminuye y la corriente

D

I

aumenta. En su flujo desde el terminal del drenador hasta el terminal de fuente, la corriente

D

I encuentra una

resistencia de conduccin (

) ( on DS

R ) dada por

o

D JFET ACC CH on DS

r r r r R

) (

Siendo:

o

CH

r = Resistencia del canal de inversin

o

ACC

r = Resistencia de la regin de acumulacin entre compuerta y drenador

o

JFET

r = Resistencia de pinch del FET de unin

o

D

r = Resistencia de la regin N- (levemente dopada) de drenador

Estas resistencias se muestran en la figura 00. La resistencia

CH

r se incrementa con la longitud del canal, la

resistencia

ACC

r con el ancho de la regin de polisilicio (poly) y la resistencia

JFET

r con la resistividad de la

regin epitaxial (epi). Estas tres resistencias son inversamente proporcionales al ancho del canal y al voltaje

GS

V . La resistencia

D

r , por su parte, es proporcional a la resistividad epitaxial y al ancho del polisilicio, e

inversamente proporcional al ancho del canal.

En el caso de dispositivos de alto voltaje, donde la capa epitaxial es gruesa y tiene una alta resistividad, la

) ( on DS

R es dominada principalmente por

D

r . En el caso de dispositivos de bajo voltaje, donde la capa la capa

epitaxial es delgada y tiene una baja resistividad, la

) ( on DS

R es dominada principalmente por

CH

r . Lo anterior

explica por qu los dispositivos de alto voltaje conducen plenamente con voltajes de compuerta moderados,

mientras que en los dispositivos de bajo voltaje la

) ( on DS

R disminuye a medida que

GS

V se incrementa.

La resistencia

) ( on DS

R es inversamente proporcional a la movilidad de los portadores. Puesto que la movilidad

de los electrones (que son los portadores mayoritarios en dispositivos de canal N) es, en promedio, 2.8 veces

mayor que la movilidad de los huecos (que lo son en dispositivos de canal P), esto significa que la

) ( on DS

R de

un MOSFET de canal P es 2.8 veces mayor que la un MOSFET de canal N equivalente. Por tanto, para que

estos dos dispositivos sean realmente complementarios en sus caractersticas, la relacin L Z entre la anchura

y la longitud del canal del MOSFET de canal P debe ser 2.8 veces mayor que la del MOSFET de canal N.

Como resultado, un dispositivo de canal P requiere un area de pastillla mayor que la del dispositivo de canal N

complementario, lo cual aumenta las capacitancias parsitas y los costos de fabricacin.

FIN

También podría gustarte

- Mosfet de EmpobrecimientoDocumento1 páginaMosfet de EmpobrecimientoMandingoAún no hay calificaciones

- Polarización y Condiciones de FronteraDocumento36 páginasPolarización y Condiciones de FronteraJhonathan MedinaAún no hay calificaciones

- Evaluavion MaestriaDocumento1 páginaEvaluavion Maestriayacu1986Aún no hay calificaciones

- Actividad 6 ACDocumento4 páginasActividad 6 ACAlejo NscAún no hay calificaciones

- Los prototipos acortan el ciclo de vida del desarrollo de sistemasDocumento1 páginaLos prototipos acortan el ciclo de vida del desarrollo de sistemasBrian ZevallosgAún no hay calificaciones

- Resolución de Ejercico - RedesDocumento5 páginasResolución de Ejercico - RedesMaria Jose Loor DelgadoAún no hay calificaciones

- Introducción A Los Sistemas CelularesDocumento5 páginasIntroducción A Los Sistemas CelularesSaul De Leon EstradaAún no hay calificaciones

- Ejercicios de ProbabilidadesDocumento13 páginasEjercicios de Probabilidadessairo panamaAún no hay calificaciones

- Primer Parcial 20-2-2021Documento8 páginasPrimer Parcial 20-2-2021Julio AlcantaraAún no hay calificaciones

- Cuadro Resumen Cualidades Del TextoDocumento3 páginasCuadro Resumen Cualidades Del TextoMónicaManzanoAún no hay calificaciones

- Práctica 04 Demodulador AMDocumento8 páginasPráctica 04 Demodulador AMbartolome777ooAún no hay calificaciones

- Presupuesto General del Estado 2020 y su análisis ante la crisis del Covid-19Documento9 páginasPresupuesto General del Estado 2020 y su análisis ante la crisis del Covid-19Liz Mejia100% (1)

- Racionalización de RadicalesDocumento102 páginasRacionalización de RadicalesjesusAún no hay calificaciones

- Integración de campos escalares con MatlabDocumento5 páginasIntegración de campos escalares con MatlabJosé Leonardo Fernández BalderaAún no hay calificaciones

- Resolucion Ejercicio 1Documento3 páginasResolucion Ejercicio 1Elian coveñaAún no hay calificaciones

- Tarea Yuliana GonzalezDocumento5 páginasTarea Yuliana GonzalezJareth GonzalezAún no hay calificaciones

- EC-1113 Ejercicios TransistoresDocumento8 páginasEC-1113 Ejercicios TransistoresDaniel VelaAún no hay calificaciones

- El Mundo Electrónico oDocumento4 páginasEl Mundo Electrónico oOran AlcaAún no hay calificaciones

- MAPQ - Práctica 02 Lab Electrónica II 19-19 PDFDocumento8 páginasMAPQ - Práctica 02 Lab Electrónica II 19-19 PDFMiguel AngelAún no hay calificaciones

- TEKOMDocumento19 páginasTEKOMCristhian TurciosAún no hay calificaciones

- 2 MAGNITUDES ELÉCTRICAS DiapositivasDocumento24 páginas2 MAGNITUDES ELÉCTRICAS DiapositivasJORDAN DE JESUS MARTINEZ ARROYOAún no hay calificaciones

- Segundo Parcial 3.0 de FIS-213-05Documento9 páginasSegundo Parcial 3.0 de FIS-213-05Enmanuel Puntiel JimenezAún no hay calificaciones

- Cuantificadores Uniformes y LogarítmicosDocumento7 páginasCuantificadores Uniformes y LogarítmicosRonald BarciaAún no hay calificaciones

- Practica Introductoria 2023-I PDFDocumento4 páginasPractica Introductoria 2023-I PDFKevin NietoAún no hay calificaciones

- Arquitectura de Los Centros de Conmutación y Señalización en Redes de TelecomunicaciónDocumento30 páginasArquitectura de Los Centros de Conmutación y Señalización en Redes de TelecomunicaciónBryan ToapaxiAún no hay calificaciones

- Examen EstadisticaDocumento3 páginasExamen EstadisticaelmanAún no hay calificaciones

- Diferencia de medias entre turnos vespertino y matutinoDocumento3 páginasDiferencia de medias entre turnos vespertino y matutinoNicole ErazoAún no hay calificaciones

- VHDL lenguaje esencial lógica digital historiaDocumento2 páginasVHDL lenguaje esencial lógica digital historiaeduardo andres rubianoAún no hay calificaciones

- Fisica 4 PDFDocumento65 páginasFisica 4 PDFFlorenciaAún no hay calificaciones

- Auditoría de redes: planeación e instalaciónDocumento16 páginasAuditoría de redes: planeación e instalaciónSifuentes SusanaAún no hay calificaciones

- T2 Problemario Introducción A La ProbabilidadDocumento4 páginasT2 Problemario Introducción A La ProbabilidadAntonio Palomares DiazAún no hay calificaciones

- Joyce EjerciciosDocumento9 páginasJoyce EjerciciosStalin SalazarAún no hay calificaciones

- Repaso Comunicaciones MóvilesDocumento2 páginasRepaso Comunicaciones MóvilesroloAún no hay calificaciones

- Sapnning TreeDocumento2 páginasSapnning TreeJorge Pichardo100% (1)

- Distribución uniforme de la vida de perros ovejerosDocumento68 páginasDistribución uniforme de la vida de perros ovejerosGómez PatriciaAún no hay calificaciones

- Práctica 03 Electrónica IDocumento12 páginasPráctica 03 Electrónica IDario TravezAún no hay calificaciones

- El Aporte de 5G en La Educación, Enrique ChoezDocumento4 páginasEl Aporte de 5G en La Educación, Enrique ChoezHeinrichAún no hay calificaciones

- Distribuciones probabilísticas variables aleatoriasDocumento26 páginasDistribuciones probabilísticas variables aleatoriasOscar Matos CanulAún no hay calificaciones

- Ejercicio 17Documento4 páginasEjercicio 17Onelia Maria May CastellanosAún no hay calificaciones

- Comunicacion Analogica PDFDocumento6 páginasComunicacion Analogica PDFHnryCMndzAún no hay calificaciones

- Proyecto SelectorDocumento16 páginasProyecto SelectorGrecia Melissa Dionicio AntunezAún no hay calificaciones

- Dominio de DifusionDocumento13 páginasDominio de Difusionpablo andres solanoAún no hay calificaciones

- Estadistica Descriptiva ADM ACT 4 FDocumento4 páginasEstadistica Descriptiva ADM ACT 4 FFernando ArmasAún no hay calificaciones

- Investigación Método de Bessel y CarsonDocumento3 páginasInvestigación Método de Bessel y CarsonJunior Peñalver RamírezAún no hay calificaciones

- Ramificación condicional CMP y TST MC68000Documento23 páginasRamificación condicional CMP y TST MC68000ShamattAún no hay calificaciones

- Informe Gira Unidad NacionalDocumento7 páginasInforme Gira Unidad NacionalCarlos Andres ChicaizaAún no hay calificaciones

- Ejercicios Tema 1 LEY OHDocumento4 páginasEjercicios Tema 1 LEY OHfcojcgAún no hay calificaciones

- Resumen TecnicoDocumento7 páginasResumen Tecnicogestionmantenimiento100% (5)

- AplicacionesDocumento1 páginaAplicacionesFEDRA FARCA VILLAVICENCIOAún no hay calificaciones

- Práctica 04 Demodulador AM UISRAELDocumento7 páginasPráctica 04 Demodulador AM UISRAELROMULO ECWAún no hay calificaciones

- Lab 4 Teoremas de Superposicion y Thevenin Vj201701 Jose Antonio Vasquez JimenezDocumento17 páginasLab 4 Teoremas de Superposicion y Thevenin Vj201701 Jose Antonio Vasquez JimenezJosé Jiménez100% (2)

- Carga y DescargaDocumento13 páginasCarga y DescargaDIEGO CAMACHOAún no hay calificaciones

- DINAMICA-SEMANA-3-Diagrama CausalDocumento71 páginasDINAMICA-SEMANA-3-Diagrama CausalallissonAún no hay calificaciones

- Ejercicios GraficasDocumento2 páginasEjercicios GraficasEsly RodriguezAún no hay calificaciones

- Probabilidades de Poisson en varios ejemplosDocumento2 páginasProbabilidades de Poisson en varios ejemplosFlavio Zambrano TorresAún no hay calificaciones

- LAB 1-1 Amp Clase A 2018Documento3 páginasLAB 1-1 Amp Clase A 2018SARA STEFANIA GUERRERO TOAPANTAAún no hay calificaciones

- Protocolo UdpDocumento18 páginasProtocolo Udpanon_76721220Aún no hay calificaciones

- Mosfet Tipo EnriquecimientoDocumento2 páginasMosfet Tipo EnriquecimientoJeisson RubioAún no hay calificaciones

- Investigacion MosfetDocumento9 páginasInvestigacion MosfetArturo DíazAún no hay calificaciones

- 5.a Power Mosfet v2.0Documento7 páginas5.a Power Mosfet v2.0Jhimmy GonzalezAún no hay calificaciones

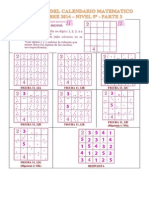

- Cm1409 Septiembre Soluciones Parte3Documento3 páginasCm1409 Septiembre Soluciones Parte3George HernándezAún no hay calificaciones

- Cm1409 Septiembre Soluciones Parte1Documento3 páginasCm1409 Septiembre Soluciones Parte1George HernándezAún no hay calificaciones

- Calendario Matemático Marzo 2014 - Solución Ejercicio 4Documento2 páginasCalendario Matemático Marzo 2014 - Solución Ejercicio 4George HernándezAún no hay calificaciones

- Introducción Al Estudio de Los Tubos Al Vacio. Parte 1Documento4 páginasIntroducción Al Estudio de Los Tubos Al Vacio. Parte 1George Hernández50% (2)

- Calendario Matemático Marzo 2014 - Solución Ejercicio 3Documento1 páginaCalendario Matemático Marzo 2014 - Solución Ejercicio 3George HernándezAún no hay calificaciones

- Clase 07 - 070901 - Resonancia Magnética Nuclear (I)Documento5 páginasClase 07 - 070901 - Resonancia Magnética Nuclear (I)George HernándezAún no hay calificaciones

- Control Programable de Lavadora-000Documento4 páginasControl Programable de Lavadora-000arturo_hernandez_78Aún no hay calificaciones

- Comunicaciones Por SateliteDocumento21 páginasComunicaciones Por SateliteEr PichonAún no hay calificaciones

- Proceso de Instalación de Un EquipoDocumento23 páginasProceso de Instalación de Un EquipoKar CrisAún no hay calificaciones

- Transmisor FM Directo Con Vco y VaractorDocumento13 páginasTransmisor FM Directo Con Vco y VaractorFrancisco DazaAún no hay calificaciones

- Es-En DS SWIFT UtilcellDocumento9 páginasEs-En DS SWIFT UtilcellDavid100% (1)

- Introducción Al ATP DrawDocumento66 páginasIntroducción Al ATP DrawAdaline IngenieriaAún no hay calificaciones

- Clase 04.12.2020 A.Circuitos 199Documento14 páginasClase 04.12.2020 A.Circuitos 199Carlos Moraga CopierAún no hay calificaciones

- Detector de metales PI sencillo deDocumento3 páginasDetector de metales PI sencillo dejose luis alvarezAún no hay calificaciones

- Circuito Rectificador en Onda Completa Con Puente de DiodosDocumento2 páginasCircuito Rectificador en Onda Completa Con Puente de DiodoszulyAún no hay calificaciones

- La Etapa de FIDocumento24 páginasLa Etapa de FIPAPACUNCUNAún no hay calificaciones

- Tipos de Computadores PDFDocumento1 páginaTipos de Computadores PDFDuvan CruzAún no hay calificaciones

- Central Telefonica ERICSSONDocumento25 páginasCentral Telefonica ERICSSONfrancoalexis50% (4)

- ConclusionesDocumento4 páginasConclusionesluis ronald ayasta tejadaAún no hay calificaciones

- Circuitos Fet en Los Circuitos IntegradosDocumento39 páginasCircuitos Fet en Los Circuitos IntegradosJhojan Mamani0% (1)

- Informe Lab.5Documento11 páginasInforme Lab.5Hugo Quezada Alegría100% (1)

- 1 Componentes Principales Del AFD Dispenser 10Documento5 páginas1 Componentes Principales Del AFD Dispenser 10Profesor Xavier100% (1)

- Transformadores de RF de banda anchaDocumento38 páginasTransformadores de RF de banda anchayes-cali100% (1)

- DEMODULACIÓNDocumento36 páginasDEMODULACIÓNEtson Heasid Tarazona CalixtoAún no hay calificaciones

- 6 - Controladores Programables y Terminales de Dialogo2020 PDFDocumento35 páginas6 - Controladores Programables y Terminales de Dialogo2020 PDFDaniel MonsalveAún no hay calificaciones

- Tarea 19 (Ftes de Corriente y El Amp OP) - Revisión Del IntentoDocumento3 páginasTarea 19 (Ftes de Corriente y El Amp OP) - Revisión Del IntentoVictoriano Meza MaderaAún no hay calificaciones

- Filtro Digital CarrilloDocumento32 páginasFiltro Digital CarrilloFREDERICK QUISPE HIPOLITOAún no hay calificaciones

- TransistoresDocumento7 páginasTransistoresDiego Marcelo CalahorranoAún no hay calificaciones

- Conexión Icsp para Grabar Microcontroladores PicDocumento6 páginasConexión Icsp para Grabar Microcontroladores PicPedro SánchezAún no hay calificaciones

- Hardware y SoftwareDocumento13 páginasHardware y SoftwareHuepe EduarAún no hay calificaciones

- Acta entrega equipos oficinaDocumento79 páginasActa entrega equipos oficinaSebas ContrerasAún no hay calificaciones

- Led - 32LD840FT 40LD835F 46LD836FDocumento36 páginasLed - 32LD840FT 40LD835F 46LD836FBolivar Arismendy Arias RuizAún no hay calificaciones

- Radioenlace 2150504 41-Tarea7Documento13 páginasRadioenlace 2150504 41-Tarea7Ever Castañeda100% (1)

- Fuente dual variable -15V a 15VDocumento15 páginasFuente dual variable -15V a 15VJorge Rivera100% (1)

- Apareamiento de Bases de DatosDocumento3 páginasApareamiento de Bases de DatosNati0716Aún no hay calificaciones

- MULTIMEDIA HDD GRABS TV & PLAYS FILESDocumento2 páginasMULTIMEDIA HDD GRABS TV & PLAYS FILESJorge LeonAún no hay calificaciones