Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Trabcolaborativo JaimeQuintero

Cargado por

Julieth Paola Saldarriaga0 calificaciones0% encontró este documento útil (0 votos)

5 vistas5 páginasTítulo original

Trabcolaborativo_JaimeQuintero (1)

Derechos de autor

© © All Rights Reserved

Formatos disponibles

DOC, PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOC, PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

5 vistas5 páginasTrabcolaborativo JaimeQuintero

Cargado por

Julieth Paola SaldarriagaCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOC, PDF, TXT o lea en línea desde Scribd

Está en la página 1de 5

Trabajo Colaborativo 2

JAIME ALBERTO QUINTERO

COD: 94472479

CEAD - Palmira

Tutor

CARLOS EMEL RUIZ

SISTEMAS DIGITALES SECUENCIALES

90178_30

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA

ESCUELA DE CIENCIAS BSICAS, TECNOLOGAS E INGENIERAS

PROGRAMA DE INGENIERA EN ELECTRNICA

Diseo de un circuito secuencial.

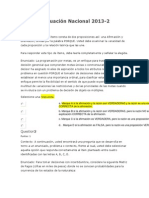

Mediante el desarrollo del trabajo se pretende implementar un circuito

secuencial que visualice en un display de siete segmentos la secuencia de diez

nmeros de manera cclica.

Para su desarrollo se implemento un contador modulo 10, que realiza el conteo

de cero hasta nueve mediante el arreglo de cuatro Flip-Flop JK conectados en

cascadas y comandados mediante una seal de reloj implementada por medio

de circuito integrado 555 configurado como multivibrador astable que entrega

una seal peridica F=1/3Hz. Por medio de la seal entregada a la salida de

los cuatro Flip-Flop (Q3Q2Q1Q0) que corresponde a los estados del circuito

secuencial, se construye la salida para las diferentes secuencias mediante el

proceso de minimizacin de cuatro mapas de Karnaugh para las salidas

(Y3Y2Y1Y0). Esta salida alimenta a un decodificador para un display de nodo

comn que corresponde al circuito integrado 7447 para su respectiva

visualizacin en un display de 7 segmentos.

Seal de reloj

Contador

Modulo 10

Modulo de salida

combinacional

Decodificador y

salida display

Fig. 1. Diagrama de bloques del sistema.

Seal de reloj. Para la implementacin de la seal de reloj se implemento

mediante el circuito integrado 555 configurado como multivibrador astable u

oscilador de relajacin, cuya frecuencia del sistema es de 1/3Hz y se calcula

mediante la siguiente frmula para la configuracin presentada en la Fig. 2.

Fig. 2. Esquema de conexin del circuito 555.

Contador modulo 10. Para la implementacin del contador se emplearon

cuatro Flip-Flop JK conectados en cascada mediante el circuito integrado

74107, en donde la entrada de reloj de primer contador se alimenta por la

salida de circuito integrado 555 en el pin 3, y para los siguientes Flip-Flop se

conecta la seal de reloj de entrada de la salida Q del anterior. Igualmente

cada Flip-Flop se interconecta las entradas J=K=1 para que conmute entre 0 y

1 para cada seal de reloj, y para fijar el conteo del contador de 0 a 9 se

emplea la operacin lgica NAND entre las salida Q 1 y Q3 de los Flip-Flop y la

operacin lgica AND con una tercera variable que corresponde a un pulsador

para reiniciar el conteo a cero.

Fig. 3. Esquema de contador modulo 10.

Modulo de salida combinacional. Este modulo tiene como parmetro de

entrada la salida de bloque secuencia compuesta por el contador modulo 10 y

por medio de un proceso de minimizacin por mapas de Karnaugh permite

obtener el valor correcto de la secuencia correspondiente como se presenta en

la siguiente tabla 1.

Q3 Q2 Q1 Q0 Y3

Y2

Y1

Y0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

1

0

0

1

1

0

0

0

1

1

0

1

0

0

0

1

0

0

0

0

1

0

0

1

0

1

0

0

0

1

0

1

1

0

0

0

1

1

0

1

1

1

0

1

0

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

Tabla 1. Tabla de relacin de estados y salida.

Minimizacin salida Y3

Minimizacin salida Y2

Q3 Q2

Q0

00

10

0

00

01

11

Q1

01

11

10

11

00

01

11

Minimizacin salida Y0

Q0

Q3 Q2

00

10

0

00

01

11

10

Q0

01

10

Minimizacin salida Y1

Q1

Q1

Q3 Q2

00

10

0

Q0

Q3 Q2

00

10

0

00

01

11

01

11

Q1

10

01

11

Decodificador y salida display. Este bloque recibe como parmetro las

cuatro variables del bloque anterior (Y 3Y2Y1Y0), y que alimenta al circuito

decodificador 7447 y el respectivo display de 7 segmentos, como se muestra

en la Fig. 4.

Fig. 4. Esquema de conexin del decodificador y display de 7 segmentos.

En la Fig. 5, se encuentra un esquema general del circuito en donde se

visualiza en el display el segundo digito de la secuencia que corresponde al 8.

Fig. 5. Esquema general del circuito secuencial.

También podría gustarte

- Trabajo Colaborativo No 2 GRUPO No. 256596 30Documento29 páginasTrabajo Colaborativo No 2 GRUPO No. 256596 30Julieth Paola SaldarriagaAún no hay calificaciones

- Trabajo Colaborativo No 2 GRUPO No. 256596 30Documento29 páginasTrabajo Colaborativo No 2 GRUPO No. 256596 30Julieth Paola SaldarriagaAún no hay calificaciones

- Instrumentacion IndustrialDocumento19 páginasInstrumentacion IndustrialJulieth Paola Saldarriaga100% (1)

- Evaluación Nacional 2013Documento17 páginasEvaluación Nacional 2013Julieth Paola SaldarriagaAún no hay calificaciones