Documentos de Académico

Documentos de Profesional

Documentos de Cultura

CPLD

Cargado por

Jano Jesus Alex0 calificaciones0% encontró este documento útil (0 votos)

12 vistas14 páginasTítulo original

cpld (3)

Derechos de autor

© © All Rights Reserved

Formatos disponibles

DOCX, PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOCX, PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

12 vistas14 páginasCPLD

Cargado por

Jano Jesus AlexCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOCX, PDF, TXT o lea en línea desde Scribd

Está en la página 1de 14

Universidad Nacional de San Agustn

Facultad: Ingeniera de Produccin y Servicios

Escuela Profesional: Ing. Electrnica

Curso: Electrnica Digital-Practica

Tema: CPLD

Docente: Ing. Juan Carlos Cuadros

Integrantes:

.

Grupo:

Arequipa Per

Un CPLD (del acrnimo ingls Complex Programmable Logic Device) es un

dispositivo electrnico.

Los CPLD extienden el concepto de un PLD (del acrnimo ingls Programmable Logic

Device) a un mayor nivel de integracin ya que permite implementar sistemas ms

eficaces, ya que utilizan menor espacio, mejoran la fiabilidad del diseo, y reducen

costos. Un CPLD se forma con mltiples bloques lgicos, cada uno similar a un PLD.

Los bloques lgicos se comunican entre s utilizando una matriz programable de

interconexiones, lo cual hace ms eficiente el uso del silicio, conduciendo a una mejor

eficiencia a menor costo. A continuacin se explican brevemente las principales

caractersticas de la arquitectura de un CPLD.

Un dispositivo lgico programable, o PLD (Programmable Logic Device), es un

dispositivo cuyas caractersticas pueden ser modificadas y almacenadas mediante

programacin. El principio de sntesis de cualquier dispositivo lgico programable se

fundamenta en el hecho de que cualquier funcin booleana puede ser expresada como

una suma de productos. El dispositivo programable ms simple es el PAL

(Programmable Array Logic). El circuito interno de un PAL consiste en un arreglo, o

matriz, de compuertas AND y un arreglo de compuertas OR. El arreglo AND es

programable mientras que el OR generalmente es fijo. Mediante una matriz de

conexiones se seleccionan cuales entradas sern conectadas al arreglo AND, cuyas

salidas son conectadas al arreglo OR y de esta manera obtener una funcin lgica en

forma de suma de productos. Una matriz de conexiones es una red de conductores

distribuidos en filas y columnas con un fusible en cada punto de interseccin.

La mayora de los PLDs estn formados por una matriz de conexiones, una matriz de

compuertas AND, y una matriz de compuertas OR y algunos, adems, con registros.

Con estos recursos se implementan las funciones lgicas deseadas mediante un software

especial y un programador. Las matrices pueden ser fijas o programables. El tipo ms

sencillo de matriz programable, que data de los aos 60, era una matriz de diodos con

un fusible en cada punto de interseccin de la misma. En la figura 1.1 se muestran los

circuitos bsicos para la mayora de los PLDs.

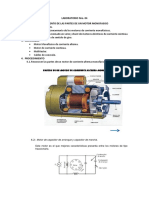

Funcionamiento de un CPLD

Un CPLD (del acrnimo ingls Complex Programmable Logic Device) es un

dispositivo electrnico que extiende el concepto de un PLD (del acrnimo ingls

Programmable Logic Device) a un mayor nivel de integracin ya que permite

implementar sistemas ms eficaces, porque utilizan menos espacio, mejoran la

fiabilidad del diseo, y reducen costos.

Un CPLD se forma con mltiples bloques lgicos, cada uno similar a un PLD.

Los bloques lgicos se comunican entre s utilizando una matriz programable

de interconexiones, lo cual hace ms eficiente el uso del silicio, conduciendo a

una mejor eficiencia a menor costo.

Matriz de Interconexiones Programables

La matriz de interconexiones programables (PIM) permiten unir los pines de

entrada/salida a las entradas del bloque lgico, o las salidas del bloque lgico a

las entradas de otro bloque lgico o inclusive a las entradas del mismo. La

mayora de los CPLDs usan una de dos configuraciones para esta matriz:

interconexin mediante bloques o interconexin mediante multiplexores.

El primero se basa en una matriz de filas y columnas con una celda

programable de conexin en cada interseccin. Al igual que en las GAL esta

celda puede ser activada para conectar/desconectar la correspondiente fila y

columna. Esta configuracin permite una total interconexin entre las entradas

y salidas del dispositivo o bloques lgicos. Sin embargo, estas ventajas

provocan que disminuya el rendimiento del dispositivo, adems de aumentar el

consumo de energa y el tamao del componente.

En la interconexin mediante multiplexores, existe un multiplexor por cada

entrada al bloque lgico. Las vas de interconexin programables son

conectadas a las entradas de un nmero de multiplexores por cada bloque

lgico. Las lneas de seleccin de estos multiplexores son programadas para

permitir que sea seleccionada nicamente una va de la matriz de interconexin

por cada multiplexor la cual se propagara a hacia el bloque lgico. Cabe

mencionar que no todas las vas son conectadas a las entradas de cada

multiplexor. La rutabilidad se incrementa usando multiplexores de mayor

tamao, permitiendo que cualquier combinacin de seales de la matriz de

interconexin pueda ser enlazada hacia cualquier bloque lgico. Sin embargo,

el uso de grandes multiplexores incrementa el tamao de dispositivo y reduce

su eficiencia.

Bloques Lgicos

Un bloque lgico es similar a un PLD, cada uno pose un bloque de compuertas

AND y OR en forma de suma de productos, una configuracin para la

distribucin de estas sumas de productos, y macroceldas. El tamao del bloque

lgico es una medida de la capacidad del CPLD, ya que de esto depende el

tamao de la funcin booleana que pueda ser implementada dentro del bloque.

Los bloques lgicos usualmente tienen de 4 a 20 macroceldas.

Macroceldas

Estas tambin estn provistas con registros, control de polaridad, y buffers para

salidas en alta impedancia. Por lo general un CPLD tiene macroceldas de

entrada/salida, macroceldas de entrada y macroceldas internas u ocultas

(buried macrocells), en tanto que un 22v10 tiene solamente macroceldas de

entrada/salida. Una macrocelda interna es similar a una macrocelda de

entrada/salida, slo que esta no puede ser conectada directamente a un pin de

salida. La salida de una macrocelda interna va directamente a la matriz de

interconexin programable.

Celda de Entrada / Salida

La funcin de una celda de entrada/salida es permitir el paso de una seal

hacia dentro o hacia el exterior del dispositivo. Dependiendo del fabricante y de

la arquitectura del CPLD estas celdas pueden o no ser consideradas parte del

bloque lgico.

Estructura de un CPLD

Los CPLD son dispositivo lgicos programables con una complejidad entre los

dispositivos PLA y FPGA. La caracterstica principal comun entre los CPLD y

PAL, es la configuracin de memoria no-volatil, y con respecto a los dispositivo

FPGA, la caracterstica comn de ste ltimo es que posee un desarrollo de

compuertas de grande densidades, con la diferencia que los FPGA, tienen

mayor densidad que los CPLD. A modo general un CPLD es como si se tuviera

varios PLD, tipo PAL, dentro de un slo chip. el tamao mas grande los CPLD

permite implementar ecuaciones lgicas o diseos mas complicados. la

programacin de estos dispositivos es generalmente en lenguajes de

descripcin de hardware , por ejemplo, VHDL o Verilog.

Matriz de Suma de Puntos

Se relacionan con un mayor nmero de interconexin de secciones de

compuertas programables, tales secciones pueden ser otros PLD, es decir el

CPLD puede contener similares PLD de baja densidad, "PAL", interconectados

entre s, en un solo chip.

Figura # 1: Diagrama de

Bloque de un CPLD (por ALTERA)

Figura # 2: Diagrama de

Bloque de un CPLD (por XILINX)

La estructura principal son los bloques de matriz lgicos (LAB) o bloques de

Funcin (Funtion Block), que se comunican en un bus interno con la matriz de

Interconexin Programable (PIA) o tambin llamado Fast CONNECT Switch

Matrix. Cada bloque es un grupo de 16 macroceldas; tienen entradas y salidas

similares a los PLD de baja densidad, con capacidad de programarse. El

nmero de pines de entrada y/o salida depender del dispositivo, para el caso

de la figura 1, corresponde al modelo MAX7000S, basados en celdas

EEPROM, del fabricante ALTERA, de 6 a 16 pines de entrada y salida, estas

ltimas se encuentran en el bloque de control de entrada y salida, la cual

tambin posee conexin con el PIA, y en la figura 2, el bloque de salida y

entrada I/O, poseen un bufer para los dispositivos de entrada y salida.

Cada bloque de funcin, para el caso de XILINX modelo de ejemplo "XC9500",

esta compuesto de 18 macroceldas independientes. Los bloques funcionales

tambin reciben una seal (reloj) de sincronismo global, una seal para

habilitar la salida y una seal para habilitar el reset/set. El bloque funcional

genera 18 salidas que maneja el FAST CONNECT. estas 18 salidas y su

correspondiente seales de habilitacin son gobernadas por el bloque I/O. la

lgica dentro de los bloques funcionales es implementada utilizando la

representacin de suma de producto .

Figura # 3: Bloque de

Funcin

Las macroceldas pueden ser configuradas individualmente por una funcin de

registro. 5 matriz de compuertas AND, directos al "product terms "(termino de

producto), son utilizados como entrada de datos primario (para las compuertas

OR y XOR) para implementar funciones combinacionales, o como entradas de

control incluyendo el reloj, seales set/reset, y seal de habilitacin de salida.

Los registros de las macroceldas pueden ser configurados como FLIP-FLOP

tipo D o FLIP-FLOP tipo T. o este puede ser omitido por una operacin

combinacinoal. Cada registro soporta operaciones set y reset asincronos.

durante el encendido del dispositivo, todos los registro son inicializados al

estado predefinido por el usuario.

Figura # 4: Macrocelda

con Bloque de Funcin

Las seales de contro global son desarrolladas individualmente en cada

macrocelda, incluyendo seal de reloj, seal de set/reset, y la seales de

habilitacin. la macrocelda registra seales de reloj de cada uno de los tres

relojes globales o del termino producto. La seal GSR, es una seal de

Reset/set, de entrada que permite que sea definido por el usuario.

Figura # 5: Reloj de

Macrocelda

El termino producto, controla que la matriz de las 5 AND sean asignadas a

cada macrocelda, un ejemplo pudiera ser que todas las AND sean manejadas

por una OR. El inconveniente de esto es que se evidencia el retardo de un

termino producto a otro como se observa en la siguiente figura.

Figura # 6: Lgica de

Macrocelda utilizando termino producto

Figura # 7: Lgica de un

termino producto

El FAST CONNECT Switch Matriz conecta las seales a la entrada del bloque

de funcin; tanto las salidas del bloque I/O como las salidas del bloque de

funcin las manejas el Fast Connect Switch Matrix, cualquiera de estas pueden

ser seleccionadas, a travs de la programacin del usuario, para poder manejar

cada bloque con un retardo uniforme.

Figura # 8: Fast Connect

Switch Matrix

El Bloque I/O es la interfaz entre la lgica interna y los pines de entrada y salida

del dispositivo CPLD. Cada bloque de I/O incluye un bufer de entrada y un

manejador de salida; un multiplexor que selecciona la salida habilitada, y

tambin incluye una seal de control de tierra para la programacin del usuario.

El bufer de entrada es compatible con tensin de 5 V CMOS, 5 V TTL, y

seales de voltaje de 3.3 V. El bufer de entrada usa internamente un suministro

de potencia de 5 V ( Vccint), para asegurarse que el umbral de entrada

permanezca constante y no varie con el voltaje Vccio. la seal de salida se

habilita de la siguiente formas: una seal puede ser generada por el termino

producto de la macrocelda, cualquiera de las seales globales de OE, o por

una seal de tercer estado GTS.

Figura # 9: Bloque I/O

Cada salida tiene un control independiente de "Slew Rate" (Mxima variacin

del voltaje de salida con respecto al tiempo); este control permite reducir o

controlar el ruido en el sistema, con slo modificar el Tslew.

Figura # 10: Slew Rate

Estos CPLD poseen circuito con memoria EEPROM; que permiten reescribirse

muchas veces, dependiendo del fabricante puede ser hasta 10.000 veces,

como es el caso del fabricante XILINX, los modelos de la serie XC9500.

Tabla de Datos (Look up Table)

Esta arquitectura se basa en la implementacin lgico de bus de interconexin

de filas y columnas, estas interconexiones tambin proveen conexin al bloque

de matriz lgicos (LAB). El LAB consiste de varios elementos lgicos (LE);

segn el modelo pueden ser 10 LE, por cada LAB. Los LE es una pequea

unidad lgica que proveen una eficiente implementacin de funciones lgicas

del usuario. El Multitrack Interconnect provee una rpida conexin entre los

LAB.

Figura # 11: Diagrama de

bloque de la arquitectura de tabla de datos

Look-Up Table (LUT), Es un circuito que implementa una funcin de lgica

combinacional para almacenar una lista de valores de salida que correspondan

a todas las posibles combinaciones de entradas, es decir un nmero de

elementos almacenados son usados; para resumir una funcin lgica,

almacenando cada funcin como una tabla de la verdad, esto se ilustra en la

figura 12.

Figura # 12: Look-Up

Table

Tomando como ejemplo la tabla de la verdad de la figura 12, como comparador

A1A0=B1B2 , hace que la salida lgica AEQB = 1 lgico. Una matriz de 16 flip-

flops (Q0 hasta Q15), contiene data de todas las posibles combinaciones

A1A0B1B0, por cada combinacin se necesita un flip-flop. La entrada de cada

LUT son decodificada por un decodificador de direcciones, cada salida del

decodificador activa una buffer de tres estados, que pasa por un bloque de

salida de flip-flop. Cuando se activa un buffer para pasar el contenido del flip-

flop, el resto de los buffer permanecen en estado de alta impedancia, de esta

manera se bloquea la data de los otros flip-flops. El contenido de los flip-flop

son cargados cuando el LUT es programado, con las funciones requeridas.

Continuando con el ejemplo de la figura 12, los 16 elementos almacenados en

dicha tabla, combinados , para seleccionar una salida combinacional y para

interconectar con otras partes del chip, es llamado Elemento Lgico (LE). La

funcin del desempeo del elemento lgico es similar a la de macroceldas en

los PLD de suma de producto. La estructura de un elemento lgico se muestra

en la figura 13.

Figura # 13: Elemento

Lgico

El circuito "Cascade Chain", permite al usuario programar la funcin boleana,

este circuito puede ser de compuertas AND o OR.

Figura # 14: Operacin

en Cascada

Bloque de Matriz Lgico (LAB), consiste en un nmero de elementos lgicos e

interconectados localmente; el bloque LAB, esta conectado con el resto del

dispositivo por medio de una serie de columnas y filas interconectadas, lo cual

para este caso el fabricante ALTERA ha llamado FastTrack Interconnect,

tambin se le conoce como Multitrack Interconnect.

Figura # 15: Bloque de

Matriz Lgicos

Embedded Array Block (EAB), este bloque es una matriz de 2048 elemento de

almacenaje que pueden ser usado eficientemente en la implementacin de

funciones lgicas complejas.

El FLEX10K es un dispositivo del fabricante ALTERA, tiene una matriz de 6

filas por 24 columnas de bloque de matriz lgico (LAB), es decir que tendr 144

LAB, que a su ves son 8 x 144LAB= 1152 elementos lgicos, estos elementos

tambin tienen 6 EAB; 6X2048 = 12288 bits de almacenaje de EAB, note que

un EAB tiene mas capacidad de almacenaje que un LAB combinado.

Algunos los dispositivos basados en LUT, son de tecnologa de memoria de

acceso aleatorio esttica (SRAM), la ventaja de esta configuracin es que este

puede ser fabricado en densidades muy altas de celdas de almacenajes y

programar rpidamente, comparado con un dispositivo, (suma de producto,

SOP), basado en EEPROM. La desventaja es que las celdas SRAM, son

voltiles; es decir que deben reconfigurarse cada vez que se reinicia el sistema.

http://www.altera.com/support/software/drivers/dri-bb-xp.htmlSistemas Digitales: Principios

y Aplicaciones. Ronald J. Tocci, Neal S. Widmer, Gregory L. Moss.Dcima Edicin. Prentice Hall

IEC FRANCISCO JAVIER TORRES VALLE

CAPTULO II: DISPOSITIVOS LGICOS PROGRAMABLES

http://es.wikipedia.org/wiki/CPLD

http://www.altera.com/devices/cpld/cpld-index.html

http://www.altera.com/devices/cpld/max2/mx2-index.jsp

http://www.xilinx.com/products/silicon-devices/cpld/

http://www.slideshare.net/euch00/manual-completo-de-cpld-10759181

http://html.rincondelvago.com/dispositivos-logicos-programables_2.html

http://www.dicom.unican.es/espanol/gilberto/CAP5.html

También podría gustarte

- Hardware computadora XT 8088 - Características y componentes del sistemaDocumento29 páginasHardware computadora XT 8088 - Características y componentes del sistemaDavid ChoquehuancaAún no hay calificaciones

- Amplificador de retroalimentación con polos y margen de faseDocumento3 páginasAmplificador de retroalimentación con polos y margen de faseJano Jesus AlexAún no hay calificaciones

- ϕ=−120=−tan f f f f fDocumento5 páginasϕ=−120=−tan f f f f fJano Jesus AlexAún no hay calificaciones

- 83 84Documento3 páginas83 84Jano Jesus AlexAún no hay calificaciones

- INFRMACION PARA LA 1ra. EVALUACION CONTINUA PDFDocumento17 páginasINFRMACION PARA LA 1ra. EVALUACION CONTINUA PDFJano Jesus AlexAún no hay calificaciones

- 88,89,90Documento3 páginas88,89,90Jano Jesus AlexAún no hay calificaciones

- 71 72 73 74Documento4 páginas71 72 73 74Jano Jesus AlexAún no hay calificaciones

- Análisis de rendimiento de procesadores superescalares con predicción de saltosDocumento3 páginasAnálisis de rendimiento de procesadores superescalares con predicción de saltosJano Jesus AlexAún no hay calificaciones

- Nanotobus de Carbono en Arquitectura de ComputadorasDocumento6 páginasNanotobus de Carbono en Arquitectura de ComputadorasJano Jesus AlexAún no hay calificaciones

- Nanotobus de Carbono en Arquitectura de ComputadorasDocumento6 páginasNanotobus de Carbono en Arquitectura de ComputadorasJano Jesus AlexAún no hay calificaciones

- Problemas para Que PractiquenDocumento2 páginasProblemas para Que PractiquenJano Jesus AlexAún no hay calificaciones

- Problemas para Que PractiquenDocumento2 páginasProblemas para Que PractiquenJano Jesus AlexAún no hay calificaciones

- Informacion Ii EvaluacionDocumento25 páginasInformacion Ii EvaluacionJano Jesus AlexAún no hay calificaciones

- Preguntas Ia - ExmenDocumento1 páginaPreguntas Ia - ExmenJano Jesus AlexAún no hay calificaciones

- Arquitectura Computadoras LabDocumento13 páginasArquitectura Computadoras LabJano Jesus AlexAún no hay calificaciones

- INFRMACION PARA LA 1ra. EVALUACION CONTINUA PDFDocumento17 páginasINFRMACION PARA LA 1ra. EVALUACION CONTINUA PDFJano Jesus AlexAún no hay calificaciones

- Preguntas Ia - ExmenDocumento1 páginaPreguntas Ia - ExmenJano Jesus AlexAún no hay calificaciones

- Mps 06 Transformada Z PDFDocumento95 páginasMps 06 Transformada Z PDFCarlos AndrésAún no hay calificaciones

- Análisis de rendimiento de procesadores superescalares con predicción de saltosDocumento3 páginasAnálisis de rendimiento de procesadores superescalares con predicción de saltosJano Jesus AlexAún no hay calificaciones

- Sesion2 Practica1 SDocumento11 páginasSesion2 Practica1 SJano Jesus AlexAún no hay calificaciones

- Diseño y funcionamiento de un pulsioxímetro para medir saturación de oxígeno y frecuencia cardíacaDocumento7 páginasDiseño y funcionamiento de un pulsioxímetro para medir saturación de oxígeno y frecuencia cardíacaJano Jesus AlexAún no hay calificaciones

- Formato Ieee para Presentar Art IculosDocumento4 páginasFormato Ieee para Presentar Art IculosZezé DI Mack SilvaAún no hay calificaciones

- IvashDocumento4 páginasIvashMARIO ALBERTO CCOYORI MENDOZAAún no hay calificaciones

- TransfZ ROCDocumento29 páginasTransfZ ROCRoberto Carlos Barragán CamposAún no hay calificaciones

- Debug1. Introducción A Los Microprocesadores de La Familia Intel 8088 - 8086Documento22 páginasDebug1. Introducción A Los Microprocesadores de La Familia Intel 8088 - 8086Jano Jesus AlexAún no hay calificaciones

- Modos de Direccionamiento Del 8086Documento2 páginasModos de Direccionamiento Del 8086Abraham Marcelo Ramirez FloresAún no hay calificaciones

- CIRCUITOS ELECTRONICOS 3 A - Lab 1Documento7 páginasCIRCUITOS ELECTRONICOS 3 A - Lab 1Jano Jesus AlexAún no hay calificaciones

- 8086 (Y)Documento28 páginas8086 (Y)bet192Aún no hay calificaciones

- Manual Ensamblador 8086Documento17 páginasManual Ensamblador 8086Mario R. Cianone100% (1)

- CIRCUITOS ELECTRONICOS 3 A - Lab 1Documento7 páginasCIRCUITOS ELECTRONICOS 3 A - Lab 1Jano Jesus AlexAún no hay calificaciones

- Laboratorio Nro.04Documento4 páginasLaboratorio Nro.04Johan MayaAún no hay calificaciones

- Sensores SCRDocumento30 páginasSensores SCRedadel23Aún no hay calificaciones

- Diseño de Sistemas Digitales y Arquitectura de ComputadorasDocumento332 páginasDiseño de Sistemas Digitales y Arquitectura de Computadorascuauh pimente100% (1)

- Protector Diferencial: Funcionamiento y TiposDocumento4 páginasProtector Diferencial: Funcionamiento y TiposBryan AndresAún no hay calificaciones

- Control Motor DCDocumento45 páginasControl Motor DCAntony Miranda AsencioAún no hay calificaciones

- LABORATORIO 2 DispositivosDocumento12 páginasLABORATORIO 2 DispositivosChristianAún no hay calificaciones

- Ejercicio N°1 - Fundamentación TeóricaDocumento2 páginasEjercicio N°1 - Fundamentación TeóricaAndrés RamosAún no hay calificaciones

- Actividad 09Documento12 páginasActividad 09jcsaadfAún no hay calificaciones

- Diagrama eléctrico de una central hidroeléctricaDocumento27 páginasDiagrama eléctrico de una central hidroeléctricagersonAún no hay calificaciones

- Electromagnetismo 1Documento20 páginasElectromagnetismo 1A Crispin AnibalAún no hay calificaciones

- Identificación de Terminales en Motores de Inducción Trifásicos de 6Documento18 páginasIdentificación de Terminales en Motores de Inducción Trifásicos de 6juan garcia100% (1)

- Pauta Inspeccion Electrica EwDocumento4 páginasPauta Inspeccion Electrica Ewluis carvajalAún no hay calificaciones

- Jesica Santibañez Control6Documento5 páginasJesica Santibañez Control6Jesica SantibañezAún no hay calificaciones

- Arquitecturas HFCDocumento19 páginasArquitecturas HFCEliana Cecilia Vallee PernaleteAún no hay calificaciones

- Vehículos HibridosDocumento6 páginasVehículos HibridosFelipe Mora TroncoAún no hay calificaciones

- Levitador MagneticoDocumento2 páginasLevitador Magneticosamuel alarcon hernandezAún no hay calificaciones

- Banda Lateral UnicaDocumento2 páginasBanda Lateral Unicadj_christ_ortizAún no hay calificaciones

- Interrupcion Grupo 8Documento22 páginasInterrupcion Grupo 8Sergio PerezAún no hay calificaciones

- Instrumentación Electronica I - Puentes de MediciónDocumento11 páginasInstrumentación Electronica I - Puentes de MediciónAlfredo Di LauroAún no hay calificaciones

- Presentacion Medicion CentralizadaDocumento23 páginasPresentacion Medicion CentralizadaJhon Cabello Blas0% (1)

- Programacion AtmegaDocumento6 páginasProgramacion AtmegaJuan G Mamani FernandezAún no hay calificaciones

- ANTENADocumento17 páginasANTENACarolina Rodriguez SolisAún no hay calificaciones

- Métodos para Analizar Los ArmónicosDocumento10 páginasMétodos para Analizar Los ArmónicosCristian BolañosAún no hay calificaciones

- PreviewDocumento20 páginasPreviewKenny Larrea CarrascoAún no hay calificaciones

- Informe PNPDocumento12 páginasInforme PNPSebastián Manosalvas100% (1)

- Qué Es El MicroprocesadorDocumento3 páginasQué Es El Microprocesadorvictor manuel yepes gomezAún no hay calificaciones

- Vivanco Martinez Alfredo: Rmu: 75290 22-02-27 XAXX-010101 005 CFEDocumento2 páginasVivanco Martinez Alfredo: Rmu: 75290 22-02-27 XAXX-010101 005 CFEAlfredo VivancoAún no hay calificaciones

- Resumen Unidad 1 - Fundamentos de electricidad y magnetismo. Máquinas de Corriente DirectaDocumento10 páginasResumen Unidad 1 - Fundamentos de electricidad y magnetismo. Máquinas de Corriente DirectaedgarAún no hay calificaciones

- Leyes de KirchhoffDocumento3 páginasLeyes de KirchhoffJuan Manuel Ortiz VargasAún no hay calificaciones

- Electricidad y Magnetismo N2Documento10 páginasElectricidad y Magnetismo N2RenzoZaldivarCastañedaAún no hay calificaciones