Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Asteroids Deluxe (Signature Analysis Guide) (English)

Cargado por

Darryl RheaDescripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Asteroids Deluxe (Signature Analysis Guide) (English)

Cargado por

Darryl RheaCopyright:

Formatos disponibles

ASTEROIDS DELUXE SIGNATURE ANALYSIS GUIDE

Introduction

This guide is intended as an aid to troubleshooting the Asteroids Deluxe video game PCB. The Signature Analyzer used to produce this guide was an HP5004a. If it is found that the signatures hold up for other makes/models of Signature Analyzers then please let me know and I can add some kind of compatibility list to the document. Suggestions of any kind to improve this document are always welcome. To get the most out of the guide youll need Signature Analyzer (HP5004a) Schematics for Asteroids Deluxe 6502 NOP card (See the separate document 6502NOP for instructions on how to build your own NOP card) IC Clips Some jumper wires (3 or 4 should be sufficient) The scope of the guide is limited in that it will not enable you to fault find the entire PCB. It should, however, be good for the following sections of the PCB: Address Bus Buffers, Address Decoding Circuitry, Clock Circuit, Program ROMs and Data Buffer, Vector Generator Address Selector, Vector Generator RAM Select, Vector Generator ROMs and the Vector Generator Data Buffer. The Clock Circuit test is very limited. The reason being is that I much prefer to check the clock chain with a scope. If you want to figure out the signatures for the Clock Circuit then pass on the information and Ill include it in the document. If you want a detailed description of these sections (and more) please refer to the Asteroids Deluxe schematic / drawing package.

Using The Guide

For those of you who have used Atari Signature Analysis guides before then this should look familiar and theres probably no need to read through this section. For the rest of you, heres a quick run down. Every section should start with the settings for the Analyzer, something like this A. SA Settings for xxxxx Test Probe Start Stop Clock Trigger +ve -ve -ve IC Pin C2-25 C2-25 C2-39 Test Pt.

The probe column refers to either the Start, Stop or Clock probes from the Signature Analyzer. The trigger column sets up the Start/Stop/Clock buttons on the front of the Analyzer. I have used ve to indicate the negative going edge of the pulse (or the falling edge). I have used +ve to indicate the positive going edge of the pulse (or the rising edge). The IC Pin column refers to the point where the appropriate probe should be attached. The Test Pt. column refers to an equivalent Test Point on the boards where the probe may be attached. For example, in the example above the Start probe should be connected to pin 25 of IC C2. The Start button on the front of the Analyzer should be in the fully out position to indicate a positive going edge. Similarly, the Stop probe should be connected to the same IC/Pin as the Start probe but the Stop button on the Analyzer should be pressed in to indicate a negative going edge. The section immediately following the set up procedure contains the signatures for that part of the test. The same structure for the Set Up was employed as explained below. B. Signatures Logic Probe On IC/Pin C1-20 C1-9 C1-12 Signal Name +5V AB0 AB1 Signature

0003 UUUU FFFF

Here, with the Analyzer probe on pin 20 of IC C1 you should get a reading of 0003. On pin 9 of IC C1 you should get a reading of UUUU. And so on. A signature denoted by an (*) indicates that signature may be unstable. Try taking the signature with a 1Kohm resistor connected between the probe tip and +5V.

Down To Business

One of the things I like about this testing method is that you dont need to have the PCB in the cabinet. If you prefer to work in the back of the cabinet then thats fine. If you have a bench/test area with a +5V PSU (as Im sure most of you have), then you can sit comfortably at the bench. Simply connect Ground (pins 1 and 22 on the edge connector) and +5V (pins 2 and 21 on the edge connector) to the PCB and youre ready to start. Just set up the Analyzer as indicated and start probing for those signatures. Always remember to have the Watchdog disabled as this will lead to permanently unstable signatures.

What To Do When You Find An Incorrect Signature

If you find a signature that doesnt match the guide, check your set up first. If your set up is OK then youll need to trace the fault. Rather than having a long winded ramble from me it would be better to look at the following link on Al Kossows page. If you havent already had a look at his site then Id definitely recommend having a look as its a bit of a gold mine. http://www.spies.com/arcade/TE/SigAnalNotes.pdf After youve had a look through the document then you should know enough to start tracing the fault. It should also give you a bit more information on Signature Analysis in general.

Some Common Faults

The two most common faults Ive come across are bad sockets and shorted traces. During the Signature Analysis the bad socket problem is highlighted by the fact that the signatures are unstable. You may get some stable and some not. When you get unstable signatures whilst doing the ROM tests it does not necessarily indicate a bad ROM. Reseating the ROM or replacing the socket is usually a good place to start. The problem of shorted traces is usually down to something being dragged across the board. Sometimes they can be quite hard to see but Signature Analysis shows it up quite good.

Disclaimer

If you toast yourself, your house, your dog, your family or more importantly your video game, then its not my fault. You use the information contained in this guide at your own risk. Good luck.

Document Author

Peter Fyfe

Email (Home) peter@bombjack.freeserve.co.uk Email (Work) peter.fyfe@honeywell.com 6th February 2000

** Tie the Watchdog Disable test point to ground **

2. Address Decoding

A. SA Settings for Address Decoder Test

1. Address Lines

A. SA Settings for Address Buffer Test Probe Start Stop Clock Trigger -ve -ve -ve IC Pin C2-25 C2-25 C2-39 Test Pt.

Probe Start Stop Clock

Trigger -ve -ve -ve

IC Pin C2-25 C2-25 C2-39

Test Pt.

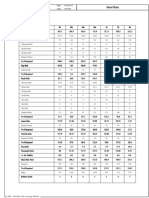

B. Signatures 2 Logic Probe On IC/Pin Signal Name SINP0 SINP1 OPTS PMEM VMEM ZPAGE PKYDCD Signature

B. Signatures Logic Probe On IC/Pin C1-20 C1-9 C1-12 C1-7 C1-14 C1-5 C1-16 C1-3 C1-18 B1-18 B1-14 B1-9 B1-5 B1-7 C2-23 C2-24 C2-25 Signal Name +5V AB0 AB1 AB2 AB3 AB4 AB5 AB6 AB7 AB8 AB9 AB10 AB11 AB12 A13 A14 A15 Signature

0003 UUUU FFFF 8484 P763 1U5P 0356 U759 6F9A 7791 6321 37C5 6U28 4FCA 4868 9UP1 0001

E3-4 E3-5 E3-6 E3-9 E3-10 E3-11 E3-12 D5-10 C5-8 L2-4 L2-5 L2-6 L2-7

AF76 6913 13HP 3282 AH63 7APA P508 3H01 3H02 P933 UH4P A04H 86C1

PROM0 PROM1 PROM2 PROM3

C. SA Settings for Address Decoder Test Probe Start Stop Clock Trigger -ve -ve -ve IC Pin C2-25 C2-25 C3-14 Test Pt.

6MHz

** Tie R/W test point to ground ** D. Signatures Logic Probe On IC/Pin D5-14 Signal Name +5V Signature

00UP

D5-4 E4-8 L5-1 L5-2 L5-3 L5-4 L5-5 L5-6 L5-7 L5-9 B8-13 B8-12 B8-11

0066 (*) 7U7C DMAGO 383U EAADDRL P759 WDCLR 90P8 EXPLODE UA0P A43F EACONTROL U5FA AUDIO 81F6 NOISERESET 1A35 00UP A43F DMARESET A43F

4..Clock Circuit

A. SA Settings for Clock Circuit Test Probe Start Stop Clock Trigger -ve -ve -ve IC Pin C2-25 C2-25 C2-39 Test Pt.

B. Signatures Logic Probe On IC/Pin B3-6 B3-8 B3-10 Signal Name Signature

** Remove jumper from R/W test point **

3KHz 12KHz

763H 8A4U 9720

3..Watchdog Circuit

A. SA Settings for Watchdog Circuit Test Probe Start Stop Clock Trigger -ve -ve -ve IC Pin C2-25 C2-25 C2-39 Test Pt.

5 ROM And Data Lines

A. SA Settings for ROM0 Test (D1) Probe Trigger -ve +ve -ve IC Pin L2-4 L2-4 C2-39 Test Pt.

** Tie L5-12 to ground ** B. Signatures Logic Probe On IC/Pin C5-14 C5-6 D4-6 D4-8 Signal Name +5V Signature

Start Stop Clock

B. Signatures Logic Probe On IC/Pin D1-24 D1-9 D1-10 D1-11 D1-13 D1-14 D1-15 D1-16 D1-17 Signal Name +5V DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 Signature

0003 752C 0398 0000

** Remove jumper from L5-12 **

826P 4869 995C F0AH UF20 A17H 232H 4590 99P1

C. SA Settings for ROM1 Test (E/F1) Probe Start Stop Clock Trigger -ve +ve -ve IC Pin L2-5 L2-5 C2-39 Test Pt.

G. SA Settings for ROM3 Test (J1) Probe Start Stop Clock Trigger -ve +ve -ve IC Pin L2-7 L2-7 C2-39 Test Pt.

D. Signatures Logic Probe On IC/Pin E/F1-9 E/F1-10 E/F1-11 E/F1-13 E/F1-14 E/F1-15 E/F1-16 E/F1-17 Signal Name DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 Signature

H. Signatures Logic Probe On IC/Pin J1-9 J1-10 J1-11 J1-13 J1-14 J1-15 J1-16 J1-17 Signal Name DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 Signature

UOF3 0UCU 0CA5 A391 7F79 U77P H494 052H

373U U96F 76U1 91PP 9P50 A126 10A0 F002

E. SA Settings for ROM2 Test (F/H1)

6. Data Buffer

Probe Start Stop Clock Trigger -ve +ve -ve IC Pin L2-6 L2-6 C2-39 Test Pt. A. SA Settings for data buffer test. 2 Probe Start Stop Clock Signal Name DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 Signature B. Signatures P65C 6FH0 7C88 PC19 94HP CP77 4AF2 7P08 Logic Probe On IC/Pin E2-18 (19) E2-17 (18) E2-16 (17) E2-15 (16) E2-14 (15) E2-13 (14) E2-12 (13) E2-11 (12) Signal Name D0 D1 D2 D3 D4 D5 D6 D7 Signature Trigger -ve +ve -ve IC Pin L2-7 L2-7 C2-39 Test Pt.

F. Signatures Logic Probe On IC/Pin F/H1-9 F/H1-10 F/H1-11 F/H1-13 F/H1-14 F/H1-15 F/H1-16 F/H1-17

373U U96F 76U1 91PP 9P50 A126 10A0 F002

** The numbers in brackets are the pin assignments when an AM8304B is used as opposed to a 74LS245 **

8. Vector Generator RAM

A. SA Settings for VG RAM Test Probe Start Stop Clock Trigger -ve -ve -ve IC Pin C2-25 C2-25 C2-39 Test Pt.

7. Vector Generator Address Selector

A. SA Settings for VG Address Sel Test Probe Start Stop Clock Trigger -ve -ve -ve IC Pin C2-25 C2-25 C2-39 Test Pt.

** Tie K2-1 to ground ** 2 B Signatures Logic Probe On IC/Pin M4-3 M4-6 L4-4 Signal Name Signature

** Tie K2-1 to ground ** B Signatures Logic Probe On IC/Pin K2-1 K2-4 K2-12 L2-10 L2-11 L2-12 F2-9 F2-7 F2-4 F2-12 H2-12 H2-4 H2-7 H2-9 J2-9 J2-12 J2-4 Signal Name +5V AM11 AM12 VROM2 VROM1 VRAM AM0 AM1 AM2 AM3 AM4 AM5 AM6 AM7 AM8 AM9 AM10 Signature

98H1 32U8 37C6

0003 6U28 4FCA F501 P693 AA2A UUUU FFFF 8484 P763 1U5P 0356 U759 6F9A 7791 6321 37C5

9. Vector Generator ROM

A. SA Settings for VG ROM1 Test (R2) Probe Start Stop Clock Trigger -ve +ve -ve IC Pin L2-11 L2-11 C2-39 Test Pt.

** Tie K2-1 to ground ** B Signatures Logic Probe On IC/Pin R2-24 R2-9 R2-10 R2-11 R2-13 R2-14 R2-15

4

Signal Name +5V DDMA0 DDMA1 DDMA2 DDMA3 DDMA4 DDMA5

Signature

826P A13F 37H3 9F59 69HU 9277 5530

R2-16 R2-17

DDMA6 DDMA7

725P 2604

10. Vector Generator Data Buffer

A. SA Settings for VG Data Buffer test

C. SA Settings for ROM2 Test (N/P2) Probe Probe Start Stop Clock Trigger -ve +ve -ve IC Pin L2-10 L2-10 C2-39 Test Pt. Start Stop Clock -ve +ve -ve L2-10 L2-10 C2-39 Trigger IC Pin Test Pt.

B Signatures ** Tie K2-1 to ground ** D Signatures Logic Probe On IC/Pin N/P2-9 N/P2-10 N/P2-11 N/P2-13 N/P2-14 N/P2-15 N/P2-16 N/P2-17 Signal Name Signature Logic Probe On IC/Pin P1-18 (19) P1-17 (18) P1-16 (17) P1-15 (16) P1-14 (15) P1-13 (14) P1-12 (13) P1-11 (12) Signal Name DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 Signature

DDMA0 6334 DDMA1 2AH5 DDMA2 3431 DDMA3 F67C DDMA4 5H7C DDMA5 7FFH DDMA6 88U2 DDMA7 A433

6334 2AH5 3431 F67C 5H7C 7FFH 88U2 A433

* The numbers in brackets are the pin assignments when an AM8304B is used as opposed to a 74LS245 *

También podría gustarte

- 101 ObservationsoftheEffectsoftheMoonsNodesonthePersonalityDocumento4 páginas101 ObservationsoftheEffectsoftheMoonsNodesonthePersonalitySachin MathurAún no hay calificaciones

- Lucky Stars NumberDocumento215 páginasLucky Stars NumbersadrotgasAún no hay calificaciones

- Astrology For The Weak . . . The World's First and Only Multiple Choice HoroscopesDe EverandAstrology For The Weak . . . The World's First and Only Multiple Choice HoroscopesAún no hay calificaciones

- Karma and AstrologyDocumento3 páginasKarma and AstrologyproddaturAún no hay calificaciones

- Keys to the Kingdom II: Ancient Astrology A Hidden Secret in the Bible: Reimagining Genesis to Revelation - End of Days Prophecies RevealedDe EverandKeys to the Kingdom II: Ancient Astrology A Hidden Secret in the Bible: Reimagining Genesis to Revelation - End of Days Prophecies RevealedAún no hay calificaciones

- SEGINUSDocumento7 páginasSEGINUSNina Elezovic SimunovicAún no hay calificaciones

- Nanotechnology and VaccinesDocumento11 páginasNanotechnology and Vaccinespranchish100% (1)

- Retrograde Planets: What They Show About Past Lives by Judy CollinsDocumento3 páginasRetrograde Planets: What They Show About Past Lives by Judy CollinsRao LakkojuAún no hay calificaciones

- Mars Activation of Eclipse Points NodesDocumento32 páginasMars Activation of Eclipse Points NodesmichaAún no hay calificaciones

- Saturn UranusDocumento11 páginasSaturn Uranusdositheus11100% (1)

- The Asteroids Or Minor Planets Between Mars and Jupiter.De EverandThe Asteroids Or Minor Planets Between Mars and Jupiter.Calificación: 4 de 5 estrellas4/5 (1)

- Saturn 11thDocumento7 páginasSaturn 11thRacheAún no hay calificaciones

- Kaal Sarp YogDocumento2 páginasKaal Sarp YogsainergyAún no hay calificaciones

- EclipsesDocumento6 páginasEclipsesAycan ÖzenbaşAún no hay calificaciones

- Harness House 12Documento3 páginasHarness House 12Dayakar Devaru100% (2)

- Beginning CosmodynesDocumento2 páginasBeginning CosmodynesDilip KiningeAún no hay calificaciones

- AstrologyDocumento331 páginasAstrologySuraj GuptaAún no hay calificaciones

- Conversing With Heaven Carter Memorial Lecture 2010Documento10 páginasConversing With Heaven Carter Memorial Lecture 2010shadowgraphAún no hay calificaciones

- Astrological Ages As An Accurate and Effective Model of HistoryDocumento15 páginasAstrological Ages As An Accurate and Effective Model of HistoryMerlin PitAún no hay calificaciones

- Mystic Powers of KalSarp YogaDocumento2 páginasMystic Powers of KalSarp Yogaगणेश पराजुलीAún no hay calificaciones

- The Jupiter-Saturn ConjunctionDocumento7 páginasThe Jupiter-Saturn Conjunctionmurx2100% (1)

- The Messageofthe StarsDocumento703 páginasThe Messageofthe StarsAbhi AbhijithAún no hay calificaciones

- Cause For Delay in MarriageDocumento7 páginasCause For Delay in Marriagedeepak joshiAún no hay calificaciones

- The Harmonic Concordance 1Documento56 páginasThe Harmonic Concordance 1lionroadAún no hay calificaciones

- The Cosmic T Square 240510Documento8 páginasThe Cosmic T Square 240510Anthony Writer0% (1)

- Astrology Lesson 1Documento4 páginasAstrology Lesson 1Valentin BadeaAún no hay calificaciones

- Pitru PakshaDocumento3 páginasPitru PakshanieotyagiAún no hay calificaciones

- 7th Degree of Aquarius-Leo Axis PDFDocumento9 páginas7th Degree of Aquarius-Leo Axis PDFahaAún no hay calificaciones

- Astrological Articles - 49Documento27 páginasAstrological Articles - 49Mehul JaniAún no hay calificaciones

- The Science of Astrology.Documento9 páginasThe Science of Astrology.Dinesh Vallecha0% (1)

- Salvador Dali: Strong Medium WeakDocumento5 páginasSalvador Dali: Strong Medium WeaknikirajendranAún no hay calificaciones

- Astrology, Guns, America and The Future - Jessica Adams Psychic AstrologerDocumento1 páginaAstrology, Guns, America and The Future - Jessica Adams Psychic AstrologerJiaqing ZhangAún no hay calificaciones

- SkyGazer - Chapter 14Documento11 páginasSkyGazer - Chapter 14MediaPirate9787100% (1)

- Year of The Water Dragon Yearly Forecast-2011-12!31!14!29!39Documento3 páginasYear of The Water Dragon Yearly Forecast-2011-12!31!14!29!39nikkig1982Aún no hay calificaciones

- Angelina Jolie Shad BalaDocumento1 páginaAngelina Jolie Shad BalaGanesan S100% (1)

- Wikipedia - List of Greek Mythological FiguresDocumento29 páginasWikipedia - List of Greek Mythological FiguresXangotAún no hay calificaciones

- The Fifth HouseDocumento10 páginasThe Fifth HouseYo DraAún no hay calificaciones

- Jupiter UranusDocumento2 páginasJupiter UranusPhalgun BalaajiAún no hay calificaciones

- Astrological Keyword System of Analyzing Character and Dest 1Documento10 páginasAstrological Keyword System of Analyzing Character and Dest 1Maha DeviAún no hay calificaciones

- Magical Aspects - Pat GeislerDocumento2 páginasMagical Aspects - Pat GeislerJust_BojanaAún no hay calificaciones

- The Fallen Madonna Story of Zosma: by Miloš TomićDocumento4 páginasThe Fallen Madonna Story of Zosma: by Miloš TomićMilos TomicAún no hay calificaciones

- Astrological TermsDocumento11 páginasAstrological Termssonali_krishAún no hay calificaciones

- Narada Purana 2 (AITM)Documento432 páginasNarada Purana 2 (AITM)SubalAún no hay calificaciones

- Science Newsletter LatestDocumento2 páginasScience Newsletter LatestDarryl RheaAún no hay calificaciones

- Joint Release U.S. Department of Housing and Urban DevelopmentDocumento6 páginasJoint Release U.S. Department of Housing and Urban DevelopmentDarryl RheaAún no hay calificaciones

- Pa 2014seasonchangesDocumento5 páginasPa 2014seasonchangesDarryl RheaAún no hay calificaciones

- The End of Amnesty in Uganda: Implications For LRA DefectionsDocumento8 páginasThe End of Amnesty in Uganda: Implications For LRA DefectionsDarryl RheaAún no hay calificaciones

- S O S Europe Report Web 02Documento24 páginasS O S Europe Report Web 02Darryl RheaAún no hay calificaciones

- Fact Sheet: A O C - U SDocumento2 páginasFact Sheet: A O C - U SDarryl RheaAún no hay calificaciones

- The Week at Fuller Village March 24 - 30Documento8 páginasThe Week at Fuller Village March 24 - 30Darryl RheaAún no hay calificaciones

- United States Marine MRCP 3-1a - 23 Feb 1999 - Part01Documento124 páginasUnited States Marine MRCP 3-1a - 23 Feb 1999 - Part01Darryl Rhea100% (1)

- Public NoticesDocumento1 páginaPublic NoticesDarryl RheaAún no hay calificaciones

- Think HackerDocumento10 páginasThink HackerDarryl RheaAún no hay calificaciones

- The Bomb For Beginners: Michael RühleDocumento4 páginasThe Bomb For Beginners: Michael RühleDarryl RheaAún no hay calificaciones

- United Sataes Army FM 21-11-27 October 1988 - Part03Documento44 páginasUnited Sataes Army FM 21-11-27 October 1988 - Part03Darryl RheaAún no hay calificaciones

- United Sataes Army FM 21-11-27 October 1988 - Part02Documento42 páginasUnited Sataes Army FM 21-11-27 October 1988 - Part02Darryl RheaAún no hay calificaciones

- Sonora LA281R-T DBS Satellite Cable Amplifier Spec SheetDocumento4 páginasSonora LA281R-T DBS Satellite Cable Amplifier Spec SheetDavid WardAún no hay calificaciones

- Nehru Place CTC PricelistDocumento7 páginasNehru Place CTC PricelistAnonymous nqIC9a8BIAún no hay calificaciones

- How To Config Android For WorkDocumento9 páginasHow To Config Android For WorkAlexandru LucaAún no hay calificaciones

- Company Sim Card Authorization Letter CompleteDocumento1 páginaCompany Sim Card Authorization Letter CompleteLoGan Ben100% (5)

- Fibre Tube Colour Codes Sheath Colours 0713 eDocumento1 páginaFibre Tube Colour Codes Sheath Colours 0713 edugoprstiAún no hay calificaciones

- Sap Abap QUESTION /ANSWERDocumento3 páginasSap Abap QUESTION /ANSWERVikrant KaushalAún no hay calificaciones

- 560CID11 Product InfoDocumento2 páginas560CID11 Product InfoGilbert H. Quiroga G.Aún no hay calificaciones

- Whats New in TDLDocumento225 páginasWhats New in TDLtaraknath1984Aún no hay calificaciones

- Vol 14 No 2 - September 2014Documento149 páginasVol 14 No 2 - September 2014ijcsbiAún no hay calificaciones

- MOLiCafe User Manual WebDocumento32 páginasMOLiCafe User Manual WebMarvin de GuzmanAún no hay calificaciones

- Professor Messer Comptia 220 901 902 A Plus Course Notes v0115Documento57 páginasProfessor Messer Comptia 220 901 902 A Plus Course Notes v0115Pedro75% (4)

- SuiteTalkWebServicesPlatformGuide (IMPRESA)Documento346 páginasSuiteTalkWebServicesPlatformGuide (IMPRESA)ZettoX0% (1)

- SfsdfsDocumento15 páginasSfsdfsNickiPaulSorianoPomayaAún no hay calificaciones

- Single Frequency Network Overview ENENSYSDocumento9 páginasSingle Frequency Network Overview ENENSYStariqahmadkhan7557Aún no hay calificaciones

- UG 2-A Method To Implement Scheduling and Prioritizing of Messages in VANetsDocumento11 páginasUG 2-A Method To Implement Scheduling and Prioritizing of Messages in VANetsSaiKumarAún no hay calificaciones

- LCG - Tcel For WbtsDocumento15 páginasLCG - Tcel For WbtsthaidvAún no hay calificaciones

- SolidThinking Embed 20171 Installation GuideDocumento9 páginasSolidThinking Embed 20171 Installation Guidealejo0091Aún no hay calificaciones

- CISM Practice Questions To Prep For The ExamDocumento25 páginasCISM Practice Questions To Prep For The ExamSamuel GetachewAún no hay calificaciones

- SIMATIC PCS 7 Positioning eDocumento28 páginasSIMATIC PCS 7 Positioning eami89ami100% (1)

- Session 04 - Homework-1Documento3 páginasSession 04 - Homework-1Thanh TranAún no hay calificaciones

- Organization of Subscriber Data 23008-g30Documento154 páginasOrganization of Subscriber Data 23008-g30derrida2897Aún no hay calificaciones

- Ehealth Administration EnuDocumento405 páginasEhealth Administration EnuAldo Ricardo Huamani ManyaAún no hay calificaciones

- RockAIR Product Information SheetDocumento1 páginaRockAIR Product Information Sheetarfariz NhAún no hay calificaciones

- User GuideDocumento5 páginasUser GuideAmanda DixonAún no hay calificaciones

- STI S-1413 EsquemaDocumento37 páginasSTI S-1413 EsquemaElvis SousaAún no hay calificaciones

- Push TechnologyDocumento21 páginasPush TechnologyPrasanth Naik0% (1)

- Aradial ManualDocumento101 páginasAradial ManualVivek YadavAún no hay calificaciones

- Setup and Reference Guide: HP Smart TankDocumento144 páginasSetup and Reference Guide: HP Smart TankRake RameAún no hay calificaciones

- Security in Openflow-Based SDN, Opportunities and ChallengesDocumento23 páginasSecurity in Openflow-Based SDN, Opportunities and Challengesjainam lathiyaAún no hay calificaciones

- Connectrix - Brocade Departmental Firmware Upgrade Procedures-DS-6510BDocumento19 páginasConnectrix - Brocade Departmental Firmware Upgrade Procedures-DS-6510BSantosh SharmaAún no hay calificaciones