Documentos de Académico

Documentos de Profesional

Documentos de Cultura

CM8870/70C CMOS Integrated DTMF Receiver: California Micro Devices

Cargado por

pilar12345678Descripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

CM8870/70C CMOS Integrated DTMF Receiver: California Micro Devices

Cargado por

pilar12345678Copyright:

Formatos disponibles

2000 California Micro Devices Corp. All rights reserved.

9/28/2000 1

CM8870/70C CALIFORNIA MICRO DEVICES

215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com

CMOS Integrated DTMF Receiver

Features

Full DTMF receiver

Less than 35mW power consumption

Industrial temperature range

Uses quartz crystal or ceramic resonators

Adjustable acquisition and release times

18-pin DIP, 18-pin DIP EIAJ, 18-pin SOIC, 20-pin

PLCC

CM8870C

Power down mode

Inhibit mode

Buffered OSC3 output (PLCC package only)

CM8870C is fully compatible with CM8870 for 18-pin

devices by grounding pins 5 and 6

Product Description

The CAMD CM8870/70C provides full DTMF receiver capability by integrating both the bandsplit filter and digital

decoder functions into a single 18-pin DIP, SOIC, or 20-pin PLCC package. The CM8870/70C is manufactured using

state-of-the-art CMOS process technology for low power consumption (35mW, max.) and precise data handling. The

filter section uses a switched capacitor technique for both high and low group filters and dial tone rejection. The

CM8870/70C decoder uses digital counting techniques for the detection and decoding of all 16 DTMF tone pairs into a

4-bit code. This DTMF receiver minimizes external component count by providing an on-chip differential input ampli-

fier, clock generator, and a latched three-state interface bus. The on-chip clock generator requires only a low cost TV

crystal or ceramic resonator as an external component.

Applications

PABX

Central office

Mobile radio

Remote control

Remote data entry

Call limiting

Telephone answering systems

Paging systems

+##'

2000 California Micro Devices Corp. All rights reserved.

9/28/2000 215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com 2

CALIFORNIA MICRO DEVICES CM8870/70C

This device contains input protection

against damage due to high static

voltages or electric fields; however,

precautions should be taken to avoid

application of voltages higher than the

maximum rating.

Notes:

1. Exceeding these ratings may cause

permanent damage, functional

operation under these conditions is

not implied.

Absolute Maximum Ratings: (Note 1)

DC Characteristics: All voltages referenced to V

SS

, V

DD

= 5.0V 5%, T

A

= -40C to +85C unless otherwise noted.

Operating Characteristics: All voltages referenced to V

SS

, V

DD

= 5.0V 5%, T

A

= -40C to +85C unless otherwise noted.

Gain Setting Amplifier

S C I T S I R E T C A R A H C C D

r e t e m a r a P l o b m y S n i M p y T x a M s t i n U s n o i t i d n o C t s e T

e g a t l o V y l p p u S g n i t a r e p O V

D D

5 7 . 4 5 2 . 5 V

t n e r r u C y l p p u S g n i t a r e p O I

D D

0 . 3 0 . 7 A m

t n e r r u C y l p p u S y b d n a t S I

Q D D

5 2 A V = D P

D D

n o i t p m u s n o C r e w o P P

O

5 1 5 3 W m V ; z H M 9 7 5 . 3 = f

D D

V 0 . 5 =

e g a t l o V t u p n I l e v e L w o L V

L I

5 . 1 V V

D D

V 0 . 5 =

e g a t l o V t u p n I l e v e L h g i H V

H I

5 . 3 V V

D D

V 0 . 5 =

t n e r r u C e g a k a e L t u p n I I

H I

L /

L I

1 . 0 A V

N I

V =

S S

V =

D D

) 1 e t o N (

E O T n o t n e r r u C ) e c r u o S ( p U l l u P I

o s

5 . 6 0 2 A V , V 0 = E O T

D D

V 0 . 5 =

) - N I , + N I ( , e c n a d e p m I t u p n I R

N I

8 0 1 M z H K 1 @

e g a t l o V d l o h s e r h T g n i r e e t S V

t s T

2 . 2 5 . 2 V V

D D

V 0 . 5 =

e g a t l o V t u p t u O l e v e L w o L V

L O

3 0 . 0 V V

D D

d a o L o N , V 0 . 5 =

e g a t l o V t u p t u O l e v e L h g i H V

H O

7 9 . 4 V V

D D

d a o L o N , V 0 . 5 =

t n e r r u C ) k n i S ( w o L t u p t u O I

L O

0 . 1 5 . 2 A m V

T U O

V 4 . 0 =

t n e r r u C ) e c r u o S ( h g i H t u p t u O I

H O

4 . 0 8 . 0 A m V

T U O

V 6 . 4 =

e g a t l o V t u p t u O

V

F E R

V

F E R

4 . 2 7 . 2 V V

D D

d a o L o N , V 0 . 5 =

e c n a t s i s e R t u p t u O R

R O

0 1

S G N I T A R M U M I X A M E T U L O S B A

r e t e m a r a P l o b m y S e u l a V

V ( e g a t l o V y l p p u S r e w o P

D D

-

V

S S

)

V

D D

x a M V 0 . 6

n i P y n a n o e g a t l o V c d V V

S S

V o t V 3 . 0 -

D D

V 3 . 0 +

n i P y n a n o t n e r r u C I

D D

x a M A m 0 1

e r u t a r e p m e T g n i t a r e p O T

A

C 5 8 + o t C 0 4 -

e r u t a r e p m e T e g a r o t S T

S

C 0 5 1 + o t C 5 6 -

S C I T S I R E T C A R A H C G N I T A R E P O

r e t e m a r a P l o b m y S n i M p y T x a M s t i n U s n o i t i d n o C t s e T

t n e r r u C e g a k a e L t u p n I I

N I

0 0 1 A n V

S S

V <

N I

V <

D D

e c n a t s i s e R t u p n I R

N I

0 1 M

e g a t l o V t e s f f O t u p n I V

S O

5 2 V m

n o i t c e j e R y l p p u S r e w o P R R S P 0 5 B d ) 2 1 e t o N ( z H K 1

n o i t c e j e R e d o M n o m m o C R R M C 0 4 B d I V < V 0 . 3 -

N

V 0 . 3 <

n i a G e g a t l o V p o o L n e p O C D A

L O V

2 3 B d

h t d i w d n a B n i a G y t i n U p o o L n e p O c f 3 . 0 z H M

g n i w S e g a t l o V t u p t u O V

O

0 . 4 V

P - P

R

L

V o t W K 0 0 1

S S

) S G ( d a o L e v i t i c a p a C m u m i x a M C

L

0 0 1 F p

) S G ( d a o L e v i t s i s e R m u m i x a M R

L

0 5 K

) d a o L o N ( e g n a R e d o M n o m m o C m c V 5 . 2 V

P - P

d a o L o N

2000 California Micro Devices Corp. All rights reserved.

9/28/2000 3

CM8870/70C CALIFORNIA MICRO DEVICES

215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com

AC Characteristics: All voltages referenced to V

SS

, V

DD

=5.0V 5%, T

A

=-40C to +85C, f

CLK

=3.579545 MHz using

test circuit (Fig. 1) unless otherwise noted.

Notes:

1. dBm = decibels above or below a reference power

of 1 mW into a 600 ohm load.

2. Digit sequence consists of all 16 DTMF tones.

3. Tone duration = 40mS. Tone pause = 40 mS.

4. Nominal DTMF frequencies are used.

5. Both tones in the composite signal have

an equal amplitude.

6. Bandwidth limited (0 to 3 KHz) Gaussian Noise.

7. The precise dial tone frequencies are

(350 Hz and 440 Hz) 2%.

8. For an error rate of better than 1 in 10,000

9. Referenced to lowest level frequency component

in DTMF signal.

10. Minimum signal acceptance level is measured with

specified maximum frequency deviation.

11. Input pins defined as IN+, IN-, and TOE.

12. External voltage source used to bias V

REF

.

13. This parameter also applies to a third tone injected onto

the power supply.

14. Referenced to Figure 1. Input DTMF tone level

at -28 dBm.

S C I T S I R E T C A R A H C C A

r e t e m a r a P l o b m y S n i M p y T x a M s t i n U s e t o N

s l e v e L l a n g i S t u p n I d i l a V

) l a n g i s e t i s o p m o c f o e n o t h c a e (

9 2 - 1 + m B d

8 , 5 , 4 , 3 , 2 , 1

5 . 7 2 9 6 8 V m

S M R

t p e c c A t s i w T e v i t i s o P 0 1 B d

8 , 4 , 3 , 2

t p e c c A t s i w T e v i t a g e N 0 1 B d

t i m i L t p e c c A n o i t a i v e D . q e r F z H 2 % 5 . 1 . m o N 0 1 , 8 , 5 , 3 , 2

t i m i L t c e j e R n o i t a i v e D . q e r F % 5 . 3 . m o N 5 , 3 , 2

e c n a r e l o T e n o T d r i h T 6 1 - B d 4 1 , 3 1 , 9 , 8 , 5 , 4 , 3 , 2

e c n a r e l o T e s i o N 2 1 - B d 9 , 8 , 6 , 5 , 4 , 3 , 2

e c n a r e l o T e n o T l a i D 2 2 + B d 9 , 8 , 7 , 5 , 4 , 3 , 2

e m i T n o i t c e t e D t n e s e r P e n o T t

P D

5 8 4 1 S m

o t r e f e R

m a r g a i D g n i m i T

e m i T n o i t c e t e D t n e s b A e n o T t

A D

5 . 0 3 5 . 8 S m

t p e c c A n o i t a r u D e n o T n i M t

C E R

0 4 S m

) e l b a t s u j d A r e s U (

e r a n w o h s s e m i T

h t i w d e n i a t b o

) 1 . g i F n i t i u c r i c

t c e j e R n o i t a r u D e n o T x a M t

C E R

0 2 S m

t p e c c A e s u a P t i g i d r e t n I . n i M t

D I

0 4 S m

t c e j e R e s u a P t i g i d r e t n I . x a M t

O D

0 2 S

) Q o t t S ( y a l e D n o i t a g a p o r P t

Q P

6 1 1 S

V = E O T

D D

) D t S o t t S ( y a l e D n o i t a g a p o r P t

S P

t

D

9 6 1 S

) D t S o t Q ( p U t e S a t a D t u p t u O t

S Q

t

D

4 . 3 S

) Q o t E O T ( y a l e D n o i t a g a p o r P

e l b a n E t

E T P

0 5 S n

R

L

K 0 1 =

C

L

F p 0 5 =

e l b a s i D t

D T P

0 0 3 S n

y c n e u q e r F k c o l C / l a t s y r C f

K L C

9 5 7 5 . 3 5 9 7 5 . 3 1 3 8 5 . 3 z H M

) 2 C S O ( t u p t u O k c o l C e v i t i c a p a C

d a o L

C

O L

0 3 F p

2000 California Micro Devices Corp. All rights reserved.

9/28/2000 215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com 4

CALIFORNIA MICRO DEVICES CM8870/70C

Explanation of Events

A) Tone bursts detected, tone duration invalid, outputs not

updated.

B) Tone #n detected, tone duration valid, tone decoded

and latched in outputs.

C) End of tone #n detected, tone absent duration valid,

outputs remain latched until next valid tone.

D) Outputs switched to high impedance state.

E) Tone #n + 1 detected, tone duration valid, tone decoded

and latched in outputs (currently high impedance).

F) Acceptable dropout of tone #n + 1, tone absent duration

invalid, outputs remain latched.

G) End of tone #n + 1 detected, tone absent duration valid,

outputs remain latched until next valid tone.

Explanation of Symbols

V

IN

DTMF composite input signal.

ESt Early Steering Output. Indicates detection

of valid tone frequencies.

St/GT Steering input/guard time output. Drives

external RC timing circuit.

Q1-Q4 4-bit decoded tone output.

StD Delayed Steering Output. Indicates that

valid frequencies have been present/absent

for the required guard time, thus constituting

a valid signal.

TOE Tone Output Enable (input). A low level

shifts Q1-Q4 to its high impedance state.

t

REC

Maximum DTMF signal duration not

detected as valid.

t

REC

Minimum DTMF signal duration required

for valid recognition.

t

ID

Minimum time between valid DTMF signals.

t

DO

Maximum allowable drop-out during valid

DTMF signal.

t

DP

Time to detect the presence of valid

DTMF signals.

t

DA

Time to detect the absence of valid

DTMF signals.

t

GTP

Guard time, tone present.

t

GTA

Guard time, tone absent.

2000 California Micro Devices Corp. All rights reserved.

9/28/2000 5

CM8870/70C CALIFORNIA MICRO DEVICES

215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com

Functional Description

The CAMD CM8870/70C DTMF Integrated Receiver provides

the design engineer with not only low power consumption, but

high performance in a small 18-pin DIP, SOIC, or 20-pin PLCC

package configuration. The CM8870/70Cs internal architec-

ture consists of a bandsplit filter section which separates the

high and low tones of the received pair, followed by a digital

decode (counting) section which verifies both the frequency

and duration of the received tones before passing the result-

ant 4-bit code to the output bus.

Filter Section

Separation of the low-group and high-group tones is achieved

by applying the dual-tone signal to the inputs of two 9

th

-order

switched capacitor bandpass filters. The bandwidths of these

filters correspond to the bands enclosing the low-group and

high-group tones (See Figure 3). The filter section also

incorporates notches at 350 Hz and 440 Hz which provides

excellent dial tone rejection. Each filter output is followed by a

single order switched capacitor section which smooths the

signals prior to limiting. Signal limiting is performed by high-

gain comparators. These comparators are provided with a

hysteresis to prevent detection of unwanted low-level signals

and noise. The outputs of the comparators provide full-rail

logic swings at the frequencies of the incoming tones.

Decoder Section

The CM8870/70C decoder uses a digital counting technique

to determine the frequencies of the limited tones and to verify

that these tones correspond to standard DTMF frequencies.

A complex averaging algorithm is used to protect against tone

simulation by extraneous signals (such as voice) while

providing tolerance to small frequency variations. The

averaging algorithm has been developed to ensure an

optimum combination of immunity to talk-off and tolerance to

the presence of interfering signals (third tones) and noise.

When the detector recognizes the simultaneous presence of

two valid tones (known as signal condition), it raises the

Early Steering flag (ESt). Any subsequent loss of signal

condition will cause ESt to fall.

Steering Circuit

Before the registration of a decoded tone pair, the receiver

checks for a valid signal duration (referred to as character-

recognition-condition). This check is performed by an

external RC time constant driven by E

St

. A logic high on ESt

causes V

C

(See Figure 4) to rise as the capacitor discharges.

Providing signal condition is maintained (ESt remains high) for

the validation period (t

GTP

), V

C

reaches the threshold (V

TSt

) of

the steering logic to register the tone pair, thus latching its

corresponding 4-bit code (See Figure 2) into the output latch.

At this point, the GT output is activated and drives VC to V

DD

.

GT continues to drive high as long as ESt remains high,

signaling that a received tone pair has been registered. The

contents of the output latch are made available on the 4-bit

output bus by raising the three-state control input (TOE) to a

logic high. The steering circuit works in reverse to validate the

interdigit pause between signals. Thus, as well as rejecting

signals too short to be considered valid, the receiver will

tolerate signal interruptions (drop outs) too short to be

considered a valid pause. This capability together with the

capability of selecting the steering time constants externally,

allows the designer to tailor performance to meet a wide

variety of system requirements.

Guard Time Adjustment

In situations which do not require independent selection of

receive and pause, the simple steering circuit of Figure 4 is

applicable. Component values are chosen according to the

following formula:

t

REC

= t

DP

+ t

GTP

t

GTP

0.67 RC

The value of t

DP

is a parameter of the device and t

REC

is the

minimum signal duration to be recognized by the receiver. A

value for C of 0.1 uF is recommended for most applications,

leaving R to be selected by the designer. For example, a

suitable value of R for a t

REC

of 40 milliseconds would be 300K.

A typical circuit using this steering configuration is shown in

Figure 1. The timing requirements for most telecommunica-

tion applications are satisfied with this circuit. Different

steering arrangements may be used to select independently

the guardtimes for tone-present (t

GTP

) and tone absent (t

GTA

).

This may be necessary to meet system specifications which

place both accept and reject limits on both tone duration and

interdigit pause.

Guard time adjustment also allows the designer to tailor

system parameters such as talk-off and noise immunity.

Increasing t

REC

improves talk-off performance, since it reduces

the probability that tones simulated by speech will maintain

signal condition for long enough to be registered. On the

other hand, a relatively short t

REC

with a long t

DO

would be

appropriate for extremely noisy environments where fast

acquisition time and immunity to drop-outs would be require-

ments. Design information for guard time adjustment is shown

in Figure 5.

Input Configuration

The input arrangement of the CM8870/70C provides a

differential input operational amplifier as well as a bias source

(V

REF

) which is used to bias the inputs at mid-rail.

Provision is made for connection of a feedback resistor to the

op-amp output (GS) for adjustment of gain.

In a single-ended configuration, the input pins are connected

as shown in Figure 1, with the op-amp connected for unity

gain and VREF biasing the input at V

DD

. Figure 6 shows the

differential configuration, which permits the adjustment of gain

with the feedback resistor R5.

Clock Circuit

The internal clock circuit is completed with the addition of a

standard television color burst crystal or ceramic resonator

having a resonant frequency of 3.579545 MHz. The

CM8870C in a PLCC package has a buffered oscillator output

(OSC3) that can be used to drive clock inputs of other devices

such as a microprocessor or other CM887Xs as shown in

Figure 7. Multiple CM8870/70Cs can be connected as shown

in figure 8 such that only one crystal or resonator is required.

2000 California Micro Devices Corp. All rights reserved.

9/28/2000 215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com 6

CALIFORNIA MICRO DEVICES CM8870/70C

Pin Function Table

Figure 1.

Single Ended Input Configuration

Figure 2.

FunctionaI Diode 1abIe

All resistors are 1%tolerance.

All capacitors are 5% tolerance.

F

W O L

F

H G I H

Y E K W O T Q

4

Q

3

Q

2

Q

1

7 9 6 9 0 2 1 1 H 0 0 0 1

7 9 6 6 3 3 1 2 H 0 0 1 0

7 9 6 7 7 4 1 3 H 0 0 1 1

0 7 7 9 0 2 1 4 H 0 1 0 0

0 7 7 6 3 3 1 5 H 0 1 0 1

0 7 7 7 7 4 1 6 H 0 1 1 0

2 5 8 9 0 2 1 7 H 0 1 1 1

2 5 8 6 3 3 1 8 H 1 0 0 0

2 5 8 7 7 4 1 9 H 1 0 0 1

1 4 9 9 0 2 1 0 H 1 0 1 0

1 4 9 6 3 3 1 H 1 0 1 1

1 4 9 7 7 4 1 # H 1 1 0 0

7 9 6 3 3 6 1 A H 1 1 0 1

0 7 7 3 3 6 1 B H 1 1 1 0

2 5 8 3 3 6 1 C H 1 1 1 1

1 4 9 3 3 6 1 D H 0 0 0 0

- - Y N A L Z Z Z Z

e c n a d e p m I h g i H = Z , h g i H c i g o L = H , w o L c i g o l = L

N O I T C N U F N I P

e m a N n o i t p i r c s e D

+ N I t u p n I g n i t r e v n i - n o N

r e i f i l p m a l a i t n e r e f f i d d n e - t n o r f e h t o t n o i t c e n n o C

- N I t u p n I g n i t r e v n I

S G t c e l e S n i a G

f o n o i t c e n n o c r o f r e i f i l p m a l a i t n e r e f f i d d n e - t n o r f f o t u p t u o o t s s e c c a s e v i G

. r o t s i s e r k c a b d e e f

V

F E R

V y l l a n i m o n ( t u p t u o e g a t l o v e c n e r e f e R

D D

. l i a r - d i m t a s t u p n i e h t s a i b o t d e s u e b y a M . ) 2 /

H N I D d n a , C , B , A s y e k s t n e s e r p e r s e n o t f o n o i t c e t e d s t i b i h n I

3 C S O . t u p t u o r o t a l l i c s o d e r e f f u b l a t i g i D

D P n w o D r e w o P . r o t a l l i c s o e h t s t i b i h n i d n a e c i v e d e h t n w o d s r e w o p h g i h c i g o L

1 C S O t u p n I k c o l C

. r o t a l l i c s o l a n r e t n i s e t e l p m o c s n i p e s e h t n e e w t e b d e t c e n n o c l a t s y r c z H M 5 4 5 9 7 5 . 3

2 C S O t u p t u O k c o l C

V

S S

. ) V O o t d e t c e n n o c y l l a m r o n ( y l p p u s r e w o p e v i t a g e N

E O T Q s t u p t u o e h t s e l b a n e h g i h c i g o L . ) t u p n i ( e l b a n e t u p t u o e t a t s - e e r h T

1

Q -

4

. p u - l l u p l a n r e t n I .

Q

1

Q

2

Q

3

Q

4

r i a p e n o t d i l a v t s a l e h t o t g n i d n o p s e r r o c e d o c e h t s e d i v o r p , E O T y b d e l b a n e n e h W . s t u p t u o e t a t s - e e r h T

. ) 2 . g i F e e S ( . d e v i e c e r

D t S

t u p t u o e h t d n a d e r e t s i g e r n e e b s a h r i a p e n o t d e v i e c e r a n e h w h g i h c i g o l a s t n e s e r P . t u p t u o g n i r e e t s d e y a l e D

V w o l e b s l l a f T G / t S n o e g a t l o v e h t n e h w w o l c i g o l o t s n r u t e R . d e t a d p u s i h c t a l

t S T

.

t S E

e l b a z i n g o c e r a s t c e t e d m h t i r o g l a l a t i g i d e h t n e h w y l e t a i d e m m i h g i h c i g o l a s t n e s e r P . t u p t u o g n i r e e t s y l r a E

. w o l c i g o l a o t n r u t e r o t t S E e s u a c l l i w n o i t i d n o c l a n g i s f o s s o l y r a t n e m o m y n A . ) n o i t i d n o c l a n g i s ( r i a p e n o t

t G / t S

V n a h t r e t a e r g e g a t l o v A . ) l a n o i t c e r i d i b ( t u p t u o e m i t d r a u g / t u p n i g n i r e e t S

t S T

e h t s e s u a c t S a d e t c e t e d

s t i d n a , t n a t s n o c e m i t g n i r e e t s l a n r e t x e e h t t e s e r o t s t c a t u p t u o T G e h T . r i a p e n o t d e t c e t e d e h t r e t s i g e r o t e c i v e d

) 2 . g i F e e S ( . t S n o e g a t l o v e h t d n a t S E f o n o i t c n u f a s i e t a t s

V

D D

. y l p p u s r e w o p e v i t i s o P

C I . n o i t c e n n o C l a n r e t n I V o t d e i t e b t s u M

S S

) y l n o n o i t a r u g i f n o c 0 7 8 8 r o f (

2000 California Micro Devices Corp. All rights reserved.

9/28/2000 7

CM8870/70C CALIFORNIA MICRO DEVICES

215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com

Figure 3. Typical Filter Characteristic Figure 4. Basic Steering Circuit

Figure 5. Guard Time Adjustment Figure 6. Differential Input Configuration

2000 California Micro Devices Corp. All rights reserved.

9/28/2000 215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com 8

CALIFORNIA MICRO DEVICES CM8870/70C

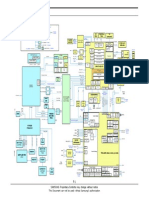

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

9

V

St/GT

ESt

StD

Q4

Q3

Q2

Q1

TOE

DD

ESt

StD

NC

Q4

Q3

Est

StD

NC

Q4

Q3

N

C

I

N

+

I

N

-

V S

t

/

G

T

D

D

G

S

I

N

+

I

N

-

V S

t

/

G

T

D

D

4

5

6

7

8

4

5

6

7

8

9 1

0

1

1

1

2

1

3

9 1

0

1

1

1

2

1

3

V

St/GT

ESt

StD

Q4

Q3

Q2

Q1

TOE

DD 18

17

16

15

14

13

12

11

10

18

17

16

15

14

13

12

11

10

IN+

IN-

GS

V

IC

IC

OSC1

OSC2

V

REF

SS

GS

V

IC

IC

OSC1

REF

V

INH

PD

OSC3

OSC1

REF 18

17

16

15

14

18

17

16

15

14

3 2 1

2

0

1

9 3 2 1

2

0

1

9

O

S

C

2

V

T

O

E

Q

1

Q

2

S

S

O

S

C

2

V

T

O

E

Q

1

Q

2

S

S

IN+

IN-

GS

V

INH

IC

OSC1

OSC2

V

REF

SS

Ordering Information

Product Identification Number

Package

P Plastic DIP (18)

F Plastic SOP EIAJ (18)

PE PLCC (20)

S SOIC (18)

Temperature/Processing

None 0

O

C to +70

O

C, 5% P.S. Tol.

I -40

O

C to +85

O

C, 5% P.S. Tol.

CM8870C

Pin Assignments

Example:

Figure 8. CM8870/70C Crystal Connection Figure 7. CM8870C Crystal Connection

(PLCC Package Only)

CM8870

30pF

OSC1 OSC2 OSC3

OSC1 of other CM887Xs

Clock input of other devices

OSC1

3.58 Mhz 30pF 30pF

OSC1 OSC1 OSC2 OSC2 OSC2

P Plastic DIP (18)

F Plastic SOP

EIAJ (18)

S SOIC (18)

P Plastic DIP (18)

F Plastic SOP

EIAJ (18)

S SOIC (18)

PE PLCC (20)

* Connect To VSS

PE PLCC (20)

C

M

8

8

7

0

C

M

8

8

7

0

C

CM8870 CM8870C

I

N

-

I

N

+

I

N

-

I

N

+

*

*

* *

*

I P

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

También podría gustarte

- Electronic Circuit Design Ideas: Edn Series for Design EngineersDe EverandElectronic Circuit Design Ideas: Edn Series for Design EngineersCalificación: 5 de 5 estrellas5/5 (2)

- Ec210b Pub20021241-I PDFDocumento1046 páginasEc210b Pub20021241-I PDFCholif 'oliph' Fadhilah100% (16)

- Command DocumentsDocumento202 páginasCommand DocumentsPaul van Kordelaar83% (6)

- Laboratory Experiment 3 Test For CarbohydratesDocumento9 páginasLaboratory Experiment 3 Test For CarbohydratesRenee Dwi Permata MessakaraengAún no hay calificaciones

- OEC-7700 - Block DiagramsDocumento36 páginasOEC-7700 - Block DiagramsWalky Ulloa100% (5)

- Pocket Book AGDocumento67 páginasPocket Book AGsudiraharjaAún no hay calificaciones

- Macedonian KavalDocumento1 páginaMacedonian Kavalmikiszekely1362Aún no hay calificaciones

- Freefall Lifeboat DrawingDocumento7 páginasFreefall Lifeboat DrawingNikNik0010% (1)

- Emcoturn 365Documento362 páginasEmcoturn 365mikadoturkAún no hay calificaciones

- NRT1 BookletDocumento13 páginasNRT1 Bookletjaya19844Aún no hay calificaciones

- Definition of Logistics ManagementDocumento4 páginasDefinition of Logistics ManagementzamaneAún no hay calificaciones

- Service Manual AE-6B: KV-29LS60B KV-29LS60K KV-29LS60EDocumento69 páginasService Manual AE-6B: KV-29LS60B KV-29LS60K KV-29LS60EИгорь Т-ЧернинAún no hay calificaciones

- Block Diagrams 8-1. Block Diagram: 8 - 1 SAMSUNG Proprietary-Contents May Change Without NoticeDocumento3 páginasBlock Diagrams 8-1. Block Diagram: 8 - 1 SAMSUNG Proprietary-Contents May Change Without NoticeSyar ArifAún no hay calificaciones

- Service Manual FE-2: KV-25FX30B KV-25FX30E KV-25FX30K KV-29FX30B KV-29FX30E KV-29FX30KDocumento50 páginasService Manual FE-2: KV-25FX30B KV-25FX30E KV-25FX30K KV-29FX30B KV-29FX30E KV-29FX30Kradomir46Aún no hay calificaciones

- Sony Kv-29cl10k Chassis Fe2 (ET)Documento52 páginasSony Kv-29cl10k Chassis Fe2 (ET)khafjiAún no hay calificaciones

- Sony Fe2 Chassis Kv29cl10 TV SMDocumento53 páginasSony Fe2 Chassis Kv29cl10 TV SMFrancisco Acosta PadillaAún no hay calificaciones

- 56.9mm (2.3 INCH) SINGLE DIGIT Numeric Display: Package Dimensions & Internal Circuit DiagramDocumento3 páginas56.9mm (2.3 INCH) SINGLE DIGIT Numeric Display: Package Dimensions & Internal Circuit DiagramNegru P. PlantatieAún no hay calificaciones

- SC1403 Data SheetDocumento30 páginasSC1403 Data Sheetnomi_nomiAún no hay calificaciones

- 58Mm (2.3 Inch) 8X8 Dot Matrix DisplaysDocumento6 páginas58Mm (2.3 Inch) 8X8 Dot Matrix DisplaysTinh NguyenAún no hay calificaciones

- pj73 sx34Documento2 páginaspj73 sx34BhaskarAún no hay calificaciones

- Control Valves (ABB Kent)Documento816 páginasControl Valves (ABB Kent)anhkietvt100% (1)

- x4540 Systems TSC Thumper Thor TOI PartaDocumento130 páginasx4540 Systems TSC Thumper Thor TOI PartaCarlita RamosAún no hay calificaciones

- 13.2mm (0.52INCH) SINGLE DIGIT Numeric DisplaysDocumento5 páginas13.2mm (0.52INCH) SINGLE DIGIT Numeric DisplaysJames ChaseAún no hay calificaciones

- Datasheet PDFDocumento5 páginasDatasheet PDFShkorpion93Aún no hay calificaciones

- Controls & Signalling Devices: Extended RangeDocumento2 páginasControls & Signalling Devices: Extended Range4usangeetAún no hay calificaciones

- Display 16 Seg Rs 451-6622Documento5 páginasDisplay 16 Seg Rs 451-6622o1771709Aún no hay calificaciones

- Kmeans Clustering-Results PDFDocumento35 páginasKmeans Clustering-Results PDFAnneAún no hay calificaciones

- Manual Central Telefónica LG GOLDSTAR 616 Man 38616Documento25 páginasManual Central Telefónica LG GOLDSTAR 616 Man 38616anon_817962718Aún no hay calificaciones

- Mosis Wafer Acceptance TestsDocumento2 páginasMosis Wafer Acceptance TestsPraveen VsAún no hay calificaciones

- GearDocumento2 páginasGearVangelis ApostolouAún no hay calificaciones

- Philips PM2517Documento104 páginasPhilips PM2517Mohammad EssamAún no hay calificaciones

- T-Pad IS703CDocumento5 páginasT-Pad IS703CKajal SarkarAún no hay calificaciones

- Maxon Smartfire Control System SpecDocumento12 páginasMaxon Smartfire Control System SpecJohn HowardAún no hay calificaciones

- W R Ite IS O 9 6 6 0 1 File e X Te N S Io N S: T R U EDocumento3 páginasW R Ite IS O 9 6 6 0 1 File e X Te N S Io N S: T R U ERicardo Fernandez PalloAún no hay calificaciones

- Stonex Sts-rp-En 2'' 0.6mgonDocumento2 páginasStonex Sts-rp-En 2'' 0.6mgonΧαν ΤρίοAún no hay calificaciones

- Photo-Interrupter: Ultra-Small Minimal Influence From Stray Light Low Collector-Emitter Saturation VoltageDocumento3 páginasPhoto-Interrupter: Ultra-Small Minimal Influence From Stray Light Low Collector-Emitter Saturation VoltageAdrian ZarnescuAún no hay calificaciones

- Yamaha AMP GP Pro A Series-Disklavier III-dc3a Dc5a Dc6a Dc7a Ds4a Ds6a Dcf3sa ProDocumento116 páginasYamaha AMP GP Pro A Series-Disklavier III-dc3a Dc5a Dc6a Dc7a Ds4a Ds6a Dcf3sa ProDamon Brunger100% (1)

- STS130Documento252 páginasSTS130MaestroColicus0% (1)

- P89V51Rd2 Microcontroller BoardDocumento6 páginasP89V51Rd2 Microcontroller BoardlkpavangbhAún no hay calificaciones

- CommodityDocumento1 páginaCommodityLucky ChougaleAún no hay calificaciones

- VLAN Trunking Protocol (VTP) : Nexus Technology Labs Classical Ethernet SwitchingDocumento6 páginasVLAN Trunking Protocol (VTP) : Nexus Technology Labs Classical Ethernet SwitchingsatourismAún no hay calificaciones

- Bentley's Substation Design Solution: Al GrayDocumento25 páginasBentley's Substation Design Solution: Al Graymissowusu100% (1)

- Service Data Sheet: Standard - Automatic Defrost Top Freezer Models (R134A)Documento2 páginasService Data Sheet: Standard - Automatic Defrost Top Freezer Models (R134A)luisperozoAún no hay calificaciones

- Ins. ElectDocumento1 páginaIns. ElectGregory BrewerAún no hay calificaciones

- (Vaid1 7) IndoreDocumento7 páginas(Vaid1 7) IndoreShibin JohneyAún no hay calificaciones

- Computer Conversions HSDC HRDC SpecsheetDocumento7 páginasComputer Conversions HSDC HRDC SpecsheetElectromateAún no hay calificaciones

- ARRI Alexa Pocket Guide 2.2Documento4 páginasARRI Alexa Pocket Guide 2.2Cristal Vidrio100% (1)

- Mr. Sameer Mittal Ji.Documento3 páginasMr. Sameer Mittal Ji.Vivek UpretiAún no hay calificaciones

- SyntheticsDocumento21 páginasSyntheticsroshmediaAún no hay calificaciones

- Ald-2i 315-091464-13 PDFDocumento4 páginasAld-2i 315-091464-13 PDFogautierAún no hay calificaciones

- PlayStation4 SpecificationDocumento1 páginaPlayStation4 SpecificationJoe_1968Aún no hay calificaciones

- Delta Ia PLC DVP Es2 Ex2 Ss2 Sa2 Sx2 Se TP PM en 20170426Documento784 páginasDelta Ia PLC DVP Es2 Ex2 Ss2 Sa2 Sx2 Se TP PM en 20170426i_aordaz100% (1)

- Maxon 5550 BulletinDocumento4 páginasMaxon 5550 BulletindcarunchioAún no hay calificaciones

- MSDS - Federal White Portland Cement: Section 1 - Ide NtificationDocumento6 páginasMSDS - Federal White Portland Cement: Section 1 - Ide Ntificationeng20072007Aún no hay calificaciones

- Advertisement 25 May 2014Documento4 páginasAdvertisement 25 May 2014Hasnain KhanAún no hay calificaciones

- Water Level ControlDocumento1 páginaWater Level ControlRajasekar ElavarasanAún no hay calificaciones

- Honeywell 3800i Industrial Linear Image ScannerDocumento2 páginasHoneywell 3800i Industrial Linear Image ScannerJohnny BarcodeAún no hay calificaciones

- CDMA 2000 1X: FP&A Summit, Hong Kong 10 Minute Win 7 MigrationDocumento5 páginasCDMA 2000 1X: FP&A Summit, Hong Kong 10 Minute Win 7 MigrationJelly WangAún no hay calificaciones

- SI M AR A: Rome ODocumento5 páginasSI M AR A: Rome Odario1855Aún no hay calificaciones

- Bata Sept 10 ResltsDocumento1 páginaBata Sept 10 Resltssubodh_purohit7258Aún no hay calificaciones

- WMO2 Modem Series GSM 900 / 1800 / 1900: User ManualDocumento23 páginasWMO2 Modem Series GSM 900 / 1800 / 1900: User ManualChristian ChavezAún no hay calificaciones

- Landauer: Luxel + Dosimeter For X, Gamma, Beta, and Neutron RadiationDocumento4 páginasLandauer: Luxel + Dosimeter For X, Gamma, Beta, and Neutron RadiationAndres Oliveros GuerreroAún no hay calificaciones

- Fortran Programming 3Documento11 páginasFortran Programming 3Kesev KeshavAún no hay calificaciones

- German Microelectronics Data 1968–69: Pergamon Electronics Data SeriesDe EverandGerman Microelectronics Data 1968–69: Pergamon Electronics Data SeriesAún no hay calificaciones

- Educational Electronics Equipment 1967–68: Pergamon Electronics Data SeriesDe EverandEducational Electronics Equipment 1967–68: Pergamon Electronics Data SeriesAún no hay calificaciones

- (Studies in American Popular History and Culture) Gail Fowler Mohanty - Labor and Laborers of The Loom - Mechanization and Handloom Weavers, 1780-1840 - Routledge (2006)Documento292 páginas(Studies in American Popular History and Culture) Gail Fowler Mohanty - Labor and Laborers of The Loom - Mechanization and Handloom Weavers, 1780-1840 - Routledge (2006)Милош Станојловић100% (1)

- Transportation ProblemDocumento4 páginasTransportation ProblemPrejit RadhakrishnaAún no hay calificaciones

- Q3 Module 15Documento33 páginasQ3 Module 15jovielyn kathley manaloAún no hay calificaciones

- Acoustic Phonetics PDFDocumento82 páginasAcoustic Phonetics PDFAnonymous mOSDA2100% (2)

- Product CatalogDocumento4 páginasProduct CatalogpeejayjacintoAún no hay calificaciones

- Pezzol Catalog 21 - INTERNATIONALDocumento74 páginasPezzol Catalog 21 - INTERNATIONALAhmed CapoAún no hay calificaciones

- Gmail - Welcome To Clarion Crossing!Documento4 páginasGmail - Welcome To Clarion Crossing!sagarnr gowdaAún no hay calificaciones

- Chemical Resistance TableDocumento6 páginasChemical Resistance TableEdgarDavidDiazCamposAún no hay calificaciones

- Chem 3052 CHAPTER 7 (Nuclear Magnetic Resonance Spectroscopy (NMR) )Documento6 páginasChem 3052 CHAPTER 7 (Nuclear Magnetic Resonance Spectroscopy (NMR) )ashenafiAún no hay calificaciones

- NID DATPrelimsTestPaper2018 BDesDocumento24 páginasNID DATPrelimsTestPaper2018 BDesManaswini ReddyAún no hay calificaciones

- Blank BPSU TemplateDocumento6 páginasBlank BPSU TemplateClarina Alviz BerganteAún no hay calificaciones

- 020 Basketball CourtDocumento4 páginas020 Basketball CourtMohamad TaufiqAún no hay calificaciones

- Money, Interest, and Inflation: Answers To CheckpointsDocumento16 páginasMoney, Interest, and Inflation: Answers To Checkpointsb96309Aún no hay calificaciones

- Pahlavi PoemDocumento9 páginasPahlavi PoemBatsuren BarangasAún no hay calificaciones

- A General Strategy For The Synthesis of Reduced Graphene Oxide-Based CompositesDocumento8 páginasA General Strategy For The Synthesis of Reduced Graphene Oxide-Based CompositesCristian Gonzáles OlórteguiAún no hay calificaciones

- 1C09-08 Design For Seismic and Climate ChangesDocumento31 páginas1C09-08 Design For Seismic and Climate ChangesSanketWadgaonkarAún no hay calificaciones

- EASL 2021 Version 4 NewDocumento691 páginasEASL 2021 Version 4 NewGupse Köroğlu AdalıAún no hay calificaciones

- Soal Test All GrammarDocumento2 páginasSoal Test All GrammarAnonymous D7lnJMJYAún no hay calificaciones

- 300 20Documento3 páginas300 20Christian JohnsonAún no hay calificaciones

- E11133 MB Pin Definition v2 Print Vendor Only PDFDocumento18 páginasE11133 MB Pin Definition v2 Print Vendor Only PDFLuciano MalancaAún no hay calificaciones

- Biomaterials in Restorative Dentistry and Endodontics: An OverviewDocumento6 páginasBiomaterials in Restorative Dentistry and Endodontics: An Overviewmanzoor ul haq bukhariAún no hay calificaciones

- Proposal Form NagDocumento1 páginaProposal Form Nagnitheesh kumarAún no hay calificaciones

- Department of Mechanical EnginneringDocumento11 páginasDepartment of Mechanical EnginneringViraj SukaleAún no hay calificaciones

- Inguinal Hernia - QuizDocumento17 páginasInguinal Hernia - Quizemily5890Aún no hay calificaciones