Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Capitulo 1 Processadores

Cargado por

Sidnei Guilherme KetlynTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Capitulo 1 Processadores

Cargado por

Sidnei Guilherme KetlynCopyright:

Formatos disponibles

1. Processadores 1.

1 Introduo

Os processadores (ou CPUs, de Central Processing Unit) so chips responsveis pela execuo de clculos, decises lgicas e instrues que resulta e todas as tare!as que u co putador pode !a"er e, por esse otivo, so ta #$ re!erenciados co o %c$re#ros% dessas quinas& ' #ora ha(a poucos !a#ricantes (essencial ente, )ntel, *+, e -)*), o ercado conta co u a grande variedade de processadores& *pesar disso e das di!erenas existentes entre cada odelo, todos co partilha de alguns conceitos e caracter.sticas&&

1.2 O trabalho de um processador

O processador $ u chip de sil.cio responsvel pela execuo das tare!as ca#.veis a u co putador& Para entender co o u processador tra#alha, $ conveniente dividir os u co putador e tr/s partes0processador, e ria e u con(unto de dispositivos de entrada e sa.da (ou )1O, de Input/Output)& 2este 3lti o, encontra4se qualquer ite responsvel pela entrada ou sa.da de dados no co putador, co o onitores de v.deo, teclados, ouses, i pressoras, scanners, discos r.gidos, etc& 2esse esque a, o#via ente, o processador exerce a !uno principal, ( que a ele ca#e o acesso e a utili"ao da e ria e dos dispositivos de entrada e sa.da para a execuo de suas atividades& Para entender elhor, suponha que voc/ queira que o seu co putador execute u progra a qualquer& U progra a consiste e u a s$rie de instrues que o processador dever executar para que a tare!a solicitada se(a reali"ada& Para isso, o processador trans!ere todos os dados necessrios 5 execuo, de u dispositivo de entrada e1ou sa.da 4 co o u disco r.gido 4 para a e ria& * partir da., todo o tra#alho $ reali"ado e o que vai ser !eito do resultado depende do progra a& O processador pode ser orientado a enviar as in!or aes processadas para o 6, nova ente ou para u a i pressora, por exe plo, tudo depende das instrues co as quais lidare &

1.3 Barramentos

* i age a seguir ilustra a co unicao entre o processador, a e ria e o con(unto de dispositivos de entrada e sa.da& 2ote que a conexo entre esses itens $ indicada por setas& )sso $ !eito para que voc/ possa entender a !uno dos #arra entos& ,e aneira geral, estes so os responsveis pela interligao e co unicao dos dispositivos e u co putador& 2ote que, para o processador se co unicar co a e ria e co o con(unto de dispositivos de entrada e sa.da, h 7 setas, isto $, #arra entos0 u se cha a barramento de endereos (address bus)8 o outro #arra ento de dados (data bus)8 o terceiro barramento de controle (control bus)&

9igura :&: ; <arra entos de co unicao& O #arra ento de endereos, #asica ente, indica de onde os dados a sere processados deve ser retirados ou para onde deve ser enviados& * co unicao por esse #arra ento $ unidirecional, ra"o pela qual s h seta e u a das extre idades da linha no gr!ico que representa a sua co unicao& Co o o no e deixa claro, $ pelo #arra ento de dados que os dados transita & Por sua ve", o #arra ento de controle !a" a sincroni"ao das re!eridas atividades, ha#ilitando ou desa#ilitando o !luxo de dados, por exe plo& Para voc/ co preender elhor, i agine que o processador necessita de u dado presente na e ria& Pelo #arra ento de endereos, ele o#t$ a locali"ao desse dado dentro da e ria& Co o precisa apenas acessar o dado, o processador indica pelo #arra ento de controle que esta $ u a operao de leitura na e ria& O dado $ ento locali"ado e inserido no #arra ento de dados, por onde o processador, !inal ente, o l/&

1.4 Clock interno e clock externo

' u co putador, todas as atividades necessita de sincroni"ao& O clock serve (usta ente para isso, ou se(a, #asica ente, atua co o de sinal de sincroni"ao& =uando os dispositivos do co putador rece#e o sinal de executar suas atividades, d4se a esse aconteci ento o no e de %pulso de cloc>%& ' cada pulso, os dispositivos executa suas tare!as, para e vo para o prxi o ciclo de cloc>& * edio do cloc> $ !eita e hertz (6"), a unidade padro de edidas de !req?/ncia, que indica o n3 ero de oscilaes ou ciclos que ocorre dentro de u a deter inada edida de te po, no caso, segundos& *ssi , se u processador tra#alha 5 @AA 6", por exe plo, signi!ica que $ capa" de lidar co @AA operaes de ciclos de cloc> por segundo& Bepare que, para !ins prticos, a palavra kilohertz (C6") $ utili"ada para indicar :AAA 6", assi co o o ter o megahertz (+6") $ usado para indicar :AAA C6" (ou : ilho de hert")& ,e igual !or a, gigahertz (D6") $ a deno inao usada quando se te :AAA +6", e assi por diante& Co isso, se u processador te , por exe plo, u a !req?/ncia de @AA +6", signi!ica que pode tra#alhar co @AA ilhes de ciclos por segundo& *s !req?/ncias co as quais os processadores tra#alha so cha adas ta #$ de clock interno& 2este ponto, voc/ certa ente ( deve ter entendido que $ da. que ve expresses co o Pentiu E de 7,F D6", por exe plo& +as, os processadores ta #$ conta co o que cha a os de clock externo ou Front Side Bus (9G<) ou, ainda, barramento rontal& O 9G< existe porque, devido a li itaes !.sicas, os processadores no pode se co unicar co a e ria ( ais precisa ente, co o a ponte norte 4 ou northbridge 4 do chipset, que cont$ o controlador da e ria) usando a es a velocidade do cloc> interno& *ssi , quando essa co unicao $ !eita, o cloc> externo, de !req?/ncia ais #aixa, $ que $ usado& 2ote que, para o#ter o cloc> interno, o processador usa u a ultiplicao do cloc> externo& Para entender elhor, suponha que u deter inado processador tenha cloc> externo de :AA +6"& Co o o seu !a#ricante indica que esse chip tra#alha 5 :,H D6" (ou se(a, te cloc> interno de :,H D6"), seu cloc> externo $ ultiplicado por :H0 :AA x :H I :HAA +6" ou :,H D6"& J i portante deixar claro, no entanto, que se dois processadores di!erentes 4 u da )ntel e outro da *+,, por exe plo 4 tivere cloc> interno de es o valor 4 F,@ D6", para exe pli!icar 4, no signi!ica que a #os tra#alha 5 es a velocidade& Cada processador te u pro(eto distinto e conta co caracter.sticas que deter ina o quo rpido $& *ssi , u deter inado processador pode levar, por exe plo, F ciclos de cloc> para executar u a instruo& ' outro processador, essa es a instruo pode requerer 7 ciclos& *l$ disso, uitos processadores 4 especial ente os ais recentes 4 trans!ere F ou ais dados por ciclo de cloc>, dando a entender que u processador que !a", por exe plo, trans!er/ncia de F dados por ciclo e que tra#alha co cloc> externo de :77 +6", o !a" 5 FHH +6"& Por esses e outros otivos, $ u erro considerar apenas o cloc> interno co o parK etro de co parao entre processadores di!erentes&

1.! Bits dos processadores

O n3 ero de #its $ outra i portante caracter.stica dos processadores e, natural ente, te grande in!lu/ncia no dese penho desse dispositivo& Processadores ais antigos, co o o F@H, tra#alhava co :H #its& ,urante uito, no entanto, processadores que tra#alha co 7F #its !ora uitos co uns, co o as linhas Pentiu , Pentiu )), Pentiu ))) e Pentiu E da )ntel, ou *thlon LP e ,uron da *+,& *lguns odelos de 7F #its ainda so encontrados no ercado, todavia, o padro atual so os processadores de HE #its, co o os da linha Core F ,uo, da )ntel, ou *thlon HE, da *+,& ' resu o, quanto ais #its internos o processador tra#alhar, ais rapida ente ele poder !a"er clculos e processar dados e geral, depedendo da execuo a ser !eita& )sso acontece porque os #its dos processadores representa a quantidade de dados que os circuitos desses dispositivos consegue tra#alhar por ve"& U processador co :H #its, por exe plo, pode anipular u n3 ero de valor at$ HM&M7M& Ge esse processador tiver que reali"ar u a operao co u n3 ero de :AA&AAA, ter que !a"er a operao e duas partes& 2o entanto, se u chip tra#alha a 7F #its, ele pode anipular n3 eros de valor at$ E&FNE&NHO&FNM e u a 3nica operao& Co o esse valor $ superior a :AA&AAA, a operao ser poss.vel e u a 3nica ve"&

1." #em$ria cache

Os processadores passa por aper!eioa entos constantes, o que os torna cada ve" ais rpidos e e!icientes& 2o entanto, o es o no se pode di"er das tecnologias de e ria B*+& ' #ora estas ta #$ passe por constantes

elhorias, no consegue aco panhar os processadores e ter os de velocidade& *ssi sendo, de nada adianta ter processador rpido se este te o seu dese penho co pro etido por causa da %lentido% da e ria&

U a soluo para esse pro#le a seria equipar os co putadores co u tipo de e ria uito ais rpida, a GB*+ (Static RAM)& 'stas se di!erencia das e rias convencionais ,B*+ ( D namic RAM) por sere uito rpidas, por outro lado, so uito ais caras e no conta co o es o n.vel de iniaturi"ao, sendo, portanto, inviveis& *pesar disso, a id$ia no !oi total ente descartada, pois !oi adaptada para o que conhece os co o mem$ria cache& * e ria cache consiste e u a pequena quantidade de e ria GB*+ e #utida no processador& =uando este precisa ler dados na e ria B*+, u circuito especial cha ado %controlador de cache% trans!ere #locos de dados uito utili"ados da B*+ para a e ria cache& *ssi , no prxi o acesso do processador, este consultar a e ria cache, que $ #e ais rpida, per itindo o processa ento de dados de aneira ais e!iciente& Ge o dado estiver no cache, o processador a utili"a, do contrrio, ir #usc4lo na e ria B*+, etapa essa que $ ais lenta& ,essa !or a, a e ria cache atua co o u inter edirio, isto $, !a" co que o processador ne se pre necessite chegar 5 e ria B*+ para acessar os dados dos quais necessita& O tra#alho da e ria cache $ to i portante que, se ela, o dese penho de u processador pode ser seria ente co pro etido& Os processadores tra#alha , #asica ente, co dois tipos de cache0 cache P: ( !e"el # 4 2.vel :) e cache PF ( !e"el $ 4 2.vel F)& 'ste 3lti o $ ligeira ente aior e ter os de capacidade e passou a ser utili"ado quando o cache P: se ostrou insu!iciente& *ntiga ente, u tipo distinguia do outro pelo !ato da e ria cache P: estar locali"ada (unto ao n3cleo do processador, enquanto que a cache PF !icava locali"ada na placa4 e& *tual ente, a #os os tipos !ica locali"ados dentro do chip do processador, sendo que, e uitos casos, a cache P: $ dividida e duas partes0 %P: para dados% e %P: para instrues%& -ale ressaltar que, dependendo da arquitetura do processador, $ poss.vel o surgi ento de odelos que tenha u terceiro n.vel de cache (P7)& +as, isso no $ novidade0 a *+, chegou a ter u processador e :NNN cha ado CH4 ))) que contava co cache P: e PF interna ente, algo inco u 5 $poca, ( que naquele te po o cache PF se locali"ava na placa4 e& Co isso, esta 3lti a aca#ou assu indo o papel de cache P7& * !oto a#aixo ostra u processador *+, *thlon, co HE C< de cache P: para instrues, HE C< de cache P: para dados e M:F C< de cache PF& 2ote que a capacidade de cada tipo de cache varia con!or e o odelo do processador&

9igura :&F ; processador *+,&

1.% Processadores com dois ou mais n&cleos

6 te pos que $ poss.vel encontrar no ercado placas4 e que conta co dois ou ais slots para processadores& * aioria es agadora dessas placas so usadas e co putadores especiais, co o servidores e %orkstations, que so utili"ados e aplicaes que exige grandes recursos de processa ento& Para aplicaes do $sticas e de escritrio, no entanto, co putadores co dois ou ais processadores so inviveis devido aos elevados custos que esses equipa entos representa , ra"o pela qual $ conveniente a esses nichos de ercado contar co processadores cada ve" ais rpidos&

*t$ u passado no uito distante, o usurio tinha noo do quo rpido era os processadores de acordo co a taxa de seu cloc> interno& O pro#le a $ que, quando u deter inado valor de cloc> $ alcanado, torna4se ais di!.cil desenvolver outro chip co cloc> aior& Pi itaes !.sicas e tecnolgicas so os otivos para isso& U a delas $ a questo da te peratura0 quanto ais egahert" u processador tiver, ais calor ele gerar& U a das !or as encontradas pelos !a#ricantes para lidar co essa li itao $ !a#ricar e disponi#ili"ar processadores co dois n3cleos (dual&core) ou ais (multi&core)& +as, o que isso signi!icaQ Processadores desse tipo conta co dois ou ais n3cleos distintos no es o circuito integrado, co o se houvesse dois processadores dentro de u & ,essa !or a, o processador pode lidar co dois processos por ve", u para cada n3cleo, elhorando o dese penho do co putador co o u todo& 2ote que, e u chip de 3nico n3cleo, o usurio pode ter a i presso de que vrios processos so executados si ultanea ente, ( que a quina est quase se pre executando ais de u a aplicao ao es o te po& 2a verdade, o que acontece $ que o processador dedica deter inados intervalos de te po a cada processo e isso ocorre de aneira to rpida, que se te a i presso de processa ento si ultKneo& Pelo enos teorica ente, $ poss.vel !a#ricar processadores co de"enas de n3cleos& J poss.vel encontrar processadores co F, 7 e E n3cleos ( dual&core, triple&clore e 'uad&core, respectiva ente)& J i portante ressaltar que ter processadores co dois ou ais n3cleos no i plica, necessaria ente, e co putadores que so proporcional ente ais rpidos& U a s$rie de !atores in!luencia nesse quesito, co o as velocidades li itadas das e rias e dos dispositivos de entrada e sa.da, e as !or as co o os progra as so desenvolvidos& 2a i age n3cleos)0 a#aixo, u a ontage que ilustra o interior de u processador )ntel Core F 'xtre e =uad4Core (co E

9igura :&7 ; processador intel&

1.' Processo de abricao 1.'.1 (il)cio

O pri eiro passo na !a#ricao de processadores consiste, o#via ente, na o#teno de at$ria4pri a& Deral ente, os chips so !or ados por sil)cio, e co os processadores no $ di!erente& O sil.cio $ u ele ento qu. ico extre a ente a#undante, tanto que $ considerado o segundo ais co u na Rerra& J poss.vel extra.4lo de areia, granito, argila, entre outros&

'sse ele ento qu. ico $ utili"ado para a constituio de vrios ateriais resistentes, co o vidro e cerK ica& 2o entanto, $ ta #$ se icondutor, isto $, te a capacidade de condu"ir eletricidade& 'ssa caracter.stica so ada 5 sua exist/ncia e a#undKncia !a" co que o sil.cio se(a u ele ento extre a ente utili"ado pela ind3stria eletrSnica& Para voc/ ter u a id$ia da i portKncia desse aterial, a concentrao de e presas que utili"a sil.cio e seus produtos eletrSnicos e vrias cidades da Cali!rnia, nos 'U*, !e" co que a regio rece#esse o no e de -ale do Gil.cio (Silicon (alle )& J l que esto locali"adas, por exe plo, as sedes da *+, e da )ntel, as aiores !a#ricantes de icroprocessadores do undo&

1.'.2 *abricao de processadores

* !a#ricao dos processadores se inicia e odernos centros tecnolgicos especiali"ados& 'sses locais so to so!isticados e de construo de valor to elevado, que existe poucos no undo& 2os la#oratrios desses centros, u a deter inada quantidade de cristal de sil.cio $ colocada e u a esp$cie de haste e, posterior ente, inserida e sil.cio !undido su# etido a u a presso e a u a te peratura extre a ente alta 4 e torno dos 7AAT& * haste $ ento retirada e girada ao es o te po& 'sse processo (cha ado de t$cnica Czochralski) !a" co que o aterial que se (untou 5 haste !or e u a esp$cie de cilindro (ta #$ conhecido co o % ingot%)& Geu diK etro varia de acordo co o avano da tecnologia, as e geral possui entre FAA e 7AA il. etros& O es o vale para o seu co pri ento0 de : a F etros& J i portante !risar que esses cilindros precisa ser !or ados de sil.cio puro& O processo de puri!icao desse aterial $ co plexo, o que encarece ainda ais a !a#ricao&

!igura :&E Cilindro !or ado por sil.cio (ingot)& Be!er/ncia0 )ikipedia U a ve" conclu.da essa etapa, o cilindro $ %!atiado%, isto $, cortado e vrias partes& Cada u a dessas divises rece#e o no e de +a er& Cada %!atia% $ polida at$ !icar per!eita, se variaes, anchas, di!erenas de #rilho ou qualquer irregularidade e sua co posio& Gua espessura, geral ente $ enor que : il. etro& ' u a etapa ais adiante, cada Ua!er ser dividido e vrios %quadradinhos% (ou %pastilhas%), que posterior ente sero separados e !or aro os processadores e si& 2o passo seguinte, a super!.cie do Ua!er passa por u processo de oxidao, onde a aplicao de gases 4 especial ente oxig/nio 4 e te peratura elevada !or a u a ca ada de dixido de sil.cio& 'ssa ca ada servir de #ase para a construo de ilhares e ilhares de transistores, e poucas palavras, in3sculos co ponentes capa"es de %a pli!icar% ou %chavear% sinais el$tricos, al$ de outras !unes relacionadas& 2a prxi a etapa, os Ua!ers passa por u processo onde rece#e u a ca ada de aterial !otossens.vel, isto $, que reage 5 lu"& 2essa etapa, cada u dos #locos que se trans!or ar e processador rece#e lu" ultravioleta e certos pontos e e deter inadas intensidades& Os pontos da ca ada !otossens.vel que reage 5 lu" ultravioleta se torna ais %gelatinosos% e so posterior ente re ovidos, deixando expostos os respectivos pontos da ca ada de dixido de sil.cio& Co isso, te 4se pontos co#ertos co ca ada !otossens.vel e pontos co#ertos co dixido de sil.cio& O#via ente, a ca ada !otossens.vel restante te dixido de sil.cio por #aixo& *s partes deste 3lti o que no estivere protegidas pela ca ada !otossens.vel so ento re ovidas atrav$s de outro procedi ento& 2o prxi o passo, a ca ada !otossens.vel $ re ovida& O que so#ra ento $ utili"ado co o estrutura para a ontage dos transistores, procedi ento esse que continua sendo !eito a partir de aplicao de ais ateriais e exposio 5 lu" ultravioleta&

9igura :&M 4 *ngenheiro segurando um Ua!er Be!er/ncia+ Intel =ue te algu a experi/ncia co !otos #aseadas e !il es, provavel ente perce#er que as etapas descritas aci a le #ra #astante os procedi entos de revelao de !otogra!ias& ,e !ato, os princ.pios so essencial ente os es os& J i portante !risar que u 3nico processador pode conter ilhes de transistores& G co o exe plo, os pri eiros processadores da linha )ntel Core F ,uo possue cerca de FN: ilhes de transistores e u 3nico chip& *ssi co o acontece co qualquer processador, esses transistores so divididos e organi"ados e agrupa entos, onde cada grupo $ responsvel por u a !uno& U a ve" ter inada a ontage dos transistores, os Ua!ers so %recortados% e u !or ato que le #ra pequenos quadrados ou pastilhas& Cada unidade se trans!or ar e u processador& Co o os Ua!ers so redondos, o que so#ra da #orda, o#via ente, no pode virar u processador, ento esse aterial $ descartado, assi co o qualquer unidade que apresentar de!eito ou anor alidade& -oc/ pode ter se perguntado se no seria ideal !a#ricar Ua!ers quadrados ou retangulares para evitar desperd.cio na #orda& Reorica ente, seria, as os Ua!ers so !or ados por cilindros devido 5 t$cnica de !a#ricao explicada no in.cio deste tpico, onde u a haste $ inserida e sil.cio e, e seguida, retirada e girada& 'sse procedi ento !a" co que u cilindro se(a constitu.do natural ente&

9igura :&H 4 Va!er de sil.cio 4 repare que as #ordas so desperdiadas Be!er/ncia )ntel

J i portante !risar que cada Ua!er d orige a centenas de processadores, portanto, todo o processo de !a#ricao $ reali"ado co #ase e u a s$rie de cuidados& Para co ear, os la#oratrios das !#ricas so locais extre a ente li pos e protegidos (conhecidos co o % clean room%), tanto $ que as poucas pessoas que aco panha a produo utili"a roupas que le #ra astronautas (co o ostra a segunda !oto deste tpico)& *l$ disso, as quinas responsveis pela produo precisa estar per!eita ente a(ustadas para seguir as instrues dos pro(etos dos chips que esto sendo !a#ricados&

9igura :&O 4 )a,er- pastilha .die/- processador Be!er/ncia+ Intel

1.'.3 ,i erena de clock

=uando os processadores chega ao ercado, eles so classi!icados e linhas, por exe plo, )ntel Core F ,uo, *+, Pheno )) e assi por diante& Cada u a dessas linhas $ constitu.da por processadores de diversas velocidades de processa ento& Co o exe plo, a linha )ntel Core F ,uo possui os odelos '@EAA, '@MAA e '@HAA& O que os di!erencia $ que o cloc> do pri eiro $ de 7 D6", o cloc> do segundo $ de 7,:H D6" e, por !i , o cloc> do terceiro $ de 7,77 D6"& Rodos esses processadores so oriundos do es o pro(eto, portanto, t/ a es a arquitetura& O que torna u odelo ais rpido que o outro $ que a !a#ricao do ais velo" !oi ais per!eita que a dos odelos i ediata ente in!eriores& Pequenos detalhes durante todo o processo de !a#ricao !a"e co que, dentro de u es o Ua!er, as %pastilhas% se(a ligeira ente di!erentes u a das outras& )sso pode acontecer, por exe plo, e virtude de pequenos desvios nas ca adas, e pequenas di!erenas na passage do !eixe de lu", entre outros& Por esse otivo, os Ua!ers passa por testes que aponta co qual !requ/ncia cada chip pode utili"ar& *penas depois disso $ que o Ua!er $ cortado e os chips passa para a !ase de encapsula ento& 'sses testes ta #$ aponta quais chips devero ser descartados por no tere condies de uso&

1.'.4 #iniaturali-ao

* ind3stria conseguiu elevar a capacidade dos processadores ao longo do te po se que, para tanto, tivesse que au entar o ta anho !.sico desses dispositivos& 'sse !eito $ poss.vel graas 5 nanotecnolo.ia, e poucas palavras, u ra o da ci/ncia que envolve as pesquisas que lida co itens edidos na casa dos nan/metros& Para que no sa#e, u nanS etro equivale a u ilion$si o de il. etro, isto $, u il. etro dividido por u ilho, e sua

sigla $ n & * edida ais usada, no entanto, $ o il. etro dividido por il&

icron, que equivale a u

il$si o de

il. etro, ou se(a, u

Draas 5s pesquisas de nanotecnologia, $ poss.vel deixar os transistores dos chips cada ve" enores& O processador )ntel E@H, por exe plo, te cerca de : ilho de transistores, sendo que cada u deles conta co pratica ente : icron de ta anho& +uito pequeno, noQ 2a verdade, $ u ta anho onstruoso, se co parado aos processadores atuais& G para voc/ ter u a id$ia, os pri eiros processadores da linha )ntel Core F ,uo conta co cerca de FN: ilhes de transistores& 'sses chips utili"a tecnologia de !a#ricao de A,AHM icron (ou HM nanS etros), sendo que os ais recentes dessa linha so !a#ricados co A,AEM icron (EM nanS etros)& *s pesquisas so#re iniaturali"ao de chips indica que ser poss.vel levar esse processo at$ a casa dos FM nanS etros (ou u valor no uito enor que isso)& ,epois disso, a ind3stria chegar a u li ite !.sico onde os transistores provavel ente sero !or ados por poucos to os e no podero ais ser di inu.dos& J claro que pesquisas ( esto e anda ento para criar u a sa.da para esse pro#le a& U a delas $ a %co putao quKntica% , que uito ais que contornar os li ites !.sicos dos processadores da %co putao clssica%, poder revolucionar a co putao co o u todo&

1.'.! 0ncapsulamento dos processadores

2as etapas de encapsula ento, o processador $ inserido e u a esp$cie de %carcaa% que o protege e cont$ contatos etlicos para a sua co unicao co os co ponentes do co putador& Cada odelo de processador pode contar co tipos de encapsula ento di!erentes, que varia con!or e o seu pro(eto& ' geral, os processadores possue e sua parte superior u a esp$cie de %ta pa% etlica cha ada % Integrated 0eat Spreader% ()6G), que serve para proteg/4lo e, uitas ve"es, para !acilitar a dissipao de calor& 'sse co ponente nor al ente co#re toda a parte superior do chip e, dentro dele, no centro, !ica o processador e si (ta #$ cha ado de % die%)& 2o entanto, e alguns odelos, o )6G no $ utili"ado& 2esses casos, a aus/ncia dessa proteo pode !acilitar a disperso de calor devido ao contato direto do die co o cooler (ventoinha) do processador e redu"ir custos de !a#ricao& J i portante !risar que h vrias tecnologias usadas no encapsula ento dos processadores& * aplicao de cada u a varia con!or e o pro(eto do chip& 'is os tipos principais, tendo co o #ase tecnologias da )ntel0 1 P234 sigla de Pin 1rid Arra (algo co o % atri" de pinos%), esse $ u tipo de encapsula ento que !a" co que o processador utili"e pinos de contato que deve ser inseridos e u encaixe adequado na placa4 e do co putador (ver soquete, logo a#aixo)& Geu aterial #sico pode ser cerK ica ( Ceramic Pin 1rid Arra 4 CPD*) ou plstico (Plastic Pin 1rid Arra 4 PPD*)& 6 ta #$ u tipo cha ado 2lip Chip Pin 1rid Arra (9C4PD*) onde a pastilha !ica parcial ente exposto na parte superior do chip8

9igura :&@ 4 Intel Pentium 3 & *ncapsulamento 2C&P1A$- 'ue 4 semelhante ao 2C&P1Amas conta com um I0S .n5o presente no 2C&P1A/ 1 (0CC4 sigla para Single *dge Contact Cartridge, este tipo !a" co que o processador utili"e u encaixe linear (ligeira ente se elhante aos slots de e ria, por exe plo) ao inv$s de contatos e !or ato de pinos& Para isso, o processador $ ontado dentro de u a esp$cie de cartucho8

9igura :&N 4 )ntel Pentiu )) 4 'ncapsula ento G'CC Be!er/ncia0r Intel 1 (0PP4 sigla para Single *dge Processor Package, este tipo $ se elhante ao G'CC, no entanto, o processador !ica acoplado e u placa que no $ protegida por u cartucho8 1 5234 sigla para !and 1rid Arra , esse $ u padro recente da )ntel& Re algu a se elhana co os padres PD*, tendo co o principal di!erena o !ato de que os processadores no utili"a pinos de contato e sua parte in!erior, as si pontos etlicos& =uando o processador $ encaixado na placa4 e, esses pontos !ica e contato co pinos existentes no soquete (le #rando que nos padres PD* h !uros ao inv$s de pinos no soquete)& 2o que se re!ere ao PD*, a )ntel utili"ava u tipo cha ado 9C4PD*E ( 2lip Chip !and 1rid Arra , onde o n3 ero E indica o n3 ero de reviso do padro)&

9igura :&:A 4 Processador com encapsulamento 2C&!1A3 & Repare 'ue n5o h6 pinos- somente contatos met6licos & Re,er7ncia+ )ikimedia 2a parte in!erior dos processadores co encapsula entos nos padres PD* e se elhantes, !ica expostos u a s$rie de contatos etlicos que !a"e a co unicao entre o processador e si e os co ponentes do co putador& Para isso, esse contatos so encaixados e u a rea apropriada na placa4 e da quina, cha ada de so6uete (ou socket)& *contece que a quantidade e a disposio desses pinos varia con!or e o odelo do processador& Por exe plo, a linha )ntel Core F ,uo e alguns dos odelos ais recentes da linha Pentiu E utili"a o soquete OOM (PD* OOM)0

9igura :&:: 4 So'uete !1A OOM Be!er/ncia+ Intel W os processadores *+, Pheno LE utili"a o soquete *+FX0

9igura :&:F 4 So'uete AM$/AM$8 Re,er7ncia+ )ikipedia

9igura :&:7 4 Processador Pheno

LE ; Be!er/ncia0 *+,

)sso deixa claro que $ necessrio utili"ar placa4 e e processador co o es o soquete no o ento de ontar u co putador& Por$ , $ i portante !risar que isso no $ garantia de co pati#ilidade entre a #os& J poss.vel, por exe plo, que u a deter inada placa4 e utili"e o es o soquete de u processador lanado depois de sua chegada ao ercado& *pesar de a #os tere o es o soquete, u a inco pati#ilidade pode ocorrer, ( que o chipset da placa4 e pode no ter sido preparado para rece#er aquele processador& Por essa ra"o, $ i portante checar se pre no site do !a#ricante ou no anual da placa4 e quais processadores esta suporta& 2ote que a disposio de pinos (ou pontos de contato, no caso de chips co encapsula ento do tipo PD*) $ !eita de !or a que o usurio tenha apenas u a !or a de encaixar o processador na placa4 e& Co isso, i pede4se inseres erradas que possa resultar e danos ao co putador& Por essa ra"o, se o usurio no estiver conseguindo encaixar o processador, deve evitar es!oros e procurar no anual da placa4 e a orientao correta&

1.'." 7omes1c$di.o dos n&cleos

Rodo processador chega ao ercado tendo u no e que per ita !acil ente identi!ic4lo, co o Pentiu E, Core F ,uo, )taniu , *thlon HE, Pheno , etc& O que pouca gente sa#e $ que o n3cleo dos processadores rece#e outra deno inao antes es o de seu lana ento o!icial0 o no e4cdigo& * utili"ao de no es4cdigo $ i portante porque per ite distinguir as caracter.sticas de arquitetura de cada chip& +es o dentro de u a deter inada linha $ poss.vel encontrar processadores co di!erenas e seu pro(eto& Pode os utili"ar co o exe plo os pri eiros odelos da linha )ntel Core F ,uo, que so #aseados nos n3cleos de no es Conroe e +ero & O pri eiro $ direcionado a des>tops, enquanto que o segundo $ voltado a co putadores portteis (co o note#oo>s)& Gendo assi , o +ero possui recursos que oti i"a seu dese penho para exigir enos energia (por exe plo, utili"a voltage enor e 9G< redu"ido, se co parado ao Conroe)&

3ti8idade Pr9tica4

,entre os equipa entos do la#oratrio, separe dois di!erentes tipos de processadores& 9otogra!e ou anote todas as in!or aes que (ulgar i portantes e necessrias a respeito destes processadores& Pesquise e e la#ore u relatrio para ser entregue na prxi a aula onde voc/ deve identi!icar as seguintes caracter.sticas dos processadores a) 9a#ricante8 #) +odelo8 c) 9a .lia (ex0 Pentiu )))8 d) 9req?/ncia de tra#alho8 e) 23 ero de n3cleos8 !) Cach/ P: e PF (ta anho dos cach/s) g) 23 ero de #its co que tra#alha& h) Ripo de encapsula ento&

Be!er/ncia0 http011UUU&in!oUester&co 1processadores:&php 4 *cessado e http011UUU&in!oUester&co 1processadoresF&php 4 *cessado e AF1A@1FA:A AF1A@1FA:A

También podría gustarte

- Pacotão de 60 Apostilas manutenÇÃo de Notebooks Juntas e Várias Dicas - Informática - Multimídia - Campo Grande - AlamaulaDocumento4 páginasPacotão de 60 Apostilas manutenÇÃo de Notebooks Juntas e Várias Dicas - Informática - Multimídia - Campo Grande - AlamaulaSidnei Guilherme Ketlyn33% (3)

- Montagem e Manutenção de PCDocumento95 páginasMontagem e Manutenção de PCakirafff100% (9)

- Decodificador Com GravadorDocumento16 páginasDecodificador Com GravadorSidnei Guilherme KetlynAún no hay calificaciones

- Planilha de CustoDocumento8 páginasPlanilha de CustoSidnei Guilherme KetlynAún no hay calificaciones

- Prática de Laboratório 02Documento1 páginaPrática de Laboratório 02Sidnei Guilherme KetlynAún no hay calificaciones

- SimuladosDocumento7 páginasSimuladosPriscila de JesusAún no hay calificaciones

- Barramentos e Conexões de Placa MãeDocumento1 páginaBarramentos e Conexões de Placa MãeSidnei Guilherme KetlynAún no hay calificaciones

- Guia de Configuracao PPPoE Rev1 0 OI DSLINK 279Documento5 páginasGuia de Configuracao PPPoE Rev1 0 OI DSLINK 279Sidnei Guilherme KetlynAún no hay calificaciones

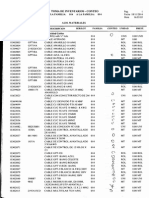

- Tabela de PreçosDocumento1 páginaTabela de PreçosSidnei Guilherme KetlynAún no hay calificaciones

- Reidasplanilhas Acompanhamento Mensal Horas Extras v9bDocumento7 páginasReidasplanilhas Acompanhamento Mensal Horas Extras v9bRodrigo SobrinhoAún no hay calificaciones

- Empresa de PropagandaDocumento3 páginasEmpresa de PropagandaSidnei Guilherme KetlynAún no hay calificaciones

- Curri LoDocumento1 páginaCurri LoSidnei Guilherme KetlynAún no hay calificaciones

- Micro Control Ad orDocumento44 páginasMicro Control Ad orpissini-1Aún no hay calificaciones

- Teclas de Atalho Do BlenderDocumento4 páginasTeclas de Atalho Do BlenderMarcio Gonzaga de SouzaAún no hay calificaciones

- Questionario Unidade II Organizao de ComputadoresDocumento4 páginasQuestionario Unidade II Organizao de ComputadoresfuentesraAún no hay calificaciones

- Lista de Exercicios - RamsesDocumento2 páginasLista de Exercicios - RamsesFernando FernandesAún no hay calificaciones

- 1.1. PCMS - Lista de Questões - Hardware e SoftwareDocumento2 páginas1.1. PCMS - Lista de Questões - Hardware e SoftwareKarine SilvaAún no hay calificaciones

- Manual Da Impressora Epson XP241Documento185 páginasManual Da Impressora Epson XP241Leticia SantosAún no hay calificaciones

- Anotações CDocumento2 páginasAnotações CSofia MoraisAún no hay calificaciones

- Exercícios de Arquitetura de ComputadoresDocumento5 páginasExercícios de Arquitetura de ComputadoresDuarlem RobertoAún no hay calificaciones

- Aula 1 TSE Principais BancasDocumento61 páginasAula 1 TSE Principais BancasErika SousaAún no hay calificaciones

- Módulo 7 - UpgradesDocumento7 páginasMódulo 7 - UpgradesPaulo ViegasAún no hay calificaciones

- Zabbix - Load CPU (System - Cpu.load) Vs Utilização CPU (System - Cpu.util)Documento5 páginasZabbix - Load CPU (System - Cpu.load) Vs Utilização CPU (System - Cpu.util)André HannemannAún no hay calificaciones

- Linguagem ZPL PDFDocumento5 páginasLinguagem ZPL PDFLacy RochaAún no hay calificaciones

- Diagrama Timer0 Oficial PDFDocumento1 páginaDiagrama Timer0 Oficial PDFFrancisco JosivanAún no hay calificaciones

- Placa de VideoDocumento21 páginasPlaca de VideoAna MarinhoAún no hay calificaciones

- Configurações de BIOS para Arranque Por USB PDFDocumento2 páginasConfigurações de BIOS para Arranque Por USB PDFpedrogilberto65Aún no hay calificaciones

- Questionário Unidade I - Organização de ComputadoresDocumento4 páginasQuestionário Unidade I - Organização de ComputadoresGeraldo SilvaAún no hay calificaciones

- Infoway Note w7645 SmerjDocumento4 páginasInfoway Note w7645 SmerjAnderson DutraAún no hay calificaciones

- Atividade 1 - Introdução A SODocumento2 páginasAtividade 1 - Introdução A SOJunior OliveiraAún no hay calificaciones

- AD1 - 2018-2 - Gabarito - Organização de Computadores PDFDocumento6 páginasAD1 - 2018-2 - Gabarito - Organização de Computadores PDFccaetanoa2Aún no hay calificaciones

- Como Surgiu o ComputadorDocumento14 páginasComo Surgiu o ComputadorWältër PömpïlïöAún no hay calificaciones

- 1 Aula de IPDDocumento2 páginas1 Aula de IPDDouglas Taveira100% (1)

- Baldan Facas PDFDocumento2 páginasBaldan Facas PDFDaniel VieiraAún no hay calificaciones

- TIC Conceitos BásicosDocumento21 páginasTIC Conceitos BásicosMaria João PessoaAún no hay calificaciones

- Prova de Sistema OperacionalDocumento3 páginasProva de Sistema OperacionalEveton MelloAún no hay calificaciones

- Padronização de Códigos de Erro de Diagnóstico DELLDocumento13 páginasPadronização de Códigos de Erro de Diagnóstico DELLJulio Cesar T ProcopioAún no hay calificaciones

- IT Essentials (ITE v6.0 + v7.0) Exame Capitulo 2 - Chapter 2 Exam - Passei DiretoDocumento1 páginaIT Essentials (ITE v6.0 + v7.0) Exame Capitulo 2 - Chapter 2 Exam - Passei Diretomano jAún no hay calificaciones

- Varredura de Textos Exercícicos Aula 10042014Documento6 páginasVarredura de Textos Exercícicos Aula 10042014uilsoonAún no hay calificaciones

- Ajuste de Kardex Parte1Documento22 páginasAjuste de Kardex Parte1Aj CampAún no hay calificaciones

- Lista 5 - Marcone Gabriel Da SilvaDocumento3 páginasLista 5 - Marcone Gabriel Da SilvaMARCONE GABRIEL DA SILVAAún no hay calificaciones