Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Lab 2

Cargado por

Andrés MartinezTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Lab 2

Cargado por

Andrés MartinezCopyright:

Formatos disponibles

PONTIFICIA UNIVERSIDAD JAVERIANA CALI

Laboratorio 2 Electrnica Digital Unidad Aritmtico Lgica

Monitor: Camilo Neira

18 de septiembre de 2013

1.

R ESUMEN

unidad aritmtica y lgica (ALU) es un circuito combinacional que desarrolla microoperaciones lgicas y aritmticas de dos operandos A y B de n bits. Las operaciones llevadas a cabo por la ALU son controladas por un grupo de entradas de seleccin de funcin.

Na

2.

E QUIPOS NECESARIOS

Software Altera Quartus II version 9.1 web Tarjeta FPGA Cyclone II

3.

O BJETIVOS

Aplicar de forma bsica el algebra de Boole sobre los circuitos combinatorios simples. Aanzar el uso de multplexadores y decodicadores BCD a 7 segmentos. Implementar y simular el diseo obtenido sobre el Software y Hardware correspondiente.

4.

P ROCEDIMIENTO

Se debe disear una ALU de 5 bits (A de 4 bits y B de 5 bits) con 4 entradas de seleccin: S3, S2, S1 y S0. Adicionalmente, algunas funciones son realizadas dependiendo del valor que tome C i n . Las funciones desarrolladas por la ALU se muestran en la siguiente tabla.

Con el n de hacer el diseo ms manejable se divide el problema en mdulos funcionales ( por ejemplo: unidad aritmtica, unidad lgica, unidad de corrimiento a la derecha y unidad de corrimiento a la izquierda) y se multiplexan las salidas de los bloques funcionales. En lugar de disear una ALU de 4 bits como un solo circuito, se implementar primero una ALU de 1 bit (bit-slice) para con base en ella montar el circuito de 4 bits. Tenga en cuenta los siguientes puntos para la elaboracin del laboratorio: 1. Los cuatro selectores del multiplexor debern ser los botnes de la tarjeta teniendo muy presente que dichos botones entregan un valor ALTO (1) cuando no estn siendo presionados. 2. Se debe especicar paso a paso el proceso desarrollado para la obtencin del diseo nal que soluciona el problema, incluir mapas de Karnaugh si es necesario. 3. Implementar el diseo en Quartus II, mostrar una imagen dentro del informe. 4. Realizar simulaciones en Quartus II del diseo nal, en estas simulaciones se deben procurar cubrir todos los posibles casos, para comprobar la validez de la solucin propuesta. 5. El circuito nal debe ser montado en el sistema de desarrollo de la Cyclone II. 6. Los resultados de la ALU debern ser observados en los display 7 segmentos de la tarjeta haciendo uso correcto de los decodicadores.

Incluir resultados de las simulaciones en el informe. El informe de laboratorio debe contener adems de su desarrollo, portada y conclusiones.

5.

O BSERVACIONES

La forma de calicacin se distribuir de la siguiente manera: 20 % Diseo (Incluye plan de prueba y la forma en la que ustedes piensen que puedan mostrar la solucin al problema planteado aprovechando los recursos, en este caso, la tarjeta FPGA). 30 % Comunicacin (Incluye el informe debidamente diligenciado, mostrando un proceso de trabajo para el desarrollo nal y unas conclusiones, adems incluye la forma de sustentacin del programa, la transmisin de la informacin) 50 % Simulacin y Funcionamiento (Programas en Quartus, simulado y quemado en la FPGA). Tenga en cuenta las siguientes recomendaciones: (a) Presente un informe impreso claro y ordenado en donde se consigne el procedimiento, los programas, las demostraciones, las guras, las respuestas, las justicaciones y los resultados obtenidos. Igualmente incluya conclusiones y la literatura consultada. El informe debe seguir la numeracin de la gua. (b) Tenga en cuenta las siguientes recomendaciones generales para el informe: Rotule con un nombre decente todas las entradas y salidas, sean pines o buses. Realice una revisin ortogrca y gramatical del reporte antes de entregarlo. Las faltas ortogrcas, la mala redaccin y los errores gramaticales se toman en cuenta para la calicacin del reporte. Las conclusiones deben ser concretas, especcas y estar soportadas por anlisis y resultados presentados en el reporte. (c) Las guas de laboratorio se desarrollan en tros y el informe se debe escribir siguiendo el formato de DOS COLUMNAS de la IEEE para conferencias IEEE Manuscript template for conference proceedings. El uso del formato IEEE en LATEX es recomendado. (d) Los informes de laboratorio deben ser entregados durante los primeros 5 minutos de la hora del laboratorio, despus de este plazo se calicar el reporte sobre 3.0. Fecha de entrega y sustentacin: Informe 4 de Octubre 7:30 A.M (Se revisar diagrama en quartus, simulacin y el modelo de pruebas en la tarjeta).

B IBLIOGRAFA

By Altera. Tutorial of ALTERA Cyclone II FPGA Starter Board By Altera. Cyclone II FPGA Starter Development Board Reference Manual

También podría gustarte

- Caso ValveDocumento2 páginasCaso ValveTomas GaviriaAún no hay calificaciones

- EETT Retenciones PreformadasDocumento45 páginasEETT Retenciones PreformadasAndrés MartinezAún no hay calificaciones

- Envoy Manual de Instalacion 60Hz ESDocumento67 páginasEnvoy Manual de Instalacion 60Hz ESAndrés MartinezAún no hay calificaciones

- Pref en z-PA RETENIDADocumento1 páginaPref en z-PA RETENIDAAndrés MartinezAún no hay calificaciones

- Pref Omega Dobl-DobleDocumento1 páginaPref Omega Dobl-DobleAndrés MartinezAún no hay calificaciones

- m215 m250 Manual Es LacDocumento50 páginasm215 m250 Manual Es LacAndrés MartinezAún no hay calificaciones

- Ej Res Ley AvoDocumento2 páginasEj Res Ley AvoAndrés Martinez100% (1)

- Brochure Formulación, Evaluación y Gestión de Proyectos MARZ 2023Documento15 páginasBrochure Formulación, Evaluación y Gestión de Proyectos MARZ 2023Andrés MartinezAún no hay calificaciones

- Pref en z-FICHADocumento1 páginaPref en z-FICHAAndrés MartinezAún no hay calificaciones

- Brochure Marketing Digital MARZ 24 - 2023Documento16 páginasBrochure Marketing Digital MARZ 24 - 2023Andrés MartinezAún no hay calificaciones

- 50217Documento2 páginas50217Andrés MartinezAún no hay calificaciones

- Examen Undecimo Grado Undecimo Lengua Periodo PrimeroDocumento4 páginasExamen Undecimo Grado Undecimo Lengua Periodo PrimeroAndrés MartinezAún no hay calificaciones

- Enlighten Feature Sheet EsDocumento4 páginasEnlighten Feature Sheet EsAndrés MartinezAún no hay calificaciones

- MT 2.41.58Documento73 páginasMT 2.41.58Francesc CapsirAún no hay calificaciones

- Programacion Eventos Academicos Feria 2 Ruedas 2017Documento1 páginaProgramacion Eventos Academicos Feria 2 Ruedas 2017Andrés MartinezAún no hay calificaciones

- Tabla PeriodicaDocumento21 páginasTabla PeriodicaAndrés MartinezAún no hay calificaciones

- Ejemplos de Preguntas Saber 9 Competencias Ciudadanas 2012 v3 PDFDocumento162 páginasEjemplos de Preguntas Saber 9 Competencias Ciudadanas 2012 v3 PDFJulieth Hernandez CruzAún no hay calificaciones

- Convert I R See Nun Habil Investiga DorDocumento36 páginasConvert I R See Nun Habil Investiga DorAndrés MartinezAún no hay calificaciones

- Sociales 35Documento1 páginaSociales 35Andrés MartinezAún no hay calificaciones

- 1-Presentación de CostosDocumento18 páginas1-Presentación de CostosAndrés MartinezAún no hay calificaciones

- Convert I R See Nun Habil Investiga DorDocumento36 páginasConvert I R See Nun Habil Investiga DorAndrés MartinezAún no hay calificaciones

- Apuntes Circuitos ElectricosDocumento13 páginasApuntes Circuitos Electricosjavier100% (20)

- Snacks N Nuts PortafolioDocumento8 páginasSnacks N Nuts PortafolioAndrés MartinezAún no hay calificaciones

- Como Convertirse en Un Habil Investigador, Wayne Booth Gregory Colomb Joseph WilliamsDocumento32 páginasComo Convertirse en Un Habil Investigador, Wayne Booth Gregory Colomb Joseph WilliamsVictor Paniagua MauleónAún no hay calificaciones

- ProjectDocumento2 páginasProjectAndrés MartinezAún no hay calificaciones

- ProjectDocumento2 páginasProjectAndrés MartinezAún no hay calificaciones

- 17 Guía9Documento16 páginas17 Guía9Andrés MartinezAún no hay calificaciones

- Jetta ClasicoDocumento4 páginasJetta ClasicoAndrés MartinezAún no hay calificaciones

- Dispositivos TiristoresDocumento26 páginasDispositivos TiristoresAndrés MartinezAún no hay calificaciones

- Jetta ClasicoDocumento4 páginasJetta ClasicoAndrés MartinezAún no hay calificaciones

- Equipos de ProteccionDocumento30 páginasEquipos de ProteccionBoris Alexander SanchezAún no hay calificaciones

- Formato Hoja de Vida Practicantes UniesDocumento3 páginasFormato Hoja de Vida Practicantes UniesNicolás UrueñaAún no hay calificaciones

- 004 - Circuito de Alumbrado de Las Zonas Comunes de Un Edificio. (Temporizador Retardo A La Desconexión)Documento3 páginas004 - Circuito de Alumbrado de Las Zonas Comunes de Un Edificio. (Temporizador Retardo A La Desconexión)José Luis Granero MontesinosAún no hay calificaciones

- Actualización XO 1.0: Solución errores actualizaciónDocumento10 páginasActualización XO 1.0: Solución errores actualizaciónvlackdrackAún no hay calificaciones

- Taller de Escritura Fundamento P. 695Documento897 páginasTaller de Escritura Fundamento P. 695Oscar Andrade EspinosaAún no hay calificaciones

- Recursos Hidricos DocDocumento34 páginasRecursos Hidricos DocMaria Celina MoyanoAún no hay calificaciones

- Informe AscensorDocumento9 páginasInforme AscensorLuis Bazan100% (1)

- Proyecto ISP Wireless: guía completa para iniciar un proveedor de servicios inalámbricoDocumento24 páginasProyecto ISP Wireless: guía completa para iniciar un proveedor de servicios inalámbricoMario JaraAún no hay calificaciones

- An TaminaDocumento9 páginasAn TaminaMilton Lugo CastilloAún no hay calificaciones

- Investigación - Concreto - Genesis A. Guevara AvilaDocumento22 páginasInvestigación - Concreto - Genesis A. Guevara AvilaAa.Aún no hay calificaciones

- Diagnostico ExternoDocumento10 páginasDiagnostico ExternoGiancarlo OnetoAún no hay calificaciones

- Especificación Revest. Ria. Monte AdentroDocumento15 páginasEspecificación Revest. Ria. Monte AdentroAntonioAún no hay calificaciones

- Pensum 288 UDO Ing. CivilDocumento4 páginasPensum 288 UDO Ing. CivilCristhian J. PiñangoAún no hay calificaciones

- Formulario Orden de ServicioDocumento3 páginasFormulario Orden de ServicioSusana Mileydi Alfaro LópezAún no hay calificaciones

- Operating Manual (Avh p6350bt Avh p5350dvd) EspDocumento120 páginasOperating Manual (Avh p6350bt Avh p5350dvd) EspDragonesta75% (4)

- Laboratorio #2 - Power Point 2016Documento10 páginasLaboratorio #2 - Power Point 2016Rodrigo AlbinagortaAún no hay calificaciones

- TESIS Nelson GonzalezDocumento111 páginasTESIS Nelson GonzalezRamon MartinezAún no hay calificaciones

- Guía para la preparación de artículos de investigaciónDocumento3 páginasGuía para la preparación de artículos de investigaciónStefy Gatita LindaAún no hay calificaciones

- Redes Distribución Media Tensión Subterráneas, HenyetDocumento13 páginasRedes Distribución Media Tensión Subterráneas, Henyethenyet medinaAún no hay calificaciones

- Amod Amod-515 ContenidosDocumento10 páginasAmod Amod-515 ContenidosAngel CaseresAún no hay calificaciones

- Software PQRS para atención de peticiones, quejas y reclamosDocumento8 páginasSoftware PQRS para atención de peticiones, quejas y reclamosrennemen75% (4)

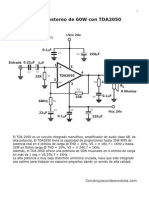

- Amplificador 60w Con Tda2050Documento8 páginasAmplificador 60w Con Tda2050david100% (1)

- Implementación de SAMBA en CentOS 7Documento4 páginasImplementación de SAMBA en CentOS 7Bryan JavierAún no hay calificaciones

- Pruebas de aceptación en equipos de alta tensiónDocumento336 páginasPruebas de aceptación en equipos de alta tensiónmartinAún no hay calificaciones

- Monografía - Santillan Ramirez Ruben Teodoro - Fac (Regularización)Documento105 páginasMonografía - Santillan Ramirez Ruben Teodoro - Fac (Regularización)urielahhAún no hay calificaciones

- Determinación de factores de tráfico para el diseño de pavimentosDocumento42 páginasDeterminación de factores de tráfico para el diseño de pavimentosMARIA BELEN MALDONADO MATUTEAún no hay calificaciones

- Guia Nº2Documento4 páginasGuia Nº2Marcos TiconaAún no hay calificaciones

- ExposiciónDocumento5 páginasExposiciónDAYHANNI RODRIGUEZ BELENAún no hay calificaciones

- PETROLEOS MEXICANOS NORMAS PARA PROYECTO DE OBRAS CONSTRUCCION DE CANALIZACIONES ELECTRICAS SUBTERRANEASDocumento96 páginasPETROLEOS MEXICANOS NORMAS PARA PROYECTO DE OBRAS CONSTRUCCION DE CANALIZACIONES ELECTRICAS SUBTERRANEASServando PerezAún no hay calificaciones

- PAYCLUB UnlockedDocumento193 páginasPAYCLUB UnlockedMax AguilarAún no hay calificaciones