Documentos de Académico

Documentos de Profesional

Documentos de Cultura

CMOS Inverter Cmosinv: Description

Cargado por

Cherry AbhiDescripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

CMOS Inverter Cmosinv: Description

Cargado por

Cherry AbhiCopyright:

Formatos disponibles

CMOS Inverter

cmosinv

In

Out

Description: This element models a CMOS inverter gate. Form: cmosinv:<instance name> n1 n2 n3 n4 <parameter list> n1 n2 n3 n4 Parameters: Parameter vtn: NMOS Threshold Voltage (V) vtp: PMOS Threshold Voltage (V) un: Effective Mobility of Electrons in NMOS ((cm^2)/(V-sec)) up: Effective Mobility of Electrons in PMOS ((cm^2)/(V-sec)) en: Permittivity of the Gate Insultor in NMOS (F/cm) ep: Permittivity of the Gate Insultor in PMOS (F/cm) tox: Thickness of the Gate Insulator (cm) wn: Channel Width of NMOS (cm) ln: Channel Length of NMOS (cm) wp: Channel Width of PMOS (cm) lp: Channel Length of PMOS (cm) td: Response Delay Time (sec) Example: cmosinv:inverter1 1 2 3 0 td=0.1e-6 Notes: This is an analog implementation of a digital inverter gate. Type TR_DOUBLE TR_DOUBLE TR_DOUBLE TR_DOUBLE TR_DOUBLE TR_DOUBLE TR_DOUBLE TR_DOUBLE TR_DOUBLE TR_DOUBLE TR_DOUBLE TR_DOUBLE Default Value 1 -1 500 200 34.515e-14 34.515e-14 2.0e-6 50e-6 2.0e-6 50e-6 2.0e-6 0 Required No No No No No No No No No No No No is the high voltage source (Vdd) terminal, is the input terminal, is the output terminal, is the ground or Vss terminal.

Known Bugs: No known bugs. Model documentation: n = (un)(en)(wn)/(tox)(ln) p = (up)(ep)(wp)/(tox)(lp) The operation of the CMOS inverter can be divided into five regions: Region A: 0 < Vin < VTn PMOS: nonsaturated; NMOS cutoff Vout = VDD IDSn = IDSp = 0 Region B: VTn < Vin < VDD/2 PMOS: nonsaturated; NMOS saturated IDSp = - p [(VDD - Vin - |VTp|)(VDD - Vout) (0.5)(VDD - Vout)2] IDSn = - IDSp Vout = (Vin VTp) + sqrt[(Vin VTp)2 2 VDD (Vin 0.5VDD - VTp) (n/ p) [(Vin VTp)2] Region C: Vin = VDD/2 PMOS: saturated; NMOS saturated IDSp = - 0.5p [(Vin - VDD - |VTp|)2] IDSn = - IDSp Vin VTn < Vout < Vin VTp Region D: VDD/2 < Vin < VDD + VTp PMOS: saturated; NMOS nonsaturated IDSp = - 0.5p [(Vin - VDD - |VTp|)2] IDSn = - IDSp Vout = (Vin VTn) + sqrt[(Vin VTn)2 (p/ n) [(Vin VDD - VTp)2] Region E: Vin > VDD + VTp PMOS: cutoff; NMOS nonsaturated Vout = Vss

References: Weste and Eshraghian, Principles of CMOS VLSI Design, Addison-Wesley, 1994 G.M. Glasford, Digital Electronic Circuits, Prentice-Hall, 1988

Sample Netlist: The following netlist plots the output voltage of the CMOS gate for an input voltage range of 0 ~ 5V. * CMOS Inverter Test .dc sweep="vsource:Vin" start=0 stop=5 step=0.1 vsource:Vdd 1 0 vdc=5 vsource:Vin 2 0 cmosinv:inverter 1 2 3 0 tr=0.5 tf=0.5 res:R 3 0 r=1000000 .out plot term 3 vt in "plot_cmos_inverter.out" .end Validation: The output graph from the above netlist is shown below:

Version: 2003.05.15 Credits: Name Affiliation Mazen M Kharbutli NCSU mazen_kharbutli@yahoo.com Date Links April, 2003 http://www4.ncsu.edu/~mmkharbu

También podría gustarte

- Cmos InverterDocumento64 páginasCmos InverterAkashAún no hay calificaciones

- Lecturer On Mos InverterDocumento24 páginasLecturer On Mos InvertersoumikbhAún no hay calificaciones

- KNL4343 VLSI Design and Technology Lecture 04: CMOS Inverter (Static View)Documento23 páginasKNL4343 VLSI Design and Technology Lecture 04: CMOS Inverter (Static View)yikamnnAún no hay calificaciones

- Pcirf 3 3 Mos 2Documento25 páginasPcirf 3 3 Mos 2Marius FerdyAún no hay calificaciones

- Mosfet Transistor Equations: University of Edinburgh EE4 Electrical EngineeringDocumento5 páginasMosfet Transistor Equations: University of Edinburgh EE4 Electrical EngineeringShachi P GowdaAún no hay calificaciones

- n-MOSFET (D) :: (I-V) Equations: Cut Off ModeDocumento6 páginasn-MOSFET (D) :: (I-V) Equations: Cut Off ModeJo KontAún no hay calificaciones

- Lecture 4 - CMOS InverterDocumento71 páginasLecture 4 - CMOS InverterShabeeb Ali OruvangaraAún no hay calificaciones

- ECEN325: Electronics Spring 2015: Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET)Documento18 páginasECEN325: Electronics Spring 2015: Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET)Joe KingAún no hay calificaciones

- Cmos Inverter CharacterizationDocumento54 páginasCmos Inverter CharacterizationVivekAún no hay calificaciones

- Amplifier Biasing TechniquesDocumento3 páginasAmplifier Biasing TechniquesMagnanil GoswamiAún no hay calificaciones

- Lecture03 B (MOSShortTransistors)Documento8 páginasLecture03 B (MOSShortTransistors)Yuichi SegawaAún no hay calificaciones

- Formula Sheet For Electronic Devices Final ExamDocumento2 páginasFormula Sheet For Electronic Devices Final Exammrdantownsend100% (1)

- Inverter NmosDocumento124 páginasInverter Nmosapoorva10393Aún no hay calificaciones

- 450 Μa, 5 Mhz Rail-To-Rail Op Amp: Features DescriptionDocumento32 páginas450 Μa, 5 Mhz Rail-To-Rail Op Amp: Features DescriptionYusuf UçkunAún no hay calificaciones

- Vlsi l4 Static Cmos InvDocumento26 páginasVlsi l4 Static Cmos InvSuriya SkariahAún no hay calificaciones

- Sol 3Documento23 páginasSol 3akakameyAún no hay calificaciones

- Formula SheetDocumento1 páginaFormula SheetdomingouclarayAún no hay calificaciones

- VLSI Design: Lecture 3a: Nonideal TransistorsDocumento30 páginasVLSI Design: Lecture 3a: Nonideal TransistorsBhagirath BhattAún no hay calificaciones

- The Cmos Inverter: Slides Adapted From: N. Weste, D. Harris, CMOS VLSI Design,, 3/e, 2004Documento40 páginasThe Cmos Inverter: Slides Adapted From: N. Weste, D. Harris, CMOS VLSI Design,, 3/e, 2004SrasVelAún no hay calificaciones

- VM Switching PowerDocumento81 páginasVM Switching PowerSuman MalikAún no hay calificaciones

- Lecture8 MOS TransistorDocumento21 páginasLecture8 MOS TransistorKartika MunirAún no hay calificaciones

- Lab Report2Documento4 páginasLab Report2Rinoop R UdinurAún no hay calificaciones

- MOS PPTDocumento13 páginasMOS PPTRenju TjAún no hay calificaciones

- Digital Integrated Circuits: A Design PerspectiveDocumento78 páginasDigital Integrated Circuits: A Design Perspectiveدانشجویان فوق لیسانس الکترونیک 91 سیرجانAún no hay calificaciones

- MOS Transistor Operation: S/D GateDocumento10 páginasMOS Transistor Operation: S/D GateConcetto CantoneAún no hay calificaciones

- Rabaey Chapter5Documento78 páginasRabaey Chapter5Vijay Kumar TAún no hay calificaciones

- CmosDocumento14 páginasCmosJannathul Firdous MohamedAún no hay calificaciones

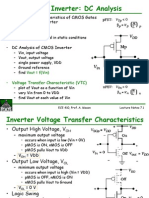

- CMOS Inverter: DC AnalysisDocumento32 páginasCMOS Inverter: DC Analysissreekanthreddy peram50% (2)

- Digital Integrated Circuits: A Design PerspectiveDocumento78 páginasDigital Integrated Circuits: A Design Perspectiveapi-127299018Aún no hay calificaciones

- Cmos Delay TimeDocumento17 páginasCmos Delay TimeCuong LaidangAún no hay calificaciones

- Inverter DynamicsDocumento86 páginasInverter DynamicsRajesh MahadevAún no hay calificaciones

- Lecture 17 - Linear Amplifier Basics - Outline: - AnnouncementsDocumento14 páginasLecture 17 - Linear Amplifier Basics - Outline: - Announcementsishanksinghthandi100% (2)

- Simplified CMOS Voltage Transfer Curve Step 1. Finding V: M M IN MDocumento6 páginasSimplified CMOS Voltage Transfer Curve Step 1. Finding V: M M IN MSeizalal SingsonAún no hay calificaciones

- Operation Mode: nMOS Operation Mode: pMOS: CMOS Inverter: Transient ResponseDocumento6 páginasOperation Mode: nMOS Operation Mode: pMOS: CMOS Inverter: Transient ResponseMostafa El AssyAún no hay calificaciones

- 2.9 Problems SolvedDocumento12 páginas2.9 Problems SolvedNajeeb Ur Rehman MalikAún no hay calificaciones

- 2sj 598 Power Mos Dell 2407wfpbDocumento8 páginas2sj 598 Power Mos Dell 2407wfpbkarkeraAún no hay calificaciones

- SFP 9520Documento7 páginasSFP 9520Leonardo NavarroAún no hay calificaciones

- HCTM Ece StudentsDocumento22 páginasHCTM Ece StudentsMunish VermaAún no hay calificaciones

- Active LoadDocumento69 páginasActive LoadVijay P. LabdeAún no hay calificaciones

- MOS Transistors and CMOS InvertersDocumento34 páginasMOS Transistors and CMOS InvertersGaurav GopalkrishnaAún no hay calificaciones

- N Channel MOSFET Level 1Documento5 páginasN Channel MOSFET Level 1Kyusang ParkAún no hay calificaciones

- Lecture13Documento5 páginasLecture13ohenri100Aún no hay calificaciones

- Sol 3Documento22 páginasSol 3ee206023Aún no hay calificaciones

- Homework 3 - SolutionsDocumento14 páginasHomework 3 - SolutionsYahya Salam SalehAún no hay calificaciones

- Vlsi Classroom Material (16-Aug-2011)Documento37 páginasVlsi Classroom Material (16-Aug-2011)naveensilveriAún no hay calificaciones

- Lecture17 Ee474 Folded Cascode OtaDocumento17 páginasLecture17 Ee474 Folded Cascode OtaRinkitori NorikarinAún no hay calificaciones

- EE5518 VLSI Digital Circuit Design VLSI Digital Circuit DesignDocumento39 páginasEE5518 VLSI Digital Circuit Design VLSI Digital Circuit DesignBharat Kumar100% (1)

- MOSFET Structure: Source Gate Drain Field Oxide Gate OxideDocumento12 páginasMOSFET Structure: Source Gate Drain Field Oxide Gate OxideRaj HakaniAún no hay calificaciones

- Digital Integrated Circuits: A Design PerspectiveDocumento55 páginasDigital Integrated Circuits: A Design Perspectiveapi-127299018Aún no hay calificaciones

- N Channel MOSFET Level 3Documento6 páginasN Channel MOSFET Level 3Kyusang Park100% (1)

- Vlsi ManualDocumento60 páginasVlsi Manualdilawar sumraAún no hay calificaciones

- Microdevices: Mosfets - Metal Oxide Field Effect Transistors N MosfetDocumento11 páginasMicrodevices: Mosfets - Metal Oxide Field Effect Transistors N Mosfetblue7nicoAún no hay calificaciones

- Recitation 10: MOSFET VI Characteristics - Channel Length Modulation & Back Gate EffectDocumento7 páginasRecitation 10: MOSFET VI Characteristics - Channel Length Modulation & Back Gate EffectLavanya SomulaAún no hay calificaciones

- Mosfet 01Documento56 páginasMosfet 01Edward Allan MangubatAún no hay calificaciones

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDe EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsAún no hay calificaciones

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsDe EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsCalificación: 1 de 5 estrellas1/5 (1)

- Randomized Partially-Minimal Routing Architecture For 3-D Mesh Network On ChipsDocumento7 páginasRandomized Partially-Minimal Routing Architecture For 3-D Mesh Network On ChipsCherry AbhiAún no hay calificaciones

- Standard Cell CharacterizationDocumento26 páginasStandard Cell CharacterizationVinayaka HmAún no hay calificaciones

- Miller Compensation Pole Spiting and ZeroDocumento8 páginasMiller Compensation Pole Spiting and ZeroShreerama Samartha G BhattaAún no hay calificaciones

- Hspice SaDocumento1024 páginasHspice SaCherry AbhiAún no hay calificaciones

- SAED90DR Rev1 2 21.01.2011Documento24 páginasSAED90DR Rev1 2 21.01.2011Cherry AbhiAún no hay calificaciones

- Latch UpDocumento4 páginasLatch UpCherry AbhiAún no hay calificaciones

- C Lecture NotesDocumento188 páginasC Lecture Notessurendraaalla0% (1)

- NXP I C Technical Questions and Answers - 2006Documento9 páginasNXP I C Technical Questions and Answers - 2006Cherry AbhiAún no hay calificaciones

- Logic Synthesis: Hsi-Pin Ma (馬席彬)Documento39 páginasLogic Synthesis: Hsi-Pin Ma (馬席彬)Cherry AbhiAún no hay calificaciones

- Model Test PaperDocumento3 páginasModel Test PaperNishant Panchal100% (1)

- Analog Electronics Constant GM CircuitDocumento11 páginasAnalog Electronics Constant GM CircuitMonique Kirkman-BeyAún no hay calificaciones

- Ece-V-fundamentals of Cmos Vlsi (10ec56) - Question PaperDocumento7 páginasEce-V-fundamentals of Cmos Vlsi (10ec56) - Question PaperAbhilash ReddyAún no hay calificaciones

- An 80-Mv-To-1.8-V Conversion-Range Low-Energy Level Shifter For Extremely Low-Voltage VlsisDocumento10 páginasAn 80-Mv-To-1.8-V Conversion-Range Low-Energy Level Shifter For Extremely Low-Voltage VlsisKavyashreeMAún no hay calificaciones

- Logic Design Styles: Dinesh SharmaDocumento6 páginasLogic Design Styles: Dinesh SharmaAnonymous hsb1qnt3BAún no hay calificaciones

- Lecture 7: Dynamic Circuits: High Speed CMOS VLSI DesignDocumento15 páginasLecture 7: Dynamic Circuits: High Speed CMOS VLSI DesignCecilia ChinnaAún no hay calificaciones

- Gate Driver For N-Channel Mosfet: Experiment 6Documento34 páginasGate Driver For N-Channel Mosfet: Experiment 6Noona MigleiAún no hay calificaciones

- 55:041 Electronic Circuits: Sections of Chapter 3 &4Documento97 páginas55:041 Electronic Circuits: Sections of Chapter 3 &4Daniel GarzonAún no hay calificaciones

- L04 NMOS Inverter With A Resistive LoadDocumento11 páginasL04 NMOS Inverter With A Resistive LoadMohammad MostafaAún no hay calificaciones

- Subsystem Design: Architectural IssuesDocumento26 páginasSubsystem Design: Architectural IssuesSanjana M PAún no hay calificaciones

- Sol 3Documento23 páginasSol 3akakameyAún no hay calificaciones

- ComosDocumento36 páginasComosmelvin45Aún no hay calificaciones

- M.tech - Thesis SramsDocumento69 páginasM.tech - Thesis SramsRatnakarVarunAún no hay calificaciones

- Delay Analysis of Half Subtractor Using CMOS and Pass Transistor LogicDocumento6 páginasDelay Analysis of Half Subtractor Using CMOS and Pass Transistor LogicSaravanan NsAún no hay calificaciones

- LPVLSI Unit 2 NotesDocumento51 páginasLPVLSI Unit 2 NotesSai Sreeja100% (2)

- Chapter 5Documento61 páginasChapter 5Faiz MohdAún no hay calificaciones

- PRACTICAL1Documento7 páginasPRACTICAL1Boy MachoAún no hay calificaciones

- Ee6301 DLLC Notes RejinpaulDocumento104 páginasEe6301 DLLC Notes RejinpaulAnney RevathiAún no hay calificaciones

- Comprehension - PDF - Electronic Devices and Analog Circuits - Electronic Devices and Analog CircuitsDocumento36 páginasComprehension - PDF - Electronic Devices and Analog Circuits - Electronic Devices and Analog Circuitssai JanhaviAún no hay calificaciones

- Ee288 5bit Flashadc ProjectDocumento5 páginasEe288 5bit Flashadc ProjectbearunagiriAún no hay calificaciones

- Lab4 Nand Schem SimDocumento20 páginasLab4 Nand Schem SimraghuippiliAún no hay calificaciones

- Low Power-Area Designs of 1bit Full Adder in Cadence Virtuoso PlatformDocumento10 páginasLow Power-Area Designs of 1bit Full Adder in Cadence Virtuoso PlatformAnonymous e4UpOQEPAún no hay calificaciones

- Experiment No.: 02 Experiment Name: ObjectiveDocumento11 páginasExperiment No.: 02 Experiment Name: ObjectiveNahin Amin100% (2)

- Unit 3Documento59 páginasUnit 3bhupendra1977Aún no hay calificaciones

- 2017 Ch3-2-Circuit Layout Rev1 EulerDocumento72 páginas2017 Ch3-2-Circuit Layout Rev1 EulerNhân LêAún no hay calificaciones

- VLSI Design Lab PDFDocumento109 páginasVLSI Design Lab PDFKvnsumeshChandraAún no hay calificaciones

- Vlsi Design PQDocumento3 páginasVlsi Design PQAkanksha DixitAún no hay calificaciones

- VLSI Backend Lab ManualDocumento56 páginasVLSI Backend Lab ManualAllanki Sanyasi Rao100% (1)

- Vlsi Design PDFDocumento120 páginasVlsi Design PDFHareesh Harsha100% (1)

- CS 801D PDFDocumento4 páginasCS 801D PDFarnab paulAún no hay calificaciones