Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Single-Phase Five-Level Inverter With Less Number of Power Elements For Grid Connection

Cargado por

vinay kumarDescripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Single-Phase Five-Level Inverter With Less Number of Power Elements For Grid Connection

Cargado por

vinay kumarCopyright:

Formatos disponibles

Single-Phase Five-Level Inverter with Less

Number of Power Elements for Grid Connection

Mahrous Ahmed, IEEE Member, Maha G. Elsheikh, Mahmoud A. Sayed, IEEE Member, and Mohamed Orabi,

IEEE Senior Member.

APEARC, Aswan Faculty of Engineering, South Valley University, Aswan City 81542, Egypt

orabi@ieee.org

Abstractrecently, the emergence of single phase multilevel

inverter has been increased due to its advantages over

traditional one. This paper proposes a single-phase five level

pulse width modulation (PWM) inverter for grid connection

employing PI controller to perform unity power factor. Two

triangular carrier signals identical to each other with an

offset equivalent to the amplitude of the reference signal were

used to generate PWM signals for the switches. The proposed

inverter has the advantage of less number of components.

Operational principles with switching functions are analyzed.

A digital proportional integral current control algorithm is

implemented in FPGA XC3S400 to control the injected

current into the grid to be almost sinusoidal. The inverter

offers much less total harmonic distortion and can operate at

near-unity power factor. Some switches operate at

fundamental frequency and others operate at switching

frequency. The proposed inverter has been compared with

the conventional single-phase five-level PWM inverter. The

effectiveness of the proposed inverter and its control

technique has been verified theoretically, using PSIM

simulation program, and experimentally, using laboratory

prototype system.

Keywords Multi-Level Inverters, Grid Connection, PWM.

I. INTRODUCTION

Multilevel Inverters (MLI) began with the neutral point

clamped inverter topology proposed by Nabae et al. [1].

Recently, multilevel inverters have become more attractive

for researchers due to their advantages over conventional

three-level pulse width-modulated (PWM) inverters. MLI

has two main advantages compared with the conventional

H-bridge inverters [2-4], the higher voltage capability and

the reduced harmonic content in the output waveform due

to the multiple dc levels. MLI is now preferred in high

power medium voltage applications due to the reduced

voltage stresses on the devices. MLI incorporates a

topological structure that allows a desired output voltage to

be synthesized among a set of isolated or interconnected

distinct voltage sources. Numerous topologies realize this

connectivity, and can be generally divided into three major

categories, namely, diode clamped MLI, flying capacitor

MLI, and separated dc sources (cascaded voltages) MLI [5].

Recently renewable energy sources for grid connected

applications are increased due to the world energy crisis.

Injecting power to the utility must meet the world harmonic

standards. Therefore, single phase MLIs become a good

solution for those applications [6-7]. Unfortunately one of

the most particular disadvantages of MLI is the large

number of the required power semiconductor switches.

Although low voltage rate switches can be utilized in a

multilevel inverter, each switch requires a related gate drive

circuit. This may cause the overall system to be more

expensive and complex. So, in practical implementation,

reducing the number of switches and gate driver circuits

have become an essential point.

Recently, many topologies of the MLI and its control

techniques have been published. The MLI technique is

implemented in [8] by adding one switch and four power

diodes to the H-bridge single phase inverter. Another

solution can be found in [9] by using two switches and two

power diodes with the H-bridge single phase inverter.

Those two systems can generate only five levels in the

output voltage with less harmonic contents. The other

solution, shown in [10], is a modular inverter that can reach

to any required voltage levels. But these inverters

topologies can be improved by reducing their switches

without affecting their performances.

This paper presents a single-phase five-level PWM

inverter with less number of power elements and hence less

gate drive circuits in addition to less circuit layout

complexity. Its output voltage has the following five levels:

Zero, +Vdc, +2Vdc, Vdc, and 2Vdc. As the number of

output levels increases, the harmonic content can be

reduced. This inverter topology uses two carrier signals to

generate PWM signals for the switches. Some switches

operate at fundamental frequency and others operate at

switching frequency. Sections II and III explain the

principle of operation and PWM strategy for the proposed

inverter, respectively. The switching algorithm that used in

PWM is presented in section IV. Section V contains a

harmonic analysis for MLI. Moreover, a results and

comparison between the proposed MLI inverter and

conventional one are presented in section VI.

Simulation and experimental results are included in

order to verify the operating principle of the proposed MLI

inverter and its capability to inject active power to the grid.

978-1-4577-1216-6/12/$26.00 2012 IEEE 1521

II. OPERATIONAL PRINCIPLE OF THE PROPOSED

INVERTER

Figure 1 shows the proposed structure single phase MLI

inverter. It consists of n cells of switch circuits. For cells

from 1 to (n-1), each k-cell is composed of one dc voltage

source and two switches (S

k1

, S

k2

); one switch (S

k2

) is

connected in series with a dc voltage source and the other

switch ( S

k1

) is connected in parallel with both the dc

voltage source and the series switch. Based on this

configuration, each cell can generate two states (0 V) and

the dc voltage source associated with the considered cell.

Cell n is composed of only the dc source voltage resulting

in generating only one state (Vn). As a result, the dc link

voltage v

bus

has (n-1) states, they are (v

1

, v

2

, , v

n

), as

shown in Fig. 2.

Figure 1: Structure of The Proposed Cascaded dc Link MLI.

Figure 2: Typical Output Waveform of v

dc

It can be noted that the dc link voltage has no zero state

voltage (0V) which needs extra two main switches. The H-

bridge inverter composes of four switches

( Q

1

, Q

2

, Q

S

, anu Q

4

). The H-bridge inverter has two

functions; it has to synthesis the inversion voltage of the dc

link voltage in addition to generating the zero state voltage

(0V) at the output voltage (v

ab

) by connecting the upper

two switches ( Q

1

, Q

S

) or the lower switches ( Q

2

, Q

4

).

Obviously, this structure can reduce the number of switches

compared to the conventional topologies without affecting

the inverter performances. This is due to that; the zero

voltage can be generated using the idea of the upper or

lower H-bridge inverter to generate this state.

The pulse width modulation (PWM) control algorithm

can be applied, also, for this topology. The PWM control

algorithm, which adopted in this paper, consists of one

modulation signal with amplitude (A

r

) and n (number of dc

link cell) carriers with same amplitude (A

c

). Each carrier is

shifted with the carrier amplitude (A

c

) from the former one.

The amplitude ( A

r

) can be changed from 0 to n - A

c

according to changing modulation index from 0 to 1.

III. SINGLE-PHASE FIVE-LEVEL PWM INVERTER

In order to generate five levels, the number of the

required cascaded cell is n = 2. One cell uses two switches

with the dc source while the other cell is only the dc source

as shown in Fig. 3. Assume that the dc voltage sources are

equal; v

1

= v

2

= v

dc

. The dc link bus voltage v

bus

will

have two states, v

dc

or 2v

dc

, and the load output voltage

will have five states 2v

dc

, v

dc

, u, -v

dc

, - 2v

dc

. The zero

state can be generated either by switching the upper

switches together or the lower switches together. The other

four states can be generated from the dc bus voltage v

bus

based on folded cascade unit operation.

The operation of the single-phase five-level inverter,

employing PWM, can be divided into 10 switching states

based on the direction of the output current as given by

table I. The signal generation waveforms are generated

using one modulating signal and two carriers. The

amplitude of the modulating signal is ( A

r

) and the

amplitude of each carrier is (A

c

). In addition, each carrier is

shifted with the carrier amplitude (A

c

) from the former one,

as shown in Fig. 4.

Figure 3: proposed Single-Phase Five-Level Inverter Configuration.

Figure 4: PWM Switching Strategy.

1522

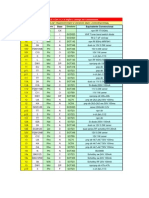

TABLE I. OPERATIONAL STATES ACCORDING TO THE SWITCH ON

CONDITIONS AND THE DIRECTION OF THE LOAD CURRENT

Switching

States

The Output

Voltage (v

ab

)

The Direction of

the Output

Current (t

u

)

ON State

Switches

1 v

dc

positive Q

1

, Q

2

anu S

11

2 v

dc

negative B

1

, B

2

anu S

11

3 2v

dc

positive Q

1

, Q

2

anu S

12

4 2v

dc

negative B

1

, B

2

anu S

12

5 0

positive Q

1

, B

3

or Q

2

, B

4

6 0

negative B

1

, Q

3

or B

2

, Q

4

7 -2v

dc

positive B

3

, B

4

, anu S

12

8 -2v

dc

negative Q

3

, Q

4

, S

12

9 -v

dc

positive B

3

, B

4

, anu S

11

10 -v

dc

negative Q

3

, Q

4

, anu S

11

IV. SWITCHING ALGORITHM FOR THE PROPOSED

INVERTER USING PWM

The switching patterns employed in the proposed

inverter are illustrated in Fig. 5. The output voltage levels,

according to the switch ON/OFF conditions, are shown in

Table II. In this paper, the switching strategy used to

generate the gate signals is accomplished by comparing the

reference signal, which is rectified sinusoidal, with two

triangular carrier waveforms having the same frequency

and phase angle, but with different offset voltages. When

the lower carrier signal is compared with the reference

signal, the first level of output voltage will be generated.

This means that the modulation index (MI) is less than or

equal 0.5 (50%). The behavior of proposed inverter is

similar to the conventional fullbridge three-level PWM

inverter. The distribution of the harmonic components in

output voltage is similar to that of the conventional inverter

having the values of two times the modulation index. The

mentioned above is the first operational mode. On the other

hand, if the required output voltage is increased beyond the

modulation index 0.5, the output will result from comparing

the upper carrier signal with the same reference signal.

Therefore, the second level of the output voltage will be

generated and it will be the second mode. According to the

amplitude of the voltage reference, the operational interval

of each mode varies within a certain period.

The modes are determined as the phase angle depends

on the modulation index.

Noue A: u < wt 01, 02 < wt n

Noue B: 01 < wt 02

Noue C: n < wt 0S, 04 < wt 2n

Noue B: 0S < wt 04 (1)

The modulation index HIof the proposed five-level PWM

inverter is defined as follows [11]:

HI =

A

M

2 A

C

(2)

Where:

A

M

The peak value of the modulating (sinusoidal) signal,

i.e. the voltage reference (:

c]

) .

A

C

The peaktopeak value of the carrier (triangular).

1

2 4

Figure 5: Switching Patterns of The Proposed Inverter.

Also, the frequency ratio, m

]

is defined as follows:

m

]

=

]

c

]

m

(3)

Where:

c

The frequency of the carrier (triangular) signal.

m

The frequency of the modulating (sinusoidal) signal.

1523

When the modulation index is less than 0.5, the phase angle

displacement is equal to:

0

1

= 0

2

=

n

2

, 0

3

= 0

4

=

3n

2

(4)

And when the modulation index is greater than 0.5, the

phase angle displacement is

0

1

= sin

-1

_

A

C

A

M

]

0

2

= n - 0

1

0

3

= n + 0

1

0

4

= 2 n - 0

1

(5)

The switching Patterns of the proposed inverter is

illustrated in Fig. 5. In one period, switches Q

1

and Q

4

operate at the fundamental frequency (i.e., 50 Hz). The

switch S

11

will be completely switched at the carrier signal

frequency, whereas Q

2

and Q

3

will be switched in both low

and high switching frequency. The switch S

12

is switching

at high frequency in a certain time of the period and off

elsewhere. The output voltage according to the switch

ON/OFF conditions is shown in Table II.

As shown in Fig. 5, the control signals are generated by

the signals C

A

and C

B

, coming from the comparators, which

compare the respective carrier signals with the voltage

reference (v

rcI

). The main six periods P1, P2, P3, P4, P5

and P6 can be calculated from the intersection of the

reference waveform with the carrier signals. Then switches

signals Q

1

- Q

4

, S

11

- S

12

can be formulated based on

P1, P2, P3, P4, P5 and P6 by the phase angle displacement

as given by equation (6).

Figure 6 describes a simplified description for generating

the control signals of switches Q

1

- Q

4

, S

11

- S

12

. The

switching functions of proposed inverter are then given by

the logical (AND, OR, NOT) gates as follows:

1

= P

1

+ P

2

+ P

3

2

= ((P

1

+ P

2

+ P

3

) . C

A

) + [(P

4

+ P

6

) C

A

3

= [(P

1

+ P

3

) C

A

+ ((P

4

+ P

6

+ P

5

) C

A

)

4

= P

4

+ P

5

+ P

6

S

11

= [((P

1

+ P

3

) +(P

4

+P

6

)) C

A

+ [(P

2

+ P

5

) C

B

S

12

= (P

2

+ P

5

) C

B

(6)

V. HARMONICANALYSIS

The harmonic components in output voltage of the

proposed inverter are calculated as follows. From the two

carrier waves and output voltage in Figure5, the Analysis of

harmonic components in the proposed inverter can be

performed. The output voltage produced by comparing the

reference signal and two carrier waves can be expressed as:

I

0

(0) = A

0

+ (A

k

cos k0 + B

k

sink0)

k=1

(7)

TABLE II. OUTPUT VOLTAGE ACCORDING TO THE SWITCH ON/OFF

CONDITIONS

Figure 6: Simplified Descriptions for Generating The Control Signals of

The Inverter Switches.

If there are 'P' pulses per a quarter periods and it is an

odd number, the coefficients B

k

and A

O

will be zero, where

'k' is an even number. Therefore, equation (7) can be

rewritten as follows:

I

0

(0) = A

k

cos k0

k=1,3,

(8)

A

k

= -

2v

dc

kn

j(-1)

nt(

2

, )

sin(ko

m+

)[

4

=1

P

m=0

(9)

Where, 'm' is a pulse number. The Fourier series

coefficients of the conventional Single-phase full-bridge

inverter by sinusoidal PWM are given as:

A

k

=

4V

dc

k

|(-1)

m

sin(k

m

)]

P

m=1

(10)

Vab

Switches State

Q1 Q2 Q3 Q4 S11 S12

+ 2vuc ON ON OFF OFF OFF ON

+ vuc ON ON OFF OFF ON OFF

u

ON OFF ON OFF OFF OFF

OFF ON OFF ON OFF OFF

- vuc OFF OFF ON ON ON OFF

- 2vuc OFF OFF ON ON OFF ON

1524

VI. RESULTS AND DISCUS

The feedback controller used in this a

the PI algorithm as shown in Fig. 7. The g

grid voltage v

g

are detected by sensors fo

estimate the reference grid current I

rc

amplitude is assumed constant and it

obtained from grid voltage waveform

power factor. The instantaneous current e

controller. The resulting error signal (u)

is compared with the two triangular

produce PWM signals for the switches

XC3S400 is used as a controller in the lab

Proposed topology has been simul

software to verify the performance

configuration. A two cells (n = 2) with

voltage waveform has been chosen and si

the topology can be extended to n ce

control for grid connection with wide ran

index has been simulated at 10 kHz sw

Two identical power supplies of 20 V ea

for the dc bus (>2 v

g

; in this case, v

g

order to inject current into the grid. The

the shape of the inverter output voltage

current i

g

. Figure 8 (a), (b), and (c) s

output voltage v

Inv

and the grid current

0.4, 0.8, and 1.2 respectively. When the m

less than or equal 0.5 (1/n), the behavio

inverter will be similar to the conventiona

level PWM inverter. In this case the lowe

always disconnected (S

11

is always ON

OFF) and the upper capacitor only is use

and generate v

ab

. As shown in figure 8(a

here that v

Inv

at 0.4 value of NI is less

means that the current will be injected fro

inverter so this condition must be avoid

inverter from damage. In case of over mo

NI =1.2, the reference signal exceed

amplitude of both carrier signals. This wi

a at portion at the peak of the waveform

pure sinusoidal waveform. Whereas whe

index is larger than 0.5 (1/n) and less th

capacitor will share the upper capacitor

resulting in five-level inverter output volta

Figure 7: Five-Level Inverter with PI Contro

SSION

application utilizes

grid current I

g

and

for the controller to

cI

. The reference

ts phase angle is

to achieve unity

error is fed to a PI

) which forms v

rcI

carrier signals to

s. A FPGA kit of

boratory prototype.

lated using PSIM

of the proposed

h five-level output

imulated. However

lls. A closed loop

nge of modulation

witching frequency.

ach have been used

is 30 V RMS) in

NI will determine

e v

In

and the grid

hows the inverter

t i

g

at NI equal to

modulation index is

or of the proposed

al full bridge three-

er capacitor bank is

and S

12

is always

ed to feed the load

a). It can be noted

s than 2 v

g

. This

om the grid into the

ded to protect the

odulation index, at

ds the maximum

ill cause i

g

to have

m, so it will not be

en the modulation

han 1.0, the lower

r in generating v

ab

age.

oller Algorithm.

TABLE III. CURRENT AND VO

SWITCH

Max Curren

All switches

max voltage

S

11

, S

12

Q

1

, Q

2

, Q

3

, and Q

4

max maximum

TABLE IV. COMPONENT COMPAR

AND OTH

1

st

[8]

m

Main switches

(m-1)*2

Main diodes

TABLE V. COMPONENT COMPA

OUTPUT VO

1

st

[8]

S

Main switches

4

Main diodes

So, to optimize the power tr

grid, it is recommended to o

shown from the inverter output

Fig. 8(b). It is clear that the gri

sinusoidal waveform and thus

drastically.

To validate the proposed

prototype of the proposed five-

experimentally carried out,

simulation results. Fig. 9 sh

laboratory. The inverter circuit

MOSFET as switches. The u

10 kHz. The switching signa

FPGA of type XC3S400 as a

power supplies of 20 V each we

The proposed inverter syst

using closed loop condition f

current controller, which is

XC3S400 and with L filter e

inverter voltage v

Inv

and g

measured for two values of M

than 0.5 as shown in Fig. 10 (

more for MI less than 0.5 the

inverter will be same as the

three-level inverter. The grid

greater than 0.5 are shown in

proposed system can inject activ

Figure 12 shows the gate

greater than 0.5. It can be noted

at line frequency and others

frequency. Switch voltage and

measured as shown in table III

carry load current and thus thei

it. The H-bridge inverter sw

OLTAGE RATING FOR INVERTER

HES

nt ratings

%(Iswitch/ILoad)max = 100

e ratings

%(Vswitch max/Vdc) = 1/n=0.5

%(Vswitch max/Vdc) = 1

RISION FOR THE PROPSED INVERTER

HERS

proposed 2

nd

[10]

m+1 m+3

0 0

ARISON FOR PRODUCING A 5-LEVEL

OLTAGE

proposed 2

nd

[10]

6 8

u u

ransferred from dc link to the

perate at 0.5 NI 1.0 as

t voltage and grid current in

id current i

g

is almost a pure

s the THD can be reduced

d inverter, an experimental

level inverter has been built,

and compared with the

hows the system setup in

t has been built using power

used switching frequency is

als are generated using an

controller. Two identical dc

ere used for the dc bus.

tem is tested experimentally

for grid connection with PI

implemented into FPGA

qual to 3.3mH. The output

grid current I

g

have been

MI greater than 0.5 and less

(a) & (b) respectively. Once

e behavior of the five-level

e conventional single-phase

voltage and current for MI

Fig. 11. It is clear that the

ve power into the grid.

signals of switches for MI

d that some switches operate

s operate at the switching

d current ratings have been

I. It is clear that all switches

ir current ratings depends on

witches have higher voltage

1525

ratings compared to the cell switches; the

voltage as a maximum voltage rating

switches have equal voltage blocking ca

proportional with the number of cell n.

Figure 8: Inverter Output Voltage (v

Inv

) and Gr

Different NI.

(a) For NI<0.5 (b) For u.S NI 1.u

Figure 9: Prototype of The Proposed Five-Lev

(a)

(b)

(c)

ey have the cell dc

g. While the cell

apability inversely

rid Current (I

g

) for

(c) For NI>1.

vel PWM Inverter.

By comparing the prop

conventional single phase inve

[8], [9], and [10], it is found th

only six switches and no pow

switches and four power diode

two main power diodes as in [9

In general, for a given numb

proposed inverter requires (m+

diodes, whereas the inverter in

and (m-1)*2 power diodes. The

and then less efficiency. In

(Cascaded inverter type) shown

switches are (m+3), that means

two switches less. Table IV

number of switches and diode

compared with that in [8] and

output voltage levels (m).

Table V shows a compariso

switches and main diodes amon

and the one in [8], and [10] in

voltage. It clearly shows t

reduction in the proposed

components grows as the n

increases. Therefore, the prop

switch, less gate drive, cost redu

(a)

(b)

Figure 10: Experimental Inverter Outp

(I

g

) for Diff

(a) For u.S NI 1.u ,

posed inverter with three

erter topologies explained in

hat the proposed inverter has

wer diodes compared to five

es in [8], or six switches and

9], or eight switches in [10].

er of voltage levels m, the

+ 1) active switches and no

n [8] requires (m) switches

ese diodes cause more losses

another inverter topology,

n [10], the number of active

s the proposed inverter have

V summarizes the required

es of the proposed inverter

[10] for a given number of

on considering the number of

ng the new proposed inverter

n case of five levels output

the substantial component

structure. This saving in

number of voltage levels

posed inverter provides less

uction, and high efficiency.

put Voltage (v

Inv

) and Grid Current

ferent NI

, (b) For NI u.S

1526

Figure 11: Experimental Grid Voltage (v

g

) and Current (I

g

)

for u.S NI 1.u

Figure 12: Gate Pulses of Switches for u.S NI 1.u.

VII. CONCLUSION

This paper has presented a new single-phase five-level

PWM inverter with grid connection control. The proposed

control technique for PWM switching and for the grid

injected current control has been presented. A digital PI

current control algorithm is implemented in FPGA

XC3S400 to optimize the performance of the proposed

inverter. The major benefits of the proposed inverter are

summarized as follow:

- It has less number of power elements.

- Some switches operate at fundament load

frequency and others operate at carrier frequency.

- Smaller filter size, less circuit layout complexity

and high efficiency can be achieved.

Both the grid voltage and the grid current are in phase,

so the system operates at unity power factor, and hence

inject active power to the grid. Simulation and experimental

results prove that the proposed single-phase multilevel

inverter has the capability of grid connection with high

efficiency as compared with conventional type.

ACKNOWLEDGMENT

This work is sponsored by Egyptian Science and

Technology Development Funds (STDF) under STDF

project # 658. Any opinions, findings, and conclusions or

recommendations expressed in this material are those of the

author(s) and do not necessarily reflect the views of the

funding agencies.

REFERENCES

[1] Nabae, A., Takahashi, I., and Akagi, H., "A new neutral-point

clamped PWM inverter", IEEE Transactions on Industrial

Applications, Vol. IA-17, pp. 518-523, September/October 1981.

[2] Siriroj Sirisukprasert, Jih-Sheng Lai, and Tian-Hua Liu, "Optimum

harmonic reduction with a wide range of modulation indexes for

multilevel converters", IEEE Transactions on Industrial on

Electronics, Vol. 49, Issue 4, pp. 875-881, August 2002.

[3] Brendan Peter McGrath, and Donald Grahame Holmes,

Multicarrier PWM strategies for multilevel inverters; IEEE

Transactions on Industrial Electronics, Vol. 49, Issue 4, pp. 858-

867, August 2002.

[4] Lai, J. S., and Peng, F. Z., Multilevel convertersa new breed of

power converters, IEEE Transactions on Industrial Applications,

vol. 32, Issue 3, pp. 509-517, May/June 1996.

[5] Villanueva, E.; Correa, P.; Rodriguez, J.; Pacas, M., Control of a

Single-Phase Cascaded H-Bridge Multilevel Inverter for Grid-

Connected Photovoltaic Systems, IEEE Transactions on Industrial

Electronics, Vol. 56 , Issue 11, 2009, pp. 4399-4406.

[6] Lee, S.J.; Bae, H.S.; Cho, B.H., Modeling and control of the single-

phase photovoltaic grid-connected cascaded H-bridge multilevel

inverter, IEEE on Energy Conversion Congress and Exposition

(ECCE), 2009, pp. 43-47.

[7] Jos Rodrguez, Jih-Sheng Lai, and Fang Zheng Peng, "Multilevel

inverters: a survey of topologies, controls, and applications", IEEE

Transactions on Industrial Electronics, Vol. 49, Issue 4, pp. 724-

738, August 2002.

[8] Sung-Jun, Park,Feel-Soon Kang, Man Hyung Lee, and Cheul-U

Kim, "A New Single-Phase Five-Level PWM Inverter Employing a

Deadbeat Control Scheme", IEEE Transactions on power

electronics, Vol. 18, No. 3, May 2003, pp: 831-843

[9] Agelidis, V. G., Baker, D. M., Lawrance, W. B., andNayar, C.

V.,A multilevel PWM inverter topology for photovoltaic

applications, Proceedings of the IEEE International symposium on

Industrial Electronics, Vol. 2, pp. 589-594, July 1997, Portugal,

Guimaraes.

[10] Gui-Jia Su, Multilevel DC-Link Inverter, IEEE Transactions on

Industry Applications, Vol. 41, No. 3, May/June 2005, pp. 848-854.

Q

1

Q

4

Q

2

Q

3

S12

S11

1527

También podría gustarte

- Bluedart Express LTD - Tracking Details PDFDocumento1 páginaBluedart Express LTD - Tracking Details PDFvinay kumarAún no hay calificaciones

- Solutions 8: Semiconductor Nanostructures Thomas Ihn Fall 2017Documento2 páginasSolutions 8: Semiconductor Nanostructures Thomas Ihn Fall 2017ApuAún no hay calificaciones

- DGS 700 ManualDocumento28 páginasDGS 700 Manualcarla monic dialinoAún no hay calificaciones

- Equivalentes SMD X ConvencionalDocumento126 páginasEquivalentes SMD X Convencionaledaoeletronica100% (1)

- Edt Deterministic Test GuideDocumento264 páginasEdt Deterministic Test GuideN Nanda Ganesh100% (4)

- Mali 2019Documento7 páginasMali 2019aymenAún no hay calificaciones

- MW Scas 2008Documento4 páginasMW Scas 2008pk27575Aún no hay calificaciones

- A Is (Facts) (SVG) ,: AbstractDocumento9 páginasA Is (Facts) (SVG) ,: AbstractSherif M. DabourAún no hay calificaciones

- Single-Phase Seven-Level Grid-Connected Inverter For Photovoltaic SystemDocumento9 páginasSingle-Phase Seven-Level Grid-Connected Inverter For Photovoltaic SystemDeepak Kumar NayakAún no hay calificaciones

- New Multilevel Inverter Topology With Reduced Number of SwitchesDocumento6 páginasNew Multilevel Inverter Topology With Reduced Number of SwitchesVikram PrasadAún no hay calificaciones

- Multi-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LDocumento6 páginasMulti-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LveguruprasadAún no hay calificaciones

- Comparative study of MLI and dual inverter using SVM techniquesDocumento8 páginasComparative study of MLI and dual inverter using SVM techniquesshiva256Aún no hay calificaciones

- Iceict2015i020315001 PDFDocumento6 páginasIceict2015i020315001 PDFmadihaAún no hay calificaciones

- Comparison of Multicarrier PWM Strategies For Five-Level Z-Source Diode-Clamped Inverter For On-Grid Renewable Energies ApplicationsDocumento5 páginasComparison of Multicarrier PWM Strategies For Five-Level Z-Source Diode-Clamped Inverter For On-Grid Renewable Energies ApplicationsJeya RamAún no hay calificaciones

- Iiii JJJJ S S S S A A A A A A A A: Simulation of Cascaded Multilevel Inverter Using Hybrid PWM TechniqueDocumento4 páginasIiii JJJJ S S S S A A A A A A A A: Simulation of Cascaded Multilevel Inverter Using Hybrid PWM TechniqueKanaga VaratharajanAún no hay calificaciones

- 04285962, DJSDocumento9 páginas04285962, DJSDeepu ChinnaAún no hay calificaciones

- 5 Level InverterDocumento6 páginas5 Level InverterRameshRtsAún no hay calificaciones

- 11 Level Diode Clamped Inverter-Ijcis-2011Documento5 páginas11 Level Diode Clamped Inverter-Ijcis-2011gjk1236596Aún no hay calificaciones

- Term PaperDocumento14 páginasTerm PaperakhilAún no hay calificaciones

- 11-Level cascaded H-bridge grid-tied inverter interfaceDocumento19 páginas11-Level cascaded H-bridge grid-tied inverter interfacesantu212Aún no hay calificaciones

- ANN Switched Z-Source Inverter Based PV Generation System: AbstractDocumento9 páginasANN Switched Z-Source Inverter Based PV Generation System: AbstractsathishAún no hay calificaciones

- 0912 F 50 DC 9 e 96 Ad 0 BD 000000Documento4 páginas0912 F 50 DC 9 e 96 Ad 0 BD 000000Pradyumna Kumar Behera100% (1)

- Optimal SVPWM for MLI Fed Induction MotorDocumento6 páginasOptimal SVPWM for MLI Fed Induction MotorManu ThomasAún no hay calificaciones

- Zero-Steady-State-Error Input-Current Controller For Regenerative Multilevel Converters Based On Single-Phase CellsDocumento8 páginasZero-Steady-State-Error Input-Current Controller For Regenerative Multilevel Converters Based On Single-Phase CellssghfqweAún no hay calificaciones

- Ridley 1991Documento10 páginasRidley 1991mounicapaluru_351524Aún no hay calificaciones

- A Comparative Study of Various Multi-Level Inverter Based On Multi-CellDocumento4 páginasA Comparative Study of Various Multi-Level Inverter Based On Multi-CellTarak BenslimaneAún no hay calificaciones

- A New Method For DC-AC Conversion Using Simplified Multilevel Inverter - Design and Analysis Using PSIM 1. V.Gowri Shankar, 2.C.UdhayashankarDocumento7 páginasA New Method For DC-AC Conversion Using Simplified Multilevel Inverter - Design and Analysis Using PSIM 1. V.Gowri Shankar, 2.C.UdhayashankarraghuevmAún no hay calificaciones

- 13 Level Nagar2017Documento5 páginas13 Level Nagar2017Siva ForeviewAún no hay calificaciones

- A New Hybrid Cascaded H-Bridge Multilevel Inverter - Performance AnalysisDocumento5 páginasA New Hybrid Cascaded H-Bridge Multilevel Inverter - Performance AnalysisGaurav BhandariAún no hay calificaciones

- Qwe Erer-135Documento9 páginasQwe Erer-135vinai2086Aún no hay calificaciones

- Simulation and Experimental Results of 7-Level Inverter SystemDocumento8 páginasSimulation and Experimental Results of 7-Level Inverter Systembacuoc.nguyen356Aún no hay calificaciones

- SRCEM Three level H-bridge inverter reportDocumento7 páginasSRCEM Three level H-bridge inverter reportAnil ShahAún no hay calificaciones

- Simulation of A Novel Multi Level Inverter Topology For Induction Motor Drive ApplicationsDocumento7 páginasSimulation of A Novel Multi Level Inverter Topology For Induction Motor Drive ApplicationsAnney RevathiAún no hay calificaciones

- Survey of CascadeDocumento10 páginasSurvey of Cascadesumiths32Aún no hay calificaciones

- Voltage-Source Active Power Filter Based On Multilevel Converter and Ultracapacitor DC LinkDocumento9 páginasVoltage-Source Active Power Filter Based On Multilevel Converter and Ultracapacitor DC LinkhdinhhienAún no hay calificaciones

- Single Phase Asymmetrical Cascaded Multilevel Inverter Design For Induction MotorDocumento6 páginasSingle Phase Asymmetrical Cascaded Multilevel Inverter Design For Induction Motorfarid kerroucheAún no hay calificaciones

- Photovoltaic Applications A Comparative Study of Cascaded Z-Source and Quasi Z-Source Multilevel Inverter ForDocumento5 páginasPhotovoltaic Applications A Comparative Study of Cascaded Z-Source and Quasi Z-Source Multilevel Inverter ForArun KumarAún no hay calificaciones

- MultilevelDocumento15 páginasMultilevelsyfullahnelAún no hay calificaciones

- Wide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial ApplicationsDocumento14 páginasWide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial Applicationsstrngr06Aún no hay calificaciones

- International Journal of Engineering Research and DevelopmentDocumento7 páginasInternational Journal of Engineering Research and DevelopmentIJERDAún no hay calificaciones

- Control H BridgeDocumento5 páginasControl H BridgeFahad Al-shammeriAún no hay calificaciones

- 9-Level Trinary DC Source Inverter Using Embedded ControllerDocumento6 páginas9-Level Trinary DC Source Inverter Using Embedded ControllerIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalAún no hay calificaciones

- Comparative Analysis of Cascade H-Bridge Multilevel InvertersDocumento6 páginasComparative Analysis of Cascade H-Bridge Multilevel Invertersnadeemq_0786Aún no hay calificaciones

- Simulation of Single Phase Multilevel Inverters With Simple Control Strategy Using MATLABDocumento9 páginasSimulation of Single Phase Multilevel Inverters With Simple Control Strategy Using MATLABFarman UllahAún no hay calificaciones

- Total Harmonics Distortion Investigation in Multilevel InvertersDocumento8 páginasTotal Harmonics Distortion Investigation in Multilevel InvertersAJER JOURNALAún no hay calificaciones

- IET-PEL - Comprehensive Analysis of A Novel Three-Phase Multilevel Inverter With Minimum Number of SwitchesDocumento8 páginasIET-PEL - Comprehensive Analysis of A Novel Three-Phase Multilevel Inverter With Minimum Number of SwitchesKartick JanaAún no hay calificaciones

- Paper 14Documento7 páginasPaper 14Suresh KotaAún no hay calificaciones

- Term Project Power D&TDocumento6 páginasTerm Project Power D&TThamer SE AlkhamiisAún no hay calificaciones

- Seven Level Inverter With Nearest Level ControlDocumento7 páginasSeven Level Inverter With Nearest Level Controlsanjay sAún no hay calificaciones

- An Effective Control Technique For Medium-Voltage High-Power Induction Motor Fed by Cascaded Neutral-Point-Clamped InverterDocumento10 páginasAn Effective Control Technique For Medium-Voltage High-Power Induction Motor Fed by Cascaded Neutral-Point-Clamped InverterRaviraj VishvakarmaAún no hay calificaciones

- High-speed voltage follower designDocumento2 páginasHigh-speed voltage follower designfatyfroisAún no hay calificaciones

- Multistring Five-Level Inverter With Novel PWMDocumento13 páginasMultistring Five-Level Inverter With Novel PWMsandeepbabu28Aún no hay calificaciones

- IET-PEL - Modulation and Control of Multilevel Inverter For An Open-End Winding Induction Motor With Constant Voltage Levels and HarmonicsDocumento9 páginasIET-PEL - Modulation and Control of Multilevel Inverter For An Open-End Winding Induction Motor With Constant Voltage Levels and HarmonicsKartick JanaAún no hay calificaciones

- Term Project PowerDocumento5 páginasTerm Project PowerThamer SE AlkhamiisAún no hay calificaciones

- Statespace Model FWD ConverterDocumento4 páginasStatespace Model FWD ConverterrogerozAún no hay calificaciones

- Improving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshDocumento5 páginasImproving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshsarathAún no hay calificaciones

- International Journal of Computational Engineering Research (IJCER)Documento7 páginasInternational Journal of Computational Engineering Research (IJCER)International Journal of computational Engineering research (IJCER)Aún no hay calificaciones

- Bbifbi Standalone Iet PeDocumento10 páginasBbifbi Standalone Iet PeJeremy MeyerAún no hay calificaciones

- Implementation and Control of A Hybrid Multilevel ConverterDocumento24 páginasImplementation and Control of A Hybrid Multilevel ConverterAnang SunnyAún no hay calificaciones

- 46 Multileveltopology PDFDocumento5 páginas46 Multileveltopology PDFDeepu ChinnaAún no hay calificaciones

- A New Single Switch Buck-Boost Type DC-DC ConverterDocumento4 páginasA New Single Switch Buck-Boost Type DC-DC ConverterRaveendhra IitrAún no hay calificaciones

- Paper 12Documento9 páginasPaper 12Hari ShankarAún no hay calificaciones

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1De EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Calificación: 2.5 de 5 estrellas2.5/5 (3)

- Simulation of Some Power System, Control System and Power Electronics Case Studies Using Matlab and PowerWorld SimulatorDe EverandSimulation of Some Power System, Control System and Power Electronics Case Studies Using Matlab and PowerWorld SimulatorAún no hay calificaciones

- TCSC and SSRDocumento6 páginasTCSC and SSRTiger FlyAún no hay calificaciones

- 91Documento7 páginas91vinay kumarAún no hay calificaciones

- Uu (Oi (PioDocumento1 páginaUu (Oi (Piovinay kumarAún no hay calificaciones

- 88Documento15 páginas88vinay kumarAún no hay calificaciones

- 96Documento6 páginas96vinay kumarAún no hay calificaciones

- 103Documento10 páginas103vinay kumarAún no hay calificaciones

- Shunt Connected STATCOM Control Grid of Wind Turbine System For Balanced Unbalanced Non Linear LoadsDocumento6 páginasShunt Connected STATCOM Control Grid of Wind Turbine System For Balanced Unbalanced Non Linear Loadsvinay kumarAún no hay calificaciones

- 106Documento6 páginas106vinay kumarAún no hay calificaciones

- 95Documento12 páginas95vinay kumarAún no hay calificaciones

- 100Documento4 páginas100vinay kumarAún no hay calificaciones

- 87Documento5 páginas87vinay kumarAún no hay calificaciones

- 101Documento6 páginas101vinay kumarAún no hay calificaciones

- 99Documento12 páginas99vinay kumarAún no hay calificaciones

- 94Documento4 páginas94vinay kumarAún no hay calificaciones

- 06080730Documento9 páginas06080730dabalejoAún no hay calificaciones

- 82Documento8 páginas82vinay kumarAún no hay calificaciones

- A Power Quality Compensator With DG Interface Capability Using Repetitive ControlDocumento7 páginasA Power Quality Compensator With DG Interface Capability Using Repetitive Controlvinay kumarAún no hay calificaciones

- 83Documento6 páginas83vinay kumarAún no hay calificaciones

- 81Documento10 páginas81vinay kumarAún no hay calificaciones

- 90Documento6 páginas90vinay kumarAún no hay calificaciones

- 84Documento5 páginas84vinay kumarAún no hay calificaciones

- Grid Interactive PV System With Harmonic and Reactive Power Compensation Features Using A Novel Fuzzy Logic Based MPPTDocumento6 páginasGrid Interactive PV System With Harmonic and Reactive Power Compensation Features Using A Novel Fuzzy Logic Based MPPTvinay kumarAún no hay calificaciones

- Grid Interactive PV System With Harmonic and Reactive Power Compensation Features Using A Novel Fuzzy Logic Based MPPTDocumento6 páginasGrid Interactive PV System With Harmonic and Reactive Power Compensation Features Using A Novel Fuzzy Logic Based MPPTvinay kumarAún no hay calificaciones

- Design and Simulation of Single Phase Z-Source Buck Boost Matrix ConverterDocumento7 páginasDesign and Simulation of Single Phase Z-Source Buck Boost Matrix Convertervinay kumarAún no hay calificaciones

- 78Documento6 páginas78vinay kumarAún no hay calificaciones

- 77Documento4 páginas77vinay kumarAún no hay calificaciones

- 75Documento4 páginas75vinay kumarAún no hay calificaciones

- 76Documento6 páginas76vinay kumarAún no hay calificaciones

- 2020 Undergraduate BrochureDocumento17 páginas2020 Undergraduate BrochureAndrew navioAún no hay calificaciones

- IRS4427Documento19 páginasIRS4427ali ülküAún no hay calificaciones

- Electronics Engineering - ECT001 Potential Electronics Technician Board Exam QuestionsDocumento3 páginasElectronics Engineering - ECT001 Potential Electronics Technician Board Exam QuestionsApril Joy Gelilang PulgaAún no hay calificaciones

- InoTouch Series HMI User Manual PDFDocumento2 páginasInoTouch Series HMI User Manual PDFjaimeasisa100% (1)

- Tracker TeamDocumento1707 páginasTracker TeamAbu Abdullah YaserAún no hay calificaciones

- 109 ManualDocumento2 páginas109 ManualJorge Eduardo CardoneAún no hay calificaciones

- Fas - Ul.p.3.013 HCP PDFDocumento2 páginasFas - Ul.p.3.013 HCP PDFShashish AshuAún no hay calificaciones

- EasyRET 18-port 1L4H FDD/3.3-3.8GHz 8T8R TDD Antenna SpecificationsDocumento5 páginasEasyRET 18-port 1L4H FDD/3.3-3.8GHz 8T8R TDD Antenna SpecificationsRobert100% (1)

- AAMCS S-Band AmplifierDocumento14 páginasAAMCS S-Band AmplifierMazlum ÜnalAún no hay calificaciones

- OscilloscopeDocumento7 páginasOscilloscopewaar lockAún no hay calificaciones

- Can Communication PDFDocumento35 páginasCan Communication PDFUmesh SanadiAún no hay calificaciones

- Control de Nivel Frio ALKAR 2 Matrix+LLC+Bulletin+515Documento4 páginasControl de Nivel Frio ALKAR 2 Matrix+LLC+Bulletin+515Lucas Sebastian PusichAún no hay calificaciones

- A Digital-To-Analog Converter (DAC) Block Diagram.: Introduction To Microprocessor-Based ControlDocumento3 páginasA Digital-To-Analog Converter (DAC) Block Diagram.: Introduction To Microprocessor-Based Controlnovo orderAún no hay calificaciones

- HoverboardDocumento31 páginasHoverboardPravat SatpathyAún no hay calificaciones

- VLSI Testing & TestabilityDocumento1 páginaVLSI Testing & TestabilityDr. Lokesh Kumar BramhaneAún no hay calificaciones

- Week 8:: ObjectivesDocumento12 páginasWeek 8:: ObjectivesJohn Kenneth MantesAún no hay calificaciones

- Lca Lab Report 9Documento7 páginasLca Lab Report 9Shahzeb BukhariAún no hay calificaciones

- Manual HC-350Documento25 páginasManual HC-350Pop100% (1)

- BGY888 Philips PDFDocumento12 páginasBGY888 Philips PDFPoso TvAún no hay calificaciones

- Ezform Cables CatalogDocumento19 páginasEzform Cables CatalogradianfmAún no hay calificaciones

- Price List MSRP For WEB PDFDocumento3 páginasPrice List MSRP For WEB PDFnavneetAún no hay calificaciones

- Simulation and Design of Dual-Gate FinFET and Tri-Gate MOSFETsDocumento2 páginasSimulation and Design of Dual-Gate FinFET and Tri-Gate MOSFETskumarguptavAún no hay calificaciones

- Update cv2020Documento2 páginasUpdate cv2020Ashish rawatAún no hay calificaciones

- CH 09Documento53 páginasCH 09Pranusha AdiviAún no hay calificaciones

- NCP1203 PWM Current-Mode Controller For Universal Off-Line Supplies Featuring Standby and Short Circuit ProtectionDocumento15 páginasNCP1203 PWM Current-Mode Controller For Universal Off-Line Supplies Featuring Standby and Short Circuit ProtectionNam NhiAún no hay calificaciones

- DTMF Based Door Opening System REPORTDocumento20 páginasDTMF Based Door Opening System REPORTprashant0% (1)