Documentos de Académico

Documentos de Profesional

Documentos de Cultura

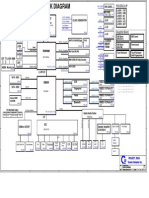

SBC Shematics

Cargado por

Tom TommyTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

SBC Shematics

Cargado por

Tom TommyCopyright:

Formatos disponibles

1

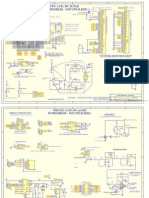

BASE.0010 - PROTO B2 rev 15/12/2010

A

REV

B1 Project start

Description

DATE BY

19/09/2010 JAP

CONTENTS PAGE NO.

1 2 3 4 5 6 7

SCHEMATIC PAGE

COVER PAGE MAIN POWER TFT + TOUCH + BACKLIGHT MODEM GSM/GPRS (UART) VIDEO DECODER RS232 USBOTG & AUDIO DVI-D USB HUB 4 ports CAN BUS (SPI) & RS485 & EEPROM ETHERNET0 ETHERNET1 INPUT_OUTPUT VGA CONNECTOR IGEP0030 CONNECTOR IGEP0032

B

B2

First public version

13/12/2010

JAP

8 9 10 11 12 13 14 15 16

W ednesday, December 15, 2010

REV

DATE

DESCRIPTION

AUTHOR

XX/XX/XX

BASE.0010 This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

1 2 3 4 5 6

SCALE

1/1

8

REV.

SHEET

COVER

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

B2

1 16

2A, 7V-28V INPUT, STEP DOWN SWIFT DC/DC CONVERTER

R100 R102 Capacitor as close as posible to Input

(5VDC/4V2)

R101 DNI 0R C100 C101 C102 DNI 1nF 50V R103

MAIN POWER SUPPLY (5V or 7V-24V)

POWER_IN

A

DNI 0R 120R@100MHz 3A 0603 FB101 DNI BLM18SG121TN1 L102 CHOKE COMMON MODE 1 2 PS+ C+ 3 100nF 50V PSC4 C118 15pF 50V

DNI 0R

The bootstrap capacitor must be 0.1uF. High-quality ceramic type with X7R or X5R. C103

STPS340U-SMB VR=40V IF=3A VF=0.57V

L101

L=15uH Isat=2.84A IRMS=2.70A

GND DNI 100nF DNI 100pF 50V 50V (*) 2A

4V2 (VBAT)

(*) 2A

4V2 (VBAT)

(*) 2A VBAT

IRLML6402 S D Q101 G

(*) 2A GND C109 120R@100MHz 3A 0603 FB102 BLM18SG121TN1 C119 470pF 50V C120 15pF 50V 120R@100MHz 3A 0603 FB103 BLM18SG121TN1 C121 470pF 50V C122 100pF 50V C123 100nF 50V R106 DNI 330K Enable and adjust under voltage lockout circuit R111 0R POWER_RAW (*) 2A C110 C111 (*) 2A DNI 10uF DNI 10uF DNI 10uF 35V 35V 35V U101 1 2 3 4 BOOT PH VIN GND EN COMP SS VSNS 8 7 6 5 DNI 100nF

C104 GND_PWR STPS340U-SMB D102 10uF 35V

C105 10uF 35V

C106

C107

C108

DNI 15uH R104 DNI 10K

C112 DNI 47uF 6V3

C113 DNI 47uF 6V3

J101 1 3 2 1 3 2

DNI 10uF DNI 10uF DNI 10uF 35V 35V 35V

D101 DNI STPS340U-SMB

DNI 0R

4V2 Push Button On/Off Controller with P Interrupt

R108 U102 100K

TP101

A

DC_PWR_EN V101 Varistor

C114

C115

C116

C117

GND C124 DNI 1800pF 50V C125 GND DNI 47pF 50V R107 DNI 2.5K

V102 DNI Varistor 100pF 100pF 1nF 50V 50V 50V

R105 100K

DNI TPS54231 C126 DNI 22nF 50V A capacitor (Css) on the SS pin to ground implements a slow start time. GND

POWER JACK FB104 DNI BLM18SG121TN1 120R@100MHz 3A 0603 GND GND GND GND

GND_PWR

GND_PWR

GND_PWR

GND_PWR

R110 DNI 150K

R109 DNI 21K

GND SW101

1 2

VIN PB GND

EN INT KILL ONT PDT

6 (open drain) 5 8 PWR_SHDN_INT PWR_KILL 15 15

GND GND PCB layout considerations. TPS54231 datasheet pag.18 R112

GND

SW_PB_SPST GND

5VDC

C127 C128 820nF 10V 820nF generate forced power-off of 5 seconds GPIO_SW_PB 15 100nF

DNI 0R

2A, 4,35V-16V INPUT, BATTERY CHARGER, 4V2 OUPUT

C116, C131 as close as posible to Output R113 DC_5V 5V (DVI and USB Host)

B

(*) 2A C129 100nF GND (*) 2A GND C130 1nF GND

VBAT from 4V4 to BAT C131 100pF 6V3 BAT+ GND C132

(*) 2A

DNI 0R

Capacitors as close as posible to Input U103 (*) 2A 4 20 100K 100K 1K 36K 30K 100K 9 8 10 13 14 7 1 AC USB CE PSEL ISET1 DPPM TMR VSS ISET2 LDO OUT OUT OUT BAT BAT TS USBPG* ACPG* STAT1 STAT2

4V2 (VBAT)

GNDGND

LTC2954ITS8-1

GND

(*) 2A 15 16 17 6 5 12 19 18 2 3

R114

DNI 0R C133 0R 10uF 35V C134 10uF 35V C135 DNI 10uF 35V

TP102 R115 R116 R117 R119 R120 R121 GND GND All low-current VSS connections should be kept separate from the high-current charge or discharge paths from the battery. Use a single-point ground technique incorporating both the small signal ground path and the power ground path.

J102 1 2

BATTERY CONNECTOR

CON2

R118 J103 J104 1 2 3 4 FCI 20020004-C04 FCI 20020110-C04 GND POWER_IN

TP103 TP104 TP105 TP106 GND

R122 22K GND

C136 47uF 6V3

GND

11

BAT+ GND_PWR

Fast Charge Current: 800 mA Temperature: 0 to 45C Fast Charge Time Limit: 5 hours VDPPM = 4.0 V

BQ24032ARHLR

GND

PWR_ACPG 16 PWR_STAT1 16 PWR_STAT2 16

PW_STAT1-2 0-0 Precharge 0-1 Charge done 1-0 Fast charge 1-1 Charge suspend

Close to power jack

STEP UP / BOOST (5v <- 4v2) / 1.8A

GND FB105 BLM18SG121TN1 120R@100MHz 3A 0603 L103 2,2uH AGND DC_5V_UP 4 2 U104 VIN VINA EN PS_SYNC 5 8 6 7

VOUT FB

PGND L1 POWERPAD GND L2

1 10 C137 FB106 BLM18SG121TN1 120R@100MHz 3A 0603 10uF 10V GND_EARTH

C138 R123 10K R124 DNI 10K 10uF 10V

3 11 9

GND

TPS63002 R125 VBAT DC_PWR_EN R127 VBAT R128 R129 R130

C

TAL1 1 DNI TAL TAL2

Q102 MMUN2233

DNI 0R R126 DNI 0R EN_5V 16

DNI 120R

DNI 120R

120R D103

1 DNI TAL TAL3 1 DNI TAL TAL4 1 DNI TAL Default power configuration GND_EARTH POWER_IN = 5VDC POWER RAW = 5VDC - Vf diode STPS340U DC_5V = 5VDC from Step up VBAT = 4V2 from BQ24032A VBAT R134 1V8 0R 10K R142 DNI 10K 16 EN_3V3 R141 10K Q105 MMUN2233 GND GND 1uF C143 10V GND GND R132 5 2 4 DNI 0R (*) 2A 8 POWER_RAW R131 GND 1uF C139 10V

Anode

120R D104

LINEAR REGULATOR (VBAT / 5v -> 3v3) / 1A

U105 IN EN NC1 GND OUT NC2 NC3 FB 1 6 7 3 3V3_ADJ R136 30.1K 1% R133 C140 100nF TP107 R135 52.3K 1% 0R 15 LED_USER1 Q103 DNI MMUN2233 GNDGND LED_USER2 Q104 DNI MMUN2233 4 LED_MODEM 15 GND 3V3 DNI LED Cathode LED

C141 10uF 10V

C142 100nF

3V3 (DVI and RS232)

S1 S2 9 S3 S4

S1 S2 PAD S3 S4 TPS73701 GND

GND

GND

LINEAR REGULATOR (VBAT / 5v -> 1v8) / 1A

1V8 U106 R138 C144 1V8_ADJ R140 56.2K 1% 100nF TP108 R139 28K 1% 0R 8 5 2 4 GND IN EN NC1 GND OUT NC2 NC3 FB 1 6 7 3

GND

D

(*) 2A R137 10K

This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU.

1V8

C145 10uF 10V C146 100nF Friday, December 17, 2010

REV

S1 S2 PAD S3 S4

DATE

DESCRIPTION

AUTHOR

S1 S2 9 S3 S4

TPS73701 GND GND GND BASE.0010 MAIN POWER

XX/XX/XX

This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

GND

SCALE

1/1

8

REV.

SHEET

B2

2 16

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

LCD POWER (3.3V)

3V3 U200 VBAT 250mA R202 C201

A

R200

DNI 0R

8 5 2 4

GND

IN EN NC1 GND

OUT NC2 NC3 FB

1 6 7 3

R201 C200 100nF R203 52.3K 1%

0R

LCD_3V3 LCD_3V3 Place near C202 connector. Near LCD_3V3 100nF GND LCD_3V3 Place near C203 connector. Near LCD_3V3 100nF GND LCD_D[0..23]

10K 1uF 10V LCD_3V_EN

S1 S2 PAD S3 S4

GND

S1 S2 9 S3 S4

R204 30.1K 1%

C204 10uF 10V

C205 100nF LCD_D[0..23] LCD_D[0..23]

TPS73701 GND

SHARP 7"

1 2 3 LCD_3V3 4 LCD_D16 5 LCD_D17 6 LCD_D18 7 LCD_D19 8 LCD_D20 9 LCD_D21 10 LCD_D22 11 LCD_D23 12 LCD_D8 13 LCD_D9 14 LCD_D10 15 LCD_D11 16 LCD_D12 17 LCD_D13 18 LCD_D14 19 LCD_D15 20 LCD_D0 21 LCD_D1 22 LCD_D2 23 LCD_D3 24 LCD_D4 25 LCD_D5 26 LCD_D6 27 LCD_D7 28 GND 29 LCD_CLK 30 31 LCD_HSYNC 32 LCD_VSYNC 33 LCD_DEN 34 35 36 GND 37 38 39 40

GND

J201 GND

SEIKO 7"

1 2 3 4 LCD_3V3 5 6 7 8 LCD_DEN 9 LCD_HSYNC 10 LCD_VSYNC 11 LCD_CLK 12 13 GND LCD_D7 14 LCD_D6 15 LCD_D5 16 LCD_D4 17 LCD_D3 18 LCD_D2 19 LCD_D1 20 LCD_D0 21 LCD_D15 22 LCD_D14 23 LCD_D13 24 LCD_D12 25 LCD_D11 26 LCD_D10 27 LCD_D9 28 LCD_D8 29 LCD_D23 30 LCD_D22 31 LCD_D21 32 LCD_D20 33 LCD_D19 34 LCD_D18 35 LCD_D17 36 LCD_D16 37 R209 10K 38 GND 10K 39 LCD_3V3 R210 40 GND

LCD_D[0..23]

J200

GND

GND

14,15 B_DSS_D[0..23]

B_DSS_D[0..23]

Place Close to the Buffer B_DSS_D0 B_DSS_D1 B_DSS_D2 B_DSS_D3 B_DSS_D4 B_DSS_D5 B_DSS_D6 B_DSS_D7 B_DSS_D8 B_DSS_D9 B_DSS_D10 B_DSS_D11 B_DSS_D12 B_DSS_D13 B_DSS_D14 B_DSS_D15 B_DSS_D16 B_DSS_D17 B_DSS_D18 B_DSS_D19 B_DSS_D20 B_DSS_D21 B_DSS_D22 B_DSS_D23 B_DSS_PCLK B_DSS_ACBIAS B_DSS_VSYNC B_DSS_HSYNC RP200A RP200B RP200C RP200D RP200E RP200F RP201B RP200G RP200H RP201A RP201C RP201D RP201E RP201F RP201G RP201H RP202A RP202B RP202C RP202D RP202E RP202F RP202G RP202H RP203A RP203B RP203C RP203D RP203E RP203F RP203G RP203H

GND

LCD_3V_EN

15

LCD_EN Q200 R214 10K GND MMUN2233

LCD BACKLIGHT DRIVER

C206 GND 10uF 10V

L200

4.7uH C207

U201A

GND

B

LCD_3V_EN 1V8

VBAT VBAT

2 6 7 3

VIN EN FSW SS

SW OUT FB

10 9 5

10uF 35V

GND

LCD_LED+ LCD_LEDR208 1R 1% Rset

8 4

R205 10K

R206 10K

R207 10K

TPS61081DRCR

(Upper contact type)

15 LCD_PW MBKL Q201 GND MMUN2233 GND

GND GND GND

5 6 7 8

12 11 10 9

10 10 10 10

CONN FFC/FPC 40POS

CONN FFC/FPC 40POS

J202

J203

TOUCHSCREEN

C

LCD_3V3

VBAT

1V8

C208 100nF C210 10uF 10V C211 100nF GND GND 100nF U202 TSC2046PW R GND

SHARP 7''

C209

CONN FPC/FFC 6POS 0.5MM SMD KYOCERA ELCO 04 6277 006 001 883+ FCI 59453_062110EDLF 0.5mm pitch dual sided or top contact

SEIKO 7"

1 2 3 4 5 6

(anode) (catode) (anode) (catode) (anode) (catode)

LCD_LED+ LCD_LEDLCD_LED+ LCD_LEDLCD_LED+ LCD_LED-

1 2 3 4 5 6

(catode) (anode) (catode) (anode) (catode) (anode)

LCD_LEDLCD_LED+ LCD_LEDLCD_LED+ LCD_LEDLCD_LED+

(Upper contact type)

14,15 14,15 14,15 14,15

B_DSS_PCLK B_DSS_ACBIAS B_DSS_VSYNC B_DSS_HSYNC

1 2 3 4 5 6 2 7 8 1 3 4 5 6 7 8 1 2 3 4 5 6 7 8 1 2 3 4

16 15 14 13 12 11 15 10 9 16 14 13 12 11 10 9 16 15 14 13 12 11 10 9 16 15 14 13

10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10

LCD_D0 LCD_D1 LCD_D2 LCD_D3 LCD_D4 LCD_D5 LCD_D6 LCD_D7 LCD_D8 LCD_D9 LCD_D10 LCD_D11 LCD_D12 LCD_D13 LCD_D14 LCD_D15 LCD_D16 LCD_D17 LCD_D18 LCD_D19 LCD_D20 LCD_D21 LCD_D22 LCD_D23 LCD_CLK LCD_DEN LCD_VSYNC LCD_HSYNC

R0 R1 R2 R3 R4 R5 R6 R7 G0 G1 G2 G3 G4 G5 G6 G7 B0 B1 B2 B3 B4 B5 B6 B7

B7 B6 B5 B4 B3 B2 B1 B0 G7 G6 G5 G4 G3 G2 G1 G0 R7 R6 R5 R4 R3 R2 R1 R0

PGND GND

CONN FPC/FFC 6POS 0.5MM SMD KYOCERA ELCO 04 6277 006 001 883+ FCI 59453_062110EDLF 0.5mm pitch dual sided or top contact

7 1 2 4 3 5

VBAT +VCC X+ XY+ Y-

IOVDD AUX VREF DCLK CS DIN DOUT

10 8 9 16 15 14 12

TP200 TP201

R211 10K GND MCSPI1_CLK MCSPI1_CS1 MCSPI1_SIMO MCSPI1_SOMI 10,15 15 10,15 10,15

J205

GND X+ XY+ Y-

1 2 3 4

(top) (left) (bottom) (right)

TouchScreen Y+ XYX+

J204

1 2 3 4

(left) (bottom) (right) (top)

TouchScreen XYX+ Y+

1V8 15 TS_nPEN_IRQ 15 TS_BUSY R213

R212 10K 0R

CONN FPC/FFC 4POS 0.5MM SMD FCI SFV4R-2STE1LF FCI 59453-042110EALF 0.5mm pitch dual sided or top contact

CONN FPC/FFC 4POS 1MM SMD KYOCERA ELCO 04 6227 004 100 829+ FCI SFW4R-1STAE1LF 1mm pitch dual sided or top contact

11 13

C212

PENIRQ BUSY

GND

TP202

D

100nF GND

GND

This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU.

Friday, December 17, 2010

REV

DATE

DESCRIPTION

AUTHOR

XX/XX/XX

BASE.0010 This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

1 2 3 4 5 6

SCALE

1/1

8

REV.

SHEET

TFT

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

B2

7

3 16

(*2A peak current, 500mA normal current) (*) 2A

VBAT

C300 10nF

C303 100nF

C304 100uF

F1 F2 F3

U301

F8 F7 E6 D7 D6 D5 C6 C5 C4 C3 B6

RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED

C301 GND Place together 6 UART3_TXD_3V3 6 UART3_RXD_3V3 6,10 UART1_TXD_3V3 6,10 UART1_RXD_3V3 6 UART2_TXD_3V3 6 UART2_RXD_3V3 R300 R301 R302 R303 R305 R306 DNI 0R DNI 0R DNI 0R DNI 0R 0R 0R TP306 TP300

C302 GND

VBATT VBATT_PA VBATT_PA

3V3

GND The Bypass low ESR capacitor must be placed close to the Telit GE864-QUAD / PY power input pads

2V8

100nF U300

100nF

TP301 SIMCLK SIMRST SIMIO SIMIN SIMVCC Note: GE-865 TXD is Serial data input Note: GE-865 RXD is Serial data output MODEM_TXD MODEM_RXD

MODEM_TXD_3V3 MODEM_RXD_3V3

7 8 1 2

VCCB B1 B2 GND

VCCA A1 A2 OE

3 5 4 6

MODEM_TXD MODEM_RXD R304 10K 2V8 TP307

A5 A8 A6 B7 A7 D1 E1 A3 A4 B3 A1 A2 B5 B2 B4 C1 H2 G8 B1 E2

SIMCLK SIMRST SIMIO SIMIN SIMVCC TXD_AUX RXD_AUX TXD RXD DTR RTS CTS DCD DSR RING RESET VRTC STAT_LED ON_OFF PWRMON GND GND GND GND GND GND GND GND GND GND

MICMIC+ EAR+ EARADC_IN2 ADC_IN1 DAC_OUT

C8 B8 D8 E8 F6 F5 G7 E3 F4 D4 G6 H8 G2 H7 E4 D2 D3 H1 H5

MODEM_MICMODEM_MIC+ MODEM_EAR+ MODEM_EAR-

TP302 TP303 TP304 TP305

GND

TXS0102DCUR VCCA <= VCCB

GE865

(DVI2_CLK: Internal pull-up 4.7K to 2.72V) SSC_TK TK0: SSC Transmitter clock MODEM_BUZZER R307 MODEM_ALARM R308 MODEM_RFTXMON R309 MODEM_TX_DISAB R310 SSC_RD RD0: SSC Receiver Data SSC_TD TD0: SSC Transmitter Data SSC_TF TF0: SSC TX frame synchro MODEM_SERVICE MODEM_ANTENNA TP312

J300

1

JUMPER GND

B

MODEM_ON_NOFF

TP311 Q300 MMUN2233 GND GND J301 2V8 R312 0R

15 GPIO_MODEM_ON_OFF R311 10K

MODEM_NRST MODEM_VRTC MODEM_STAT_LED MODEM_ON_NOFF MODEM_PW RMON

GPIO_10 GPIO_09 GPIO_08/DVI_CLK GPIO_07/BUZZER GPIO_06/ALARM GPIO_05/RFTXMON GPIO_04/TX_DISAB GPIO_03/DVI_TX GPIO_02/DVI_RX GPIO_01/DVI_WA0 SERVICE ANTENNA

47K 47K 47K 47K

TP308 TP309 TP310 2V8

GE865 supplies power for level translator

H6 H3 G3 G4 G5 E7 E5 C7 C2 G1

GE865

1

JUMPER GND 15 GPIO_MODEM_NRST

MODEM_NRST LED_MODEM 2 (*) 2A GND MODEM_STAT_LED (1.8 CMOS)

R313 10K

Q301 MMUN2233 GND

Q302 MMUN2233 GND

GND RF Cable antenna. Very close to GE865

C C

R314 15 GPIO_MODEM_PW RMON 47K R315 68K MODEM_PW RMON CMOS 2V8

MODEM_ANTENNA 1

J302

GND SIMIN SIMIO SIMVCC SIMRST SIMCLK J303 MOLEX 0475530001

GND

2V8 C305 1V8 C306

3

DNI 100nF 16 16 16 16 McBSP1_DX McBSP1_DR McBSP1_CLKX McBSP1_FSX U302 DNI 100nF PGB0010603MR PGB0010603MR D300 D301 PGB0010603MR D302 C307 33pF C308 33pF

C3 C2 C1 T CD1 CD2

C7 C6 C5 H

7 6 5

D303 C310 33pF PGB0010603MR

REV

2 1

1 2 3 4 5 6 7

VCCA A1 A2 A3 A4 NC1 GND

VCCB B1 B2 B3 B4 NC2 OE

14 13 12 11 10 9 8

SSC_TD SSC_RD SSC_TK SSC_TF R316

TD0: Transmitter Data RD0: Receiver Data TK0: Transmitter clock TF0: Transmitter frame synchro 1V8 DNI 10K

PGB0010603MR D304

This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU.

C309 33pF

CONN_COAX_R

W ednesday, December 15, 2010

DATE

DESCRIPTION AUTHOR

DNI TXB0104PW R GND

XX/XX/XX

GND This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

1 2 3 4

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND BASE.0010 MODEM

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

SCALE

1/1

8

REV.

SHEET

B2

4 16

1V8D_DDEC

J402 R407 R418 0R R403 225R 56R 2.7uH 2.7uH C419 180pF C413 180pF R415 225R C405 180pF L401 L404 R401 0R

C420 1V8A_DDEC 100nF R414 75R 1% C404 100nF GND

C406 100nF

4 1

IO_DVDD

RCA JACK

1V8A_DDEC 1V8D_DDEC C424 IO_DVDD 100nF GND

C426 100nF

RP400A 1 RP400B 2 RP400C 3

16 10 15 10 14 10

GND

DDEC_GND J401

DDEC_GND R417

DDEC_GND R405

DDEC_GND L403

DDEC_GND L402

DDEC_GND R416

DDEC_GND

32

20

10

DDEC_GND C407 0R R412 225R 56R 2.7uH 2.7uH C423 180pF C416 180pF 100nF R408 75R 1% VIDE0_IN1 1 VIDE0_IN2 2 R410 225R C411 180pF 0R

U401A

DVDD

CH1_AVDD

PLL_AVDD

IO_DVDD

4 1

INTREQ/GPCL AVID FID/GLCO SCLK/PCLK VSYNC/PALI HSYNC YOUT0 YOUT1 YOUT2 YOUT3 YOUT4 YOUT5 YOUT6 YOUT7/I2CSEL

27 26 23 9 24 25 18 17 16 15 14 13 12 11

CAM_INTREQ TP401 CAM_FIELD CAM_PCLOCK CAM_VSYNC CAM_HSYNC CAM_DATA0 CAM_DATA1 CAM_DATA2 CAM_DATA3 CAM_DATA4 CAM_DATA5 CAM_DATA6 CAM_DATA7 R411

RP400D 4

13 10

CAM_IRQ

CAM_IRQ

16

RCA JACK

AIP1A AIP1B

RP400E RP400F RP400G RP400H RP401A RP401B RP401C RP401D RP401E RP401F RP401G RP401H

5 6 7 8 1 2 3 4 5 6 7 8

12 11 10 9 16 15 14 13 12 11 10 9

10 10 10 10 10 10 10 10 10 10 10 10

DDEC_GND

DDEC_GND

DDEC_GND

DDEC_GND

DDEC_GND

DDEC_GND

DDEC_GND CAM_XTAL1 CAM_XTAL2

R406 8,10,15 I2C3_SCL 8,10,15 I2C3_SDA GND 16 16 27 MHz

B

5 6 21 22

XTAL1/OSC XTAL2 SCL SDA PDN RESETB

TVP5150PBS

100K Y401

CAM_FLD CAM_PCLK CAM_VS CAM_HS R413 4.7K CAM_D0 CAM_D1 CAM_D2 CAM_D3 CAM_D4 CAM_D5 CAM_D6 CAM_D7

CAM_FLD CAM_PCLK CAM_VS CAM_HS

16 16 16 16 IO_DVDD

R419 CAM_PDN CAM_RESET

DNI 10K

28 8

CAM_D[0..7]

16

B

CH1_AGND

PLL_AGND

IO_DVDD

C412 18pF

C409 18pF

R402 10K

REFP

R409 10K

DGND

REFM

NSUB

DNI 10K R404 I2CSEL: Determines address for I2C 1K Logic 1: Address = 0xBA, Logic 0: Address = 0xB8 GND

29

30

31

GND

GND

IO_DVDD C410

1uF C414 1uF

DDEC_GND C418 1uF

GND

19

TVP5150PBS

IO_DVDD DDEC_GND DDEC_GND FB401 BLM18SG121TN1 120R@100MHz 3A 0603 C408 100nF

C

C421 10uF 6V3

C

GND 1V8

GND 1V8D_DDEC

C417 100nF

FB402 BLM18SG121TN1 120R@100MHz 3A 0603

C402 100nF

C425 10uF 6V3

GND GND GND 1V8A_DDEC

FB403 C403 BLM18SG121TN1 120R@100MHz 3A 0603 10uF 6V3

C422 100nF

C415 10uF 6V3

This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU.

GND

FB404 BLM18SG121TN1 120R@100MHz 3A 0603

W ednesday, December 15, 2010 DDEC_GND DDEC_GND

REV

DATE

DESCRIPTION

AUTHOR

XX/XX/XX

This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

BASE.0010 VIDEO DECODER

SCALE

1/1

8

REV.

SHEET

B2

5 16

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

C508 GND

1V8 GND

C507

3V3 U504 All resistors together UART1_RTS_3V3 10 UART1_CTS_3V3 10 RS232_RX1 RS232_RX2 TXD1_3V3 TXD2_3V3 UART1_TXD_3V3 UART1_RXD_3V3 UART3_TXD_3V3 UART3_RXD_3V3 UART1_TXD_3V3 UART1_RXD_3V3 UART2_TXD_3V3 UART2_RXD_3V3 UART1_RTS_3V3 UART1_CTS_3V3 UART1_TXD_3V3 4,10 UART1_RXD_3V3 4,10 GNDGND R508 R513 R521 R514 R503 R506 R510 R520 R516 R522 DNI 0R DNI 0R 0R 0R 0R 0R DNI 0R DNI 0R DNI 0R DNI 0R TXD1_3V3 RXD1_3V3 C502 100nF 13 8 11 10 1 3 4 5 C511 100nF 15 6 C512 100nF RIN1 RIN2 DIN1 DIN2 C1+ C1C2+ C2C506 GND V100nF SN65C3232 GND VCC V+ DOUT1 DOUT2 ROUT1 ROUT2 16 2 14 7 12 9 RS232_TX1 RS232_TX2 RXD1_3V3 RXD2_3V3 3V3 GND C509 A 100nF 3V3

100nF 15 UART1_RTS_1V8 15 UART1_CTS_1V8 1V8 Internal 10K Pullups. 3 5 4 6 VCCA A1 A2 OE

U501 100nF VCCB 7 UART1_RTS_3V3 B1 8 UART1_CTS_3V3 B2 1 GND 2 GND 3V3

TXS0102DCUR VCCA <= VCCB

Internal 10K Pullups.

C503 GND

1V8 GND

C505

TXD2_3V3 RXD2_3V3

100nF 15 UART1_TXD_1V8 15 UART1_RXD_1V8 1V8 Internal 10K Pullups.

B

3 5 4 6

VCCA A1 A2 OE

U502 100nF VCCB 7 UART1_TXD_3V3 B1 8 UART1_RXD_3V3 B2 1 GND 2 GND

TXS0102DCUR VCCA <= VCCB

Internal 10K Pullups.

B

C501 GND

1V8 GND

C513

3V3

DEBUG CONSOLE RS232 INTERFACE

R504 J501 10 8 6 4 2 R512 R511 220R 220R 220R RS232_TX2 RS232_RX2

100nF 15 UART2_TXD_1V8 15 UART2_RXD_1V8 1V8 Internal 10K Pullups. 3 5 4 6 VCCA A1 A2 OE

U505 100nF VCCB 7 UART2_TXD_3V3 B1 8 UART2_RXD_3V3 B2 1 GND 2 GND

UART2_TXD_3V3 4 UART2_RXD_3V3 4

R515 RS232_RX1 R507 RS232_TX1 R502

220R 220R 220R

9 7 5 3 1

TXS0102DCUR VCCA <= VCCB

Internal 10K Pullups. DNI HEADER 5X2

C510

C

1V8 GND

C504

3V3

by default OMAP UART3 10 GND GND D502 DNI PGB0010603MR D504 DNI PGB0010603MR R519 DNI 220R RS232_CTS GND 5 9 4 8 3 7 2 6 1 11 GND_EARTH

C

GND 100nF 15 UART3_TXD_1V8 15 UART3_RXD_1V8 1V8 Internal 10K Pullups. 3 5 4 6

VCCA A1 A2 OE

U503 100nF VCCB 7 UART3_TXD_3V3 B1 8 UART3_RXD_3V3 B2 1 GND 2 GND

J502 A-DS09A/KG-T2

R505 UART3_TXD_3V3 4 UART3_RXD_3V3 4 RS232_TX1 RS232_RX1 R501 R509 R517

DNI 220R 220R 220R DNI 220R

RS232_RX2 RS232_TX RS232_RX RS232_TX2 GND GND

UART RS-232 Transceiver

J502

TXS0102DCUR VCCA <= VCCB

Internal 10K Pullups. R518 DNI 220R RS232_RTS D503 DNI PGB0010603MR D501 DNI PGB0010603MR

GND_EARTH Wednesday, December 15, 2010

REV

D

DATE

DESCRIPTION

AUTHOR

D

XX/XX/XX This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU.

This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

1 2 3 4

BASE.0010 RS232

SCALE

1/1

REV.

SHEET

B2

7 8

6 16

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

15 15

D

HSOL HSOR

HSOL HSOR

C600 47uF C601 47uF

INTER_HSOL INTER_HSOR

R600 R601

33R CONN_HSOL 33R CONN_HSOR

5 J601 4

AUDIO_OUT

1

35RASMT2BHNTR C602 47pF D601 C603 47pF D602

PGB0010603MR PGB0010603MR GND AUXL AUXR C604 100nF C605 100nF C606 47pF C607 47pF PGB0010603MR PGB0010603MR GND GND GND GND GND GNDGND 15 15 AUXL AUXR CONN_AUXL CONN_AUXR D603 D604

5 J602 4

AUDIO_IN

1

35RASMT2BHNTR

6 G5 G3

GND

D605 SM6T

GND

USBOTG_VBUS 15 USBOTG_DN 15 USBOTG_DP 15 USBOTG_ID R602 0R D608 D606 D607 R603 DNI 0R GND PGB0010603MR PGB0010603MR PGB0010603MR

B

1 2 3 4 5

G4

VB DD+ ID G1

G2

C608 10uF 10V

GND_EARTH

Mini-AB (OTG) J603

GND GND GND GND GND_EARTH

W ednesday, December 15, 2010 This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU.

A INIT EDIT

REV

AFG

DES.

25/08/08

DATE

MCT

VER. REV.

xx/xx/08

DATE

SHEET

MODIF.

This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

BASE.0010 USB OTG / AUDIO

SCALE

1/1

1

B2

7 16

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

3V3

FB701

EXC-3BP121H 500mA / 0.1DCR DVI_PVDD EXC-3BP121H 500mA / 0.1DCR TVDD EXC-3BP121H 500mA / 0.1DCR DVI_DVDD C700 100nF C701 100nF C702 100nF C703 100nF C704 100nF C705 100nF RT701 DNI MICROSMD010F VBAT R701 DNI 0R DC_5V R700 0R

FB702

FB703

1V8 R702 10K

Adjusted for .9V

Place Close to the OMAP Processor. R703 10K DVI_VREF U701 15 R_DSS_D[0..23] R_DSS_D0 R_DSS_D1 R_DSS_D2 R_DSS_D3 R_DSS_D4 R_DSS_D5 R_DSS_D6 R_DSS_D7 R_DSS_D8 R_DSS_D9 R_DSS_D10 R_DSS_D11 R_DSS_D12 R_DSS_D13 R_DSS_D14 R_DSS_D15 R_DSS_D16 R_DSS_D17 R_DSS_D18 R_DSS_D19 R_DSS_D20 R_DSS_D21 R_DSS_D22 R_DSS_D23

RT702 RXEF010

SOLAPAR

1 33 12 29 23 18

J701

15 R_DSS_PCLK 15 R_DSS_ACBIAS 15 R_DSS_VSYNC 15 R_DSS_HSYNC 15 B_DVI_PUP R708 R709 3V3 R713 R714 R715 R710 R711 GND DVI_PUP 10K 1K 10K 10K DNI 1K DNI 1K DNI 1K ISEL BSEL DVI_DSEL DK3 DK2 DK1

63 62 61 60 59 58 55 54 53 52 51 50 47 46 45 44 43 42 41 40 39 38 37 36 57 56 2 5 4 3 10 13 15 14 6 7 8

DVDD DVDD DVDD TVDD TVDD PVDD

PD0 PD1 PD2 PD3 PD4 PD5 PD6 PD7 PD8 PD9 PD10 PD11 PD12 PD13 PD14 PD15 PD16 PD17 PD18 PD19 PD20 PD21 PD22 PD23 IDCK+ IDCKDE VSYNC HSYNC VREF

TXD2TXD2+

30 31

DVI_TXD2DVI_TXD2+

3 1 2 15 16

DAT2DAT2+ DAT2_S SCL SDA DAT1DAT1+ DAT1_S S1 S2 S3 S4 S1 S2 S3 S4

DVI-D Interface

TXD1TXD1+

27 28

DVI_TXD1DVI_TXD1+

6 4 5

DVI_+5v

GND_EARTH 3V3 HTPLG R704 10K

HTPLG TXD0TXD0+

9 24 25

DVI_TXD0DVI_TXD0+

18 17 19 9 7 8 11 10 12

+5V DDC/CEC GND HPLG DAT0DAT0+ DAT0_S CLK_S CLK+ CLKHDMI-A

TXC+ TXC-

22 21

3V3 TVDD R705 510 R706 1K

DVI_TXC+ DVI_TXC1V8

CEC NC

13 14

R707 4.7K

PD ISEL/RESET BSEL/SCL DSEL/SDA DK3 DK2 DK1

TFADJ DKEN RSVD2 NC MSEN

19 35 34 49 11

TFADJ DKEN 410_NC MSEN R712 4.7K

TGND TGND TGND DGND DGND DGND 26 32 20 16 48 64

17 65

TFP410

PGND TP

GND 1V8

GND C706 100nF

C707 100nF 5,10,15 I2C3_SCL 5,10,15 I2C3_SDA Internal 10K Pullups.

U702

3 5 4 6

VCCA A1 A2 OE

VCCB B1 B2 GND

7 8 1 2

Internal 10K Pullups.

DDC_I2C3_SCL DDC_I2C3_SDA

TXS0102DCUR

EDID I2C Interface

<Variant Name> This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU. BASE.0010 DVI-D

W ednesday, December 15, 2010

A INIT EDIT

REV

AFG

DES.

25/08/08

DATE

MCT

VER. REV.

xx/xx/08

DATE

SHEET

This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

MODIF.

SCALE

1/1

1

B2 8 16

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

GND HUB_3V3 For self-powered applications with a permanent attached host, this pin must be connected to 3V3 U801 USB2514QFN36

GND

Upstream

27 USBUP_DP VBUS_DET USBUP_DM 31 30

Differential pairs together USBH_DP 15 USBH_DM 15 R800 DNI 0R R801 DNI 0R DC_5V USB Current-Limited Power Switch

C802 1nF USBHUB1_VBUS USBHUB2_VBUS USBHUB1_OC USBHUB2_OC GND C805 1nF GND + + J801 DM DP A

C800 100uF 10V 300R@100MHz 500mA 0603 MMZ1608R301A FB800 300R@100MHz 500mA 0603 MMZ1608R301A FB801 C806 100uF 10V

C801 100nF USBHUB1_OC

2

USBHUB1_DP Differential pairs together USBHUB1_DM R802 C803 47pF 50V C804 100nF 50V R803 10K 10K

Downstream 1

13 OCS1 USBDN1_DP USBDN1_DM PRTPWR1 2 1 12

IN

OUT1_L

7 6 8 5

3 4 1

EN1_L OUT2_L EN2_L GND

U802

GND

OC1 OC2

GND USBHUB2_OC

GND GND

TPS2042BD

Downstream 2

17 OCS2 USBDN2_DP USBDN2_DM PRTPWR2 4 3 16

Differential pairs together USBHUB2_DP USBHUB2_DM

USBHUB3_OC

Downstream 3

19 OCS3 USBDN3_DP USBDN3_DM PRTPWR3 7 6 18

Differential pairs together USBHUB3_DP USBHUB3_DM

USBHUB1_DM USBHUB1_DP

Common Mode Choke Coil L801 DLP11SN900SL2 90R@100MHz 150mA 2 1

4 3 2

DN801 C807

B1 B2 B3 B4 4 3

A1 A2 DM A3 DP A4

C808

Common Mode Choke Coils L802 DLP11SN900SL2 90R@100MHz 150mA USBHUB2_DM 2 1 USBHUB2_DP 3 4

2 1

1nF DN802

1nF A-USBA-2PC GND_EARTH

USBHUB4_OC

Downstream 4

21 OCS4 USBDN4_DP USBDN4_DM PRTPWR4 9 8 20

Differential pairs together USBHUB4_DP USBHUB4_DM

1

PRTR5V0U2X Ultra low GND capacitance double rail-to-rail ESD protection diode

4

PRTR5V0U2X Ultra low capacitance double rail-to-rail ESD protection diode

GND

GND

GND

HUB_3V3

EEPROM/Config

R805 100K

SDA/SMBDATA/NON_REM1 SCL/SMBCLK/CFG_SEL0 HS_IND/CFG_SEL1

22 24 25

R804 R806 R807

100K 100K 100K GND

Common

26

C809 15 USBHUB_RESET R813 10K GND 100nF Q801 MMUN2233 GND GND GND HUSB_XTAL1 GND Layout note: keep Capacitor close to oscillator with limited distance from traces, recommend using 0402 with pads on traces.

C

RESET

RBIAS

35 23

28

R809 100K

LOCAL_PWR/NON_REM0/SUSP_IND_N VDD33(IO) TEST VDD33(REG)

HUSB_RBIAS R808 12K 1% GND C810 100nF C811 47pF

300R@100MHz 500mA 0603 MMZ1608R301A FB802 HUB_3V3 300R@100MHz 500mA 0603 MMZ1608R301A FB803 HUB_3V3 C814 4.7uF 300R@100MHz 500mA 0603 MMZ1608R301A FB804 HUB_3V3 DC_5V

11

15

C812 100nF C813 47pF

GND

GND

C815

GND

33

XTAL1/CLKIN VDDA33

22pF Y801 24MHz C824 HUSB_XTAL2 R810 1M

C818 100nF

VDDA33

10

C820 100nF

C819 47pF 300R@100MHz 500mA 0603 MMZ1608R301A FB806 HUB_3V3 C821 47pF 300R@100MHz 500mA 0603 MMZ1608R301A FB808 HUB_3V3 C828 47pF 300R@100MHz 500mA 0603 MMZ1608R301A FB809 HUB_3V3 C830 47pF

2

R811 C822 47pF 50V C823 100nF 50V R812 10K 10K

IN

OUT1_L

7 6 8 5

USBHUB3_VBUS USBHUB4_VBUS USBHUB3_OC USBHUB4_OC GND C825 1nF GND + C826 100uF 10V 300R@100MHz 500mA 0603 MMZ1608R301A FB807

C

3 4 1

EN1_L OUT2_L EN2_L GND

U803

32

OC1 OC2

XTAL2 VDDA33 VDDPLL18 VDDCR18

29

C827 100nF

GND

22pF

GND

C823 GND GND

TPS2042BD

37

VSS(FLAG)

VDDPLLREF/VDDA33

36

C829 100nF

34

14

VDD18PLL C831 100nF C832 1uF C833 1uF

VDD18CR USBHUB3_DM C834 100nF C835 1uF C836 1uF USBHUB3_DP

Common Mode Choke Coil L803 DLP11SN900SL2 90R@100MHz 150mA 2 1

J802 DM DP

4 3 2

DN803 C837

B1 B2 B3 B4 4 3

1nF A-USBA-2PC GND_EARTH

4

3V3 FB810

D

HUB_3V3 PRTR5V0U2X Ultra low GND capacitance double rail-to-rail ESD protection diode C840 C839 100nF + 1uF C841 100uF This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU.

REV

GND

BLM18SG121TN1 120R@100MHz 3A 0603

GND

GND

GND

This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

1 2 3 4 5

USB Current-Limited Power Switch

C816 1nF

C817 100uF 10V

300R@100MHz 500mA 0603 MMZ1608R301A FB805

A B

A1 A2 DM A3 DP A4

C838

Common Mode Choke Coils L804 DLP11SN900SL2 90R@100MHz 150mA USBHUB4_DM 2 1 USBHUB4_DP 3 4

2 1

1nF DN804

4

PRTR5V0U2X Ultra low capacitance double rail-to-rail ESD protection diode Thursday, December 16, 2010

DATE

DESCRIPTION AUTHOR

GND

GND

XX/XX/XX

BASE.0010 USB HOST 4 PORT

SCALE

1/1

8

REV.

SHEET

B2

9 16

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

D901 U901 CAN_DTX GND VDD_CAN 1V8 C900 VDD_CAN C901 CAN_DRX GND GND PGB0010603MR

1 2 3 4

TXD VSS VDD RXD

RS CANH CANL VREF

8 7 6 5

CANH CANL

MCP2551 C902 D902 PGB0010603MR VDD_CAN GND 100nF GND GND CANH CANL RS485_A RS485_B

J901

J902

GND

100nF

U902

100nF GND

3,15 McSPI1_SIMO 3,15 McSPI1_SOMI 3,15 McSPI1_CLK 15 McSPI1_CS0

1 2 3 4 5 6 7

VCCA A1 A2 A3 A4 NC1 GND

VCCB B1 B2 B3 B4 NC2 OE

14 13 12 11 10 9 8

1 2 3 4 5

FCI 20020004-C05 FCI 20020110-C05

CAN_SPI_SI CAN_SPI_SO CAN_SPI_CLK CAN_SPI_CS

TXB0104PW R GND

R901 10K

VDD_CAN

CAN INTERFACE

R902 10K CAN_NRST C903 VDD_CAN VDD_CAN 100nF GND GND U903 CAN_DTX CAN_DRX TP901 TP902 TP903 TP904 CAN_OSC2 CAN_OSC1 Q901 MMUN2233 CAN_RESET 15

1V8

Y901 GND C904 22pF 20.000MHZ C905 22pF

1 2 3 4 5 6 7 8 9 10

TXCAN RXCAN CLKOUT TXB0RTS TXB1RTS NC TXB2RTS OSC2 OSC1 VSS

MCP2515

VDD RESET CS SO SI NC SCK INT RX0BF RX1BF

20 19 18 17 16 15 14 13 12 11

CAN_SPI_CS CAN_SPI_SO CAN_SPI_SI CAN_SPI_CLK CAN_INT TP905 TP906

CAN_IRQ MMUN2233

15

I2C EEPROM

I2C Address = 0x52

Q902 GND 1V8 R917 10K

U904

1 2 3 6 7

A0 A1 A2 SCL WP VCC

SDA

I2C3_SDA 5,8,15

5,8,15 I2C3_SCL GND

GND

GND

DC_5V VBAT

R903 0R R904 DNI 0R

VDD_CAN

GND

1V8

AT24C01BN-SH-B 1V8

C906 GND

C

100nF

RS485 INTERFACE

3V3 3V3 3V3 C907 GND GND

R905 4.7K UART1_RXD_3V3 UART1_CTS_3V3 UART1_RTS_3V3 UART1_TXD_3V3 R910 R911 R912 R914 DNI 0R DNI 0R DNI 0R DNI 0R RS485_RXD RS485_CTS RS485_TXEN RS485_TXD

R906 10K

R907 100nF 1K U905 GND 3V3 R908 1K D903 PGB0010603MR

TP907 RS485_B D904 R913 220R D905 GND R909 1K PGB0010603MR TP908 3V3 PGB0010603MR RS485_A

4,6 UART1_RXD_3V3 6 UART1_CTS_3V3 6 UART1_RTS_3V3 4,6 UART1_TXD_3V3

1 2 3 4

RO RE DE DI

SP3483

VCC B A GND

8 7 6 5

R915 100K

R916 DNI 0R

GND

GND

GND W ednesday, December 15, 2010

REV

DATE

DESCRIPTION

AUTHOR

This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU.

XX/XX/XX

BASE.0010 CAN BUS - RS485

SCALE

1/1

8

REV.

SHEET

B2

10 16

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

3V3 FB1000 EXC-3BP121H 500mA / 0.1DCR 1V8 ENET0_VDDVARIO ENET0_VDDVARIO R1000 0R

A

ENET0_VDD_A

ENET0_CORE_1.8V

ENET0_VDD_A R1001 49.9 R1002 49.9 R1003 49.9 R1004 49.9 R1005 10

RJ45 ETHERNET CONNECTOR

18 24 30 56

46 49 51

53

U1001 12,15 GPMC_A[1:7] GPMC_A1 GPMC_A2 GPMC_A3 GPMC_A4 GPMC_A5 GPMC_A6 GPMC_A7 12,15 GPMC_D[0:15] GPMC_D0 GPMC_D1 GPMC_D2 GPMC_D3 GPMC_D4 GPMC_D5 GPMC_D6 GPMC_D7 GPMC_D8 GPMC_D9 GPMC_D10 GPMC_D11 GPMC_D12 GPMC_D13 GPMC_D14 GPMC_D15

2 37

15

VDDVARIO VDDVARIO VDDVARIO VDDVARIO

+3.3V

VDD33A VDD33A VDD33A

VDD18A

VDD18CORE VDD18CORE

J1001

12 11 10 9 8 7 6 36 35 34 33 32 31 29 28 27 26 25 23 22 21 20 19

A1 A2 A3 A4 A5 A6 A7 D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15

TPO+

45

C1001 15pF

ENET0_TPO+

P1

TD+ CT

16

TX+

TPO-

44

ENET0_TPO-

P2 P3

TD-

TX-

TPI+

48

C1000 15pF

ENET0_TPI+

P4

RD+ CT

RX+

LAN9221i

TPIEXRES

47 50 40 38 39

ENET0_EXRES1

ENET0_TPI-

P5 P6 P7

NC

RD-

RX-

EECLK/GPO4/RX_DV/RX_CLK EEDIO/GPO3/TX_EN/TX_CLK EECS

ENET0_PROM_CLK ENET0_PROM_DIO ENET0_PROM_CS ENET0_VDDVARIO

R1006 12.4K

P8 P9

4 5

ENET0_VDDVARIO

R1008 4.7K

GPIO0/nLED1 GPIO1/nLED2 GPIO2/nLED3 PME XTAL1/CLKIN XTAL2 VSS(PAD) nRESET

3 4 5 41 55

ENET0_nLINK_ACT ENET0_nFDPLX ENET0_PME

R1007 1K

C1002 22nF R1009 R1010 75R R1011 75R R1012 75R 75R

P10

7 8

12,15 GPMC_nOE 12,15 GPMC_nW E 15 ENET0_CS

GPMC_nOE GPMC_nW E ENET0_CS ENET0_MADIX_EN ENET0_FIFO_SEL

15 16 17 52 13 43 14

nRD nWR nCS MADIX_EN FIFO_SEL IRQ TEST

LAN9221

R1013

R1014 ENET0_XETH2 ENET0_XETH1 1M Y1001 Layout note: keep C1 and C4 close to U2 with limited distance from traces, recommend using 0402 with pads on traces. +

54 42

10

11

12

13

R1015 DNI 1K

15

ENET0_IRQ

ENET0_IRQ

Use Res to tune your Crystal choice to the correct drive power.

2000V

2000V

3V3 R1016 R1017

57

25MHz ENET0_VDDVARIO C1005 33pF C1006 33pF

1K ENET0_nLINK_ACT 1K ENET0_nFDPLX

ENET0_VDDVARIO ENET0_VDDVARIO

C

14

C1003 1nF

C1004 1nF

R1018 4.7K R1020 DNI 4.7K 15 ENET0_nRESET

R1019 4.7K ENET0_VDDVARIO

OPTIONAL

ENET0_VDDVARIO R1022 4.7K

R1021 10K R1023 1K ENET0_CORE_1.8V C1009 C1008 4.7uF 10nF C1010 10nF C1011 C1012 100nF 10nF C1013 100nF C1014 100nF C1015 100nF GND GND GND ENET0_VDDVARIO C1007 100nF

U1002 8 VCC

6 7 5

DI ORG DO DC CS SK GND

3 4 1 2

ENET0_PROM_DIO R1024 1K ENET0_PROM_CLK ENET0_PROM_CS R1025 100K

DNI AT93C46E

3V3

D

ENET0_VDD_A

D

W ednesday, December 15, 2010 C1016 100nF C1017 100nF C1018 100nF C1019 100nF

REV

C1020 4.7uF

DATE

DESCRIPTION

AUTHOR

This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

1 2 3 4 5

This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU.

XX/XX/XX

BASE.0010 ETHERNET0

SCALE

1/1

8

REV.

SHEET

B2

11 16

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

3V3 L1102 EXC-3BP121H 500mA / 0.1DCR 1V8 ENET1_VDDVARIO ENET1_VDDVARIO R1100 0R

A

ENET1_VDD_A

ENET1_CORE_1.8V

ENET1_VDD_A R1101 49.9 R1102 49.9 R1103 49.9 R1104 49.9 R1105 10

RJ45 ETHERNET CONNECTOR

18 24 30 56

46 49 51

53

U1101 11,15 GPMC_A[1:7] GPMC_A1 GPMC_A2 GPMC_A3 GPMC_A4 GPMC_A5 GPMC_A6 GPMC_A7 11,15 GPMC_D[0:15] GPMC_D0 GPMC_D1 GPMC_D2 GPMC_D3 GPMC_D4 GPMC_D5 GPMC_D6 GPMC_D7 GPMC_D8 GPMC_D9 GPMC_D10 GPMC_D11 GPMC_D12 GPMC_D13 GPMC_D14 GPMC_D15

2 37

15

VDDVARIO VDDVARIO VDDVARIO VDDVARIO

+3.3V

VDD33A VDD33A VDD33A

VDD18A

VDD18CORE VDD18CORE

J1101

12 11 10 9 8 7 6 36 35 34 33 32 31 29 28 27 26 25 23 22 21 20 19

A1 A2 A3 A4 A5 A6 A7 D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15

TPO+

45

C1100 15pF

ENET1_TPO+

P1

TD+ CT

16

TX+

TPO-

44

ENET1_TPO-

P2 P3

TD-

TX-

TPI+

48

C1101 15pF

ENET1_TPI+

P4

RD+ CT

RX+

LAN9221i

TPIEXRES

47 50 40 38 39

ENET1_EXRES1

ENET1_TPI-

P5 P6 P7

NC

RD-

RX-

EECLK/GPO4/RX_DV/RX_CLK EEDIO/GPO3/TX_EN/TX_CLK EECS

ENET1_PROM_CLK ENET1_PROM_DIO ENET1_PROM_CS ENET1_VDDVARIO

R1106 12.4K

P8 P9

4 5

ENET1_VDDVARIO

R1108 4.7K

GPIO0/nLED1 GPIO1/nLED2 GPIO2/nLED3 PME XTAL1/CLKIN XTAL2 VSS(PAD) nRESET

3 4 5 41 55

ENET1_nLINK_ACT ENET1_nFDPLX ENET1_PME

R1107 1K

C1102 22nF R1109 R1110 75R R1111 75R R1112 75R 75R

P10

7 8

11,15 GPMC_nOE 11,15 GPMC_nW E 15 ENET1_CS

GPMC_nOE GPMC_nW E ENET1_CS ENET1_MADIX_EN ENET1_FIFO_SEL

15 16 17 52 13 43 14

nRD nWR nCS MADIX_EN FIFO_SEL IRQ TEST

LAN9221

R1113

R1114 ENET1_XETH2 ENET1_XETH1 1M Y1101 Layout note: keep C1 and C4 close to U2 with limited distance from traces, recommend using 0402 with pads on traces. +

54 42

10

11

12

13

R1115 DNI 1K

15

ENET1_IRQ

ENET1_IRQ

Use Res to tune your Crystal choice to the correct drive power.

2000V

2000V HFJ11-RPE26E-S1L12RL

3V3 R1116 R1117

57

25MHz ENET1_VDDVARIO C1105 33pF C1106 33pF

1K ENET1_nLINK_ACT 1K ENET1_nFDPLX

ENET1_VDDVARIO ENET1_VDDVARIO

C

14

C1103 1nF

C1104 1nF

R1118 4.7K R1120 DNI 4.7K 15 ENET1_nRESET

R1119 4.7K ENET1_VDDVARIO

OPTIONAL

ENET1_VDDVARIO R1122 4.7K

R1121 10K R1123 1K ENET1_CORE_1.8V C1109 C1108 4.7uF 10nF C1110 10nF C1111 C1112 100nF 10nF C1113 100nF C1114 100nF C1115 100nF GND GND GND ENET1_VDDVARIO C1107 100nF

U1102 8 VCC

6 7 5

DI ORG DO DC CS SK GND

3 4 1 2

ENET1_PROM_DIO R1125 1K ENET1_PROM_CLK ENET1_PROM_CS R1124 100K

DNI AT93C46E

3V3

D

ENET1_VDD_A

D

W ednesday, December 15, 2010 C1116 100nF C1117 100nF C1118 100nF C1119 100nF

REV

C1120 4.7uF

DATE

DESCRIPTION

AUTHOR

This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

1 2 3 4 5

This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU.

XX/XX/XX

BASE.0010 ETHERNET1

SCALE

1/1

8

REV.

SHEET

B2

12 16

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

J1202 J1201 FCI 20020110-C04 R1200 POW ER_RAW DNI 0R R1201 DC_5V 0R

A

J1204 J1203 FCI 20020110-C04

PW R_RELAY

1 2 3 4

FCI 20020004-C04

1 2 3 4

FCI 20020004-C04

RL1201 5mm isolation PW R_RELAY D1201 1N4148

RL1202

RL1203

RL1204

4 3 1 2

TP1201 G6DS-1A-5VDC PW R_RELAY D1202 1N4148

4 3 1 2

TP1202 G6DS-1A-5VDC PW R_RELAY D1203 1N4148

4 3 1 2

TP1203 G6DS-1A-5VDC PW R_RELAY D1204 1N4148

4 3 1 2

TP1204 G6DS-1A-5VDC

5mm isolation

TP1205 Q1201 BSS138-SOT23 15 DOUTPUT2_1V8 R1202 1K

TP1206 Q1202 BSS138-SOT23 R1203 1K

TP1207 Q1203 BSS138-SOT23 R1204 1K

TP1208 Q1204 BSS138-SOT23 R1205 1K

15 DOUTPUT1_1V8

15 DOUTPUT3_1V8

16 DOUTPUT4_1V8

GND

GND

GND

GND

GND

GND

GND

GND

R1206 POW ER_RAW 0R R1207 DC_5V DNI 0R PW R_INPUT D1205 1N4148 D1206 J1205 FCI 20020110-C04 Q1205 BC81740E6327 GND DINPUT2_1V8 15 R1209 10K 1N4148

C

PW R_INPUT

DINPUT1_1V8 15 R1208 10K C1200 TP1209 470nF

GND

1 2 3 4

FCI 20020004-C04 J1206

DNI PGB0010603MR GND GND GND D1207 PW R_INPUT

C1201 TP1210 470nF

C

D1208

Q1206 BC81740E6327 GND

GND

DNI PGB0010603MR GND PW R_INPUT D1209 1N4148 D1210 J1207 FCI 20020110-C04 R1210 10K

DINPUT3_1V8 15 C1202 TP1211 470nF

Q1207 BC81740E6327 GND

GND

1 2 3 4

FCI 20020004-C04 J1208

DNI PGB0010603MR GND GND GND D1211 1N4148 PW R_INPUT R1211 10K

DINPUT4_1V8 16 C1203 TP1212 470nF

D

D1212

Q1208 BC81740E6327 GND

W ednesday, December 15, 2010 GND This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU.

REV

DATE

DESCRIPTION

AUTHOR

XX/XX/XX

DNI PGB0010603MR GND This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

BASE.0010 INPUT / OUTPUT

SCALE

1/1

8

REV.

SHEET

B2

13 16

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

3V3 FB1300 C1300 10uF 10V

A

VGA_AVCC

BLM18SG121TN1 120R@100MHz 3A 0603 C1301 100nF FB1301 BLM18SG121TN1 120R@100MHz 3A 0603

C1302 10uF 10V C1303 100nF

The PC board layout should have two distinct power planes, one for analog circuitry and one for digital circuitry. The analog power plane should encompass the ADV7125 (VAA) and all associated analog circuitry. This power plane should be connected to the regular PCB power plane (VCC) at a single point through a ferrite bead, as illustrated in Figure 6. This bead should be located within three inches of the ADV7125. The PCB power plane should provide power to all digital logic on the PC board, and the analog power plane should provide power to all ADV7125 power pins, voltage reference circuitry, and any output amplifiers. The PCB power and ground planes should not overlay portions of the analog power plane. Keeping the PCB power and ground planes from overlaying the analog power plane will contribute to a reduction in plane-to-plane noise coupling.

GND_EARTH

16

VGA_R_OUT VGA_G_OUT VGA_B_OUT

GND

VGA_GND

VGA_HSYNC_OUT VGA_VSYNC_OUT POWER SUPPLY DECOUPLING (100nF AND 10nF CAPACITOR FOR EACH VAA GROUP) VGA_AVCC VGA_AVCC VGA_AVCC VGA_GND C1304 100nF C1305 10nF C1306 100nF C1307 10nF C1308 100nF C1309 10nF

1 9 2 10 3 11 4 12 5 13 6 14 7 15 8 17

A-HDF15A-KG/T

J1301

GND_EARTH

VGA_GND

B

VGA_GND

VGA_GND VGA_AVCC

B

3,15 B_DSS_D[0..23]

B_DSS_D[0..23]

Place Close to the Buffer B_DSS_D0 B_DSS_D1 B_DSS_D2 B_DSS_D3 B_DSS_D4 B_DSS_D5 B_DSS_D6 B_DSS_D7 B_DSS_D8 B_DSS_D9 B_DSS_D10 B_DSS_D11 B_DSS_D12 B_DSS_D13 B_DSS_D14 B_DSS_D15 B_DSS_D16 B_DSS_D17 B_DSS_D18 B_DSS_D19 B_DSS_D20 B_DSS_D21 B_DSS_D22 B_DSS_D23 B_DSS_PCLK B_DSS_ACBIAS B_DSS_VSYNC B_DSS_HSYNC RP1300A1 RP1300B2 RP1300C3 RP1300D4 RP1300E5 RP1300F 6 RP1300G7 RP1300H8 RP1301A1 RP1301B2 RP1301C3 RP1301D4 RP1301E5 RP1301F 6 RP1301G7 RP1301H8 RP1302A1 RP1302B2 RP1302C3 RP1302D4 RP1302E5 RP1302F 6 RP1302G7 RP1302H8 RP1303A1 RP1303B2 RP1303C3 RP1303D4 RP1303E5 RP1303F 6 RP1303G7 RP1303H8

VGA_D[0..23] U1301

VGA_GND VGA_GND VGA_GND

3,15 3,15 3,15 3,15

B_DSS_PCLK B_DSS_ACBIAS B_DSS_VSYNC B_DSS_HSYNC

16 15 14 13 12 11 10 9 16 15 14 13 12 11 10 9 16 15 14 13 12 11 10 9 16 15 14 13 12 11 10 9

10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10

VGA_D0 VGA_D1 VGA_D2 VGA_D3 VGA_D4 VGA_D5 VGA_D6 VGA_D7 VGA_D8 VGA_D9 VGA_D10 VGA_D11 VGA_D12 VGA_D13 VGA_D14 VGA_D15 VGA_D16 VGA_D17 VGA_D18 VGA_D19 VGA_D20 VGA_D21 VGA_D22 VGA_D23 VGA_CLK VGA_DEN VGA_VSYNC VGA_HSYNC

VGA_D16 VGA_D17 VGA_D18 VGA_D19 VGA_D20 VGA_D21 VGA_D22 VGA_D23 VGA_D8 VGA_D9 VGA_D10 VGA_D11 VGA_D12 VGA_D13 VGA_D14 VGA_D15 VGA_D0 VGA_D1 VGA_D2 VGA_D3 VGA_D4 VGA_D5 VGA_D6 VGA_D7 VGA_AVCC VGA_AVCC C1313 100nF VGA_CLK VGA_REF 530R

41 42 43 44 45 46 47 48 3 4 5 6 7 8 9 10 16 17 18 19 20 21 22 23 24 36 35 37 11 38 12 1 2 14 15 25 26 39 40

R0 R1 R2 R3 R4 R5 R6 R7 G0 G1 G2 G3 G4 G5 G6 G7 B0 B1 B2 B3 B4 B5 B6 B7 CLOCK VREF COMP RSET BLANK PSAVE SYNC GND GND GND GND GND GND GND GND

VAA VAA VAA IOR IOR IOG IOG IOB IOB

13 29 30 34 33 32 31 28 27

C1310 10pF

C1311 10pF

C1312 10pF VGA_R_OUT VGA_G_OUT VGA_B_OUT 3V3 3V3 D1302 BAV99L 3V3 D1303 BAV99L

3

VGA_GND VGA_GND VGA_GND VGA_GND

VGA_GND

VGA_GND

VGA_GND

C

C1314 100nF R1303 VGA_DEN B_VGA_PUP

DC_5V U1302 VGA_HSYNC VGA_VSYNC

VGA_GND 15 B_VGA_PUP

1 3 2

1A 2A GND

VCC 1Y 2Y

5 6 R1304 4 R1305

33R 33R DC_5V D1304 BAV99L DC_5V VGA_HSYNC_OUT VGA_VSYNC_OUT

VGA_GND

74LVC2G34GV VGA_GND C1315 DC_5V 100nF

R1300 75R

R1301 75R

R1302 75R

D1301 BAV99L

3

VGA_GND

ANALOG ADV7125KSTZ140 VGA_GND

D1305 BAV99L C1316 3 10pF

C1317 10pF

VGA_GND

D

VGA_GND W ednesday, December 15, 2010

REV

DATE

DESCRIPTION

AUTHOR

This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU.

XX/XX/XX

BASE.0010 VGA

SCALE

1/1

8

REV.

SHEET

B2

7

14 16

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

IGEP.0030 and IGEP.0032 Expansion Connectors

J1 SW 1401 N_MANUAL_RESET DNI SW _PB_SPST GND GND 3

A

J4 PMIC_VBACKUP R1400 DNI 0R GND GPIO59_GPMC_CLK GPIO61_GPMC_nBE1 GPMC_WAIT0 TP1402 GPIO57_GPMC_nCS6 GPMC_nCS0 TP1403 GPIO60_GPMC_nBE0_CLE GPIO52_GPMC_nCS1 GPIO62_GPMC_nWP GPIO42_GPMC_A9 GPMC_A4 GPIO43_GPMC_A10 GPMC_A3 GPMC_A1 GPMC_A6 GPMC_D0 GPMC_D9 GPMC_D8 GPMC_D1 GPMC_D13 GPMC_D6 GPMC_D14 GPMC_D7 GPIO151_RXD1 GPIO150_CTS1 GPIO149_RTS1 GPIO173_SPI1_MISO GPIO172_SPI1_MOSI GPIO171_SPI1_CLK GPIO175_SPI1_CS1 GPIO114_SPI1_NIRQ GPIO12_MMC3_CLK DVI_PUP GPIO20_MMC3_D2 VGA_PUP GPIO23_MMC3_D5 GPIO22_MMC3_D6 GPIO19_MMC3_D1

TS_nPEN_IRQ R1401 R1402 10K 10K

5,8,10 I2C3_SDA 1V8 1V8 5,8,10 I2C3_SCL 3 LCD_EN

6 UART2_RXD_1V8 3 LCD_PW MBKL

UART2_RXD UART2_CTS

6 UART2_TXD_1V8 4 GPIO_MODEM_ON_OFF

UART2_TXD

6 UART3_TXD_1V8

6 UART3_RXD_1V8

N_MANUAL_RESET DSS_D1 DSS_D0 DSS_D3 DSS_D5 DSS_D2 DSS_D4 GPIO10 GPIO0_SYSnIRQ0 GPIO185_I2C_SDA DSS_D10 DSS_D11 GPIO184_I2C_SCL GPIO186 DSS_D22 GPIO147_GPT8_PWM DSS_D13 GPIO144_GPT9_PWM DSS_D14 DSS_D15 GPIO146_GPT11_PWM GPIO163_UART3_CTS DSS_D21 DSS_D17 DSS_D18 GPIO166_UART3_TX DSS_D19 DSS_D9 DSS_D7 DSS_D8 GPIO165_UART3_RX DSS_PCLK DSS_D6 DSS_VSYNC DSS_HSYNC

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35

70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36

GND HSOR HSOL PMIC_PWRON PMIC_ADCIN7 GPIO164_RTS3 GPIO15_MCSPI3_SOMI DSS_D23 DSS_D12 SYSEN PMIC_ADCIN2 PMIC_MIC_MAIN_M GPIO145_GPT10_PWM PMIC_ADCIN6 PMIC_VBACKUP PMIC_ADCIN5 PMIC_PWM1 PMIC_ADCIN3 GPIO170_HDW_1WIRE PMIC_USBOTG_ID DSS_D20 DSS_D16 DSS_ACBIAS PMIC_PWM0 PMIC_ADCIN4 PMIC_MIC_SUB_M PMIC_USBOTG_DN PMIC_USBOTG_DP TP1401 PW R_KILL 2 GPIO_SW _PB 2 TP1404 TP1405 UART2_RTS GND GPIO_MODEM_NRST 4 TP1407 TP1408 7 7 VBAT

GND used on IGEP.0032 module 11 ENET0_CS 11,12 GPMC_nW E 11,12 GPMC_nOE used on IGEP.0032 module 12 ENET1_IRQ

VBAT GPIO56_GPMC_nCS5 GPIO55_GPMC_nCS4 GPMC_nWE GPMC_nADV_ALE GPMC_nOE GPIO65_GPMC_WAIT3 GPIO64_GPMC_WAIT2 GPMC_A2 GPIO41_GPMC_A8 GPMC_A5 GPMC_A7 GPMC_D2 GPMC_D10 GPMC_D3 GPMC_D11 GPMC_D4 GPMC_D12 GPMC_D5 GPMC_D15 GPIO13_MMC3_CMD GPIO148_TXD1 GPIO176_SPI1_CS2 GPIO18_MMC3_D0 GPIO174_SPI1_CS0 GPIO168_USBH_CPEN GPIO14_MMC3_D4 GPIO21_MMC3_D7 GPIO17_MMC3_D3 USBH_VBUS USBH_DP USBH_DM

USBOTG_VBUS

AGND GPIO_MODEM_PW RMON 4 USBOTG_ID 7 CAN_IRQ 6 UART1_TXD_1V8 13 DINPUT1_1V8 13 DINPUT2_1V8 10 MCSPI1_CS0 13 DINPUT3_1V8 13 DOUTPUT1_1V8 13 DOUTPUT2_1V8 13 DOUTPUT3_1V8 DC_5V 9 9 10

AUXR TP1406

AUXL 7 USBOTG_DN 7 USBOTG_DP 7

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35

70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36

CAN_RESET

10

BT1401

ENET0_nRESET 11 PW R_SHDN_INT 2 ENET0_IRQ 11 ENET1_CS 12 GPMC_A[1:7] GPMC_A7 GPMC_A6 GPMC_A5 GPMC_A4 GPMC_A3 GPMC_A2 GPMC_A1 UART1_RXD_1V8 6 UART1_CTS_1V8 6 UART1_RTS_1V8 6 MCSPI1_SOMI 3,10 MCSPI1_SIMO 3,10 MCSPI1_CLK 3,10 MCSPI1_CS1 3 TS_BUSY 3 USBHUB_RESET 9 LED_USER1 2 LED_USER2 2 GPMC_D15 GPMC_D14 GPMC_D13 GPMC_D12 GPMC_D11 GPMC_D10 GPMC_D9 GPMC_D8 GPMC_D7 GPMC_D6 GPMC_D5 GPMC_D4 GPMC_D3 GPMC_D2 GPMC_D1 GPMC_D0 11,12 BATTERY

A

ENET1_nRESET 12

GMPC_Ax

GPMC_D[0:15] 11,12

GMPC_Dx

GND

HEADER 35x2

HEADER 35x2

70-pin connector J1 features the LCD, PWM and analog signals

70-pin connector J4 features Extended Memory Bus and MMC signals

Place close to connector J1 DSS_D[0..23] DSS_D0 DSS_D1 DSS_D2 DSS_D3 DSS_D4 DSS_D5 DSS_D6 DSS_D7 DSS_D8 DSS_D9 DSS_D10 DSS_D11 DSS_D12 DSS_D13 DSS_D14 DSS_D15 DSS_D16 DSS_D17 DSS_D18 DSS_D19 DSS_D20 DSS_D21 DSS_D22 DSS_D23 DSS_PCLK DSS_ACBIAS DSS_VSYNC DSS_HSYNC RP1400A1 RP1400B2 RP1400C3 RP1400D4 RP1400E5 RP1400F 6 RP1400G7 RP1400H8 RP1401A1 RP1401B2 RP1401C3 RP1401D4 RP1401E5 RP1401F 6 RP1401G7 RP1401H8 RP1402A1 RP1402B2 RP1402C3 RP1402D4 RP1402E5 RP1402F 6 RP1402G7 RP1402H8 RP1403A1 RP1403B2 RP1403C3 RP1403D4 RP1403E5 RP1403F 6 RP1403G7 RP1403H8 R_DSS_D0[0..23] R_DSS_D[0..23] 8 1V8 3V3 1V8 3V3 C1402 100nF GND R_DSS_D16 R_DSS_D17 R_DSS_D18 R_DSS_D19 R_DSS_D20 R_DSS_D21 R_DSS_D22 R_DSS_D23 R_DSS_PCLK R_DSS_ACBIAS R_DSS_VSYNC R_DSS_HSYNC VGA_PUP DVI_PUP C1403 100nF GND

16 15 14 13 12 11 10 9 16 15 14 13 12 11 10 9 16 15 14 13 12 11 10 9 16 15 14 13 12 11 10 9

10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10 10

R_DSS_D0 R_DSS_D1 R_DSS_D2 R_DSS_D3 R_DSS_D4 R_DSS_D5 R_DSS_D6 R_DSS_D7 R_DSS_D8 R_DSS_D9 R_DSS_D10 R_DSS_D11 R_DSS_D12 R_DSS_D13 R_DSS_D14 R_DSS_D15 R_DSS_D16 R_DSS_D17 R_DSS_D18 R_DSS_D19 R_DSS_D20 R_DSS_D21 R_DSS_D22 R_DSS_D23 R_DSS_PCLK R_DSS_ACBIAS R_DSS_VSYNC R_DSS_HSYNC

7 18

42 31

7 18

VCCB VCCB

VCCA VCCA

VCCB VCCB

R_DSS_D[0..23]

GND R_DSS_D0 R_DSS_D1 R_DSS_D2 R_DSS_D3 R_DSS_D4 R_DSS_D5 R_DSS_D6 R_DSS_D7 R_DSS_D8 R_DSS_D9 R_DSS_D10 R_DSS_D11 R_DSS_D12 R_DSS_D13 R_DSS_D14 R_DSS_D15

GND

B_DSS_D[0..23]

3,14

VCCA VCCA

U1402 B_DSS_D0 B_DSS_D1 B_DSS_D2 B_DSS_D3 B_DSS_D4 B_DSS_D5 B_DSS_D6 B_DSS_D7 B_DSS_D8 B_DSS_D9 B_DSS_D10 B_DSS_D11 B_DSS_D12 B_DSS_D13 B_DSS_D14 B_DSS_D15

B_DSS_D[0..23]

42 31

C1400 100nF

C1401 100nF

R_DSS_D[0..23]

U1401

B_DSS_D[0..23]

B_DSS_D[0..23]

3,14

2 3 5 6 8 9 11 12 13 14 16 17 19 20 22 23 1 24 48 25 4 10 15 21

1B1 1B2 1B3 1B4 1B5 1B6 1B7 1B8 2B1 2B2 2B3 2B4 2B5 2B6 2B7 2B8 1DIR 2DIR 1OE 2OE GND GND GND GND

1A1 1A2 1A3 1A4 1A5 1A6 1A7 1A8 2A1 2A2 2A3 2A4 2A5 2A6 2A7 2A8

47 46 44 43 41 40 38 37 36 35 33 32 30 29 27 26

2 3 5 6 8 9 11 12 13 14 16 17 19 20 22 23 1 24 48 25

1B1 1B2 1B3 1B4 1B5 1B6 1B7 1B8 2B1 2B2 2B3 2B4 2B5 2B6 2B7 2B8 1DIR 2DIR 1OE 2OE GND GND GND GND

1A1 1A2 1A3 1A4 1A5 1A6 1A7 1A8 2A1 2A2 2A3 2A4 2A5 2A6 2A7 2A8

47 46 44 43 41 40 38 37 36 35 33 32 30 29 27 26

B_DSS_D16 B_DSS_D17 B_DSS_D18 B_DSS_D19 B_DSS_D20 B_DSS_D21 B_DSS_D22 B_DSS_D23 B_DSS_PCLK B_DSS_ACBIAS B_DSS_VSYNC B_DSS_HSYNC B_VGA_PUP

B_DSS_PCLK 3,14 B_DSS_ACBIAS 3,14 B_DSS_VSYNC 3,14 B_DSS_HSYNC 3,14 B_VGA_PUP 14 B_DVI_PUP 8

R_DSS_PCLK 8 R_DSS_ACBIAS 8 R_DSS_VSYNC 8 R_DSS_HSYNC 8

GND GND GND GND

45 39 34 28

GND GND

4 10 15 21

GND GND GND GND

45 39 34 28

GND

GND

SN74AVC16T245DGG DIR low --> B data to A Bus DIR high --> A data to B Bus

SN74AVC16T245DGG DIR low --> B data to A Bus DIR high --> A data to B Bus GND

W ednesday, December 15, 2010

REV

DATE

DESCRIPTION

AUTHOR

This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU.

XX/XX/XX

BASE.0010 CONNECTOR IGEP0030

SCALE

1/1

8

REV.

SHEET

B2

15 16

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

VIO_1V8 J8 PMIC_VMMC1 PMIC_VMMC2 GND USB2HS_CLK USB2HS_STP USB2HS_DIR USB2HS_NXT USB2HS_DAT0 USB2HS_DAT1 GPIO16 GPIO131_MMC2_CMD EN_5V 2 GPIO133_MMC2_DAT1 EN_3V3 2 GPIO135_MMC2_DAT3 GPIO137_MMC2_DAT5 GPIO139_MMC2_DAT7 GPIO121_MMC1_CMD GPIO123_MMC1_DAT1 GPIO125_MMC1_DAT3 GPIO127_MMC1_DAT5 GPIO129_MMC1_DAT7 GPIO53_GPMC_nCS2 GPIO54_GPMC_nCS3 GPMC_nCS7 ENET_nLED1 ENET_nLINK_ACT ENET2_nLINK_ACT ENET_nFDPLX ENET2_nFDPLX ENET_TPI+ ENET_TPIENET_CT ENET_TPO+ ENET_TPO-

R1505

DNI 0R

1V8 J9 PMIC_IHF_LEFT_P PMIC_IHF_LEFT_M PMIC_IHF_RIGHT_P PMIC_IHF_RIGHT_M PMIC_EAR_P PMIC_EAR_M GND PMIC_ADCIN0 PMIC_ADCIN1 GND 32KCLKOUT nRESWARM PMIC_START_ADC PMIC_SYSEN PMIC_GPIO13 PMIC_GPIO15 PMIC_GPIO16 PMIC_GPIO17 GPIO155_MCBSP4_FSX GPIO152_MCBSP4_CLKX GPIO153_MCBSP4_DR GPIO154_MCBSP4_DX GPIO111_CAM_XCLKB GPIO126_CAM_STROBE GPIO110_CAM_D11 GPIO108_CAM_D9 GPIO106_CAM_D7 GPIO104_CAM_D5 GPIO102_CAM_D3 GPIO100_CAM_D1 GPIO97_CAM_PCLK GPIO95_CAM_VS AGND

D

VBAT VIO_1V8 I2C1_SCL I2C1_SDA GPIO168_I2C2_SCL GPIO183_I2C2_SDA I2C4_SCL I2C4_SDA GPIO130_MMC2_CLK GPIO132_MMC2_DAT0 GPIO134_MMC2_DAT2 GPIO136_MMC2_DAT4 GPIO138_MMC2_DAT6 GPIO120_MMC1_CLK GPIO122_MMC1_DAT0 GPIO124_MMC1_DAT2 GPIO126_MMC1_DAT4 GPIO128_MMC1_DAT6 GPIO143_MCBSP3_FSX GPIO142_MCBSP3_CLKX GPIO141_MCBSP3_DR GPIO140_MCBSP3_DX GPIO116_MCBSP2_FSX GPIO117_MCBSP2_CLKX GPIO118_MCBSP2_DR GPIO119_MCBSP2_DX GPIO156_McBSP1_CLKR GPIO157_McBSP1_FSR GPIO158_McBSP1_DX GPIO159_McBSP1_DR GPIO161_McBSP1_FSX GPIO162_McBSP1_CLKX

GND

2 PW R_ACPG 2 PW R_STAT1 2 PW R_STAT2 13 DINPUT4_1V8 13 DOUTPUT4_1V8

4 4 4 4

McBSP1_DX McBSP1_DR McBSP1_FSX McBSP1_CLKX

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35

70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36

HEADER 35x2

VBAT VIO_1V8 PMIC_VHSMIC PMIC_HSMIC_P PMIC_HSMIC_M TV_OUT1R TV_OUT2R PMIC_CD1 PMIC_CD2 PMIC_RFIN_EN PMIC_UART1_RXD PMIC_UART1_TXD SYS_BOOT6 SYS_BOOT5 SYS_BOOT4 SYS_BOOT3 SYS_BOOT2 SYS_BOOT1 SYS_BOOT0 GPIO167_CAM_WEN GPIO63_CAM_IRQ GPIO109_CAM_D10 GPIO107_CAM_D8 CAM_D6 GPIO105_CAM_D6 CAM_D4 GPIO103_CAM_D4 CAM_D2 GPIO101_CAM_D2 CAM_D0 GPIO99_CAM_D0 GPIO98_CAM_FLD GPIO96_CAM_XCLKA GPIO94_CAM_HS

GND

GND

GND

5 5

CAM_RESET CAM_IRQ

ENET2_TPI+ ENET2_TPI- Differential Pair ENET2_CT ENET2_TPO+ ENET2_TPO- Differential Pair

GND 5 5 GND CAM_FLD CAM_HS

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35

70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36

HEADER 35x2

GND

CAM_PDN CAM_D7 CAM_D5 CAM_D3 CAM_D1 CAM_PCLK CAM_VS 5 5

GND

RJ45 ETHERNET CONNECTOR Only for IGEP.0032 module

C

GND_EARTH

15

70-pin connector J8 features MMC1,MMC2, MCBSP1, MCBSP2, MCBSP3

70-pin connector J9 features CAMERA, SYSBOOT, VIDEO COMPOSITE

J3 ENET2_TPO+ Differential Pair ENET2_TPOENET2_CT ENET2_TPI+ Differential Pair

P1

TD+ CT

16

TX+

P2 P3 P4

TD-

TX-

RD+ CT

RX+

S-Video Connector

J2

P1 P2 P3 P4 MH1 MH2 MH3

1 2 3 4 MH1 MH2 MH3

TV_OUT1R TV_OUT2R

CAM_D0 CAM_D1 CAM_D2 CAM_D3 CAM_D4 CAM_D5 CAM_D6 CAM_D7

CAM_D[0..7]

ENET2_TPI-

P5 P6 P7 P8 P9

NC

RD-

RX-

4 5

P10

R1502 75R GND R1501 75R R1506 75R R1504 75R

7 8

MINIDIN 4POS

11

12

13

2000V

GND_EARTH

2000V

3V3 GND_EARTH R1503 R1507

1K ENET2_nLINK_ACT 1K ENET2_nFDPLX

14

C1501 1nF

C1502 1nF

HFJ11-RPE26E-S1L12RL

Thursday, December 16, 2010

REV

DATE

DESCRIPTION

AUTHOR

XX/XX/XX This design is *NOT SUPPORTED* and DO NOT constitute a reference design. THERE IS NO WARRANTY FOR THE DESIGN. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU.

This work is licensed under a Creative Commons Reconocimiento 3.0 Unported License. Attribution You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

BASE.0010 CONNECTOR IGEP0032

SCALE

1/1

1

REV.

SHEET

B2

16 16

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

También podría gustarte

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDe EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsAún no hay calificaciones

- Hws 13642Documento3 páginasHws 13642dhieward100% (2)

- ®MCI Electronics WWW - Olimex.cl: 3V3 3V3 RssiDocumento1 página®MCI Electronics WWW - Olimex.cl: 3V3 3V3 Rssiefx8100% (1)

- DVD Toshiba Sd-3990su, Sd-3990sc Service ManualDocumento30 páginasDVD Toshiba Sd-3990su, Sd-3990sc Service Manualmaldo7Aún no hay calificaciones

- Un32c5000 - 40C5000 - 46C5000 MainDocumento16 páginasUn32c5000 - 40C5000 - 46C5000 Mainmj15015Aún no hay calificaciones

- Steval Mki062v2 SchematicDocumento2 páginasSteval Mki062v2 Schematicd280299Aún no hay calificaciones

- ADV Main SchematicDocumento1 páginaADV Main Schematicgerardobrandao100% (1)

- 42LK520 InterconnectDocumento7 páginas42LK520 InterconnectErnesto SuarezAún no hay calificaciones

- Schematic DiagramDocumento13 páginasSchematic DiagramSas WajiAún no hay calificaciones

- Cigpack Main RC1aDocumento1 páginaCigpack Main RC1aMotojunkie TLAún no hay calificaciones

- 07 Schematic Diagram EDocumento6 páginas07 Schematic Diagram EGiovanni Mendoza100% (1)

- Noblex - RCD - 138Documento8 páginasNoblex - RCD - 138pablo190381Aún no hay calificaciones

- Vin IC2Documento1 páginaVin IC2Harish Kumar MAún no hay calificaciones

- RK-10132 113Documento1 páginaRK-10132 113Sumit SinghAún no hay calificaciones

- Arduino Wifi Shield SchematicDocumento1 páginaArduino Wifi Shield SchematicgetmicrosAún no hay calificaciones

- Diagram PDFDocumento3 páginasDiagram PDFHarsh BoradAún no hay calificaciones

- Wiring DiagramDocumento6 páginasWiring DiagramZoran ProkicAún no hay calificaciones

- Reflow Toaster v2 SchematicDocumento1 páginaReflow Toaster v2 SchematicBest PC BoxAún no hay calificaciones

- HPS10 Calidrare SchemaDocumento20 páginasHPS10 Calidrare SchemafercikeAún no hay calificaciones

- Top-Level Diagram: SHEET 13-18Documento21 páginasTop-Level Diagram: SHEET 13-18Aref MGHAún no hay calificaciones

- LCD Monitor - DC - XL2720TZ - 20130805 - 144041 - 5E.23A01.011 (4H.23A01.S11)Documento12 páginasLCD Monitor - DC - XL2720TZ - 20130805 - 144041 - 5E.23A01.011 (4H.23A01.S11)pasmanteriabella100% (1)

- LCD Monitor - DC - XL2420TX - 20120302 - 150546 - 5E.1M001.002 (4H.1M001.A00)Documento11 páginasLCD Monitor - DC - XL2420TX - 20120302 - 150546 - 5E.1M001.002 (4H.1M001.A00)pasmanteriabellaAún no hay calificaciones

- 6012 SchematicsDocumento24 páginas6012 SchematicsDexter DanielAún no hay calificaciones

- 11 Digit VFD Display With AC Filament Drive C021 EB 20-Bit VFD ...Documento1 página11 Digit VFD Display With AC Filament Drive C021 EB 20-Bit VFD ...Ioana Bulgariu100% (1)

- Easypic Fusion v7 SCH v101Documento2 páginasEasypic Fusion v7 SCH v101vietanh_askAún no hay calificaciones

- CignalDocumento1 páginaCignalNiaz Manik100% (1)

- Marcas Varias DVD Con Procesador Zoran Manual de ServicioDocumento44 páginasMarcas Varias DVD Con Procesador Zoran Manual de ServicioVicente MalvicaAún no hay calificaciones

- EGS002 Manual en PDFDocumento6 páginasEGS002 Manual en PDFValerică Hizanu67% (6)

- PCB DiagramDocumento10 páginasPCB DiagramCraig KalinowskiAún no hay calificaciones

- LAB-X1 SchematicDocumento2 páginasLAB-X1 SchematicRenato MirandaAún no hay calificaciones

- Labx 1 SCHDocumento2 páginasLabx 1 SCHercervantesAún no hay calificaciones

- Thomson Chassis Lcd12b 20lb120s4Documento18 páginasThomson Chassis Lcd12b 20lb120s4vascoalmAún no hay calificaciones

- Circuit Diagram 1201-4529 1B 1Documento14 páginasCircuit Diagram 1201-4529 1B 1Juan Luis VallejoAún no hay calificaciones

- SIM808 UNO SchematicDocumento1 páginaSIM808 UNO Schematicdark hiramekiAún no hay calificaciones

- Wiring DiagramDocumento5 páginasWiring DiagramFernando CoutoAún no hay calificaciones

- Wiring DiagramDocumento4 páginasWiring DiagramManuel Gomez MerquezAún no hay calificaciones

- FPP3Documento1 páginaFPP3uzunku100% (1)

- Schematic - Pic ModuleDocumento1 páginaSchematic - Pic ModuleDuc Le100% (1)

- M52259evb SCHDocumento13 páginasM52259evb SCHkunalkundanam1046Aún no hay calificaciones

- CECL08D Datasheet Mp3-PlayerDocumento1 páginaCECL08D Datasheet Mp3-PlayerGlauber CostaAún no hay calificaciones

- 8 Led Array 16X2 LCD Display Connector Push Botton SwitchDocumento1 página8 Led Array 16X2 LCD Display Connector Push Botton SwitchHarsh BoradAún no hay calificaciones

- LM220WE4Documento8 páginasLM220WE4acostaricciAún no hay calificaciones

- Quanta Bd3a r3c SchematicsDocumento44 páginasQuanta Bd3a r3c SchematicsKostas AthanasiadisAún no hay calificaciones

- Circuit Diagram: ModelDocumento26 páginasCircuit Diagram: ModelOmar LugoAún no hay calificaciones

- Stm32f4discovery LCD UserguideDocumento6 páginasStm32f4discovery LCD UserguideAmil CuryAún no hay calificaciones

- Okok Sony - kv-2197m3 - Cxp85220a - Tda8375 - str-6707 - La7830 - Ta8248k PDFDocumento13 páginasOkok Sony - kv-2197m3 - Cxp85220a - Tda8375 - str-6707 - La7830 - Ta8248k PDFAloui Zakaria100% (1)

- CCTV Surveillance: Video Practices and TechnologyDe EverandCCTV Surveillance: Video Practices and TechnologyCalificación: 4 de 5 estrellas4/5 (1)

- Exploring Arduino: Tools and Techniques for Engineering WizardryDe EverandExploring Arduino: Tools and Techniques for Engineering WizardryCalificación: 4.5 de 5 estrellas4.5/5 (5)

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIDe EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIAún no hay calificaciones

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysDe EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysAún no hay calificaciones

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Aún no hay calificaciones

- Beginning Digital Electronics through ProjectsDe EverandBeginning Digital Electronics through ProjectsCalificación: 5 de 5 estrellas5/5 (1)

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsDe EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsCalificación: 3 de 5 estrellas3/5 (2)

- Radio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142De EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142Aún no hay calificaciones

- OopDocumento53 páginasOopsadani1989Aún no hay calificaciones

- ES - 07 - BuzzersDocumento14 páginasES - 07 - BuzzersYoutube of the dayAún no hay calificaciones

- TEMS Investigation 24.1.1 - Release NoteDocumento21 páginasTEMS Investigation 24.1.1 - Release NoteMuhammad Usman100% (1)

- A Review of The Literature On Environmental Innovation Management in Smes: Implications For Public PoliciesDocumento10 páginasA Review of The Literature On Environmental Innovation Management in Smes: Implications For Public PoliciesworldshiftAún no hay calificaciones

- Winbond W83310dg DatasheetDocumento13 páginasWinbond W83310dg DatasheetLaarsAún no hay calificaciones

- Cisco CCNP JCacademyDocumento1 páginaCisco CCNP JCacademyRobert HornAún no hay calificaciones

- D1 - ModBus Device Importer - LABDocumento11 páginasD1 - ModBus Device Importer - LABGonzo MelaoAún no hay calificaciones

- Manual Hand Drill: Mini - Project - CADDocumento34 páginasManual Hand Drill: Mini - Project - CADKengsuen KhooAún no hay calificaciones

- ZXG10 B8018 (V1.00) In-Door Base Transceiver Station Technical ManualDocumento128 páginasZXG10 B8018 (V1.00) In-Door Base Transceiver Station Technical ManualPrashant MaraAún no hay calificaciones

- HENRY, ET AL (2017) QR CodeDocumento6 páginasHENRY, ET AL (2017) QR CodeMiki AntonAún no hay calificaciones

- Spi FlashDocumento17 páginasSpi FlashmikhaccAún no hay calificaciones

- Catalogo Mass Parts - Accesorios Final - 2017Documento50 páginasCatalogo Mass Parts - Accesorios Final - 2017Carlos Reconco100% (1)

- LG Ht303su Ht353sd SM (ET)Documento81 páginasLG Ht303su Ht353sd SM (ET)domi56Aún no hay calificaciones

- Electric Machines and Drives - Ned MohanDocumento3 páginasElectric Machines and Drives - Ned MohanNaveed Iqbal0% (4)

- Social Media CompetencyDocumento2 páginasSocial Media CompetencyNoah OkitoiAún no hay calificaciones

- Intergrative Programming and Technology 1 QUIZ 2Documento10 páginasIntergrative Programming and Technology 1 QUIZ 2julius obregonAún no hay calificaciones

- Chapter 3-Section 3.2-Cylinder BlockDocumento46 páginasChapter 3-Section 3.2-Cylinder BlockNikkikumar MaisuriyaAún no hay calificaciones

- Cisco Configure Cisco Meeting Server and CUCMDocumento11 páginasCisco Configure Cisco Meeting Server and CUCMandreicainAún no hay calificaciones

- Basic of SoundDocumento54 páginasBasic of SoundRoslina Jaafar75% (4)

- UZZ32 Suspension Codes PDFDocumento32 páginasUZZ32 Suspension Codes PDFAdel Sta MariaAún no hay calificaciones

- Apachehvac: Training Notes - Part 1Documento31 páginasApachehvac: Training Notes - Part 1joe1256100% (1)

- Caterpillar C15 Engine SpecsDocumento5 páginasCaterpillar C15 Engine SpecsDesta 77Aún no hay calificaciones

- Zepto Product Teardown - Likhita ParasuDocumento6 páginasZepto Product Teardown - Likhita ParasuVikas DeshmaneAún no hay calificaciones

- Ubuntu+Server+CLI+pro+tips+ 18X 06.01.20Documento2 páginasUbuntu+Server+CLI+pro+tips+ 18X 06.01.20donna.nix100% (1)

- Assignment On LifiDocumento19 páginasAssignment On LifiMushir BakshAún no hay calificaciones

- User Manual 26829Documento51 páginasUser Manual 26829Héctor vercherAún no hay calificaciones

- Rotomixx: Cost Effective and Reliable Total Stainless Batch MixersDocumento2 páginasRotomixx: Cost Effective and Reliable Total Stainless Batch MixersYusuf DabhiyaAún no hay calificaciones

- How To Set Up Inter Company Stock Transfer PDFDocumento13 páginasHow To Set Up Inter Company Stock Transfer PDFUfuk DoğanAún no hay calificaciones

- JSON Data Modeling: Matthew D. Groves, @mgrovesDocumento56 páginasJSON Data Modeling: Matthew D. Groves, @mgrovesGorzilloAún no hay calificaciones

- FMEADocumento12 páginasFMEAboyetAún no hay calificaciones