Documentos de Académico

Documentos de Profesional

Documentos de Cultura

JairoInforme Practica 4

Cargado por

Odioso Fabian MendezDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

JairoInforme Practica 4

Cargado por

Odioso Fabian MendezCopyright:

Formatos disponibles

1

Compuertas CMOS (Mayo 2009)

Laura Carrascal cdigo 260968, Jairo Sacipa cdigo 261050, y Jaime Pea cdigo: 260909

Abstract Through the development of the lab practice No. 4 of techniques of integration we characterized three gates (nand, nor and transmission gate) based on transistors MOS with the I.C CD4007. The first thing that we did was see the degradation of the logic states of the N-MOS transistor and the P-MOS transistor. After that we constructed the transmission gate and we observed that the behavior of this gate is much better that the behavior of one N-mos or P-mos transistor alone. Finally we measured the power that dissipates the different kind of gates in the static configuration and the dynamic configuration.

Index Terms N-MOS transistor, P-MOS Transistor, Transmission Gate, NAND Gate, NOR Gate, Static Power and Dynamic Power of a gate.

I.

II. TEORA CMOS COMPLEMENTARIO Una compuerta esttica CMOS es una combinacin de dos redes, llamadas la red Pull-up (PUN) y la red de Pull-down (PDN) que se pueden ver en la figura 1. La figura muestra una compuerta lgica genrica de N entradas donde todas las entradas estn distribuidas en ambas redes. La funcin de la PUN es proveer una conexin entre la salida y Vdd en cualquier momento que la sala de la compuerta lgica represente un uno (1) (de acuerdo con las entradas). Similarmente, la funcin de la red PDN es conectar la salida con Vss cuando la salida de la compuerta represente un cero lgico. La PUN y la PDN son construidas de tal forma que una y solo una de las redes conduzca en un estado estacionario. De esta forma, una vez el transiente se ha estabilizado, un camino siempre existir entre Vdd y la salida F, con una salida en alto o alternativamente, entre Vss y F para una salida en bajo.

INTRODUCCIN

En la practica pasada estudibamos el comportamiento de un simple circuito inversor construido a base de la tecnologa CMOS, ahora con el desarrollo de esta practica discutiremos un poco mediante pruebas de laboratorio el comportamiento de algunas compuertas en especifico como son las NAND , NOR y de transmisin. Estas compuertas son los circuitos ms representativos de lo que se conoce como lgica combi nacional. Tales compuertas tienen la propiedad que en cualquier punto del tiempo, la salida del circuito esta relacionada con la corriente de entrada de la seales de entrada por alguna expresin booleana. Como pasaba con el inversor, los parmetros comunes para el diseo de estas compuertas son el rea, la velocidad, la energa consumida y la potencia disipada. Adicionalmente a estos parmetros, el que las compuerta sean robustas e inmunes al ruido son consideraciones importantes a tener en cuenta. El estilo lgico mas usado para la implementacin de las compuertas es el CMOS complementario esttico, el cual es una extensin del inversor CMOS a mltiples entradas. La principal ventaja de la estructura CMOS es la inmunidad al ruido, buen desempeo y bajo consumo de potencia.

Figura 1. Compuerta de lgica complementaria. En la construccin de las redes PDN y PUN, deben tenerse en cuenta las siguientes observaciones: y Un transistor puede ser pensado como un switch controlado por una seal de puerta. Un switch Nmos esta encendido cuando la seal de control es un

2 estado alto y esta apagado cuando la seal de control es un estado bajo. Un transistor Pmos acta inversamente al comportamiento del Nmos. Una red PDN se construye usando dispositivos Nmos, mientras una red PUN se construye con dispositivos Pmos. La razn principal para esta escogencia es que los transistores Nmos producen ceros fuertes y los transistores Pmos producen unos fuertes.

El transistor MOS de canal P conectado en la configuracin de la figura 5 funciona como compuerta de transmisin. Su funcionamiento es similar a la compuerta de transmisin NMOS, excepto que la lgica que maneja para entrar en conduccin es inversa, es decir que la tensin en la compuerta (VG) debe ser negativa para encender el transistor, en este caso la seal aplicada corresponde a un 0 lgico.

Figura 2. Respuesta de los transistores PMOS y NMOS ante la entrada de un cero.

Figura 5. Compuerta de Transmisin PMOS Compuerta de transmisin CMOS Esta compuerta agrupa algunas caractersticas de las compuertas de transmisin NMOS y PMOS. En la figura 6(a) se ilustra el circuito de esta compuerta, observe que esta compuerta contiene un transistor NMOS, un PMOS y un Inversor.

Figura 3. Respuesta de los transistores PMOS y NMOS ante la entrada de un uno.

Compuerta de Transmisin CMOS La compuerta de transmisin es un dispositivo utilizado como interruptor controlado por tensin. Generalmente se emplean transistores para cumplir la funcin de interrupcin y existen compuertas en tecnologa NMOS, PMOS y CMOS. Compuerta de transmisin NMOS La compuerta NMOS corresponde a un transistor MOS de canal N conectado en la configuracin que se muestra en la figura 4. En la figura se observa que la fuente se encuentra conectada a tierra. Este transistor puede conducir corriente en cualquiera de sus dos direcciones (Vsal/Vent o viceversa) cuando la tensin en la compuerta (VG) supere la tensin de umbral para encenderlo, es decir, aplicando un 1 lgico.

Figura 6. Compuerta de transmisin CMOS El inversor es empleado para tener una sola seal de control para encender o apagar los transistores. Cuando VC se encuentra en bajo (0 lgico) el transistor NMOS se apaga al igual que el transistor PMOS, anlogamente, si la tensin VC cambia alto (1 lgico), los transistores se encenderan. Existe otra representacin de esta compuerta de transmisin, la cual se ilustra en la figura 6 (b) en donde la compuerta no tiene incluido el inversor y las seales de control son C y C'. Otra opcin de representacin se muestra en la figura 6 (c).

Figura 4. Compuerta de Transmisin NMOS Compuerta de transmisin PMOS

3 COMPUERTA NAND Figura 8. Compuerta NAND a base de transistores Cmos.

COMPUERTA NOR

Figura 7. Smbolo de la funcin lgica NAND. a) Contactos, b) Normalizado y c) No normalizado La puerta lgica NAND, realiza la operacin de producto lgico negado. En la figura 7 pueden observarse sus smbolos. La ecuacin caracterstica que describe el comportamiento de la puerta NAND es: Figura 9. Smbolo de la funcin lgica NOR. a) Contactos, b) Normalizado y c) No normalizado La compuerta NOR, realiza la operacin de suma lgica negada. En la figura 9 se pueden observarse sus smbolos. La ecuacin caracterstica que describe el comportamiento de la puerta NOR es:

Su tabla de verdad es la siguiente: Tabla de verdad puerta NAND Entrada A Entrada B Salida 0 0 1 1 0 1 0 1 1 1 1 0 Su tabla de verdad es la siguiente: Tabla de verdad puerta NOR Entrada A Entrada B Salida 0 0 1 1 0 1 0 1 1 0 0 0

Podemos definir la compuerta NAND como aquella que proporciona a su salida un 0 lgico nicamente cuando todas sus entradas estn a 1.

Podemos definir la puerta NOR como aquella que proporciona a su salida un 1 lgico slo cuando todas sus entradas estn a 0. La puerta lgica NOR constituye un conjunto completo de operadores.

También podría gustarte

- Net LogoDocumento25 páginasNet LogoOdioso Fabian MendezAún no hay calificaciones

- 100 Cuentos para Pensar - Jorge BucayDocumento21 páginas100 Cuentos para Pensar - Jorge BucayMilton MaldonadoAún no hay calificaciones

- Comic - Los Muertos de Cristo & Juanito WatiosDocumento76 páginasComic - Los Muertos de Cristo & Juanito WatiosPene PoserAún no hay calificaciones

- Occams Razor 04 01Documento64 páginasOccams Razor 04 01Odioso Fabian MendezAún no hay calificaciones

- Occams Razor 01 03Documento31 páginasOccams Razor 01 03Odioso Fabian MendezAún no hay calificaciones

- Actividad Ficha 2Documento2 páginasActividad Ficha 2Sandra Navarro AguadoAún no hay calificaciones

- Diversidad cultural y respeto mutuoDocumento3 páginasDiversidad cultural y respeto mutuokevin I. GuillenAún no hay calificaciones

- Informe planimétrico inspección ocularDocumento10 páginasInforme planimétrico inspección ocularangelar05Aún no hay calificaciones

- Libreto - La Flauta Mágica (MOZART)Documento53 páginasLibreto - La Flauta Mágica (MOZART)Elizabeth CottetAún no hay calificaciones

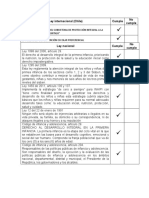

- Lista de Cotejo LeyesDocumento2 páginasLista de Cotejo Leyesleidy cetinaAún no hay calificaciones

- Neumonía en niño de 9 añosDocumento20 páginasNeumonía en niño de 9 añosGuayo1976Aún no hay calificaciones

- Examenes Salud PDFDocumento32 páginasExamenes Salud PDFDiego RoccaAún no hay calificaciones

- Actividad de Aprendizaje 2Documento2 páginasActividad de Aprendizaje 2mayi082003Aún no hay calificaciones

- Taller deontología profesionalesDocumento5 páginasTaller deontología profesionalesEstefania Giraldo RamirezAún no hay calificaciones

- Orígenes Plástica UChile PDFDocumento10 páginasOrígenes Plástica UChile PDFAle NinAún no hay calificaciones

- Lectura - #17Documento4 páginasLectura - #17MarcoVillacortaAún no hay calificaciones

- Triptico Bullying ProfesoresDocumento2 páginasTriptico Bullying ProfesoresBeetzy Navarro100% (1)

- El Misterio de La Bruja Aullante - OneShot Del Sot Equus (Final)Documento14 páginasEl Misterio de La Bruja Aullante - OneShot Del Sot Equus (Final)Joan P. PereiraAún no hay calificaciones

- Fisica y Matematicas, Hector Rago-2Documento23 páginasFisica y Matematicas, Hector Rago-2BEGRAIJPAún no hay calificaciones

- Modelo Lambda-CDM - Wikipedia, La Enciclopedia LibreDocumento7 páginasModelo Lambda-CDM - Wikipedia, La Enciclopedia LibreRXAún no hay calificaciones

- Sistematizacion de ExperienciasDocumento10 páginasSistematizacion de Experienciasjuan david beltranAún no hay calificaciones

- Fallo RiosDocumento2 páginasFallo RiosagAún no hay calificaciones

- El Ojo de La LunaDocumento3 páginasEl Ojo de La LunaJose Figueroa RamírezAún no hay calificaciones

- Adinistracion Vitamina K - A RNDocumento3 páginasAdinistracion Vitamina K - A RNroy rosarioAún no hay calificaciones

- Romero, José Luis - La Edad Media. Guía DidácticaDocumento5 páginasRomero, José Luis - La Edad Media. Guía DidácticaVerónica Díaz PereyroAún no hay calificaciones

- Avance Grupo #4 - Trastornos DisociativosDocumento8 páginasAvance Grupo #4 - Trastornos DisociativosfranciaruizraAún no hay calificaciones

- Norma 34.1 CastellanoDocumento51 páginasNorma 34.1 CastellanoEskalera RealAún no hay calificaciones

- Denuncia TribunalesDocumento2 páginasDenuncia TribunalesLuis CarutoAún no hay calificaciones

- Que Analíticas Se Piden en Un Infarto Agudo de MiocardioDocumento5 páginasQue Analíticas Se Piden en Un Infarto Agudo de MiocardioCrisdavi OrtegaAún no hay calificaciones

- El Partido Socialista Ecuatoriano, 1926-1931Documento41 páginasEl Partido Socialista Ecuatoriano, 1926-1931Steve SocagAún no hay calificaciones

- Sistemas de Alimentacion Motores Diesel RenaultDocumento86 páginasSistemas de Alimentacion Motores Diesel Renaultapi-3806781100% (2)

- Copia de TRAUMA DE TORAXDocumento5 páginasCopia de TRAUMA DE TORAXTatiana OrtizAún no hay calificaciones

- Prueba 8º MCMDocumento3 páginasPrueba 8º MCMSebastianHormazabalAún no hay calificaciones

- Poemas LagerkvistDocumento6 páginasPoemas LagerkvistDavid JaramilloAún no hay calificaciones

- Objetivos y Alcance de AuditoriaDocumento18 páginasObjetivos y Alcance de AuditoriacristianAún no hay calificaciones