Documentos de Académico

Documentos de Profesional

Documentos de Cultura

LAB 5 - Análisis y Diseño de Circuitos Secuenciales Modelos Tipo Moore y Tipo Mealy (Prof. Casimiro)

Cargado por

Elmer525Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

LAB 5 - Análisis y Diseño de Circuitos Secuenciales Modelos Tipo Moore y Tipo Mealy (Prof. Casimiro)

Cargado por

Elmer525Copyright:

Formatos disponibles

UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS

FACULTAD DE INGENIERIA ELECTRONICA

LABORATORIO DE CIRCUITOS DIGITALES II

LAB. 5 : Anlisis y Diseo de Circuitos Secuenciales: Modelos tipo Moore y tipo Mealy

Profesor: Ing. Oscar Casimiro Pariasca

I. OBJETIVO:

1. Verificar y/o disear circuitos secuenciales tipo Moore y tipo Mealy.

II. MATERIALES y EQUIPO :

- Protoboard, cables de conexin.

- CI TTL: 74LS74, 74LS76, 74LS109, 74LS164, 74LS161, 74LS374, 74LS375, otros.

- Resistencias : 120 OHM, Watt; Leds. Displays, etc

- Fuente C.C. +5 voltios; VOM; ORC; Generador de Pulsos.

III. CUESTIONARIO PREVIO

1. Cual es la diferencia entre circuitos secuenciales del tipo Moore y del tipo Mealy. Explique.

2. Disear el sistema secuencial , utilizando flip flop tipo D y tipo JK, correspondiente al diagrama de estados

mostrado

x1=0

3.

4.

5.

6.

Elabore una tabla de estados mnimos para un circuito secuencial tipo Moore de entrada y salida nicas que

generan una salida de 1 si en la secuencia de entrada detecta patrones 110 101 . Deben detectarse

secuencias sobrepuestas.

Repita el problema anterior para un circuito secuencial tipo Mealy.

Disear un circuito secuencial utilizando flip flops J-K que tiene una entrada w y una salida z. La mquina

es un detector de secuencias que produce z = 1 cuando los dos valores previos de w eran 00 11 ; de lo

contrario, z = 0.

Para los siguientes circuitos secuenciales: disear los circuitos secuenciales si fuera el caso deducir las

ecuaciones caractersticas, la tabla y el diagrama de estado de cada circuito. Mostrar los diagramas de

tiempo correspondientes para 10 pulsos de reloj:

Ejemplo 1 de Diseo.

Definicin del problema: Disear un circuito secuencial utilizando Flip Flops, que implemente el

siguiente diagrama de transicin de estados :

a)

Obtenga la tabla de estados, las ecuaciones de entradas, salida y de estados. A partir de la tabla, obtenga

funciones simplificadas.

Utilize para su diseo:

a) Flips Flops tipo JK

b) Flip Flops tipo D

Ejemplo 2 de Diseo.

Definicin del problema: Disear, utilizando flip flops tipo D el circuito secuencial (sncrono) detector de

secuencia de tres unos consecutivos (111), de acuerdo al diagrama de seales mostrado:

Ing. Oscar Casimiro Pariasca

Sem. 2011- 0

Indique si es una mquina de Moore o

de Mealy.

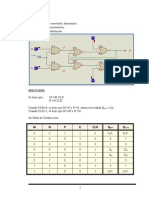

Ejemplo 3 de Diseo.

Definicin del problema: Para el circuito secuencial tipo Moore, mostrado en la figura, deducir las

ecuaciones caractersticas, la tabla y el diagrama de estado del circuito. Utilize Flip-flop tipo J-K (74LS76 y/o

otros adicionales.

Ejemplo 4 de Diseo.

Definicin del problema: Para el circuito secuencial tipo Mealy, mostrado en la figura, deducir las

ecuaciones caractersticas, la tabla y el diagrama de estado del circuito. Utilize Flip-flop tipo J-K (74LS74 y/o

otros adicionales.

IV. PARTE EXPERIMENTAL:

1. Implementar los circuitos del cuestionario previo. Presentar y deducir las ecuaciones caractersticas, la

tabla, el diagrama de estado, el diagrama de tiempos, etc.

V. CUESTIONARIO FINAL:

1.

Analize y explique el funcionamiento de los circuitos de la parte experimental. Presentar el diagrama de

tiempos de los circuitos del experimento. Presentar las tablas de transicin, diagramas de estados, etc.

Indique a que tipo de circuito secuencial corresponde cada uno de los que ha analizado.

2.

Se puede utilizar un tipo de flip-flop para implementar otros tipos de flip-flop. Dibujar las tablas de estado

para las siguientes preguntas. Debe mostrar la entrada (D), las salidas (Q, Q+) y cada entrada al flip-flop en

su tabla de estado.

a) Utilize flip-flop J-K para implementar un flip-flop tipo D

b) Utilize flip-flop T para implementar un flip-flop tipo D

3. Dada una seal de reloj de 100 MHz, disee un circuito usando flip-flops tipo D para generar seales de reloj

de 50 y 25 MHz. Trace un diagrama de tiempo para las tres seales de reloj, suponiendo retrasos razonables.

4. Disear un sistema Mealy con una entrada X y una salida Z de tal forma que Z = 1 si X es actualmente 1 y

tambin ha sido 1 en los dos pulsos de clock anteriores.

5. Disear un sistema Moore con una entrada X y una salida Z que ser 1 si en la entrada ocurrieron tres 0

consecutivos ms recientemente que tres 1 consecutivos.

Conclusiones.

Ing. Oscar Casimiro Pariasca

Sem. 2011- 0

También podría gustarte

- LAB 2 - Latch Flip Flop 2019-1Documento4 páginasLAB 2 - Latch Flip Flop 2019-1Migvel Angel Soncco XDAún no hay calificaciones

- LAB 6 - Análisis y Síntesis de Circuitos Lógicos Secuenciales (Prof. Casimiro)Documento3 páginasLAB 6 - Análisis y Síntesis de Circuitos Lógicos Secuenciales (Prof. Casimiro)Elmer525Aún no hay calificaciones

- Cuestionario DFTDocumento7 páginasCuestionario DFTPato RiveraAún no hay calificaciones

- Informe Final 3 Sistemas DigitalesDocumento24 páginasInforme Final 3 Sistemas Digitalestania tarazonaAún no hay calificaciones

- Final 2 Comunicacion AnalogicaDocumento23 páginasFinal 2 Comunicacion AnalogicaCésar Guerrero CorneAún no hay calificaciones

- Osciladores DiscretosDocumento13 páginasOsciladores DiscretosXavier PalaciosAún no hay calificaciones

- Ej 3-Labo1 PDSDocumento8 páginasEj 3-Labo1 PDSTadokaDragneelAún no hay calificaciones

- Señales DiscretasDocumento7 páginasSeñales DiscretasRaissaPazVasquezAún no hay calificaciones

- Prob Unid 1Documento6 páginasProb Unid 1Gregory PinoAún no hay calificaciones

- GUIA-Laboratorio N°1 Antenas y Medios de Transmisión FIEE-UNMSMDocumento11 páginasGUIA-Laboratorio N°1 Antenas y Medios de Transmisión FIEE-UNMSMAlexander SolanoAún no hay calificaciones

- Convertidores DAC ADCDocumento3 páginasConvertidores DAC ADCCristihan Criollo100% (1)

- Lab05 PdsDocumento16 páginasLab05 PdsHilario SoteloAún no hay calificaciones

- Modulación Shift Keying (PSK)Documento15 páginasModulación Shift Keying (PSK)fabrizzioAún no hay calificaciones

- Principios de Sistemas de ComunicacionesDocumento100 páginasPrincipios de Sistemas de Comunicacionespoly8mb3109100% (1)

- MatlabTeleco - Mauricio Ruiz PDFDocumento7 páginasMatlabTeleco - Mauricio Ruiz PDFD Saul P Sandoval0% (1)

- ModuladoresAMFMDocumento10 páginasModuladoresAMFMHector MejiasAún no hay calificaciones

- 3.4 Introduccion A Control Digital PDFDocumento80 páginas3.4 Introduccion A Control Digital PDFJohann Smith Aranda RamosAún no hay calificaciones

- Taller 1 Diseño Enlace de MicroondasDocumento14 páginasTaller 1 Diseño Enlace de MicroondasmiltonAún no hay calificaciones

- Codigos de MatlabDocumento12 páginasCodigos de MatlabMICHELLE YUNORVI LUNA ALAMAAún no hay calificaciones

- Matlab PamDocumento224 páginasMatlab PamHernandez Sayuranys100% (1)

- Practica de Potencia 1Documento7 páginasPractica de Potencia 1Orlando Bustamante FernandezAún no hay calificaciones

- Control DigitalDocumento10 páginasControl DigitalYoset Fran Mamani AyalaAún no hay calificaciones

- Aporte 2 Proyecto Final de Procesamiento Digital de SenalesDocumento4 páginasAporte 2 Proyecto Final de Procesamiento Digital de SenalesMiguel Angel Garcia CanoAún no hay calificaciones

- Siste Digit Previo 3Documento6 páginasSiste Digit Previo 3DiegoAún no hay calificaciones

- Señales analógicas y discretas en MATLABDocumento9 páginasSeñales analógicas y discretas en MATLABalvaroczAún no hay calificaciones

- Informefinal 5 Sistemas Digitales Ee635Documento15 páginasInformefinal 5 Sistemas Digitales Ee635juan ramos ruizAún no hay calificaciones

- Funciones de Transferencia (MATLAB)Documento27 páginasFunciones de Transferencia (MATLAB)GABI DANIELA LOPEZ PEREZAún no hay calificaciones

- Labo2 Mayorgahilarioivan1713220193Documento8 páginasLabo2 Mayorgahilarioivan1713220193Iván Fernando Mayorga HilarioAún no hay calificaciones

- Diseño Del Convertidor Inversor CDDocumento25 páginasDiseño Del Convertidor Inversor CDDavid SanchezAún no hay calificaciones

- Exs Finales Sist Radio y TVDocumento7 páginasExs Finales Sist Radio y TVVictorAún no hay calificaciones

- Primera Practica Sensores Parte IDocumento1 páginaPrimera Practica Sensores Parte IRaúl QCAún no hay calificaciones

- Tutorial 2 - RuidoDocumento15 páginasTutorial 2 - RuidoMorena G. Lopez Vargas100% (1)

- Carta de Smith EjerciciosDocumento28 páginasCarta de Smith EjerciciosFidel Andres Vargas CallejasAún no hay calificaciones

- Examen Parcial-MicroCONTROLADORES-2020BDocumento2 páginasExamen Parcial-MicroCONTROLADORES-2020BTRUJILLO ZULUETA RENATO ANGELOAún no hay calificaciones

- Antenas FractalesDocumento19 páginasAntenas FractalesOSORIO GALVEZ JORGE MIGUELAún no hay calificaciones

- Propiedades Basicas de Los SistemasDocumento3 páginasPropiedades Basicas de Los SistemasAntonioRamosAún no hay calificaciones

- 2) Introduccion-Control-DigitalDocumento16 páginas2) Introduccion-Control-DigitalManuelMartinezAún no hay calificaciones

- 4.5 DirectividadDocumento13 páginas4.5 DirectividadDgh Rdd100% (1)

- Untitled2 PDFDocumento77 páginasUntitled2 PDFluisgonza84Aún no hay calificaciones

- Guía de ondas microondas y adaptación de impedanciasDocumento43 páginasGuía de ondas microondas y adaptación de impedanciasArmando CajahuaringaAún no hay calificaciones

- Antena BocinaDocumento10 páginasAntena BocinaAlexander GDAún no hay calificaciones

- Proyecto Integrador AutomatizaciónDocumento44 páginasProyecto Integrador AutomatizaciónWilmer Andres Escalante MancillaAún no hay calificaciones

- Clase CMOS Y TTLDocumento66 páginasClase CMOS Y TTLerteduAún no hay calificaciones

- Diseño de Convertidores DC-DC Tipo Buck Típicos y Controlado para Un Mejor Entendimiento en Cuanto A Su Funcionamiento.Documento12 páginasDiseño de Convertidores DC-DC Tipo Buck Típicos y Controlado para Un Mejor Entendimiento en Cuanto A Su Funcionamiento.hhryc7100% (3)

- Lab Com Digitales Lab3Documento30 páginasLab Com Digitales Lab3Cesar MixAún no hay calificaciones

- Laboratorio 1Documento10 páginasLaboratorio 1Gustavo Dioses SiguasAún no hay calificaciones

- HETERODINAJEDocumento2 páginasHETERODINAJEAlejandro MoscosoAún no hay calificaciones

- Informe Previo 5Documento13 páginasInforme Previo 5Felipe SanchezAún no hay calificaciones

- CuestionarioDocumento10 páginasCuestionario25 Olmedo RenatoAún no hay calificaciones

- Examen Final de PDSDocumento1 páginaExamen Final de PDSacajahuaringaAún no hay calificaciones

- Examen Parcial 2017-1 - DISEÑO DIGITAL - FIEE - UNMSMDocumento3 páginasExamen Parcial 2017-1 - DISEÑO DIGITAL - FIEE - UNMSMElmer525Aún no hay calificaciones

- LAB 5 - Cir Secuenc - Moore y Mealy - 2012-1Documento2 páginasLAB 5 - Cir Secuenc - Moore y Mealy - 2012-1Carlos Enrique Falcon ZapataAún no hay calificaciones

- LAB 5 - Cir Secuenc - Moore y Mealy - 2013-2Documento3 páginasLAB 5 - Cir Secuenc - Moore y Mealy - 2013-2juanjo20_11Aún no hay calificaciones

- LAB 7-2020-II - CIRCUITOS DIGITALES II - Análisis y Diseño de Circuitos Secuenciales - Modelo Tipo Moore y Modelo Tipo MealyDocumento2 páginasLAB 7-2020-II - CIRCUITOS DIGITALES II - Análisis y Diseño de Circuitos Secuenciales - Modelo Tipo Moore y Modelo Tipo MealyLuis Misiyauri GutiérrezAún no hay calificaciones

- LAB 6 - Cir Secuenc - Moore y Mealy - 2018-1Documento2 páginasLAB 6 - Cir Secuenc - Moore y Mealy - 2018-1jorgeAún no hay calificaciones

- LAB 6 - Cir Secuenc - Moore y Mealy - 2016-1Documento2 páginasLAB 6 - Cir Secuenc - Moore y Mealy - 2016-1Victor Angel Yurivilca LazoAún no hay calificaciones

- LAB 6 - Analisis Sintesis Circ Secuenciales - 2013-2Documento3 páginasLAB 6 - Analisis Sintesis Circ Secuenciales - 2013-2juanjo20_11Aún no hay calificaciones

- Laboratorio4 FlipFlops CDIIDocumento3 páginasLaboratorio4 FlipFlops CDIIespinozaAún no hay calificaciones

- Lab 2-Circuitos Latch y Flip FlopDocumento3 páginasLab 2-Circuitos Latch y Flip Flopjuanjo20_11Aún no hay calificaciones

- Tasas Tarifas Cts PDFDocumento1 páginaTasas Tarifas Cts PDFElmer525Aún no hay calificaciones

- Control de Velocidad de Un Motor DC Con DacDocumento9 páginasControl de Velocidad de Un Motor DC Con DacElmer525100% (1)

- MATPEL 2 IdentificaciónDocumento1 páginaMATPEL 2 IdentificaciónElmer525Aún no hay calificaciones

- Reconocimiento de Materiales Peligrosos en 5 MinutosDocumento1 páginaReconocimiento de Materiales Peligrosos en 5 MinutosElmer525Aún no hay calificaciones

- Tema1 Circuitos Temporizadores 74121 74122 74123Documento21 páginasTema1 Circuitos Temporizadores 74121 74122 74123Julio David Vilca PizarroAún no hay calificaciones

- Examen Parcial 2017-1 - DISEÑO DIGITAL - FIEE - UNMSMDocumento3 páginasExamen Parcial 2017-1 - DISEÑO DIGITAL - FIEE - UNMSMElmer525Aún no hay calificaciones

- Estudio de La Tecnología de Comunicación Por Radiofrecuencia RFID y Su ImplementaciónDocumento110 páginasEstudio de La Tecnología de Comunicación Por Radiofrecuencia RFID y Su ImplementaciónElmer525Aún no hay calificaciones

- Laboratorio Calificado N°2 - Viernes 24/05/19 - AdanaqueDocumento2 páginasLaboratorio Calificado N°2 - Viernes 24/05/19 - AdanaqueElmer525Aún no hay calificaciones

- La Tecnologia RFID - HuidobroDocumento10 páginasLa Tecnologia RFID - HuidobroGonzaloAún no hay calificaciones

- Tarea Academica - Simulacion de Sistemas - Upc PDFDocumento4 páginasTarea Academica - Simulacion de Sistemas - Upc PDFElmer525Aún no hay calificaciones

- Archivo 1Documento50 páginasArchivo 1Ivan Hermilio Mera IbarguenAún no hay calificaciones

- Tema 1 - Latch Flip Flop PDFDocumento21 páginasTema 1 - Latch Flip Flop PDFElmer525Aún no hay calificaciones

- Identificación Por Radiofrecuencia Fundamentos y Aplicaciones PDFDocumento10 páginasIdentificación Por Radiofrecuencia Fundamentos y Aplicaciones PDFedgardoboieroAún no hay calificaciones

- Horarios Por Ciclos 2018 0 Electronica Vi X 06ene18Documento5 páginasHorarios Por Ciclos 2018 0 Electronica Vi X 06ene18LuceroMilagrosCubaMirandaAún no hay calificaciones

- Informe #1 - Lab. Introducción A Las TelecomunicacionesDocumento22 páginasInforme #1 - Lab. Introducción A Las TelecomunicacionesElmer525Aún no hay calificaciones

- Sistemas Digitales Problemas 2 PDFDocumento27 páginasSistemas Digitales Problemas 2 PDFElmer525Aún no hay calificaciones

- C02 PDFDocumento37 páginasC02 PDFElmer525Aún no hay calificaciones

- 2da Tarea de Circuitos Digitales 2 (2015-2)Documento8 páginas2da Tarea de Circuitos Digitales 2 (2015-2)Elmer5250% (1)

- 1P SistCont I ExPa 2015-2Documento2 páginas1P SistCont I ExPa 2015-2Elmer525Aún no hay calificaciones

- Control AutomaticoDocumento34 páginasControl AutomaticoJonathan Jara MontecinosAún no hay calificaciones

- Apuntes Medios de Transmisi NDocumento19 páginasApuntes Medios de Transmisi NAnita GonzálezAún no hay calificaciones

- Tarea Domiciliaria de Circuitos Digitales IIDocumento9 páginasTarea Domiciliaria de Circuitos Digitales IIDaniel DzmAún no hay calificaciones

- Diseño Avanzado de Controladores SISO: Parte 4Documento24 páginasDiseño Avanzado de Controladores SISO: Parte 4Myriam Raquel Gaete GaeteAún no hay calificaciones

- Resonancia en ParaleloDocumento11 páginasResonancia en ParaleloElmer525Aún no hay calificaciones

- 2da Tarea Mestas 2016-2Documento11 páginas2da Tarea Mestas 2016-2Elmer525Aún no hay calificaciones

- FisicaDocumento26 páginasFisicawalterAún no hay calificaciones

- Mediciones Electronicas - Mestas 2016-2Documento14 páginasMediciones Electronicas - Mestas 2016-2Elmer525Aún no hay calificaciones

- Modelos de Organización Del Sector ElectricoDocumento5 páginasModelos de Organización Del Sector ElectricoElmer525Aún no hay calificaciones

- A5Documento46 páginasA5edsg29Aún no hay calificaciones

- Los Microcontroladores en La IndustriaDocumento5 páginasLos Microcontroladores en La IndustriaElmer525Aún no hay calificaciones

- Proyecto BriquetaDocumento25 páginasProyecto BriquetaMakarena Paz Fernanda Barría NavarroAún no hay calificaciones

- Minicargadores: Características y aplicacionesDocumento25 páginasMinicargadores: Características y aplicacionesRoger UrianAún no hay calificaciones

- Taller AlgoritmosDocumento1 páginaTaller Algoritmosjaen hannier herreño rosasAún no hay calificaciones

- Zapatas y Losas de CimentaciónDocumento5 páginasZapatas y Losas de Cimentaciónoliver ponce ramosAún no hay calificaciones

- El Microscopio Óptico Partes e HistoriaDocumento34 páginasEl Microscopio Óptico Partes e HistoriaVictoria Cevallos BonillaAún no hay calificaciones

- EC-062 Pantoscopio PDFDocumento1 páginaEC-062 Pantoscopio PDFRichard PerezAún no hay calificaciones

- Contenido Teóricodel Curso STAFDocumento397 páginasContenido Teóricodel Curso STAFGustavo MesaAún no hay calificaciones

- Plan izaje grúa móvilDocumento3 páginasPlan izaje grúa móvilWilber Gonzalez Jimenez100% (3)

- 03 Calculo de Tuberia de Alimentacion A CisternaDocumento35 páginas03 Calculo de Tuberia de Alimentacion A CisternaFavio Cueva100% (3)

- Procedimiento HollidayDocumento12 páginasProcedimiento HollidayOmar VilchezAún no hay calificaciones

- Presentacion CRMDocumento34 páginasPresentacion CRMMarketing y servicios100% (3)

- Temario 1 PrimariaDocumento26 páginasTemario 1 PrimariaLuis Carlos CamposAún no hay calificaciones

- Utilización de Dinámicas Grupales en El Taller de Inserción LaboralDocumento5 páginasUtilización de Dinámicas Grupales en El Taller de Inserción LaboralEmy Mendoza AlcalaAún no hay calificaciones

- Laboratorio N°2 Alcantarillado PluvialDocumento32 páginasLaboratorio N°2 Alcantarillado PluvialAnaAún no hay calificaciones

- Anticongelante PDFDocumento3 páginasAnticongelante PDFjuanmanuel_4615958Aún no hay calificaciones

- COMPLETO BiopolimerosDocumento204 páginasCOMPLETO BiopolimeroschryseduardoleonAún no hay calificaciones

- Encuesta CurricularDocumento8 páginasEncuesta CurricularsegueavantiAún no hay calificaciones

- Energia RenovableDocumento16 páginasEnergia RenovableandresAún no hay calificaciones

- Tema - 5 - Diseño de Maquinas de Estados Finitos - 2020-2021Documento43 páginasTema - 5 - Diseño de Maquinas de Estados Finitos - 2020-2021eros.llorensAún no hay calificaciones

- Taller - Ing. CivilDocumento4 páginasTaller - Ing. CivilVictor Manuel Rodriguez Andaur0% (1)

- Evp3 OkDocumento2 páginasEvp3 OkEdgarContreras75% (12)

- Examen Unidad 2 EmprendimientoDocumento7 páginasExamen Unidad 2 Emprendimientojulian5ruiz-10100% (2)

- Equipos para El Procesamiento Del ArrozDocumento20 páginasEquipos para El Procesamiento Del ArrozRaúl Rafael Huaman TincoAún no hay calificaciones

- Informe de Practicas Pre P - 2017Documento57 páginasInforme de Practicas Pre P - 2017Huberth Ñahuinmallma92% (26)

- CM20150709 23195 20742Documento71 páginasCM20150709 23195 20742Mark LMAún no hay calificaciones

- Presión hidrostática y manómetrosDocumento6 páginasPresión hidrostática y manómetrosJulian SeguraAún no hay calificaciones

- Gestión proyecto 9 puntosDocumento7 páginasGestión proyecto 9 puntosjulian5ruiz-1067% (3)

- Proyecto de Creación de Un Campus Intergeneracional en La Universidad de CórdobaDocumento32 páginasProyecto de Creación de Un Campus Intergeneracional en La Universidad de Córdobarb3lagoaAún no hay calificaciones

- Formato de Entrevista EstructuradaDocumento3 páginasFormato de Entrevista EstructuradaJohn Aaron Cortez DamianAún no hay calificaciones

- Manuel Alcaraz González - El Objeto Digital Como Máquina Autónoma de Producción ArtísticaDocumento179 páginasManuel Alcaraz González - El Objeto Digital Como Máquina Autónoma de Producción ArtísticaEllés GuerreroAún no hay calificaciones