Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Preparatorio 9 Digitales

Cargado por

AlexisRobertoVallejoDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Preparatorio 9 Digitales

Cargado por

AlexisRobertoVallejoCopyright:

Formatos disponibles

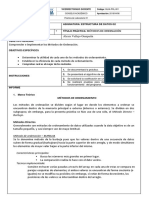

ESCUELA POLITCNICA NACIONAL

FACULTAD DE INGENIERA ELCTRICA Y ELECTRNICA

DEPARTAMENTO DE ELECTRNICA, TELECOMUNICACIONES Y REDES DE LA INFORMACIN

PRCTICA No. 9

DISEO FLIP-FLOPS

OBJETIVOS:

Entender el diseo y funcionamiento de multivibradores biestables, ms conocidos como

flip-flops, as como su utilidad prctica.

TRABAJO PREPARATORIO

I.

Utilizando flip-flops J-K disee un contador asincrnico descendente mdulo 67 que

pueda ser visualizado en displays de nodo comn, y el circuito de borrado manual que

me permita empezar en 0 en cualquier momento.

R22

10k

12

7476

10

16

7476

CLK

K

U5:A

11

14

CLK

U4:B

7

9

15

15

CLK

K

16

10

CLK

12

U4:A

2

4

11

U5:B

7476

14

7476

U6

7

1

2

6

4

5

3

A

B

C

D

BI/RBO

RBI

LT

1

2

13

U12

R8

R9

R10

330

R11

330

R12

330

R13

330

R14

330

13

12

11

10

9

15

14

330

330

7447

U14:A

U11:A

QA

QB

QC

QD

QE

QF

QG

U10:B

12

7411

2

74LS00

AND

7476

12

4

1

CLK

K

7476

U8:A

11

10

16

14

U7:B

7

6

CLK

K

16

15

7476

15

CLK

K

10

U7:A

Q

CLK

K

11

12

U8:B

74LS00

14

7476

U9

7

1

2

6

4

5

3

U14:B

3

4

5

7411

U10:A

A

B

C

D

BI/RBO

RBI

LT

7447

QA

QB

QC

QD

QE

QF

QG

13

12

11

10

9

15

14

R15

R16

R17

330

R18

330

R19

330

R20

330

R21

330

330

330

2

3

1

U15

74LS00

AND

GR2- GRUPO 5 Alexis Vallejo Guaipatn

Pgina 1

ESCUELA POLITCNICA NACIONAL

FACULTAD DE INGENIERA ELCTRICA Y ELECTRNICA

DEPARTAMENTO DE ELECTRNICA, TELECOMUNICACIONES Y REDES DE LA INFORMACIN

II.

Utilizando flip-flops J-K disee un contador asincrnico ascendente mdulo 136 que

pueda ser visualizado en displays de nodo comn, y el circuito de borrado manual que

me permita empezar en 0 en cualquier momento.

R22

10k

7476

7476

CLK

12

10

U2:A

14

11

U1:B

CLK

16

15

CLK

16

10

9

6

15

CLK

12

U1:A

4

1

U13

11

U2:B

7476

14

7476

U3

AND

7

1

2

6

4

5

3

A

B

C

D

BI/RBO

RBI

LT

R1

R2

R3

330

R4

330

R5

330

R6

330

R7

330

13

12

11

10

9

15

14

QA

QB

QC

QD

QE

QF

QG

330

330

7447

7476

7476

10

U5:A

CLK

12

14

11

CLK

16

U4:B

15

CLK

16

15

10

CLK

12

U4:A

11

U5:B

7476

14

7476

U6

7

1

2

6

4

5

3

A

B

C

D

BI/RBO

RBI

LT

U11:A

1

2

13

U12

13

2

1

R8

R9

R10

330

R11

330

R12

330

R13

330

R14

330

13

12

11

10

9

15

14

330

330

7447

U14:A

12

QA

QB

QC

QD

QE

QF

QG

U10:B

12

5

6

7411

4

74LS00

AND

7476

14

12

11

4

1

CLK

K

7476

U8:A

U7:B

10

16

16

15

10

U7:A

Q

CLK

7476

15

CLK

K

11

CLK

12

U8:B

74LS10

14

7476

U9

7

1

2

6

4

5

3

U14:B

3

4

5

7411

U10:A

A

B

C

D

BI/RBO

RBI

LT

7447

QA

QB

QC

QD

QE

QF

QG

13

12

11

10

9

15

14

R15

R16

R17

330

R18

330

R19

330

R20

330

R21

330

330

330

2

3

1

U15

74LS00

AND

GR2- GRUPO 5 Alexis Vallejo Guaipatn

Pgina 2

ESCUELA POLITCNICA NACIONAL

FACULTAD DE INGENIERA ELCTRICA Y ELECTRNICA

DEPARTAMENTO DE ELECTRNICA, TELECOMUNICACIONES Y REDES DE LA INFORMACIN

III.

Disear un contador asincrnico ascendente mdulo 245 utilizando el contador 7490 y

7492 que pueda ser visualizado en displays de nodo comn, y el circuito de borrado

manual que me permita empezar en 0 en cualquier momento.

GR2- GRUPO 5 Alexis Vallejo Guaipatn

Pgina 3

ESCUELA POLITCNICA NACIONAL

FACULTAD DE INGENIERA ELCTRICA Y ELECTRNICA

DEPARTAMENTO DE ELECTRNICA, TELECOMUNICACIONES Y REDES DE LA INFORMACIN

IV.

Disear un contador sincrnico descendente mdulo 36, utilizando flip flop JK que pueda

ser visualizado en displays de nodo comn, y el circuito de borrado manual que me

permita empezar en 0 en cualquier momento.

V.

Realice un circuito digital que permita dividir una seal cuadrada de 25 KHz para obtener

una seal de 5 KHz.

BIBLIOGRAFA:

Sistemas digitales, Ing. Carlos Novillo, EPN

GR2- GRUPO 5 Alexis Vallejo Guaipatn

Pgina 4

ESCUELA POLITCNICA NACIONAL

FACULTAD DE INGENIERA ELCTRICA Y ELECTRNICA

DEPARTAMENTO DE ELECTRNICA, TELECOMUNICACIONES Y REDES DE LA INFORMACIN

GR2- GRUPO 5 Alexis Vallejo Guaipatn

Pgina 5

También podría gustarte

- Introduccion A La Antropologia - C PDFDocumento126 páginasIntroduccion A La Antropologia - C PDFAlexisRobertoVallejo88% (8)

- Manejo Poscosecha de Granos PDFDocumento76 páginasManejo Poscosecha de Granos PDFLuz Marina Vasquez100% (1)

- P6 VallejoAlexisDocumento8 páginasP6 VallejoAlexisAlexisRobertoVallejoAún no hay calificaciones

- Práctica 02 Laboratorio Linux FSODocumento5 páginasPráctica 02 Laboratorio Linux FSOAlexisRobertoVallejoAún no hay calificaciones

- Ética y Dios UPSDocumento24 páginasÉtica y Dios UPSAlexisRobertoVallejoAún no hay calificaciones

- P1 VallejoAlexisDocumento11 páginasP1 VallejoAlexisAlexisRobertoVallejoAún no hay calificaciones

- CuadernoVidaTrascendencia AlexisVallejoGuaipatínDocumento23 páginasCuadernoVidaTrascendencia AlexisVallejoGuaipatínAlexisRobertoVallejoAún no hay calificaciones

- P5 VallejoAlexisDocumento7 páginasP5 VallejoAlexisAlexisRobertoVallejoAún no hay calificaciones

- Análisis de Circuitos Por Los Métodos de Malla y Tensiones de NodoDocumento3 páginasAnálisis de Circuitos Por Los Métodos de Malla y Tensiones de NodoAlexisRobertoVallejoAún no hay calificaciones

- Práctica04 Colas VallejoAlexisDocumento6 páginasPráctica04 Colas VallejoAlexisAlexisRobertoVallejoAún no hay calificaciones

- OrdenaciónSelección VallejoAlexis EstrucDatosDocumento2 páginasOrdenaciónSelección VallejoAlexis EstrucDatosAlexisRobertoVallejoAún no hay calificaciones

- Práctica MétodosBúsqueda VallejoAlexis PDFDocumento6 páginasPráctica MétodosBúsqueda VallejoAlexis PDFAlexisRobertoVallejoAún no hay calificaciones

- Práctica MétodosOrdenación VallejoAlexisDocumento15 páginasPráctica MétodosOrdenación VallejoAlexisAlexisRobertoVallejoAún no hay calificaciones

- Práctica01 MétodoBurbuja VallejoAlexisDocumento4 páginasPráctica01 MétodoBurbuja VallejoAlexisAlexisRobertoVallejoAún no hay calificaciones

- Práctica01 MétodoBurbuja VallejoAlexisDocumento4 páginasPráctica01 MétodoBurbuja VallejoAlexisAlexisRobertoVallejoAún no hay calificaciones

- ColaCircular AlexisVallejoGuaipatín 22052020Documento6 páginasColaCircular AlexisVallejoGuaipatín 22052020AlexisRobertoVallejoAún no hay calificaciones

- Alexis Vallejo (Prepa6)Documento3 páginasAlexis Vallejo (Prepa6)AlexisRobertoVallejoAún no hay calificaciones

- OrdenaciónSelección VallejoAlexis EstrucDatosDocumento2 páginasOrdenaciónSelección VallejoAlexis EstrucDatosAlexisRobertoVallejoAún no hay calificaciones

- Lab Inst 11 - 13 - Prep10 - Mayorga BryanDocumento11 páginasLab Inst 11 - 13 - Prep10 - Mayorga BryanAlexisRobertoVallejoAún no hay calificaciones

- Laboratorio1 Sistemas DigitalesDocumento6 páginasLaboratorio1 Sistemas DigitalesAlexisRobertoVallejoAún no hay calificaciones

- Informe 9 InstrumentacionDocumento7 páginasInforme 9 InstrumentacionAlexisRobertoVallejoAún no hay calificaciones

- Correcion Prueba 1Documento5 páginasCorrecion Prueba 1AlexisRobertoVallejoAún no hay calificaciones

- A Una Gran MujerDocumento1 páginaA Una Gran MujerAlexisRobertoVallejoAún no hay calificaciones

- Laboratorio 5 Sistemas Dig.Documento11 páginasLaboratorio 5 Sistemas Dig.AlexisRobertoVallejoAún no hay calificaciones

- ApuntesDocumento3 páginasApuntesEduardo PozoAún no hay calificaciones

- Analisis de Costos UnitariosDocumento12 páginasAnalisis de Costos UnitariosRuben Palacios ChuquirunaAún no hay calificaciones

- Juego de Pesas 1 MG A 200 G F1 PR-LM-001-PE21-C-1478Documento3 páginasJuego de Pesas 1 MG A 200 G F1 PR-LM-001-PE21-C-1478Edgardo Hurtado QuintoAún no hay calificaciones

- TEMA 2 - 2 Fatiga v3Documento61 páginasTEMA 2 - 2 Fatiga v3Ayrton Portilla EstradaAún no hay calificaciones

- Reactivos Prueba Enlace Media Superior 2011 - LecturaDocumento32 páginasReactivos Prueba Enlace Media Superior 2011 - LecturaTeresa Gordillo Escobar20% (5)

- 2021 08 20 Clase de Teoria de Radiadores 5 m1Documento23 páginas2021 08 20 Clase de Teoria de Radiadores 5 m1Valerio NavarreteAún no hay calificaciones

- Guía de Laboratorio Loayza Yepez Krisdaniel HoguerDocumento110 páginasGuía de Laboratorio Loayza Yepez Krisdaniel HoguerLoayza Yepez Krisdaniel HoguerAún no hay calificaciones

- TRUTZSCHLERDocumento34 páginasTRUTZSCHLERJonathan Celin100% (3)

- 001 Muestreo de Aceites UsadosDocumento2 páginas001 Muestreo de Aceites UsadosYojan CarhuachinAún no hay calificaciones

- Reporte 4Documento15 páginasReporte 4byessiAún no hay calificaciones

- Especificaciones AnfiteatroDocumento87 páginasEspecificaciones AnfiteatroManuel Aurelio Esparza Monroy100% (1)

- Terminologia Relatva Al Agregado para Concreto Astm C 125Documento19 páginasTerminologia Relatva Al Agregado para Concreto Astm C 125Jose Amaya Ahumada100% (1)

- Electricidad BasicaDocumento38 páginasElectricidad BasicaJohn CamachoAún no hay calificaciones

- WifiSlax-Linset (Wpa-Wpa2) - Hackeo de RedesDocumento8 páginasWifiSlax-Linset (Wpa-Wpa2) - Hackeo de Redesdiego2190Aún no hay calificaciones

- Examen CinematicaDocumento16 páginasExamen CinematicaAlba PascualAún no hay calificaciones

- Dimensionamiento de Piñones para Cadena de Rodillos Simple Doble y TripleDocumento9 páginasDimensionamiento de Piñones para Cadena de Rodillos Simple Doble y TripleSaulithop SanchezAún no hay calificaciones

- Ejercicio Basico de Circuitos IntegradosDocumento5 páginasEjercicio Basico de Circuitos IntegradosDanielAún no hay calificaciones

- Aforador ParshallDocumento15 páginasAforador ParshallMaria TaipeAún no hay calificaciones

- Ficha de Seguridad NitrogenoDocumento4 páginasFicha de Seguridad NitrogenoPedro Cerna VelasquezAún no hay calificaciones

- Ciencia de Los MaterialesDocumento2 páginasCiencia de Los MaterialesJorman GrisalesAún no hay calificaciones

- Problemas FlujoDocumento12 páginasProblemas FlujoJackAún no hay calificaciones

- Tarea 2.2 SMR Montaje y MantenimientoDocumento3 páginasTarea 2.2 SMR Montaje y Mantenimientoyejolor284Aún no hay calificaciones

- Sesiön #12 TopografíaDocumento17 páginasSesiön #12 TopografíaMía TerrelAún no hay calificaciones

- Transistor BipolarDocumento75 páginasTransistor BipolaralextapiaromanAún no hay calificaciones

- Especificaciones de MontajeDocumento30 páginasEspecificaciones de MontajeMaxlejAún no hay calificaciones

- Factura Honda 123456Documento2 páginasFactura Honda 123456porto100% (1)

- Operación Español E450AJ PDFDocumento120 páginasOperación Español E450AJ PDFFelipe HernandezAún no hay calificaciones

- Metrado LunesDocumento12 páginasMetrado Lunesluis angelAún no hay calificaciones

- Fisica Semana 2 PDocumento8 páginasFisica Semana 2 PFelipe Moreno Nfs100% (1)